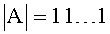

Изобретения относятся к области вычислительной техники и могут быть использованы в процессорах ЭВМ и в устройствах цифровой автоматики. Известны способы и устройства выполнения вычислительных операций (УВВО), заключающиеся в последовательном выполнении элементарных операций (ЭО) приема слагаемых, формировании переноса и суммы в каждом разряде и занесении суммы в триггеры регистра результата или в триггеры первого слагаемого. Способы и устройства выполнения вычислительных операций детально рассмотрены в книге М.А. Карцева «Арифметика цифровых машин», изд-во «Наука», 1969 г., стр. 130-201, 273-286, 331-338. Общими недостатками известных способов и устройств являются необходимость использования трех триггерных регистров для выполнения базовой операции сложения, затрат не менее трех временных тактов выполнения ЭО приема кода, формирования потенциала переноса Тп=2nτ (здесь n - число двоичных разрядов, τ - временная задержка сигнала переноса на одном элементе И, ИЛИ) и запоминания результата суммирования в регистре результата. Для повышения быстродействия выполнения операций сложения широко применяют различные схемы цепей ускорения распространения потенциала переноса, но это связано с дополнительными затратами оборудования, электропотребления и финансовых расходов. Наиболее близким, принятым за прототип, является устройство по патенту RU 2388041 Способ и устройство сложения двоичных кодов, в котором используется только два RS-триггера в каждом разряде, частично совмещены во времени выполнение элементарных операций приема второго слагаемого и формирование переноса, но суммарная задержка сигнала переноса остается равной 2nτ. Предлагаемые способы и устройство устраняют отмеченные недостатки прототипа. Целью изобретения является повышение быстродействия выполнения вычислительных операций за счет снижения временных задержек сигнала переноса, расширение перечня выполняемых операций при минимальных аппаратурных затратах. Для этого предложены способы и устройство выполнения вычислительных операций (ВО), обеспечивающие выполнение одновременно ЭО приема кода и формирование переноса за один временной такт, при этом требуется только два триггерных регистра, построенных на основе RS-триггеров и элементы И, ИЛИ, НЕ, операция логического умножения выполняется за один временной такт без учета времени приема кода второго сомножителя, при этом не требуется дополнительного оборудования, введена операция сравнения модулей кодов регистров

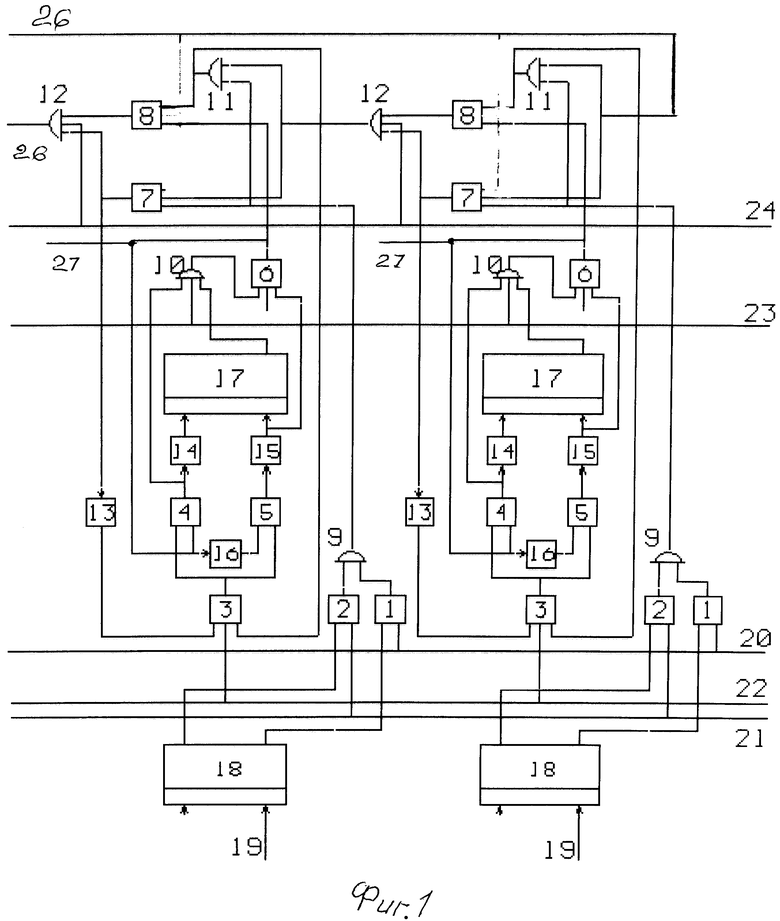

На фиг. 1 приведена функциональная схема двух разрядов УВВО, каждый разряд которого содержит элементы И 1-8, элементы ИЛИ 9-12, элементы НЕ 13-16, RS-триггеры (Tr) 17, 18, информационный вход (ИВ) 19, вход управления (ВУ) выдачей прямого кода В 20, ВУ выдачей инверсного кода

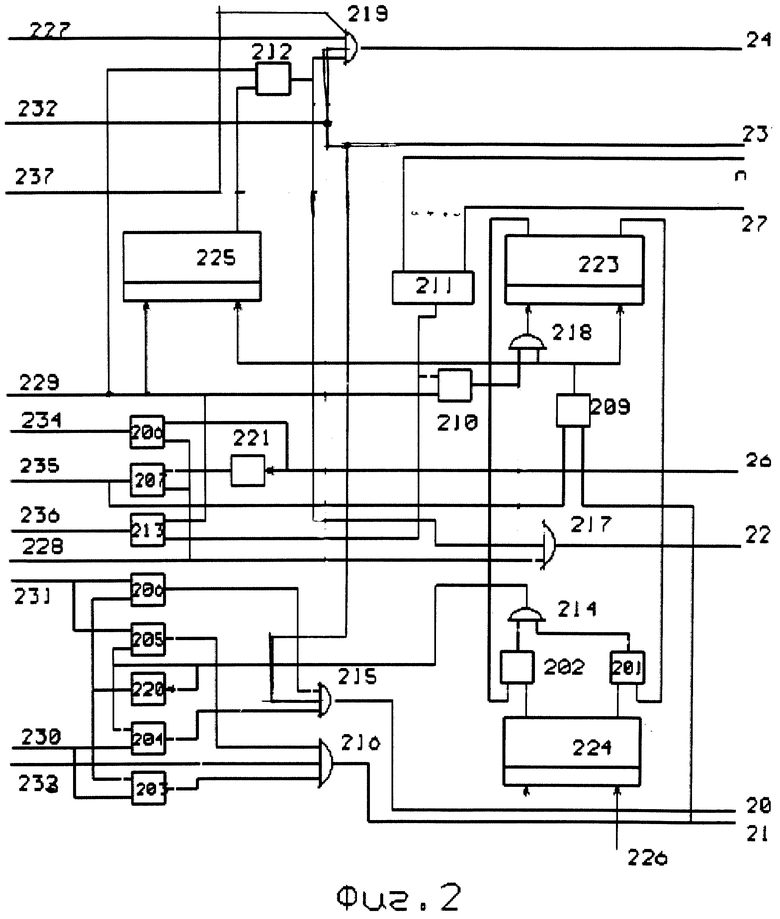

Устройство выполнения вычислительных операций выполнено следующим образом. В исходном состоянии (в статике) в Tr 17 хранится код первого слагаемого, в Tr 18 хранится код нуля, на ВУ 20-24 отсутствуют высокие потенциалы (ВП). Каждый разряд устройства выполнения вычислительных операций осуществляется следующим образом. Информационный вход (ИВ) 19 подключен к единичному входу Tr 18. Единичный и нулевой выходы Tr 18 соединены с первыми входами И 1, 2 соответственно, вторые входы этих элементов подключены к ВУ 20, 21. Выходы И 1, 2 через ИЛИ 9 соединены с первыми входами ИЛИ 11 и И 7. Вторые входы этих элементов подключены к выходу ИЛИ 12 младшего разряда, выход ИЛИ 11 соединен с первыми входами И 8, И 3. Второй вход И 8 подключен к выходу И 6. Выходы И 8, 7 подключены к первому и второму входам ИЛИ 12, третий вход которого соединен с ВУ 24. Выход И 7 через НЕ 13 соединен с вторым входом И 3, третий вход которого подключен к ВУ 22. Выход И 3 соединен с первыми входами И 4, 5, вторые входы которых подключены к входу и выходу НЕ 16 соответственно. Выход И 4 через НЕ 14 соединен с нулевым входом Tr 17. Выход И 5 через НЕ 15 подключен к единичному входу Tr 17 и первому входу И 6. Выход И 6 является выходом счетного триггера Ai. Выход И 4 соединен с первым входом ИЛИ 10, второй и третий входы которого подключены к единичному выходу Tr 17 и ВУ 23 соответственно. Выход ИЛИ 10 соединен с вторым входом И 6. Выход И 6 подключен к второму входу И 4 и НЕ 5. Выход НЕ 16 соединен с И 6. Выход элемента И 6 каждого разряда соединен с входами И 211 БУВО. Работа блока управления выполнением операций (Фиг. 2) осуществляется следующим образом. Информационный вход знака регистра В 226 подключен к единичному входу Tr 224, единичный и нулевой выходы этого триггера подключены к первым входам И 201, 202, их вторые входы связаны с единичным и нулевым выходами Tr 223. Выходы И 201, 202 через ИЛИ 214, соединены с входами И 204, 205 и через НЕ 220 с входами И 203, 206. Выходы И 203, 205 через ИЛИ 216 соединены с первым входом. И 209, второй вход которого связан с выходом И 207. Выход И 209 соединен с единичным входом Tr 223 и через ИЛИ 218 с нулевым входом этого же триггера и единичным входом Tr 225. Выходы И 204, 206 подключены к входам ИЛИ 215. Выходы ИЛИ 215, 216 являются ВУ 20, 21 устройства выполнения вычислительных операций. Вход первого временного такта (t1) 227 подключен к ИЛИ 219, вход t2 228 соединен с входом ИЛИ 217 и с первыми входами И 208, 207, вход t3 229 соединен с нулевым входом Tr 225 и с первыми входами И 210, 212, 213. Второй вход И 212 соединен с единичным выходом Tr 225, выход упомянутого И подключен к входам ИЛИ 219, 217, выходами которых являются ВУ 24, 22 устройства выполнения вычислительных операций. Вход операции вычитания (ОВ) 231 соединен с вторыми входами И 205, 206. Вход операции сложения (ОС) 230 соединен с вторыми входами И 204, 203. Вход операции логического умножения (ОЛУ) 232, далее, ВУ 23 и через ИЛИ 219, 215 подключен к ВУ 24, 20 соответственно. Вход операции сравнения модулей кодов

Рассмотрим работу устройства выполнения вычислительных операций и блока управления вычислительными операциями.

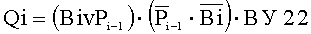

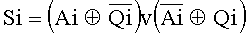

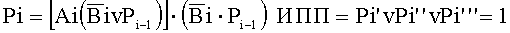

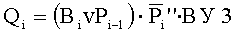

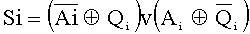

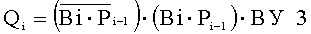

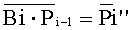

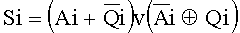

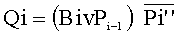

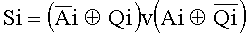

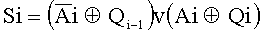

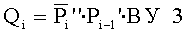

1. Операция сложения (ОС). Операция выполняется за два-три временных такта t1, t2, t3. По t1 на вход управления (ВУ) 230 поступает высокий потенциал (ВП) ОС. Одновременно выполняют ЭО: прием кода второго слагаемого, поступающего по информационным входам (ИВ) 19 на единичные входы Tr 18 и на Tr 224; сравнение знаков слагаемых на И 201, 202, ИЛИ 214 БУВО, при 3 нА=3 нВ на выходе ИЛИ 214 вырабатывается ВП, который по цепи И 204, ИЛИ 215 поступает на ВУ 20 выдачи прямого кода В; формирование имитационного потенциала переноса (ИПП) Pi′″, основного и вспомогательного потенциалов переносов Pi′ и Pi″, равных Pi′=(BivPi-1)·Ai и Pi″=Bi·Pi-1 соответственно. Pi″′=1 во всех разрядах формируется за счет подачи ВП на ВУ 227. Далее сигнал проходит по цепи ИЛИ 219, ВУ 24 и поступает на третий вход ИЛИ 12 каждого разряда УВВО. Все три вида потенциалов переноса логически складываются на ИЛИ 12. Таким образом, потенциал переноса в каждом разряде формируется по соотношению Pi=[A·(BivPi-1)]vBi·Pi-1vИПП=Pi′vPi″vPi″′=1. Такой способ формирования максимального ПП без временой задержки сигнала достигается при условии A1=B1=1, во всех старших разрядах AivBi=1. Это позволяет исключить временные задержки формирования сигнала сквозного переноса, определяемые известным соотношением Pt=2nτ (n - число разрядов; τ - время задержки сигнала на одном элементе И, ИЛИ), и свести максимальную временную задержку переноса до длительности, равной длительности t1. Это позволяет исключить зависимость быстродействия выполнения ОС от числа разрядов УВВО без дополнительного использования оборудования. По t2, после снятия ВП с ВУ 24, в каждом разряде устройства будут сформированы реальные потенциалы Pi. Для получения Si ВП по ВУ 228, ИЛИ 217, ВУ 22 поступает на вход И 3 и вырабатывает импульс Qi выполнения ЭО сложения по модулю два, определяемый по соотношению

2. Операция вычитания (ОВ). Операция выполняется за два-три временных такта. Для выполнения ОВ на ВУ 231 подают ВП, который подключен к первым входам И 205, 206, одновременно принимают код уменьшаемого с ИВ 19, 226 на единичные входы Tr Tr 18 и 224, определяют неравенство знаков регистров А и В с помощью схемы сравнения на элементах И 201, 202, ИЛИ 214, НЕ 220. При равенстве знаков регистров А и В, т.е. при 3 нА≠3 нВ по цепи элементов ИЛИ 14, НЕ 220, И 206, ИЛИ 215, ВУ 20 выдают прямой код Tr 18 на входы элементов формирования Pi и Si, т.е. на элементы И 1, ИЛИ 9, ИЛИ 11, И 7. При 3 нА=3 нВ ВП с входа 231 проходит по цепи элементов И 205, ИЛИ 216, ВУ 21 и выдает инверсный код регистра

3. Операция логического умножения (ОЛУ). По t1 принимают код второго сомножителя в регистр В. По t1 и t2 ВП ОЛУ по входу 232 поступает на ВУ 23, через ИЛИ 219 - на ВУ 24 и через ИЛИ 215 на ВУ 20. При этом ВП по ВУ 23, ИЛИ 10, И 6 поступает на И 4, т.е. разрешает работу этого элемента. ВП с ВУ 24 через ИЛИ 12 i-го разряда поступает на И 7, ИЛИ 11 i-1-го разряда, с выхода ИЛИ 11 сигнал поступает на вход И 3 и разрешает работу этого элемента. При Bi=1 ВП с ВУ 20 по цепи элементов И 1, ИЛИ 9, И 7, НЕ 13 запрещает работу И 3. По t2 ВП по входу 228, ИЛИ 217, ВУ 22 поступит на вход И 3 всех разрядов и выполнит установку триггеров А в «0» тех разрядов, в которых Bi=0, все триггеры А других разрядов сохранят прежнее состояние. При этом сигнал с ВУ 22, И 3, И 4, НЕ 14 проходит на нулевой вход Tr 17. После окончания t2 в Tr 17 будет храниться результат выполнения ОЛУ.

4. Операция инвертирования кода регистра А (ОИА). Операция выполняется за два временных такта. По t1 выполняют ЭО: формирование ИПП за счет подачи на вход 237 ВП, который по цепи элементов ИЛИ 219, ВУ 24, ИЛИ 12 i-го разряда поступает на И 3 i+1-го разряда и разрешает его работу. По t2 ВП, по входу 228, ИЛИ 217, ВУ 22, И 3 поступает на входы И 4, 5 и выполняет инвертирование кода Ai. Если Ai=1, то ВП с единичного выхода RS-триггера 17 через ИЛИ 10, И 6 поступает на второй вход И 4 и разрешает прохождение импульса на нулевой вход Tr 17. При этом ВП с выхода ИЛИ 10 будет поддерживаться неизменным в течение длительности сигнала с ВУ 22 за счет связи выхода И 4 с входом ИЛИ 10. Если Tr 17 хранит код «0», то высокий потенциал с выхода НЕ 16 будет поддерживаться на время длительности сигнала с ВУ 22, поступающего на единичный вход Tr 17 через И 5, НЕ 15. Таким образом, будет выполнено инвертирование кода триггера Ai.

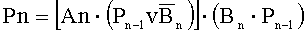

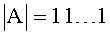

5. Операция сравнения модулей кодов (ОСМ). По t1 выполняют ЭО: формирование ИПП во всех разрядах за счет подачи на вход 227 ВП, который через ИЛИ 219 поступает на ВУ 24, ИЛИ 12 i-го разряда и на входы И 7 ИЛИ 11 i+1-го разряда; принимают код второго числа в регистр В; выдают инверсный код регистра В на входы формирования Pi и Si в каждом разряде; при этом ВП операции по входу 233, ИЛИ 216, ВУ 21 подключают к И 2, И 209 и сохраняют в течение t1 и t2. По t2 выполняют операцию сложения прямого кода А и инверсного кода В и анализируют наличие Pn, выработанного в самом старшем разряде. При Pn=1 на выходе И 208 вырабатывают ВП, соответствующий

Таким образом, предложенные способы и устройство выполнения элементарных вычислительных операций сложения, вычитания, логического умножения, инвертирования и сравнения модулей кодов обеспечивают повышение быстродействия за счет совмещения во времени выполнения ЭО приема кода и формирования сигналов переноса, при этом исключается зависимость времени формирования сигнала переноса от числа двоичных разрядов устройства. Повышение быстродействия вычислительных операций и перечня выполняемых операций достигается при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2013 |

|

RU2537046C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2009 |

|

RU2410745C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2505850C2 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

Группа изобретений относится к области цифровой вычислительной техники и может быть использована для выполнения вычислительных операций. Техническим результатом является повышение быстродействия. Устройство содержит в каждом двоичном разряде два RS-триггера, восемь логических элементов И, четыре логических элемента ИЛИ, четыре логических элемента НЕ, информационный вход, пять входов управления. В устройство входит блок управления вычислительными операциями, содержащий три RS-триггера, тринадцать логических элементов И, шесть логических элементов ИЛИ, два логических элемента HE, три входа подачи временных тактов, пять входов управления, три выхода операции сравнения модулей двух кодов. 6 н.п. ф-лы, 2 ил.

1. Способ выполнения элементарной вычислительной операции (ЭВО) сложения двоичных кодов, реализуемый на основе оборудования сумматора параллельного действия, отличающийся тем, что первое слагаемое хранят в первом регистре А как результат выполнения предыдущей операции, по первому временному такту t1 принимают второе слагаемое во второй регистр В, поступающее с информационных входов каждого разряда, включая информационный вход знака регистра В, определяют равенство или неравенство знаков слагаемых 3 нА=3 нВ или 3 нА≠3 нВ, при 3 нА=3 нВ выдают код В за счет подачи высокого потенциала (ВП) на первый вход управления (ВУ) выдачей прямого кода регистра В на входы элементов формирования переносов; формируют имитационный потенциал переноса (ИПП) Р′″ во всех двоичных разрядах устройства выполнения вычислительных операций (УВВО) путем подачи импульса t1 на четвертый ВУ выработкой ИПП, перенос в каждом разряде формируют по соотношению Pi=[Ai·(BivPi-1)]vBiPi-1vИПП=P1′vP1″vP1″′, здесь Ai, Bi - значение прямых кодов i-го разряда А и В; Pi-1 - перенос из младшего разряда; Pi′ - основной перенос, равный Ai·(BivPi-1), вспомогательный перенос Pi″ равен Bi·Pi-1; Pi″′ - имитационный перенос; одновременно вырабатываются и реальные потенциалы переносов при Ai·Bi=1 и при Ai·Pi-1=1, упомянутые потенциалы переноса (ПП) логически складывают с помощью четвертого элемента ИЛИ, что позволяет свести максимальное время задержки сигнала переноса с 2nτ до длительности импульса t1, τ - временная задержка сигнала на одном элементе И, ИЛИ, при условии, что в каждом разряде устройства коды равны AivBi=1, а в первом разряде A1=B1=1, по второму временному такту t2, после снятия ВП с ИПП, в каждом разряде будут сформированы реальные потенциалы переносов, при 3 нА=3 нВ выполняют ЭО сложения по модулю два кода триггера Ai с кодом триггера Bi или с сигналом переноса, поступившим из младшего разряда Pi-1, при Bi·Pi-1=1 выполнение ЭО сложения по модулю два в i-м разряде запрещают, исполнительный импульс выполнения ЭО сложения по модулю два в i-м разряде Qi вырабатывают согласно соотношению

2. Способ выполнения ЭВО вычитания двоичных кодов, реализуемый на основе оборудования сумматора параллельного действия, отличающийся тем, что уменьшаемое хранят в первом регистре А в прямом коде как результат выполнения предыдущей операции, по первому временному такту t1 выполняют прием вычитаемого во второй регистр В, поступающего с информационных входов каждого разряда, включая знаковый разряд; формируют имитационный потенциал переносов ИПП во всех разрядах устройства, кроме знакового, путем подачи высокого потенциала на четвертый вход управления формированием имитационного потенциала переноса; одновременно формируют и реальные потенциалы переносов при Ai·Bi=1 и при Ai·Pi-1, формирование ИПП выполняют по соотношению Pi=[Ai·(Pi-1vBi)]v(Bi·Pi-1)vИПП=Pi′vPi″vP′″, здесь Ai, Bi - значение прямых кодов триггеров i-го разряда; Pi-1 - перенос из младшего разряда; Pi′=Ai·(BivPi-1) - основной сигнал переноса; Pi″=Bi·Pi-1 - вспомогательный сигнал переноса Pi′″ - имитационный потенциал переноса, такой способ формирования сквозного переноса позволяет свести максимальное время задержки переноса с 2nτ у известных способов до длительности t1, при условии, что в старших разрядах сумматора AivBi=1, а коды первого разряда равны 1, т.е. А1·В1=1, τ - временная задержка сигнала на одном элементе И, ИЛИ, определяют равенство или неравенство знаков уменьшаемого и вычитаемого 3 нА=3 нВ или 3 нА≠3 нВ, при неравенстве знаков выдают прямой код модуля вычитаемого

3. Способ выполнения ЭВО логического умножения, отличающийся тем, что первый и второй сомножители хранят в регистрах А и В соответственно, для выполнения операции формируют высокие потенциалы на первом четвертым и пятом входах управления выполнения вычислительных операций: выдачи прямого кода Bi, формирования имитационного потенциала переноса и операции логического умножения ВУ 1, ВУ 4 и ВУ 5, а также подают исполнительный импульс выполнения операции сложения по модулю два по ВУ 3 и вырабатывают импульс с выхода третьего элемента И, который через четвертый элемент И и второй элемент НЕ поступает на нулевой вход триггера Ai и устанавливает его в «0», что соответствует результату выполнения операции логического умножения в i-м разряде, операцию выполняют за два временных такта, с учетом приема второго сомножителя в триггеры регистра В, результат хранят в регистре А.

4. Способ выполнения ЭВО инвертирования кода регистра А, отличающийся тем, что по t1 формируют имитационный потенциал переносов во всех разрядах за счет подачи высокого потенциала на четвертый вход управления, подают высокий потенциал на третий вход управления выполнением операции сложения по модулю два и вырабатывают в каждом разряде сигнал Qi согласно соотношению

5. Способ выполнения ЭВО сравнения модулей двух кодов, отличающийся тем, что по первому временному такту t1 принимают модуль второго кода в регистр В, поступающий с информационных входов ИВ, выдают инверсный код триггеров регистра

6. Устройство выполнения элементарных вычислительных операций сложения, вычитания, логического умножения, инвертирования кода регистра А и сравнения модулей двух кодов, содержащее устройство выполнения вычислительных операций (УВВО) и блок управления выполнением операций (БУВО), n - разрядные триггерные регистры А и В, схемы формирования потенциалов переносов Pi и суммы Si в каждом разряде, выполненное на основе RS-триггеров и логических элементов И, ИЛИ, НЕ, отличающееся тем, что каждый двоичный разряд УВВО содержит первый и второй RS-триггеры Ai и Bi соответственно, при этом информационный вход i-го разряда (ИBi) подключен к единичному входу второго триггера Bi, единичный и нулевой выходы которого соединены с первыми входами первого и второго элементов И, вторые входы этих элементов связаны с первым входом управления выдачей прямого кода Bi и вторым входом управления выдачей инверсного кода

| СПОСОБ И УСТРОЙСТВО СЛОЖЕНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2388041C2 |

| СПОСОБ И УСТРОЙСТВО ВЫЧИТАНИЯ ДВОИЧНЫХ КОДОВ | 2010 |

|

RU2410746C1 |

| ПРОЦЕССОРНЫЙ ЭЛЕМЕНТ | 1996 |

|

RU2089936C1 |

| Управляемый арифметический модуль | 1978 |

|

SU840881A1 |

| US 4920509 A, 24.04.1990 | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| US 2008281897 A1, 13.11.2008 | |||

Авторы

Даты

2015-06-10—Публикация

2013-06-13—Подача