о со со ю со

Изобретение относится к вычислительной технике и предназначено для использования в высокоскоростных процессорах быстрого преобразования Фурье, базирующихся на алгоритмах типа Винограда

Цель изобретения - повышение быстродействия и расширение области применения за счет реализации преобразования для произвольного целою значения основания

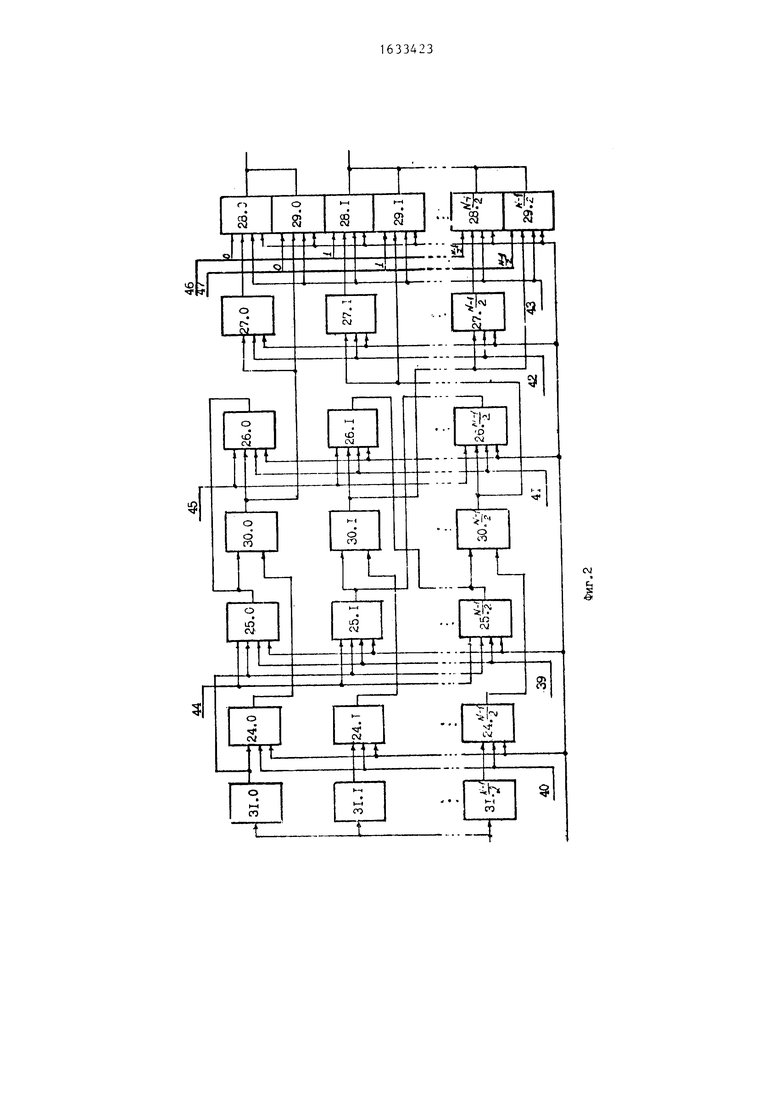

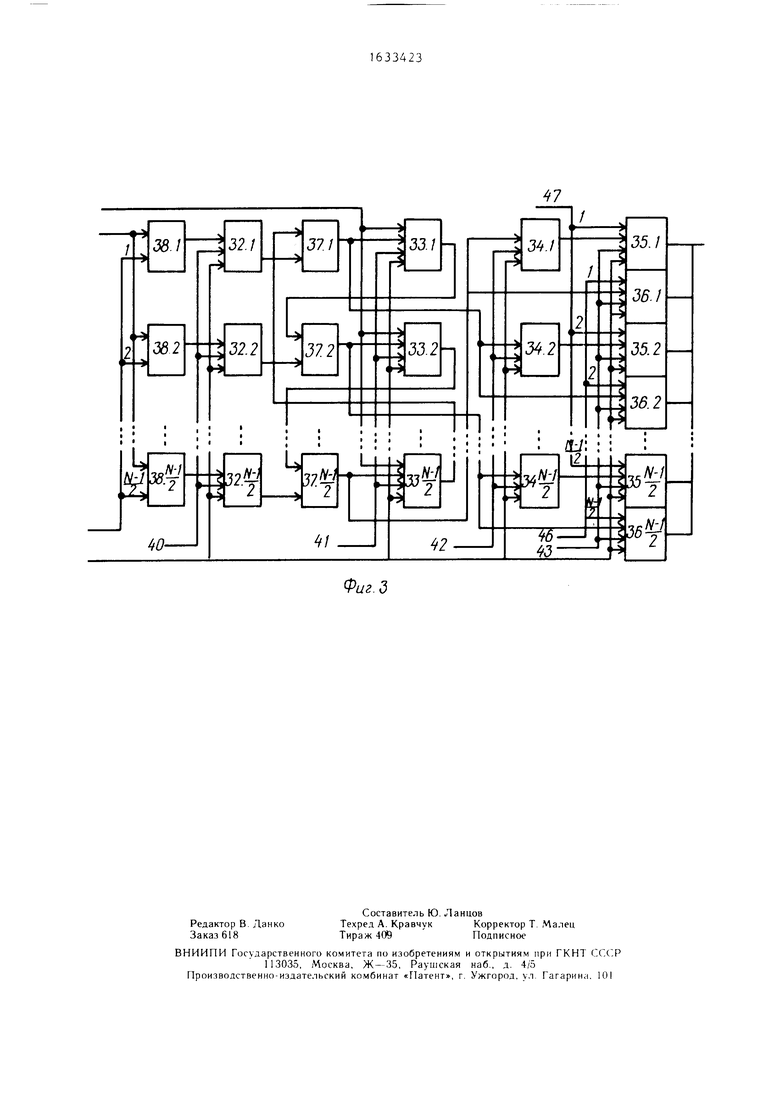

На фиг 1 представлена структурная схема устройства для вычисления дискретного преобразования Фурье в модулярной системе счисления, на фиг 2 и 3 - структурные схемы операционных блоков соответственно первой и второй групп

Устройство содержит информационный вход 1, первый 2 и второй 3 установочные входы, входы 4-8 кода операции, знаковый вход 9, тактовый вход 10, четыре группы регистров 11 /-14/, две группы сумматоров 15/, 16/ по модулю ml,две группы вычита- телей 17/, 18/ по модулю ml, две группы операционных блоков 19/ и 20/, преобразо ватель 21 двоичного кода в модулярный, преобразователь 22 с масштабированием модулярного кода в двоичный, выход 23 Индексы / номеров блоков (, 2, ,К) совпадают с порядковыми номерами модульных оснований mi, m2, ,тц, связанных с этими блоками

Операционный блок 19/ первой группы состоит (фиг 2) из групп регистров 24 р - 29 р (, 1, , (Лг-1)/2), группы сумматоров 30 р по модулю ml и группы умножителей 31 р по модулю ml

Операционный блок 20 / содержит (фиг 3) группы регистров 32 г-36 г (,2, ,( - 1)/2), группу сумматоров 37 г по модулю ml и группу умножителей 38 г по модулю ml

Входы разрешения записи регистров 250. 25 1, , 25 (Л -1)/2 объединены и подключены к входу 39 кода операции устройства Входы 40-42 кода операции устройства соединены с входами разрешения записи соответственно регистров 24 р, 26 р и 27 р (р 0,1, , (/V-1)/2) операционных блоков 19 / группы и соответственно регистров 32 г-34 г (,2, ,(V-1)/2) операционных блоков 20/ группы Входы разрешения записи регистров 280, 28 1, , 28(Л -1)/2 и 290, 291, , 29(Л -1)/2 объединены и подключены к входу 43 кода операции устройства

Входы 44 и 45 кода операции устройства соединены с входами разрешения выдачи соответственно регистров 25 р и 26 р групп

Входы 46 и 47 кода операции устройства содержат по (Л + 1)/2 шин, причем р-я шина входа 46 заведена на вход разрешения выдачи регистра 28 р, а р-я шина 47 - на вход разрешения выдачи регистра 29 р (,1, , ( - 1)/21,г-я шина входа 46 заведена на вход разрешения выдачи регистра 35л, d r-я шина входа 47 устройства -

на вход разрешения выдачи регистра 36 г (,2,. ,(Л -1)/2).

Все функциональные узлы устройства могут быть реализованы на основе постоянных запоминающих устройств (ПЗУ) небольшой емкости (например, серий К556, К541) и регистров разрядностью bi Iog2ml, через х обозначается наименьшее целое число, не

меньшее действительного числа х, где / соответствует индексу номера регистра или операционного блока, куда входит регистр Причем выходы регистров 25 р, 26 р, 28 р 29 р, 35 г, Зб.л (,1, ,( - 1)/2, ,2, . ,(А - -1)/2) могут переходить в высокоомное третье

состояние, что позволяет объединить выходы блоков и осуществлять таким обратом мультиплексирование данных Информация на выходе этих регистров появляется при наличии сигнала ни-жот уровня на входе

0 разрешения выдачи кода соответствующего регистра Запись информации в любой ре гистр устройства осуществляется нарастающим фронтом тактового сипмла на тактовом входе регистра при наличии низкого уровня на входе разрешения приема кода

5 Сумматоры 15 /, 16 /, 30 р. 37 г и вычита- тели 17/, 18/ (,2, ,К, ,1, ,( - 1)/2, ,2, ,(Л 1)/2) могут представлять собой ПЗУ емкостью по Ь, бит, в которых по адресу Л-|- Y-2hl записана ма |А +У,„( для сумматоров или разность |А-Я , для нычитателеи С умматоры 16/ и вычитатели 18/ имеют управляемые выходы с гремя состояниями Информация на их выходах появляется при наличии сигнала низ кою уровня на входе разрешения выдачи В остагьное время выход находится в высо коомном состоянии Умножители 31 р и 38 г /-х операционных блоков также могу i являться ПЗУ емкостью соответственно и по bi бит

0 В качестве преобразователя 21 двоичного кода в модулярный и преобразователя 22 с масштабированием модулярного кода в двоичный мо ..но использовать любые известные устройства, работающие в конвейерном ре жиме Тогда преобразователь 21 будет осу5 ществлять преобразование двоичного кода в модулярный за / тактов () с пропускной способностью одно число за такт, а преобразователь 22- перевод числа из модулярной системы счисления в двоичную и

Q масштабирование на констант уф ы 7 4-3 так- тов с пропускной способностью одно число за гакт

Реализация дискретного Л-точечного (Л-простое число) преобразования Фурье входной последовательности у(п) / («) +

5 (п) (,1, , Л -1, у (п) и у (п) - соответственно действительная и мнимая со ставляющие входного отсчета ц(п)) заключается в вычислении

5

V-Y x(u)Zy(n) IF

1

.&

я.0

(V

где u, n, Ј(0,1,..,/V

(2nun/N)-jsin(2nun/N) (2).

Подставляя (2) в (1) и отделив действительную и мнимую составляющие, получаем

V-/

x(u)I.(y (n)cos(2nun/N)+y (n)sin(2xun/N));

)f((n)cos(2nun)N)-y (n)sin(2n.un/N)). (3)

Учитывая периодичность cos(2nun/N) и sin(2nun/N) и аппроксимируя их соответственно дробями Z/(un)/Q и )/Q, исходное ДПФ можно переписать в следующем приближенном виде

А,

W У V)())

x (u)ZQ у (0) (/)Z ( ;/it f

+ 2 ,4(,v-/)-zV))

)«

)Qy {0)+Z Л Ы« Z ()/ - 7/2 ,,

-s ,4W-/).z W)) i

x10)(Qy(0)(n.Q i

J M(Q/)+Ј X).z ()-zV( XZV)) :

AW fy ftI

x ( - со ) I ( Q y ( fl ) + I Л (/) Z ( A;-/)-Z(o/))Q- J-,

(rt-bt

+ v Л

/

где ,2 (.V-l)/2;

,2 (,V-l)/2;

(/ y fO+yV-O; Af(N - t)y (t)-y (,V - t),

Л(/)У (0+У (Л -/); Л(Л;-/) / (/)- y(N - t),

Q-cos(2np/tM) Q sin(2np /N )}fs;

Через Л обозначается ближайшее к А целое число. В последнем выраженииС - это некоторое целое число, задающее диапазон измерения действительной и мнимой составляющих констант м р (, 1,..., ,V-1).

Рассмотрим, как работает устройство для вычисления Л -точечного дискретного пре1633423

образования Фурье в модулярной системе счисления (Л -простое).

Двоичные чиста, поступающие на информационный вход устройства, а также фор- мируемые на его выходе, принадлежат диапазону ( - Q, - , . Q. где Q выбирают из условия

Q- .

М - т, т, ,тк i;

/«о - вспомогательный , выбираемый ич условий

, -- К- 2, та Л - Z .

За время очередного преобразования Фурье через информационный вход 1 за гак- тов поступают Л комплексных отсчетов У(0), У(1) у(Л -1), причем установлен

0 следующий порядок их поступления

g (Q Ч1(). ), yiV-2), . y ((.V -D/2), v ((A +D/2j, ). s/Y/i. ),. ., y((,V-l)/2).V+l)/2

Так как устройство работает в конвейер ном режиме с пропускной способность одно преобразование Фурье за 2 тактов, то каждый блок устройства занят в данном преобразовании в течение 2/V тактов. Если за начало текущего преобразования принять момент поступления первого отсчета на ино формационный вход I устройства, то начало работы любого блока чстройства в данном преобразовании будет сдвинуто на неличину задержек в предыдущих блоках стройсгва Рассмотрим вначале подробно обработку действительных частей входных отсчетов, по5 ступающих на устройство в течение первых /V тактов. С информационного входа I ст- ройства отсчеты попадают в преобразователь 21, который осуществляет перевод числа из двоичной системы в модулярную Число ) (,1, ...Л -1) проходит преобразователь

0 21 за Т тактов и появляется на его выходе

в виде набора остатков t/i(n), )).

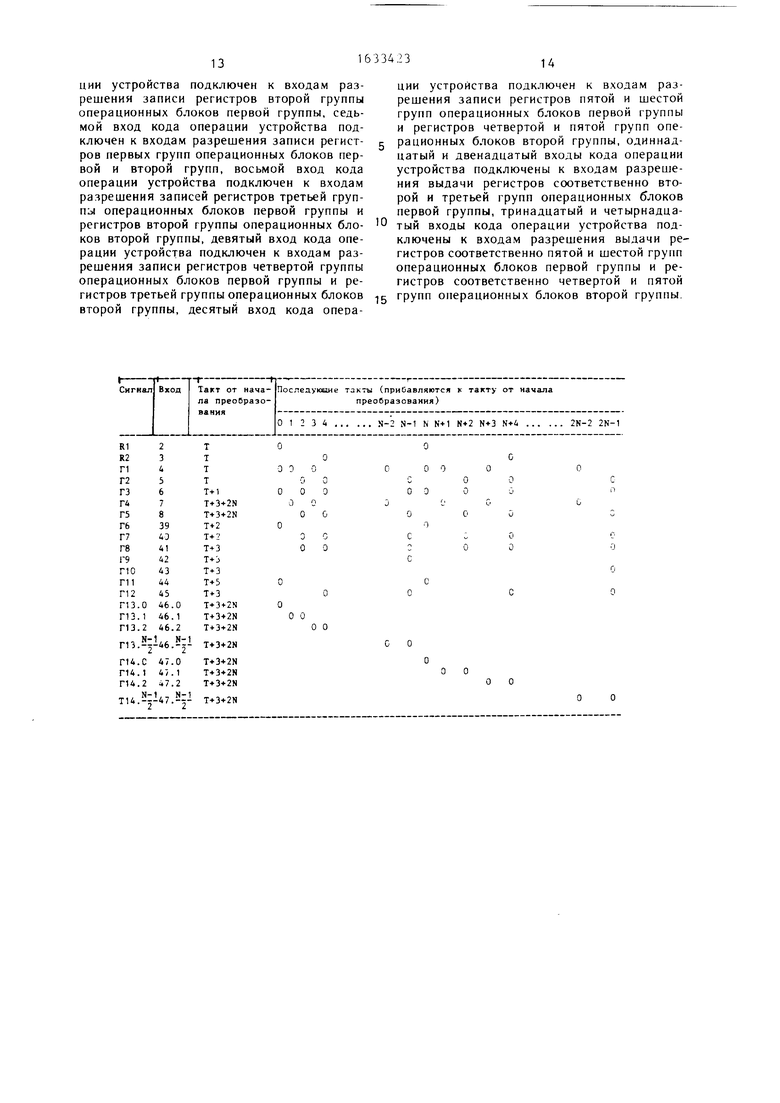

где у /(л)е1у(л)1т/ (/ 1.2,...,/(). На /-м такте от начала преобразования на входе 4 появляется сигнал низкого уровня (см, таблицу,

5 где указаны номера тактов, во время которых на установочные входы кода операции устройства поступают сигналы низкого уровня, управляющие работой блоков устройства) и в регистр 11./ заносится вычет У/(0). Одновременно сигнал /() с первого

0 установочного входа 2 устройства обнуляет регистр 12./. Тогда на следующем (7 +1)-м такте с входа 6 устройства поступает сигнал , и число (//(0), после сложения (вычитания) с нулем в сумматоре 15./ и вычитателе 17./ заносится в регистры 13./, 14./. В этом же такте по Г1-0 в регистр 11./ занесется вычет у /{ 1).

По сигналу на входе 5 устройства в регистр 12/ поступает на ( такте

5

/Q(/H0)+- A (tt-Z(.

число y i(, -) Одновременно вычет у /(О) HI регистра 13/ поступает в операционный б юк 19 /, где после умножения в умножи теле 31 0 на Q произведение | ц /(0) , за носится в регистры 25 0-25 (Л -1 )/2 по сиг налу , поступающему в данном такте (см таблицу) с входа 39 устройства На (7 4-3)-м такте пара чисел у/ (1) и У((, - 1) формирует согласно формуле (5) на выхо дах сумматора 15 / и вычигателя 17 / величины A I() и /fy/V-1), которые поступают соответственно в регистры 13 / и 14 / по CHI налу с входа 6 устройства В этом же такте в регистр 11 / по сигналу Г заносится новое число у(2) Таким образом, поочередно через такт вычеты у/(/) и у,( V - I) 15 (,2, ,(/V-1)/2) с /-го выхода преобразователя 21 заносятся соответственно в регистры il / и 12/ Тогда на выходе сумматора 15 / формируется величина Ai(t)r а на выходе вычитателя 17/- величина ЛдЛ-/), которые запоминаются соответственно в ре гистрах 13/-и 14/ по сигналу , поступающему с входа 6 устройства на (Г+ 1 +2);-м тактах С выхода регистра 13/ число .4/(/) поступает на (7+2 + 2/)-м такте на входы умножителей 31 р (,1, , ,( -1)/2)

На выходе умножителя 31 г (/,2, , (V-l)/2) формируется произведение I Д/(/)Х X2(r)mi, которое заносится в этом же такте в регистр 24 г по сигналу , поступающему с входа 40 устройства Этим же сигна лом в регистр 240 заносится величина A i(t) с умножителя 310 На (/+5)-м такте на вход разрешения выдачи числа регистров 25 р поступает сигнал с входа 44 устройства По этому сигналу число A (0) поступает на первые входы сум

матрров 30 р, где оно складывается с числом 35 осуществляется по сигналу I Ai() (для сумматора 300) и с числом I/4 (/)-ZV))m (для сумматора 30 г) Сумма заносится в регистр 26 р по сигналу , поступающему на вход разрешения записи этого регистра в данном такте с входа 41 устройства Далее на (У+З+2/i) м такте (, 3, , (Л -1/2) осуществляется суммирование содержимого регистра 26 0 с числом Ai(t) , поступающим из регистра 24.0 При этом на входы разрешения выдачи регистров 26 р поступают на () x тактах с входа 45 устройства сигналы (см таблицу) Результат суммирования поступает с выхода сумматора 30 0 в регистр 26 0, где запоминается по сигналу

Ы

На ( + 2)-M такте по сигналу , поступающему с входа 42 устройства, первая из этих величин заносится в регистр 270, а вторая - в регистр 27 г2

Аналогичным образом в течение следующих N тактов осуществляется обработка следующих Л входных отсчетов У (0), /(), 10 уЧЛМ). у(2), , Ч((-)/2), )/2). Сформированная на (7 -f-2V-(-2)-M такте величина

« №1г „ , |Q«MO)+QX A,(t)m,

заносится с вылода сумматора 30 0 в регистр 29 0, а величина

i,,

|Qy,(0)4-2 AM)-Z(r2t)m,

20 с выхода сумматора 30 г в регистр 29 г Од повременно осуществляется перезапись чисел из регистра 27 р в регистр 28 р Запись в регистры 28 р и 29 р осуществляется по сигналу Г , поступающему на (7-|-2А

„ +2)-м такте с входа 43 устройства

Пареллельно с работой операционного блока 19 / осуществляется обработка выче тов /4/(,V - /) и A (N - /) в операционном блоке 20 / В соответствии с тим вычет А((- /), поступающий с выхода регистра 14 / на первые входы умножителей 38 г (,2, ,(V-1)/2), совместно со знаковым признаком Srt на втором входе умножите ля формирует произведение ISrM (V- /)Х XZ(r)mi, которое поступает на (74-2/4-2) м такте в регистр 32 г Запись в регистр 32 г ществляется по сиг Знаковый признак

5г,(1,

30

Одновременно в регистре 26 г по этому же сигналу запоминается сумма от сложения содержимого регистра 26 г и числа A /(t)X XZ (r)mi (п )г-21(м pjfe+1) Таким образом, через i тактов от начала работы сумматора 30 0 на его выходе сформируется величина

{Qy (0)+QZ /4/(/)U

а на выходе сумматора

30 г - величина

поступает со знакового входа 9 устройства, такте 40 содержащего (Л - 1)/2 шин, причем л-я шина заведена на второй вход умножителя 38 г операционного блока 20 / С выхода регистра 32 г числа поступают на второй вход сумматора 37 г, где они суммируются с содержи- мым регистра 33 г, jfri k-21.+1)

Результат сложения по сигналу запоминается вновь в регистре 33 г При этом на 7Y4-M такте на установочные входы регистров 33 1, 33 2, , 33 (Л/- 1) /2 поступает сигнал с установочного входа 3

5Q устройства В результате действия этого сигнала в указанных регистрах появляются НУЛИ. Тогда на (7+5)-м такте в регистр 33 г поступает сумма |SrM /(/V-/)Z(r)lm( Далее, на (/4-34-2/|)-м (/,2,3, , (/V-1)/2) такте в регистр 33 г по сигналу поступает

55 результат сложения величины ISr//4/iV-/)Х XZ(r)mi с содержимым регистра 33 г

Таким образом, на () м гакте на выходе сумматора 37 г появляется

/Q(/H0)+- A (tt-Z(.

5

5 осуществляется по сигналу

Ы

На ( + 2)-M такте по сигналу , поступающему с входа 42 устройства, первая из этих величин заносится в регистр 270, а вторая - в регистр 27 г2

Аналогичным образом в течение следующих N тактов осуществляется обработка следующих Л входных отсчетов У (0), /(), уЧЛМ). у(2), , Ч((-)/2), )/2). Сформированная на (7 -f-2V-(-2)-M такте величина

« №1г „ , |Q«MO)+QX A,(t)m,

заносится с вылода сумматора 30 0 в регистр 29 0, а величина

i,,

|Qy,(0)4-2 AM)-Z(r2t)m,

0 с выхода сумматора 30 г в регистр 29 г Од повременно осуществляется перезапись чисел из регистра 27 р в регистр 28 р Запись в регистры 28 р и 29 р осуществляется по сигналу Г , поступающему на (7-|-2А

+2)-м такте с входа 43 устройства

Пареллельно с работой операционного блока 19 / осуществляется обработка выче тов /4/(,V - /) и A (N - /) в операционном блоке 20 / В соответствии с тим вычет А((- /), поступающий с выхода регистра 14 / на первые входы умножителей 38 г (,2, ,(V-1)/2), совместно со знаковым признаком Srt на втором входе умножите ля формирует произведение ISrM (V- /)Х XZ(r)mi, которое поступает на (74-2/4-2) м такте в регистр 32 г Запись в регистр 32 г ществляется по сиг Знаковый признак

5г,(1,

0

./tfuV-O-ZViOU ы

которая поступает в регистр 34.л (г -IrUi-iy + 1) по сигналу .

Аналогично в течение следующих А тактов обрабатываются числа Ai(N-l), поступающие из регистра 14./. Сформированная на (7 -|-2Л/+2)-м такте величина

-)k „,,

12 SrtAt(,M - Л/(л2пи/ Ј-/

заносится в регистр 36.г}, здесь Srt(-1 Одновременно в регистр 35.г переписывается содержимое регистра 34.г, для чего на регистры 35.г и 36.г поступает сигнал с входа 43 устройства.

После заполнения регистров 28.р. 29.р,

35.л, 36.л (, 1 (N-1)/2; ,2,...,

(Л1 -1)/2) начинается формирование выходных отсчетов(и) согласно (4). Для этого на

перевод поступающих на его вход чисел из модулярной системы счисления в двоичную. Одновременно происходит масштабирование на величину Q в соответствии с (4). Таким образом, начиная с (27+2Л -(-6)-го такта, на выходе преобразователя 22 появляются выходные отсчеты. Они поступают на выход 23 устройства в течение 2V тактов в следующем порядке х {0) х (), лЛЛ - I), х (2),

х (2) х (-)/2), .V+l), 2.i, ),

10 х(), л(Л;-1), ..., Jt-n.,V-l)/2), xV.V+n/2).

На этом заканчивается выполнение -точечного дискретного преобразования Фурье. Следует отметить, что следующее преобразование мо/кет начинаться сразу после 2Л -(О такта текущего преобразования.

Из приведенного следует, что при работе в конвейерном режиме выполнение одного Л-точечного ДПФ в устройстве занимает 4Л/-J-2/ + 6 тактов, при этом, обращение к устройству можно производить через каждые

(7Ч-2Л + 3)-м такте из регистра 28.0 опера- 20 т 2Л тактов. Если, например, ,, то т 10

тактов. При длительности одного модчльного такта 100 не, частота обращения к устройству составляет 1 МГц. Если используется модулярная система счисления с осно„ ваниями т 123, т 125, т.- 127, т. 128, 25 «т Г I U О п О п f LJ 1 О IJ О I IT и п U LJ f It |Л ЯЛИЫЛЛ ЛЫ 1 1 ционного блока 19./ по сигналу Г13-0, поступающему с входа 46 устройства, считывается величина

,Wit

Q9№)+QZA (

то диапазон действительной и мнимой составляющих отсчетов входных и выходных сигналов представляет собой

то диапазон действительной и ставляющих отсчетов входных сигналов представляет собой

30

и подается на /-и вход преобразователя 22 с масштабированием модулярного кода в двоичный. При этом выходы сумматора 16./ и вычитателя 18./ закрыты. В течение следующих .V- 1 тактов выход регистра 28.0 становится закрытым, а открываются поочередно выходы сумматора 16./ и вычитателя 18./, причем сигнал на вход разрешения выдачи кода сумматора 16./ поступает с входа 7 устройства в (,V-|-2-)-2|ij-x

тактах, а сигнал с управляющего вхо-и 172 семиразрядных регистров

да 8 устройства поступает на вход вычитателя 18./ в (7 +27 + 3 + 2ц)-х тактах (ц 1.2,...,(/V-1)/2). На первые входы сумматора 16./ и вычитателя 18./ поступает содержимое регистров 28.г, а на вторые входы - регистров 30.г. Для этого на (Т+ 4-2Л +2+2р.)-м такте на вход разрешения выдачи регистров 28. ц и 36. ц подается сигнал с входа 46 устрой ,;-за.

Аналогичным образом в течение следующих тактов на /-и вход преобразователя 22 поступают величины

1 - , , ..., 21

При этом для построения пр устройства в случае Л 7 без у на преобразователи кодов из од счисления в другую необходимо костью 256 четырехразрядных с

Формула изобретени

Устройство для вычисления преобразования Фурье в модуля 40 счисления, содержащее преобра ичного кода в модулярный, п пы сумматоров и вычитателей по (/ I,/(, где К - количество оснований), три группы регистр гистров в каждой, преобразоват табированием модулярного кода причем тактовые входы регистр по третью групп, преобразовате го кода в модулярный и прео с масштабированием модулярн

lQyXO))|m(,)+

t ,(

+ 2( AAt)(it)+Ј /l,OV-l)ZVu;

, , -К„ (Wk,,,

QV(0)+Z Att)Z(4)-Z )A

t--t

lHOlmf

соответственно на тактах (/ +ЗЛ +3), (7 + + ЗЛ/+2 + 2ц) и (Т + + 2ц). Сигналы П4 0 поступают на входы разрешения выдачи

двоичный подключены к тактовому вхаду устройства, входы установки в «О регистров второй группы подключены к первому установочному входу устройства, входы разрешения записи регистров с первой по третью группу подключены соответственно к первокода регистров 29.ц и 35.ц с входа 47 уст- 55 му, второму и третьему входам кода операройства (см. таблицу).

Преобразователь 22 осуществляет в конвейерном режиме в течение (/ -(-З)-х тактов

ции устройства, отличающееся тем, что, с целью повышения быстродействия и расширения области применения за счет осущестперевод поступающих на его вход чисел из модулярной системы счисления в двоичную. Одновременно происходит масштабирование на величину Q в соответствии с (4). Таким образом, начиная с (27+2Л -(-6)-го такта, на выходе преобразователя 22 появляются выходные отсчеты. Они поступают на выход 23 устройства в течение 2V тактов в следующем порядке х {0) х (), лЛЛ - I), х (2),

х (2) х (-)/2), .V+l), 2.i, ),

0 х(), л(Л;-1), ..., Jt-n.,V-l)/2), xV.V+n/2).

На этом заканчивается выполнение -точечного дискретного преобразования Фурье. Следует отметить, что следующее преобразование мо/кет начинаться сразу после 2Л -(О такта текущего преобразования.

Из приведенного следует, что при работе в конвейерном режиме выполнение одного Л-точечного ДПФ в устройстве занимает 4Л/-J-2/ + 6 тактов, при этом, обращение к устройству можно производить через каждые

0 т 2Л тактов. Если, например, ,, то т 10

ваниями т 123, т 125, т.- 127, т. 128, «т Г I U О п О п f LJ 1 О IJ О I IT и п U LJ f It |Л ЯЛИЫЛЛ ЛЫ диапазон действительной и мнимой составляющих отсчетов входных и выходных сигналов представляет собой

и 172 семиразрядных регистров

1 - , , ..., 21 ,.

При этом для построения предлагаемого устройства в случае Л 7 без учета затрат на преобразователи кодов из одной системы счисления в другую необходимо 160 ПЗУ емкостью 256 четырехразрядных слов каждое

Формула изобретения

Устройство для вычисления дискретного преобразования Фурье в модулярной системе 0 счисления, содержащее преобразователь двоичного кода в модулярный, первые группы сумматоров и вычитателей по модулю ml (/ I,/(, где К - количество модульных оснований), три группы регистров по Д регистров в каждой, преобразователь с масш- табированием модулярного кода в двоичный, причем тактовые входы регистров с первой по третью групп, преобразователя двоичного кода в модулярный и преобразователя с масштабированием модулярного кода в

50

двоичный подключены к тактовому вхаду устройства, входы установки в «О регистров второй группы подключены к первому установочному входу устройства, входы разрешения записи регистров с первой по третью группу подключены соответственно к перво 55 му, второму и третьему входам кода операции устройства, отличающееся тем, что, с целью повышения быстродействия и расширения области применения за счет осуществления преобразования для произвольного целого значения основания Л , в него введены вторые группы сумматоров и вычи- тателей по модулю ml, четвертая группа регистров и первая и вторая группы операционных блоков, при этом информационный вход преобразователя двоичного кода в модулярный является информационным входом устройства, а /-и выход преобразователя двоичнго кода в модулярный соединен с информационными входами 1-х регистров первой и второй групп, второй установочный вход устройства подключен к установочным входам операционных блоков второй группы, третий вход кода операции устройства подключен к входам разрешения записи регистров четвертой группы, четвертый и пятый входы кода операции устройства подключены к входам разрешения выдачи соответственно сумматоров по модулю ml и вычитателей по модулю ml вторых групп, выход /-го регистра первой группы соединен с первыми входами 1-х. сумматора по модулю ml и вычитателя по модулю ml первых групп, вторые входы которых подключены к выходу /-го регистра второй группы, выход /-го сумматора по модулю ml первой группы соединен с информационным входом 1-го регистра третьей группы, выход которого соединен с информационным входом 1-го опера- ционного блока первой группы, выход 1-го вычитателя по модулю ml первой группы соединен с информационным входом 1-го регистра четвертой группы, выход которого соединен с информационным входом 1-го операционного блока второй группы, знаковый вход которого соединен со знаковыми входами операционных блоков второй группы и подключен к знаковому входу устройства, выход /-го операционного блока второй группы соединен с первыми информационными входами /-х сумматора по модулю ml и вычитателя по модулю ml вторых групп, вторые информационные входы которых подключены к первому выходу 1-го операционного блока первой группы, второй выход которого соединен с выходами 1-х сумматора по модулю ml и вычитателя по модулю ml вторых групп и подключен к /-му входу преобразователя с масштабированием модулярного кода в двоичный, выход которого является выходом устройства, тактовый вход которого подключен к тактовым входам операционных блоков первой и второй групп и регистров четвертой группы, причем /-Й операционный блок первой группы содержит с первой по шестую группы регистров по l.V-f-l)/2 регистров в каждой, группу из (/V-)- 1 )/2 сумматоров по модулю ml и группу из (.V-j-l)/2 умножителей по модулю ml, при этом входы умножителей подключены к информационному входу операционного блока первой группы, выход р-го умножителя, где ,1 ,...,(jV-1)/2, соединен с информационным входом р-го регистра первой группы, кроме того, выход нулевого умножи теля соединен с информационными входами регистров второй группы, выход р-го регистра первой группы соединен с первым входом р-го сумматора по модулю ml группы, выход нулевого регистра второй группы соединен с выходом нулевого регистра третьей группы и подключен к второму входу нулевого сумматора по модулю ml группы,

- выход которого соединен с информационными входами нулевых регистров третьей, четвертой и шестой групп, выход r-го регистра, где ,2, ..., (Л - 1)/2, второй группы соединены с выходом (г-2|( V - 1 )/2 + I )-го

регистра третьей группы и подключен к первому входу г-го сумматора по модулю ml группы, выход которого соединен с информационными входами r-го регистра третьей группы и (irl(V-1)/2 + ) реестров четвертой и шестой групп, выход р-го регист0 ра четвертой группы соединен с информационным входом р-го регистра пятой группы, выходы нулевых регистров пятой и шестой групп соединены и являются первым выходом операционного блока первой груп5 пы, а выходы остальных регистров пятой и шестой групп соединены между собой и образуют второй выход операционного блока первой группы, тактовые входы всех регистров операционного блока первой группы соединены между собой и образуют так0 товый вход операционного блока первой группы, причем /-Й операционный блок второй группы содержит с первой по пятую группы регистров по (Л1 -1)/2 в каждой, группу из (Л -1)/2 сумматоров по модулю ml и группу из (Л -1)/2 умножителей по

5 модулю ml, при этом первые входы умножителей соединены между собой и являются информационным входом операционного блока второй группы, вторые входы умножителей образуют знаковый вход операционного блока второй группы, выход r-го умножителя, где , 2, ..., (N-1)/2, соединен с информационным входом r-го регистра первой группы, выход которого соединен с первым входом л-го сумматора по модулю ml группы, второй вход которого подклю5чен к выходу (I г-21 (Л -1)/2-)-1) регистра второй группы, а выход - соединен с информационными входами л-го регистра второй группы и (r-2|(,V-l)/2+l) регистров третей и пятой групп, выход r-го регистра третьей группы соединен с информационным

0 входом r-го регистра четвертой группы, входы установки в «О регистров второй группы являются установочным входом операционного блока второй группы, выходы регистров четвертой и пятой групп соединены через монтажное ИЛИ и образуют выход

5 операционного блока, а тактовые входы всех регистров являются тактовым входом операционного блока, шестой вход кода опера0

ции устройства подключен к входам разрешения записи регистров второй группы операционных блоков первой группы, седьмой вход кода операции устройства подключен к входам разрешения записи регистров первых групп операционных блоков первой и второй групп, восьмой вход кода операции устройства подключен к входам разрешения записей регистров третьей группы операционных блоков первой группы и регистров второй группы операционных блоков второй группы, девятый вход кода операции устройства подключен к входам разрешения записи регистров четвертой группы операционных блоков первой группы и регистров третьей группы операционных блоков второй группы, десятый вход кода операции устройства подключен к входам разрешения записи регистров пятой и шестой групп операционных блоков первой группы и регистров четвертой и пятой групп операционных блоков второй группы, одиннадцатый и двенадцатый входы кода операции устройства подключены к входам разрешения выдачи регистров соответственно второй и третьей групп операционных блоков первой группы, тринадцатый и четырнадцатый входы кода операции устройства подключены к входам разрешения выдачи регистров соответственно пятой и шестой групп операционных блоков первой группы и регистров соответственно четвертой и пятой 5 групп операционных блоков второй группы

O

Фиг 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Вычислительное устройство в модулярной системе счисления | 1984 |

|

SU1244665A1 |

| Устройство для обнаружения и исправления ошибок в интервально-модулярном коде | 1988 |

|

SU1541784A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

Изобретение относится к вычислительной технике и предназначено для использования в высокоскоростных процессорах, базирующихся на алгоритмах типа Винограда. Цель изобретения - повышение быстродействия и расширение области применения за счет реализации преобразования для произвольного целого значения основания. Для достижения цели устройство содержит регистры 11./-14./, сумматоры 15./, 16./ по модулю ml, вычитатели 17./. 18/ по модулю ml, операционные блоки 19./, 20/, преобразователь 21 двоичного кода в модулярный и преобразователь 22 с масштабированием модулярного кода в двоичный. 1 табл 3 ил. с $ /

| Арифметическое устройство для процессоров быстрого преобразования Фурье | 1983 |

|

SU1116434A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-07—Публикация

1988-07-05—Подача