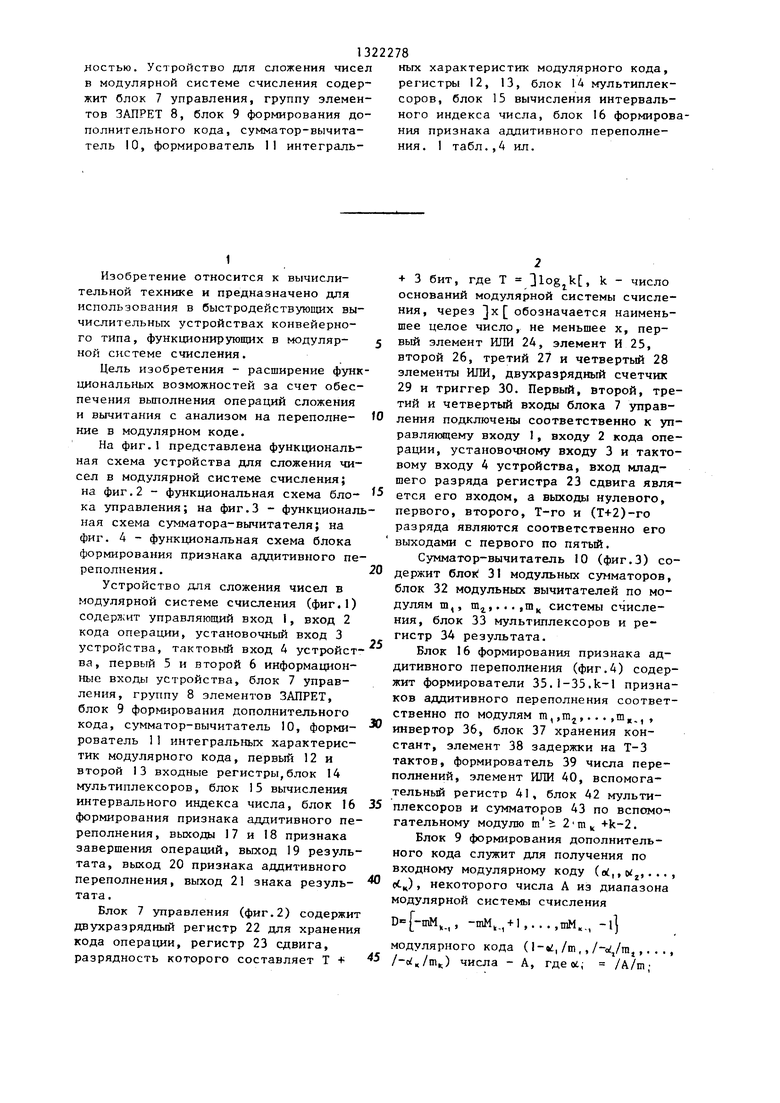

ocтью. Устройство для сложения чисел в модулярной системе счисления содержит блок 7 управления, группу элементов ЗАЛРЕТ 8, блок 9 формирования дополнительного кода, сумматор-вычита- тель 10, формирователь 11 интеграль1

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих вычислительных устройствах конвейерного типа, функционирующих в модуляр- ной системе счисления.

Цель изобретения - расширение функциональных возможностей за счет обеспечения выполнения операций сложения и вычитания с анализом на переполне- кие в модулярном коде.

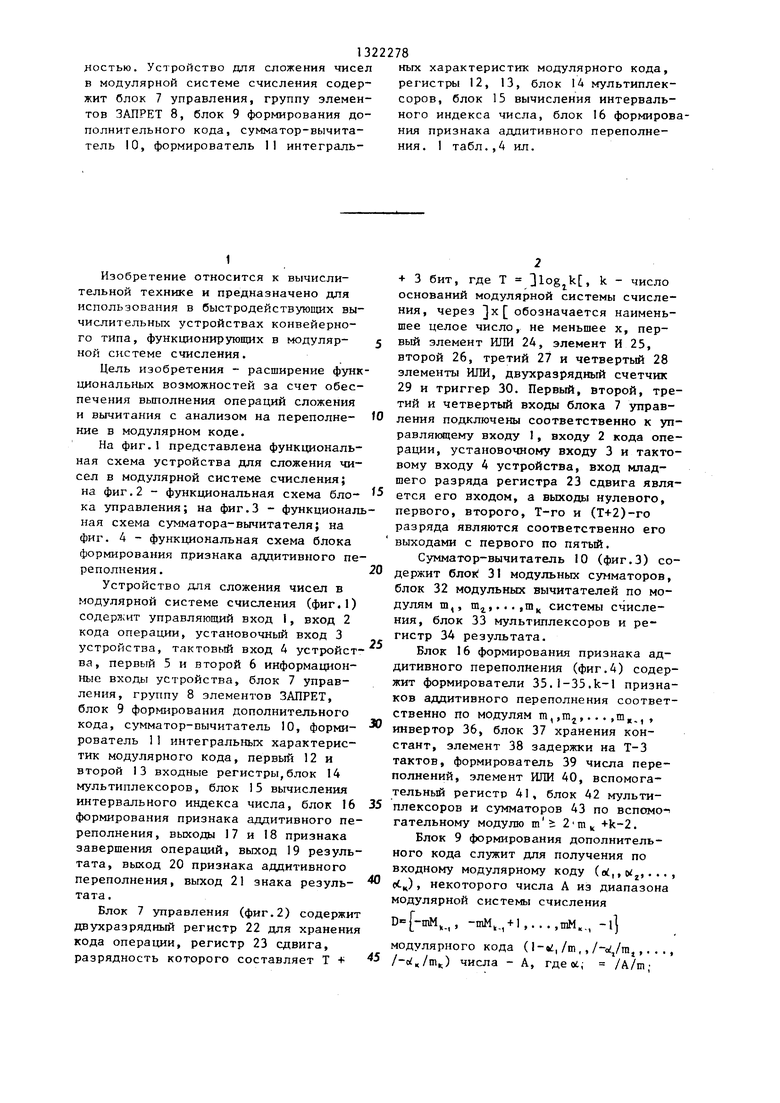

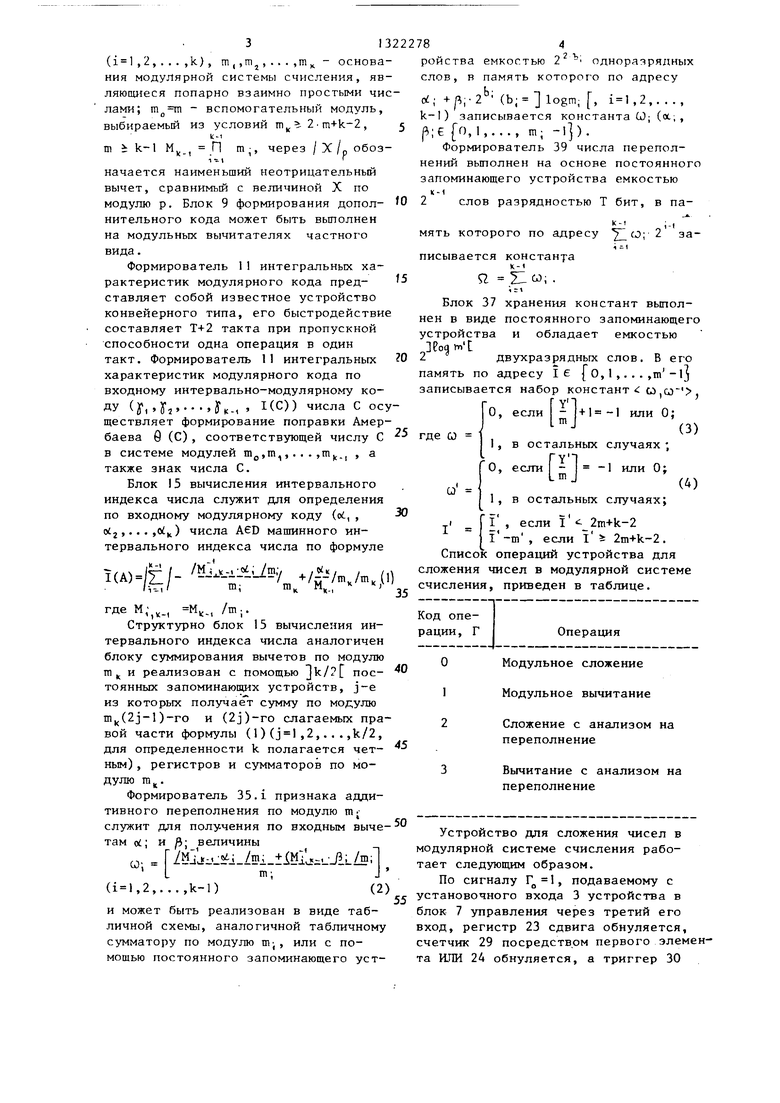

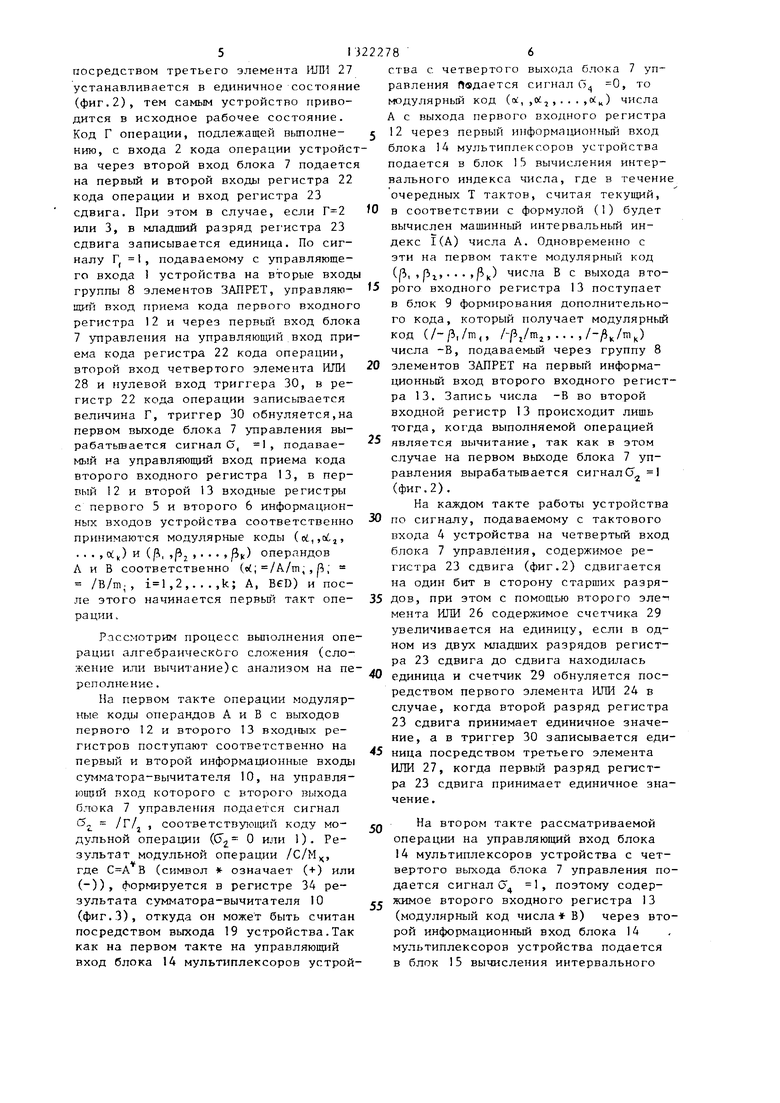

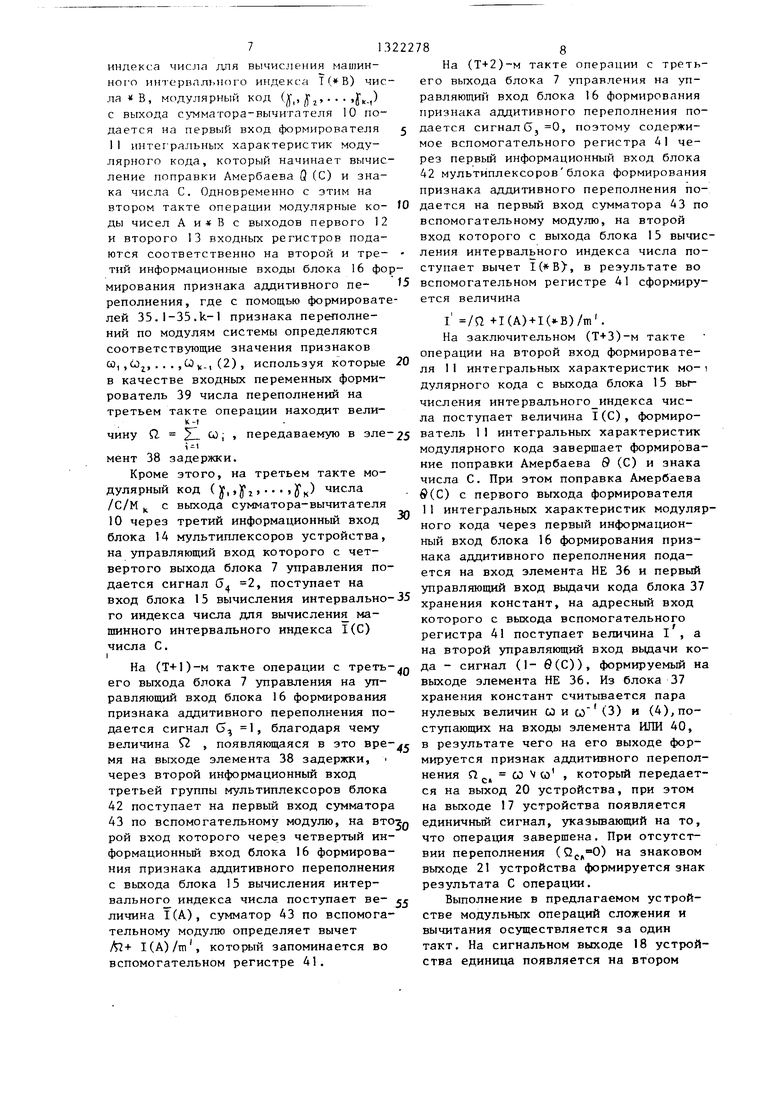

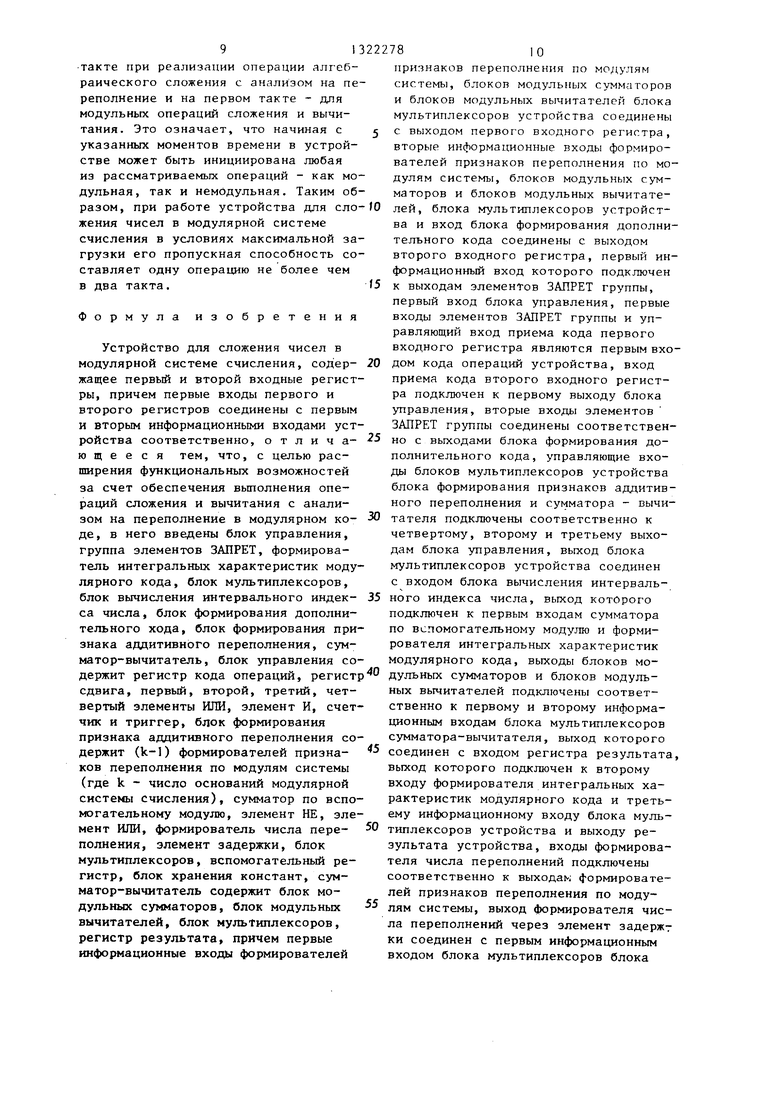

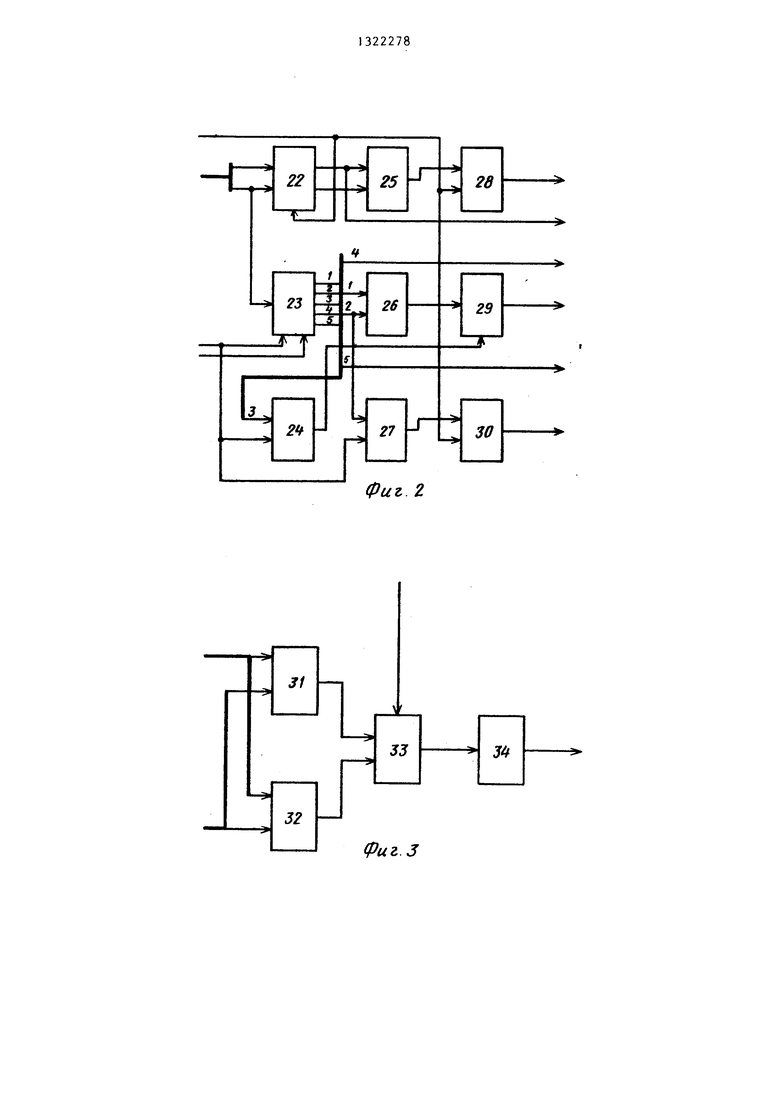

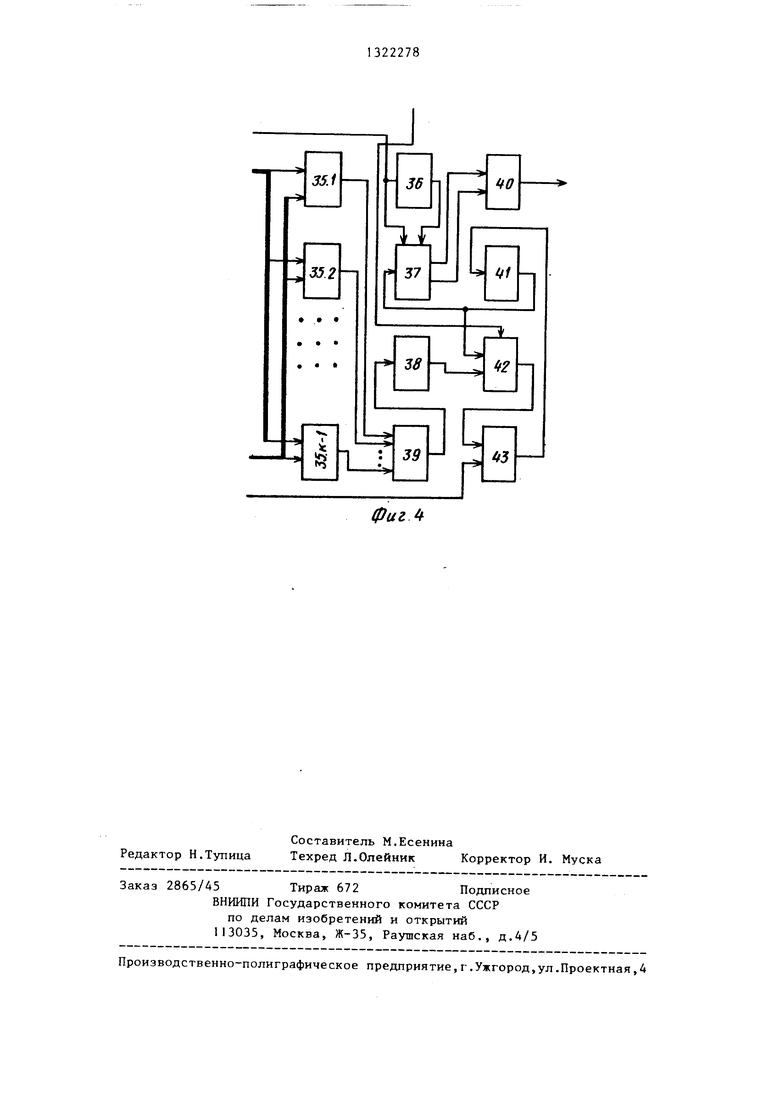

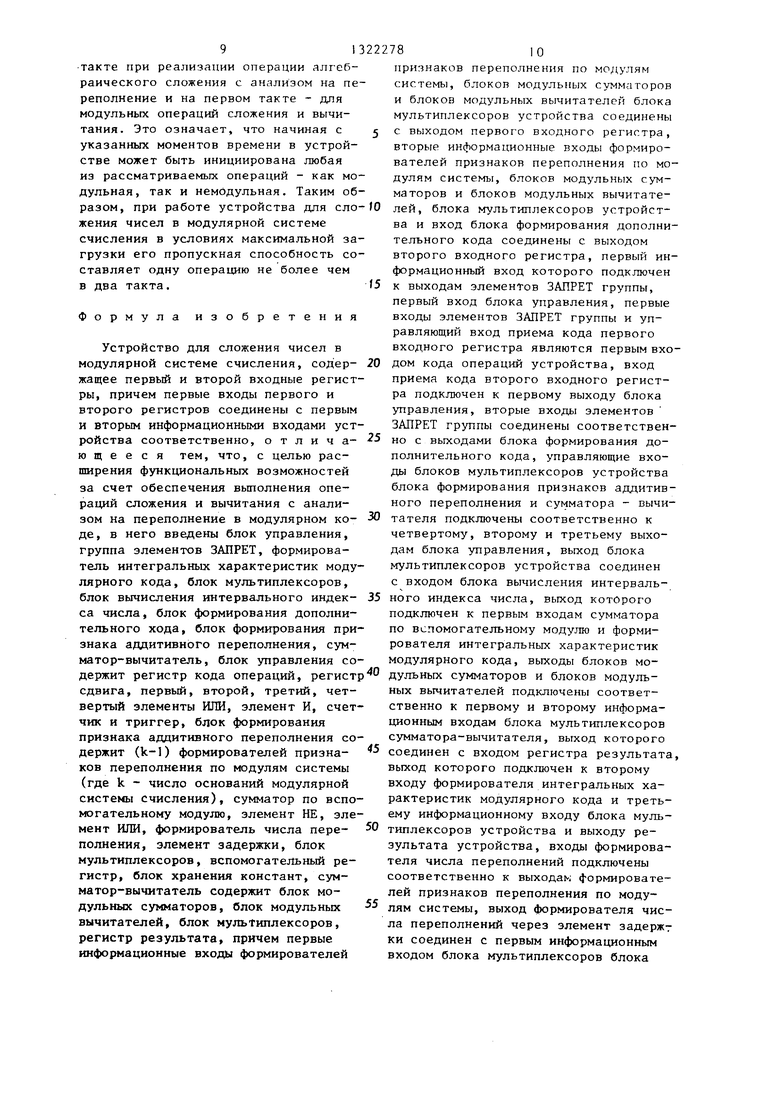

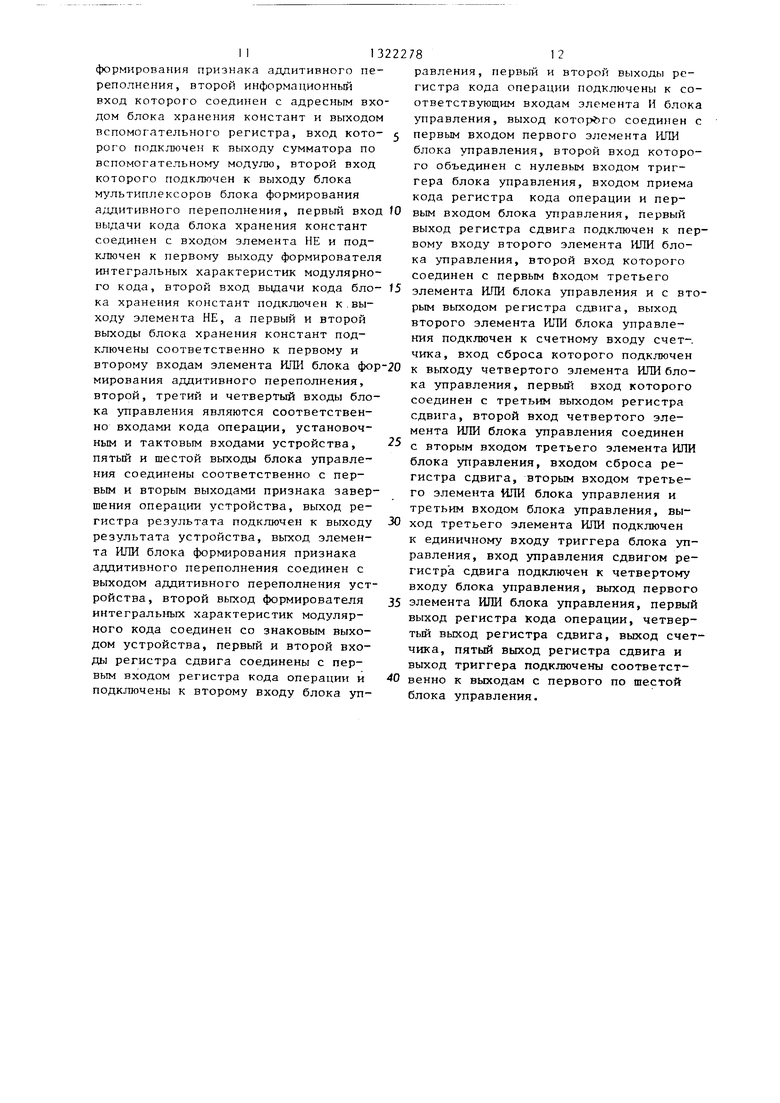

На фиг.1 представлена функциональная схема устройства для сложения чисел в модулярной системе счисления; на фиг.2 - функциональная схема бло- ка управления; на фиг.З - функциональная схема сумматора-вычитателя; на фиг. 4 - функциональная схема блока формирования признака аддитивного переполнения.

Устройство для сложения чисел в модулярной системе счисления (фиг.1) содержит управляющий вход 1, вход 2 кода операции, установочный вход 3 устройства, тактовый вход 4 устройства, первый 5 и второй 6 информационные входы устройства, блок 7 управления, группу 8 элементов ЗАПРЕТ, блок 9 формирования дополнительного кода, сумматор-вычитатель 10, форми- рователь 11 интегральных характеристик модулярного кода, первьй 12 и второй 13 входные регистры,блок 14 мультиплексоров, блок 15 вычисления интервального индекса числа, блок 16 формирования признака аддитивного переполнения, выходы 17 и 18 признака завершения операций, выход 19 результата, выход 20 признака аддитивного переполнения, выход 21 знака резуль- тата.

Блок 7 управления (фиг.2) содержит двухразрядный регистр 22 для хранения кода операции, регистр 23 сдвига, разрядность которого составляет Т -f

ных характеристик модулярного кода, регистры 12, 13, блок 1Д мультиплексоров, блок 15 вычисления интервального индекса числа, блок 16 формирования признака аддитивного переполнения. 1 табл.,4 ил.

О

0

5

5

+ 3 бит, где Т 3logj k, k - число оснований модулярной системы счисления, через JX обозначается наименьшее целое число, не меньшее х, первый элемент ИЛИ 24, элемент И 25, второй 26, третий 27 и четвертый 28 элементы ИЛИ, двухразрядный счетчик 29 и триггер 30. Первый, второй, третий и четвертый входы блока 7 управления подключены соответственно к управляющему входу I, входу 2 кода операции, установочному входу 3 и тактовому входу 4 устройства, вход младшего разряда регистра 23 сдвига является его входом, а выходы нулевого, первого, второго, Т-го и (Т+2)-го разряда являются соответственно его выходами с первого по пятый.

Сумматор-вычитатель 10 (фиг.З) содержит блок 31 модульных сумматоров, блок 32 модульных вычитателей по модулям т,, системы счисления, блок 33 мультиплексоров и ре гистр 34 результата.

Блок 16 формирования признака аддитивного переполнения (фиг.4) содержит формирователи 35.i-35.k-l признаков аддитивного переполнения соответственно по модулям т,,mj,...,т,, , инвертор 36, блок 37 хранения констант, элемент 38 задержки на Т-3 тактов, формирователь 39 числа переполнений, элемент ИЛИ 40, вспомогательный регистр 41, блок 42 мультиплексоров и сумматоров 43 по вспомо-i гательному модулю m Ь 2 m i-k-2.

Блок 9 формирования дополнительного кода служит для получения по входному модулярному коду (в(,, 6,. .. , ct), некоторого числа А из диапазона модулярной системы счисления

,., , -1пМ,, + 1,...,тМ,., -l)

модулярного кода (l-«i,/т,,,,. . ., ) числа - А, где oi; /А/ш;

(i 1 , 2, . . . ,k), m , ,m, .. . ,m 1 - основания модулярной системы счисления, яв- ляющлеся попарно взаимно простыми числами ; выбираемый из условий

Ь k-1

m

- вспомогательный модуль, т 2.m+k-2,

k-i

м.-, Л

1-t

m

через

/Х/р обоз

начается наименьший неотрицательный

вычет, сравнимый с величиной X по

модулю р. Блок 9 формирования допол-

нительного кода может быть вьтолнен

на модульных вычитателях частного

вида.

Формирователь 11 интегральных характеристик модулярного кода представляет собой известное устройство конвейерного типа, его быстродействи составляет 1+2 такта при пропускной способности одна операция в один такт. Формирователь 11 интегральных характеристик модулярного кода по входному интервально-модулярному ко- ДУ (у,, У,У., , КС)) числа С осществляет формирование поправки Амер баева Q (С), соответствующей числу С

,m

|c-l

в системе модулей m,m, также знак числа С.

Блок 15 вычисления интервального индекса числа служит для определения по входному модулярному коду (oi, , ,..,,ot) числа лев машинного интервального индекса числа по формуле

т/AN lv / /M i у-1-oi; /m;/ , / /

i(A)a:/- ------- -/jn /„- к/т./

и-1 i к K-i Д ,K-( Км /n iСтруктурно блок 15 вычисления интервального индекса числа аналогичен блоку суммирования вычетов по модулю га и реализован с помощью Jk/ постоянных запоминаюгаих устройств, j-e из которых получает сумму по модулю m(2j-l)-ro и (2j)-ro слагаемых правой части формулы (1)(,2,...,k/2, для определенности k полагается четным) , регистров и сумматоров по модулю т.

Формирователь 35.1 признака аддитивного переполнения по модулю Ш;- служит для получения по входным выче там oi; и ; величины

./I ± ±iMiU -JiL/mn

U-,

П ГУrSdJlrlMI

r/Mjj,2ii.

m;

,2,...,k-l)

и может быть реализован в виде табличной схемы, аналогичной табличному сумматору по модулю т, или с по- мошью постоянного запоминающего уст)2 Ъ;

ройства емкостью 2 одноразрядных слов, в память которого по адресу

Ы; +|,2 (Ь; logm, , ,2,. . ., k-I) записывается константа G); (оС; , 0,1,..., m; -l).

Формирователь 39 числа переполнений выполнен на основе постоянного запоминающего устройства емкостью

слов разрядностью Т бит, в па5

5

0

мять которого по адресу У1 со; 2 зал -1

писывается констан-ра

К-1

Q .

; г

Блок 37 хранения констант выполнен в виде постоянного запоминающего устройства и обладает емкостью

leoam t 2 двухразрядных слов. В его

память по адресу le { 0,1 ,. . . ,m -ij записывается набор констант : ci

fY l

0,если - или 0;

1,в остальных случаях ;

PY T О, если - -1 или 0:

Lm J

где о

Q

(3)

(4)

I, в остальных случаях; Г , если « 2m+k-2

i -m , если l i 2m+k-2. Список операций устройства для сложения чисел в модулярной системе счисления, приведен в таблице.

0Модульное сложение

1Модульное вычитание

2Сложение с анализом на переполнение

3Вычитание с анализом на переполнение

50

55

Устройство для сложения чисел в модулярной системе счисления работает следующим образом.

По сигналу , подаваемому с установочного входа 3 устройства в блок 7 управления через третий его вход, регистр 23 сдвига обнуляется, счетчик 29 посредством первого элемента ИЛИ 24 обнуляется, а триггер 30

посредством третьего элемента ИЛИ 27 устанавливается в единичное состояние (фиг.2), тем самым устройство приводится в исходное рабочее состояние. Код Г операции, подлежащей выполнению, с входа 2 кода операции устройства через второй вход блока 7 подается на первый и второй входы регистра 22 кода операции и вход регистра 23 сдвига. При этом в случае, если или 3, в младший разряд рег истра 23 сдвига записывается единица. По сигналу Г, 1 подаваемому с управляющего входа 1 устройства на вторые входы группы 8 элементов ЗАПРЕТ, управляю- цц-ш вход приема кода первого входного регистра 12 и через первый вход блока 7 управления на управляющий вход приема кода регистра 22 кода операции, второй вход четвертого элемента ИЛИ 28 и нулевой вход триггера 30, в регистр 22 кода операции записывается величина Г, триггер 30 обнуляется,на первом выходе блока 7 управления вы- рабатьшается сигнал G, 1, подаваемый на управляюпдш вход приема кода второго входного регистра 13, в первый 12 и второй 13 входные регистры с первого 5 и второго 6 информационных входов устройства соответственно принимаются модулярные коды (oil,,,, . . . ,(х:„) и (р, ,р., ,. . . ,ft) операндов Л и В соответственно (с(; /А/т, , ; /В/ш;, ,2,...,k; А, ВеВ) и после этого начинается первый такт опера ции,

Рассмотрим процесс вьтолнения операции алгебраического сложения (сложение или вычитание)с анализом на переполнение .

На первом такте операции модулярные коды операндов А и В с выходов первого 12 и второго 13 входных регистров поступают соответственно на первый и второй информационные входы сумматора-вычитателя 10, на управляющий вход которого с второго выхода блока 7 управления подается сигнал 2. соответствующий коду модульной операции (2, О или 1). Результат модульной операции /С/М, где В (символ означает ( + ) или (-)), формируется в регистре 34 результата сумматора-вычитателя 10 (фиг.З), откуда он может быть считан посредством выхода 19 устройства.Так как на первом такте на управляющий вход блока 14 мультиплексоров устрой

5

ства с четвертого выхода блока 7 управления Подается сигнал О 0, то модулярный код (oi, ,01: , . . . ,(/) числа А с выхода первого входного регистра 12 через первый и)1формапд1онный вход блока 14 мультиплексоров устройства подается в блок 15 вычисления интервального индекса числа, где в течение очередных Т тактов, считая текущий, в соответствии с формулой (1) будет вычислен машинный интервальный индекс 1(А) числа А. Одновременно с эти на первом такте модулярный код (А, , rij,. . . ,/ii) числа В с выхода второго входного регистра 13 поступает в блок 9 формирования дополнительного кода, который получает модулярный код (/-/i,/m,, /-/ij/iTij, .. . ,/-,/га) числа -В, подаваемый через группу 8 элементов ЗАПРЕТ на первьй информационный вход второго входного регистра 13. Запись числа -В во второй входной регистр 13 происходит лишь тогда, когда выполняемой операцией является вычитание, так как в этом случае на первом выходе блока 7 управления вырабатывается сигнал,,, (фиг.2).

На каждом такте работы устройства по сигналу, подаваемому с тактового входа 4 устройства на четвертый вход блока 7 управления, содержимое регистра 23 сдвига (фиг.2) сдвигается на один бит в сторону старших разря- 5 дов, при этом с помощью второго эле-1 мента ИЛИ 26 содержимое счетчика 29 увеличивается на единицу, если в одном из двух младших разрядов регистра 23 сдвига до сдвига находилась единица и счетчик 29 обнуляется посредством первого элемента ИЛИ 24 в случае, когда второй разряд регистра 23 сдвига принимает единичное значение, а в триггер 30 записывается единица посредством третьего элемента ИЛИ 27, когда первый разряд регистра 23 сдвига принимает единичное значение.

0

5

0

0

5

На втором такте рассматриваемой операции на управляющий вход блока 14 мультиплексоров устройства с четвертого выхода блока 7 управления подается сигнал (J 1, поэтому содержимое второго входного регистра 13 (модулярный код числа В) через второй информационный вход блока 14 мультиплексоров устройства подается в блок 15 вычисления интервального

fO

индекса числа для вычисления машинного интервллт.иого индекса 1(В) числа « В, модулярный код ((Ч ,,/fj, 4к-1 с выхода сумматора-вычитателя 10 подается на первый вход формирователя 1 I HHTer-paJTbHbix характеристик модулярного кода, который начинает вычисление поправки Амербаева Q (С) и знака числа С. Одновременно с этим на втором такте операции модулярные коды чисел А и В с выходов первого 12 и второго 13 входных регистров подаются соответственно на второй и тре- тли информационные входы блока 16 формирования признака аддитивного пе- 5 реполнения, где с помощью формирователей 35.l-35.k-l признака перелолне- ний по модулям системы определяются соответствующие значения признаков со, ,со, . . . ,О ., (2), используя которые 20 в качестве входных переменных формирователь 39 числа переполнений на

третьем такте операции находит вели11. -1 чину о, ы;

i-1

мент 38 задержки.

Кроме этого, на третьем такте модулярный код (y,yi. .У) числа /С/М с выхода сумматора-вычитателя 10 через третий информационный вход блока 14 мультиплексоров устройства, на управляющий вход которого с четвертого выхода блока 7 управления поНа (Т+2)-м такте операции с третьего выхода блока 7 управления на управляющий вход блока 16 формирования признака аддитивного переполнения по- 5 дается сигналGj 0, поэтому содержимое вспомогательного регистра АI через первый информационный вход блока 42 мультиплексоров блока формирования признака аддитивного переполнения подается на первьп вход сумматора 43 по вспомогательному модулю, на второй вход которого с выхода блока 15 вычисления интервального индекса числа поступает вычет IC-K-B), в результате во вспомогательном регистре 41 сформируется величина

I /а +I(A)+I(B)/m .

На заключительном ()-м такте операции на второй вход формирователя 11 интегральных характеристик моi дулярного кода с выхода блока 15 вычисления интервального индекса числа поступает величина 1(С), формиро30

передаваемую в эле-25 ватель 11 интегральных характеристик

модулярного кода завершает формирование поправки Амербаева Q (С) и знака числа С. При этом поправка Амербаева (С) с первого выхода формирователя 11 интегральных характеристик модулярного кода через первый информационный вход блока 16 формирования признака аддитивного переполнения подается на вход элемента НЕ 36 и первый управляющий вход выдачи кода блока 37 хранения констант, на адресный вход которого с выхода вспомогательного регистра 41 поступает величина I , а на второй управляющий вход вьщачи кода - сигнал (1- б(С)), формируемый на выходе элемента НЕ 36. Из блока 37 хранения констант считывается пара нулевых величин со и (3) и (4), поступающих на входы элемента ИЛИ 40, в результате чеГо на его выходе формируется признак аддитивного переполнения QJ., СО Vco , который передается на выход 20 устройства, при этом на выходе 17 устройства появляется

дается сигнал 6, 2, поступает на вход блока 15 вычисления интервально-35 го индекса числа для вычисления машинного интервального индекса 1{С)

числа С.

I

На (Т+1)-м такте операции с треть- д его выхода блока 7 управления на управляющий вход блока 16 формирования признака аддитивного переполнения подается сигнал G, 1, благодаря чему

, появляющаяся в это

величина Q

мя на выходе элемента 38 задержки, через второй информационный вход третьей группы мультиплексоров блока 42 поступает на первый вход сумматора

43 по вспомогательному модулю, на единичный сигнал, указьшающий на то.

рой вход которого через четвертый информационный вход блока 16 формирования признака аддитивного переполнения с выхода блока 15 вычисления интер- вального индекса числа поступает ве- « личина 1(А), сумматор 43 по вспомогательному модулю определяет вычет Л7+ I(A)/m , который запоминается во вспомогательном регистре 41.

что операция завершена. При отсутствии переполнения () на знаковом выходе 21 устройства формируется знак результата С операции.

Выполнение в предлагаемом устройстве модульных операций сложения и вычитания осуществляется за один такт. На сигнальном выходе 18 устройства единица появляется на втором

fO

50

22788

На (Т+2)-м такте операции с третьего выхода блока 7 управления на управляющий вход блока 16 формирования признака аддитивного переполнения по- 5 дается сигналGj 0, поэтому содержимое вспомогательного регистра АI через первый информационный вход блока 42 мультиплексоров блока формирования признака аддитивного переполнения подается на первьп вход сумматора 43 по вспомогательному модулю, на второй вход которого с выхода блока 15 вычисления интервального индекса числа поступает вычет IC-K-B), в результате во вспомогательном регистре 41 сформируется величина

I /а +I(A)+I(B)/m .

На заключительном ()-м такте операции на второй вход формирователя 11 интегральных характеристик модулярного кода с выхода блока 15 вычисления интервального индекса числа поступает величина 1(С), формиро30

что операция завершена. При отсутствии переполнения () на знаковом выходе 21 устройства формируется знак результата С операции.

Выполнение в предлагаемом устройстве модульных операций сложения и вычитания осуществляется за один такт. На сигнальном выходе 18 устройства единица появляется на втором

такте при реализации операции алгебраического сложения с анализом на переполнение и на первом такте - для модульных операций сложения и вычитания. Это означает, что начиная с указанных моментов времени в устройстве может быть инициирована любая из рассматриваемых операций - как модульная, так и немодульная. Таким образом, при работе устройства для ело-10 лей, блока мультиплексоров устройстжения чисел в модулярной системе счисления в условиях максимальной загрузки его пропускная способность составляет одну операцию не более чем в два такта.

Формула изобретения

Устройство для сложения чисел в модулярной системе счисления, содержащее первый и второй входные регистры, причем первые входы первого и второго регистров соединены с первым и вторым информационными входами устройства соответственно, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения выполнения операций сложения и вычитания с анализом на переполнение в модулярном коде, в него введены блок управления, группа элементов ЗАПРЕТ, формирователь интегральных характеристик моду30 тателя подключены соответственно к четвертому, второму и третьему выхо дам блока управления, выход блока мультиплексоров устройства соединен с входом блока вычисления интерваль

.40

лярного кода, блок мультиплексоров, блок вычисления интервального индек- 35 ного индекса числа, выход которого са числа, блок формирования дополни- подключен к первым входам сумматора тельного хода, блок формирования признака аддитивного переполнения, сум- матор-вычитатель, блок управления содержит регистр кода операций, регистр сдвига, первый, второй, третий, четвертый элементы ИЛИ, элемент И, счетчик и триггер, блок формирования признака аддитивного переполнения содержит (k-1) формирователей призна- ков переполнения по модулям системы (где k - число оснований модулярной CHCTehtti счисления), сумматор по вспомогательному модулю, элемент НЕ, элемент ИЛИ, формирователь числа пере- 0 полнения, элемент задержки, блок

по вспомогательному модулю и формирователя интегральных характеристик модулярного кода, выходы блоков модульных сумматоров и блоков модульных вычитателей подключены соответственно к первому и второму информационным входам блока мультиплексоров сумматора-вычитателя, выход которого соединен с входом регистра результат выход которого подключен к второму входу формирователя интегральных характеристик модулярного кода и треть ему информационному входу блока муль типлексоров устройства и выходу результата устройства, входы формирова теля числа переполнений подключены соответственно к выходам формировате лей признаков переполнения по моду- лям системы, выход формирователя чис ла переполнений через элемент задерж ки соединен с первым информационным входом блока мультиплексоров блока

мультиплексоров, вспомогательный регистр, блок хранения констант, сумма тор-вычитатель содержит блок модульных сумматоров, блок модульных вычитателей, блок мультиплексоров, регистр результата, причем первые информационные входы формирователей

признаков переполнения по модулям системы, блоков модульных сумматоров и блоков модульных вычитателей блока мультиплексоров устройства соединены с выходом первого входного регистра, вторые информационные входы формирователей признаков переполнения по модулям системы, блоков модульных сумматоров и блоков модульных вычитатева и вход блока формирования дополнительного кода соединены с выходом второго входного регистра, первый информационный вход которого подключен

к выходам элементов ЗАПРЕТ группы, первый вход блока управления, первые входы элементов ЗАПРЕТ группы и управляющий вход приема кода первого входного регистра являются первым входом кода операций устройства, вход приема кода второго входного регистра подключен к первому выходу блока управления, вторые входы элементов ЗАПРЕТ группы соединены соответственно с выходами блока формирования дополнительного кода, управляющие входы блоков мультиплексоров устройства блока формирования признаков аддитивного переполнения и сумматора - вычитателя подключены соответственно к четвертому, второму и третьему выходам блока управления, выход блока мультиплексоров устройства соединен с входом блока вычисления интервального индекса числа, выход которого подключен к первым входам сумматора

ного индекса числа, выход которого подключен к первым входам сумматора

по вспомогательному модулю и формирователя интегральных характеристик модулярного кода, выходы блоков модульных сумматоров и блоков модульных вычитателей подключены соответственно к первому и второму информационным входам блока мультиплексоров сумматора-вычитателя, выход которого соединен с входом регистра результата, выход которого подключен к второму входу формирователя интегральных характеристик модулярного кода и третьему информационному входу блока мультиплексоров устройства и выходу результата устройства, входы формирователя числа переполнений подключены соответственно к выходам формирователей признаков переполнения по моду- лям системы, выход формирователя числа переполнений через элемент задержт ки соединен с первым информационным входом блока мультиплексоров блока

II13

формирования признака аддитивного переполнения, второй информационный вход которого соеди}1ен с адресным входом блока хранения констант и выходом вспомогательног о регистра, вход кото- рого подключен к выходу сумматора по вспомогательному модулю, второй вход которого подключен к выходу блока мультиплексоров блока формирования аддитивного переполнения, первый вход выдачи кода блока хранения констант соединен с входом элемента НЕ и подключен к первоьгу выходу формирователя интегральных характеристик модулярного кода, второй вход выдачи кода бло- ка хранения констант подключен к.выходу элемента НЕ, а первый и второй выходы блока хранения констант подключены соответственно к первому и второму входам элемента ИЛИ блока фор мирования аддитивного переполнения, второй, третий и четвертый входы блока управления являются соответственно входами кода операции, установочным и тактовым входами устройства, пятый и шестой выходы блока управления соединены соответственно с первым и вторым выходами признака завершения операции устройства, выход регистра результата подключен к выходу результата устройства, выход элемента ИЛИ блока формирования признака аддитивного переполнения соединен с выходом аддитивного переполнения устройства, второй выход формирователя интегральных характеристик модулярного кода соединен со знаковым выходом устройства, первый и второй входы регистра сдвига соединены с первым входом регистра кода операции и подключены к второму входу блока уп7812

равления, первый и второй выходы регистра кода операции подключены к соответствующим входам элемента И блока управления, выход которого соединен с первым входом первого элемента ИЛИ блока управления, второй вход которого объединен с нулевым входом триггера блока управления, входом приема кода регистра кода операции и первым входом блока управления, первый выход регистра сдвига подключен к первому входу второго элемента ИЛИ блока управления, второй вход которого соединен с первым Входом третьего элемента ИЛИ блока управления и с вторым выходом регистра сдвига, выход второго элемента ИЛИ блока управления подключен к счетному входу счет-. чика, вход сброса которого подключен к выходу четвертого элемента ИЛИ блока управления, первый вход которого соединен с третьим выходом регистра сдвига, второй вход четвертого элемента ИЛИ блока управления соединен с вторым входом третьего элемента ИЛИ блока управления, входом сброса регистра сдвига, вторым входом третьего элемента ИЛИ блока управления и третьим входом блока управления, выход третьего элемента ИЛИ подключен к единичному входу триггера блока управления, вход управления сдвигом регистра сдвига подключен к четвертому входу блока управления, выход первого элемента ШШ блока управления, первый выход регистра кода операции, четвертый выход регистра сдвига, выход счетчика, пятый выход регистра сдвига и выход триггера подключены соответственно к выходам с первого по шестой блока управления.

rtU

Фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в системе остаточных классов | 1983 |

|

SU1149254A1 |

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих вычислительных устройствах коивейер- ного типа, функционирующих в модулярной системе счисления. Цель изобретения - расширение функциональных возможностей за счет обеспечения выполнения операций сложения и вычитания с анализом на переполнение в модулярном коде, благодаря чему устройство может быть использовано для реализации в конвейерном режиме не только вычислительных процессов, отличающихся немодульностью, но и процессов, обладающих высокой модульс в (Л Altl

Фиг 3

Редактор Н.Тупица

Составитель М.Есенина

Техред Л.Олейник Корректор И. Муска

Заказ 2865/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4

фиг Л

Авторы

Даты

1987-07-07—Публикация

1986-02-20—Подача