Изобретение относится к вычислительной технике и предназначено для использования в быстродействукщих специализ1фованных вычислительных системах конвейерного типа, функционирующих в модулярной системе счисления .

Цель изобретения - расширение области применения за счет обработки операндов,, представленных в форме с плавающей запятой.

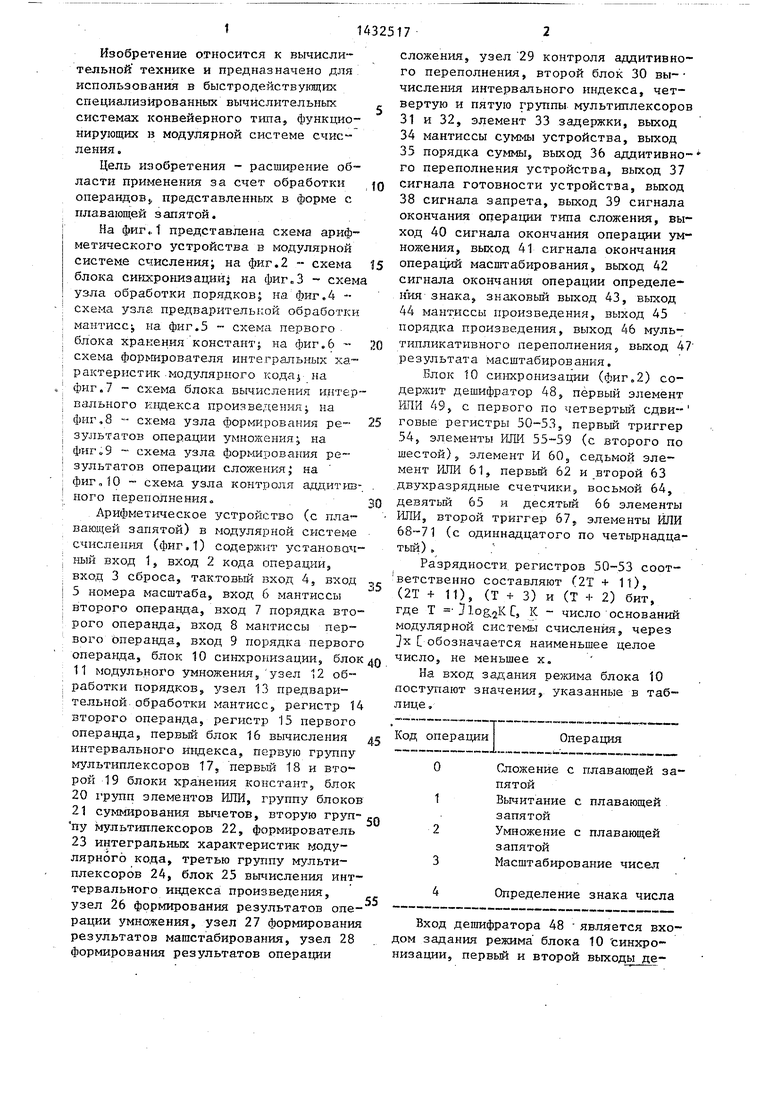

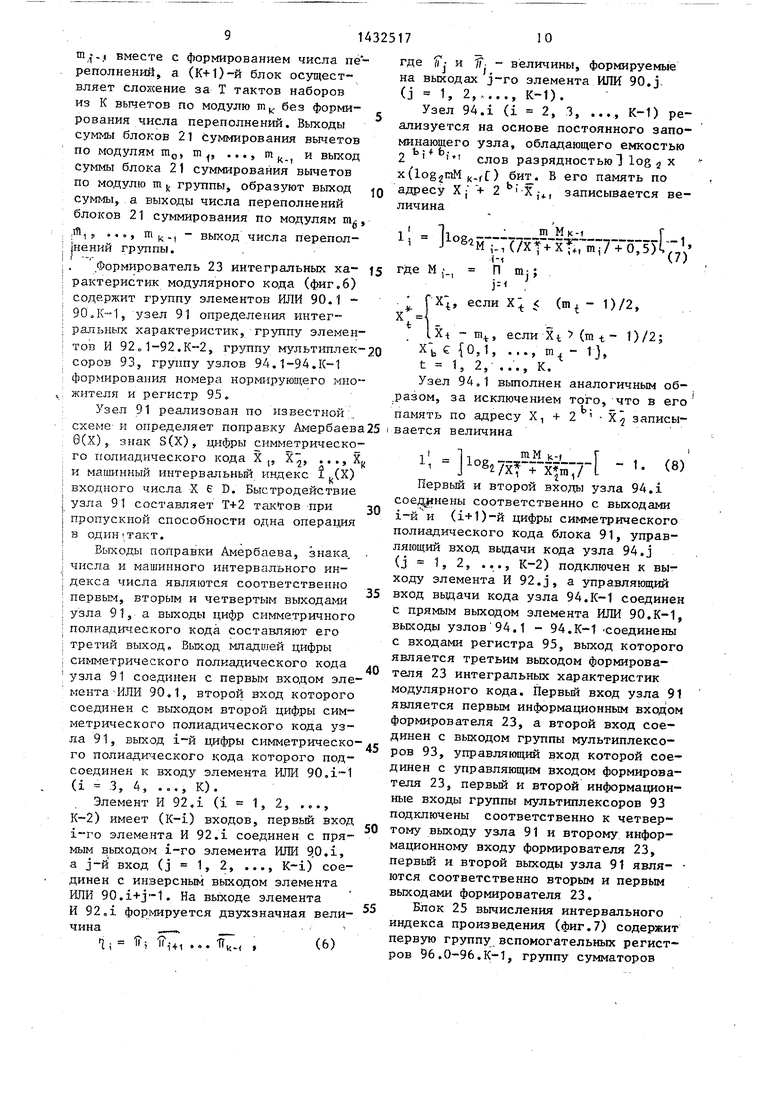

На фиг., t представлена схема арифметического устройства в модулярной системе счисления; на фиг.2 - схема блока синггронизаций- на фиг.З схема I узла обработки порядков на фиг,4 - ; схема узла предварительной обработки ; мантисс на фиг.5 - схема первого I блока хранения константу на фиг,6 - : схема фop tиpoвaтeля интегральных ха™ : рактеристик .модулярного кода на

фиг,7 схема блока вычисления интер- : Бального кгщекса произведенияj на

; фиг .,8 схема узла формкрования

I зультатов операции умножения на

: фиг„9 - схема узла формирования ре™

; зультатов операции сложения; на

; фиг „10 - схема узла контроля аддитрш-.

: ного переполнения,. .

Арифметическое устройство (с пла вающей запятой) в модулярной системе счислен{-ш (фиг,1) содержит установоч : вход 1, вход 2 кода операции, : вхо,ц 3 сброса, так.товый вход 4, вхо,ц ; 5 номера масштаба, вход 6 мантиссы : второго операнд:а, вход 7 порядка второго операнда, вход 8 мантиссы пер- вого Операнда, вход 9 порядка первого операвда, блок 10 синхронизации, блок

; 11 модульного умножения, узел 12 об-- ; работки порядков, узел 13 предварительной.обработки мантисс, регистр 14 второго операнда, регистр 15 первого операнда, первьй блок 16 вычисления интервального ивдекса, первую мультиплексоров 17, первый 18 и второй 19 блоки хранетшя констант, блок

20групп элементов ИЛИ, группу блоков

21суммирования вьпштов, вторую груп пу мультга1.пексоров 22, формировате.ль

23 интегральных характеристик модулярного ко,ца, третью группу мультиплексоров 24, блок 25 вычисления инт- тервального индекса произведения, узел 26 формирования результатов операции умножения, узел 27 формирования результатов машстабирования, узел 28 формирования результатов операции

сложения, узел 29 контроля аддитивного переполнения, второй блок 30 вы- числения интервального индекса, четвертую и пятую группы мультиплексоров 31 и 32, элемент 33 задержки, выход

34мантиссы суммы устройства, выход

35порядка суммы, выход 36 аддитивного переполнения устройства, выход 37 сигнала готовности устройства, выход 38 сигнала запрета, выход 39 сигнала окончания операции типа сложения, вы ход 40 сигнала окончания операции умножения, выход 41 сигнала окончания операций масштабирования, выход 42 сигнала окончания операции определения знака, знаковый выход 43, выход 44 мантиссы произведения, выход 45 порядка произведения, выход 46 мультипликативного переполнения, 4 результата масштабирования,

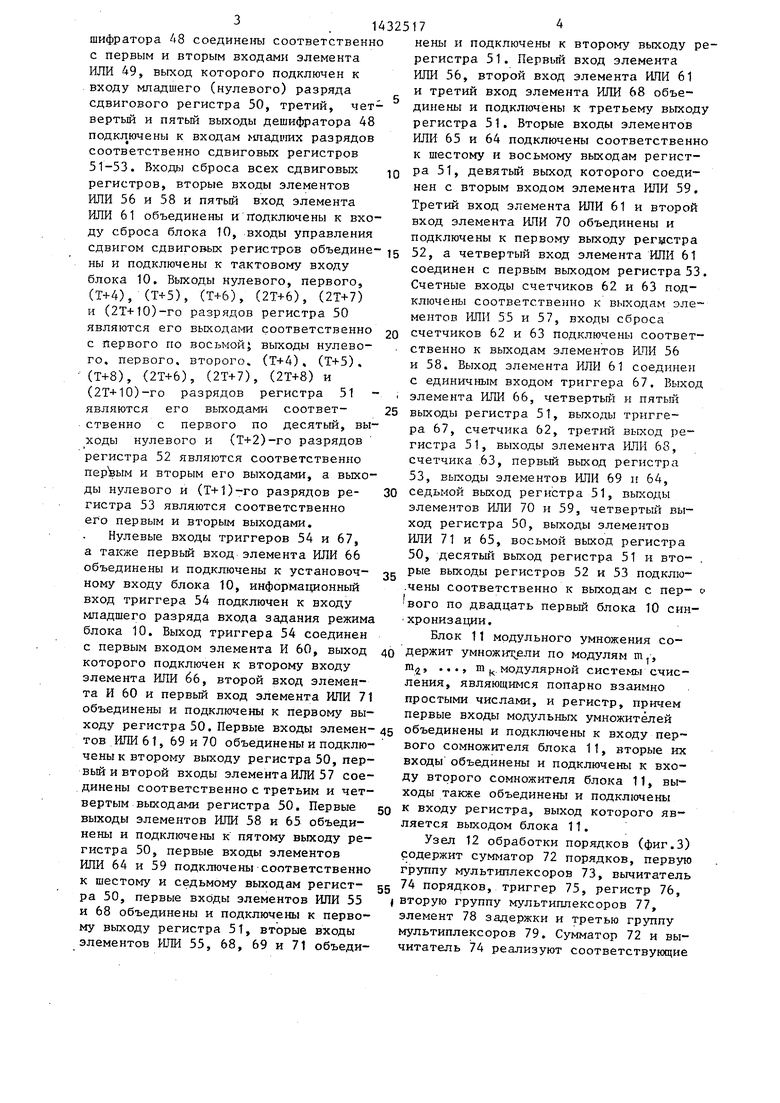

.Блок 10 синхронизации (фиг.2) содержит дешифратор 48, первый элемент ИПИ 49, с первого по четвертый сдвигоБые регистры 50-53, первьй триггер 54, элементы ИШ1 55-59 (с второго по шестой), элемент И 60, седьмой элемент ШШ 61, первый 62 и второй 63 .двухразрядные счетчики, восьмой 64, девятый 65 и десятый 66 элементы ИЛИ, второй триггер 67, элементы ШШ 68-71 (с одиннадцатого по четьфнадца- тьш) .

Разрядности, регистров 50-53 соот- ветственно составляют (2Т + 11), 2Т + 11), (Т + 3) и (Т -I- 2) бит, где Т -7log./jKC, К - число оснований модулярной системы счисления, через х С обозначается наименьшее целое число, не меньшее х.

На вход задания блока 10 поступают значения, указанные в таблице ,

од операции О 1 2 3

Операция

Сложение с плавающей запятой

Вычитание с плавающей запятой

Умножение с плавающей запятой Масштабирование чисел

Определение знака числа

Вход дешифратора 48 яв,пяется вхо дом задания режима блока 10 синхронизации, первьй и второй выходы дешифратора 48 соедине1л 1 соответственно с первым и вторым входами элемента ИЛИ 49, выход которого подключен к входу младшего (нулевого) разряда сдвигового регистра 50, третий, чет- вертьй и пятый выходы дешифратора 48 подключены к входам шадишх разрядов соответственно сдвиговых регистров 51-53. Входы сброса всех сдвиговых регистров, вторые входы элементов ИЛИ 56 и 58 и пятый вход элемента РШИ 61 объединены и подключены к входу сброса блока 10, входы управления

нены и подключены к второму выходу ре- регистра 51. Первьй вход элемента ИЛИ 56, второй вход элемента ИЛИ 61 и третий вход элемента ИЛИ 68 объединены и подключены к третьему выходу регистра 51. Вторые входы элементов ИЛИ 65 и 64 подключены соответственно к шестому и восьмому выходам регистра 51, девятый выход которого соединен с вторым входом элемента ИЛИ 59. Третий вход элемента ИЛИ 61 и второй вход элемента ИЛИ 70 объединены и подключены к первому выходу регистра

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для нормализации чисел в модулярной системе счисления | 1986 |

|

SU1332317A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для нормализации чисел в модулярном коде | 1984 |

|

SU1242942A1 |

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих специализированных вычислительных системах конвейерного типа, функционирующих в модулярной системе счисления . Целью изобретения является расширение области применения за счет обработки операндов, представленных в форме с плавающей запятой. Поставленная цель достигается тем, что в арифметическое устройство в модулярной системе счисления, содержащее блок 10 синхронизации, блок 11 модульного умножения, узел 13 предварительной обработки мантисс, регистры 14 и 15 второго и первого операндов., блок 16 вычисления интервального индекса, группы мультиплексоров 17, 22 и 24, блоки 18, 19 хранения констант, блок 20 групп элементов ИЛИ, группу блоков 21 суммирования вычетов, формирователь 23 интегральных характеристик модулярного кода, блок 25 вычисления интервального индекса произведения, узел 26 формирования результатов операции умножения, узел 27 формирования результатов масштабирования, узел.28 формирования результатов операции сложения и элемент 33 задержки, введены узел 12 обработки порядков, узел 29 контроля аддитивного переполнения, блок 30 вычисления интервального индекса и группы 31,, 32 мультиплексоров с соответствующими связями. 10 шт., 1 табл. Ф 4 СО N СП

сдвигом сдвиговых регистров объедине- 5 52, а четвертый вход элемента ИЛИ 61

20

ны и подключены к тактовому входу блока 10. Выходы нулевого, первого, (Т+4), (Т+5), (T-t-6), (2Т+6), (2Т+7) и (2Т+10)-го разрядов регистра 50 являются его выходами соответственно с первого по восьмой выходы нулевого, первого, второго. (Т+4), (Т+5), (Т+8), (2Т+6), (2Т+7), (2Т+8) и (2Т+10)-го разрядов регистра 51 - , являются его выходами соответ- 25 ственно с первого по десятый, выходы нулевого и (Т+2)-го разрядов регистра 52 являются соответственно первым и вторым его выходами, а выходы нулевого и (Т+1)-го разрядов регистра 53 являются соответственно его первым и вторым выходами.

Нулевые входы триггеров 54 и 67, а также первый вход элемента ИЛИ 66 объединены и подключены к установочному входу блока 10, информационный вход триггера 54 подключен к входу младшего разряда входа задания режима блока 10. Выход триггера 54 соединен с первым входом элемента И 60, выход которого подключен к второму входу элемента Ш1И 6б, второй вход элемента И 60 и первьй вход элемента ИЛИ 71 объединены и подключены к первому вы40

30

35

ходу регистра 50. Первые входы элемен-45 объединены и подключены к входу пертон ИЛИ 61, 69 и 70 объединены и подключены к второму выходу регистра 50, первьй и второй входы элементаИЛИ 57 соединены соответственно с третьим и четвертым выходами регистра 50. Первые go выходы элементов ИЛИ 58 и 65 объединены и подключены к пятому выходу регистра 50, первые входы элементов

вого сомножителя блока 11, вторые их входы объединены и подключены к входу второго сомножителя блока 11, выходы также объединены и подключены к входу регистра, выход которого является выходом блока 11.

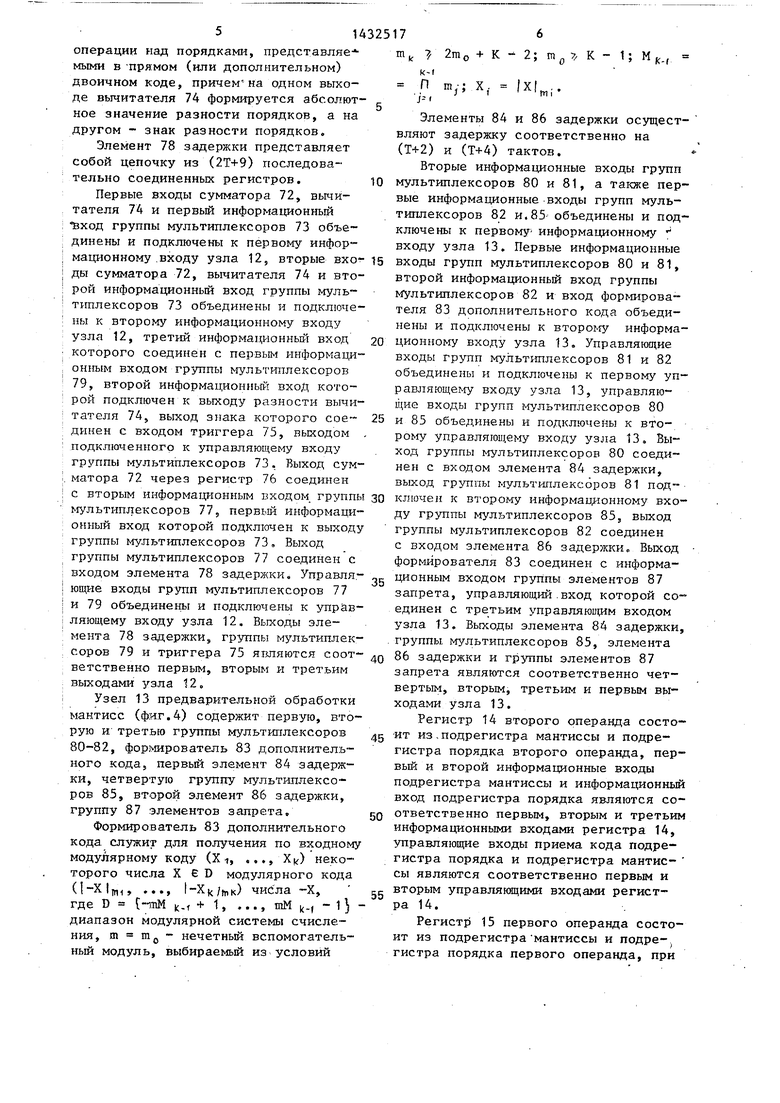

Узел 12 обработки порядков (фиг.З) родержит сумматор 72 порядков, первую группу мультиплексоров 73, вычитатель

Узел 12 обработки порядков (фиг.З) родержит сумматор 72 порядков, первую группу мультиплексоров 73, вычитатель

ИЛИ 64 и 59 подключены соответственно

к шестому и седьмому выходам регист- 55 порядков, триггер 75, регистр 76, ра 50, первые входы элементов ИЛИ 55 | вторую группу мультиплексоров 77, и 68 объединены и подключены к перво- элемент 78 задержки и третью группу му выходу регистра 51, вторые входы мультиплексоров 79. Сумматор 72 и вы- элементов ИЛИ 55, 68, 69 и 71 объеди- читатель 74 реализуют соответствующие

0

, 5

соединен с первым вькодом регистра 53. Счетные входы счетчиков 62 и 63 подключены соответственно к выходам элементов 11ЛИ 55 и 57, входы сброса счетчиков 62 и 63 подключены соответственно к выходам элементов ЕПИ 56 и 58. Выход элемента ИЛИ 61 соединен с единичным входом триггера 67. Выход элемента ИЛИ 66, четвертьй и пятьш выходы регистра 51, выходы триггера 67, счетчика 62, третий выход регистра 51, выходы элемента ИЛИ 68, счетчика .63, первьй выход регистра 53, выходы элементов ИЛИ 69 и 64, седьмой выход регистра 51, выходы элементов РШИ 70 и 59, четвертьцг выход регистра 50, выходы элементов ИЛИ 71 и 65, восьмой выход регистра 50, десятый выход регистра 51 и вто- . рые выходы регистров 52 и 53 подклю- .чены соответственно к выходам с пер- с. вого по двадцать первый блока 10 син- хронизации.

Блок 11 модульного умножения со- 0 держит умножш;ели по модулям т,,

т, ..., m ц., модулярной системы счисления, являющимся попарно взаимно простыми числами, и регистр, причем первые входы модульных умножителей

0

5

вого сомножителя блока 11, вторые их входы объединены и подключены к входу второго сомножителя блока 11, выходы также объединены и подключены к входу регистра, выход которого является выходом блока 11.

Узел 12 обработки порядков (фиг.З) родержит сумматор 72 порядков, первую группу мультиплексоров 73, вычитатель

порядков, триггер 75, регистр 76, вторую группу мультиплексоров 77, элемент 78 задержки и третью группу мультиплексоров 79. Сумматор 72 и вы- читатель 74 реализуют соответствующие

51432517

операции над порядками, представляв в -прямом (или дополнительном) двоичном коде, причем на одном выходе вычитателя 74 формируется абсолют- ..

3

нов значение разности порядков, а на другом - знак разности порядков.

Элемент 78 задержки представляет собой цепочку из (2Т+9) последовательно соединенных регистров, to

Первые входы сумматора 72, вычитателя 74 и первый информационный вход группы мультиплексоров 73 объединены и подключены к первому инфорo+K-2;m 7, К-1; М ., Х(.

ml

m, 2га

k-i

П т.; X,. Я

Элементы 84 и 86 задержки осуществляют задержку соответственно на (Т+2) и (Т+4) тактов.

Вторые информационные входы групп мультиплексоров ВО и 81, а также первые информационные входы групп мультиплексоров 82 и.85 объединены и подключены к первому информационному

входу узла 13. Первые информационные мационному .входу узла 12, вторые вхо- 15 входы групп мультиплексоров 80 и 81, ; ДБ1 сумматора 72, вычитателя 74 и вто- второй информационный вход группы ; рой информационный вход группы муль- мультиплексоров 82 и вход формирова- типлексоров 73 объединены и подключе- теля 83 дополнительного кода объеди- : ны К второму информационному входу иены и подключены к BTopoi-iy информаузла 12, третий информащонный вход 20 ционному входу узла 13. Управляющие : которого соединен с первым информаци™

; онным входом группы ryльтиплeкcopoв

79, второй информационный вход кото

: рой подключен к выходу разности вычитателя 74, выкод знака которого сое: динен с входом триггера 75, выходом .

входы групп мультиплексоров 81 и 82 объединены и подключены к первому управляющему входу узла 13, управляющие входы групп мультиплексоров 80 25 и 85 объединены и подключены к второму управляющему входу узла 13. Вы подключенного к управляющему входу , ход группы мультиплексоров 80 соеди- группы мультиплексоров 73. Выход сум- нен с входом элемента 84 задержки,

;. матора 72 через регистр 76 соединен выход группы мультиплексоров 81 под™

: с вторым информационным входом группы 30 ключей к второму информационному вхо- мультиплексоров 77, первый информаци- ду группы мультиплексоров 85, выход

: онный вход которой подключен к выходу группы мультиплексоров 82 соединен группы мультиплексоров 73, Выход с входом элемента 86 задержки. Выход группы мультиплексоров 77 соединен с формирователя 83 соединен с информа; входом элемента 78 задержки. Управля- д ционным входом группы элементов 87

i ющие входы групп мультиплексоров 77...

и 79 объединены и подключены к упрйв: ляющему входу узла 12. Выходы эле, мента 78 задержки, группы мультиплек-

; соров 79 и триггера 75 являются соот- о 86 задержки и группы элементов 87 ветственно первым, вторым и третьим запрета являются соответственно чет- Bbtxодами узла 12.

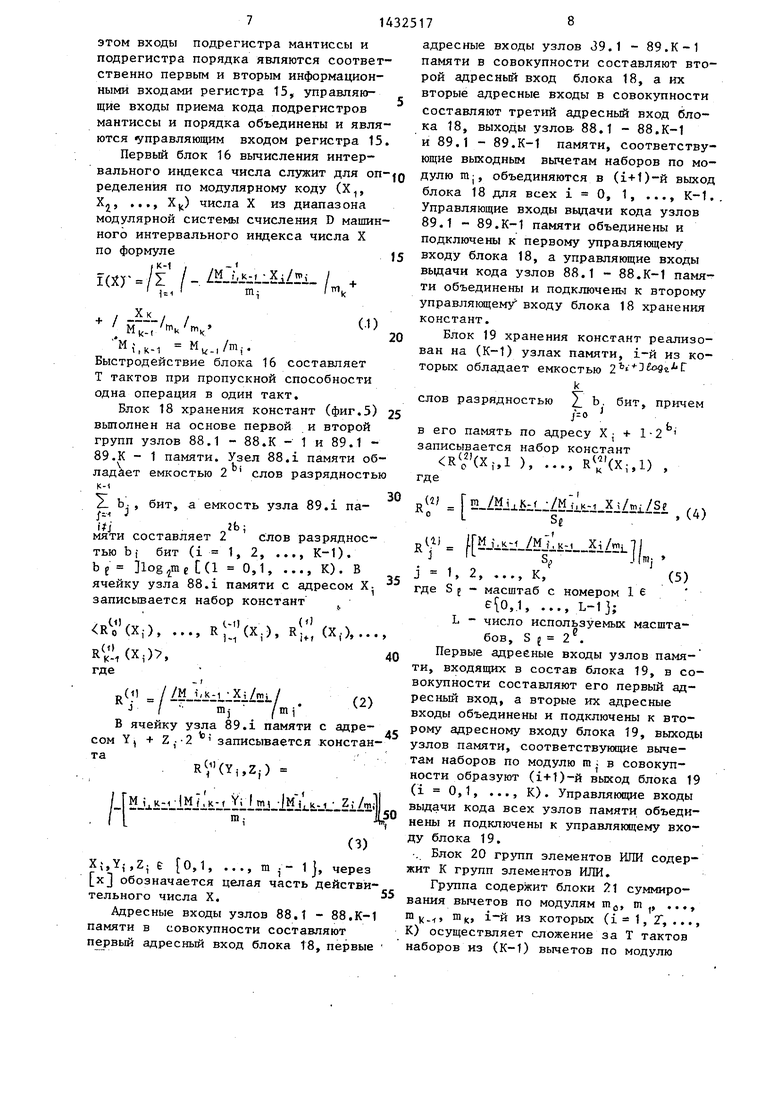

Узел 13 предварительной обработки мантисс (фиг.4) содержит первую, вторую И третью группы мультиплексоров 80-82, фор 1ирователь 83 дополнительного кода, первый элемент 84 задержки, четвертую группу ryльтиплeкco запрета, управляющий.вход которой соединен с третьим управляющим входом узла 13. Вьгкоды элемента 84 задержки, группы мультиплексоров 85, элемента

вертым, вторым, третьим и первым выходами узла 13.

Регистр 14 второго операнда состо45 Ит из-подрегистра мантиссы и подре- гистра порядка второго операнда, первый и второй информационные входы подрегистра мантиссы и информационный вход подрегистра порядка являются соров 85, второй элемент 86 задержки, группу 87 .элементов запрета.

Формирователь 83 дополнительного кода служит для получения по входному модулярному коду (X1, ..,, Х|) некоторого числа X е D модулярного кода (I-XIm, ..., 1-Хк/)пк) числа -X, где D f-iuM K.t + 1, ..., uiM k., - 1 } - диапазон модулярной системы счисления, m Шд - нечетньй вспомогательный модуль, выбираемьй из условий

o+K-2;m 7, К-1; М ., Х(.

ml

m, 2га

k-i

П т.; X,. Я

Элементы 84 и 86 задержки осуществляют задержку соответственно на (Т+2) и (Т+4) тактов.

Вторые информационные входы групп мультиплексоров ВО и 81, а также первые информационные входы групп мультиплексоров 82 и.85 объединены и подключены к первому информационному

ционному входу узла 13. Управляющие

входы групп мультиплексоров 81 и 82 объединены и подключены к первому управляющему входу узла 13, управляющие входы групп мультиплексоров 80 и 85 объединены и подключены к второму управляющему входу узла 13. Вы...

запрета, управляющий.вход которой соединен с третьим управляющим входом узла 13. Вьгкоды элемента 84 задержки, группы мультиплексоров 85, элемента

86 задержки и группы элементов 87 запрета являются соответственно чет-

вертым, вторым, третьим и первым выходами узла 13.

Регистр 14 второго операнда состо Ит из-подрегистра мантиссы и подре- гистра порядка второго операнда, первый и второй информационные входы подрегистра мантиссы и информационный вход подрегистра порядка являются соответственно первым, вторым и третьим информационными входами регистра 14, управляющие входы приема кода подрегистра порядка и подрегистра мантис- сы являются соответственно первым и вторым управляющими входами регистра 14.

Регистр 15 первого операнда состоит из подрегистра мантиссы и подрегистра порядка первого операнда, при

этом входы подрегистра мантиссы и подрегистра порядка являются соответственно первым и вторым информационными входами регистра 15, управляю- щие входы приема кода подрегистров мантиссы и порядка объединены и являются «управляющим входом регистра 15.

Первый блок 16 вычисления интервального индекса числа служит для onределения по модулярному коду (Х, X,, ..., Х) числа X из диапазона модулярной системы счисления D машинного интервального индекса числа X по формуле

iK-1

,/,/./«:ь....х./..../„.

Хк

(1)

20

J. / / M(,.,/Wk/m

,к-1 M,.,/mj. Быстродействие блока 16 составляет Т тактов при пропускной способности одна операция в одий такт.

Блок 18 хранения констант (фиг.5) 25 выполнен на основе первой и второй групп узлов 88.1 - 88.К - 1 и 89.1 - 89.К - 1 памяти. Узел 88.1 памяти об- емкостью 2 слов разрядностью

I Ь. , бит, а емкость узла 89.1 па- S-/MdabL

;- ., s«

МЯТИ составляет 2 слов разрядностью b,- бит (1 1, 2, ..., К-1). be (1 0,1, ..., К). В ячейку узла 88.1 памяти с адресом X. записывается набор констант ,j

о (Xf ) , .. , R j (Xj) , R (Xf ), кУм(Х,).

40

R) ...Xi/.Lj| ,

j 1, 2, ..., K/(5)

где S f - масштаб с номером 1 в

,.1, ..., L-lj; L - число используемых масштабов, S j 2 .

Первые адрееные входы узлов памя- ти, входящих в состав блока 19, в совокупности составляют его первый адресный вход, а вторые их адресные входы объединены и подключены к второму адресному входу блока 19, выходы узлов памяти, соответствующие вычетам наборов по модулю m ; в совокупности образуют (1+1)-и выход блока 19 (1 0,1, ..., К). Управляющие входы выдачи кода всех узлов памяти объединены и подключены к управляющему входу блока 19.

где

- ;

,

mj

/mj

в ячейку узла 89.1 памяти сом Y, + Z,.-2 записывается RV (Yi Zi)

.. J--i-i-2 -5-i-Jj-s..н

Го;

(3)

XJ,Y,-,Z. е 0,1, ..., т|- 1, через х обозначается целая часть действительного числа X.

Адресные входы узлов 88.1 - 88.К-1 памяти в совокупности составляют первый адресный вход блока 18, первые

|QJ5

20

25

адресные входы узлов 39.1 - 89.К-1 памяти в совокупности составляют второй адресньй вход блока 18, а их вторые адресные входы в совокупности составляют третий адресный вход блока 18, выходы узлов- 88.1 - 88.К-1 и 89.1 - 89.К-1 памяти, соответствующие выходным вычетам наборов по модулю fflj, объединяются в (1+1)-й выход блока 18 для всех , 1, ..., К-1.. Управляющие входы вьщачи кода узлов 89.1 - 89.К-1 памяти объединены и подключены к первому управляющему входу блока 18, а управляющие входы выдачи кода узлов 88.1 - 88.К-1 памяти объединены и подключены к второму управлякицему входу блока 18 хранения констант.

Блок 19 хранения констант реализован на (К-1) узлах памяти, 1-й из которых обладает емкостью 2 Зго4г Г

k слов разрядностью 1 Ь. бит, причем

0

Ь;

в его память по адресу X + 1-2 записывается набор констант

RV4Xf,l ), ..., RV(Xi,l) ,

где

40

50

55

R) ...Xi/.Lj| ,

j 1, 2, ..., K/(5)

где S f - масштаб с номером 1 в

,.1, ..., L-lj; L - число используемых масштабов, S j 2 .

Первые адрееные входы узлов памя- ти, входящих в состав блока 19, в совокупности составляют его первый адресный вход, а вторые их адресные входы объединены и подключены к второму адресному входу блока 19, выходы узлов памяти, соответствующие вычетам наборов по модулю m ; в совокупности образуют (1+1)-и выход блока 19 (1 0,1, ..., К). Управляющие входы выдачи кода всех узлов памяти объединены и подключены к управляющему входу блока 19.

. Блок 20 групп элементов ИЛИ содержит К групп элементов ИЛИ.

Группа содержит блоки 21 суммирования вычетов по модулям т, m , ..., го х-о ™к из которых (,2,..., К) осуществляет сложение за Т тактов наборов из (К-1) вычетов по модулю

.( вместе с фор миро в а if нем числа пё реполнени, а (К+1)-й блок осуществляет сложение за Т тактов наборов из К вычетов по модулю т без формирования числа переполнений. Выходы суммы блоргов 21 суммирования вычетов по модулям Гоо, m , ..., т, и выход суммы блока 21 суммирования вычетов по модулю m ), группы, образуют выход суммы, а выходы числа переполнений блоков 21 суммирования по модулям т,

Д, J .,., 111ц., - выход числа перепол- шений группы.

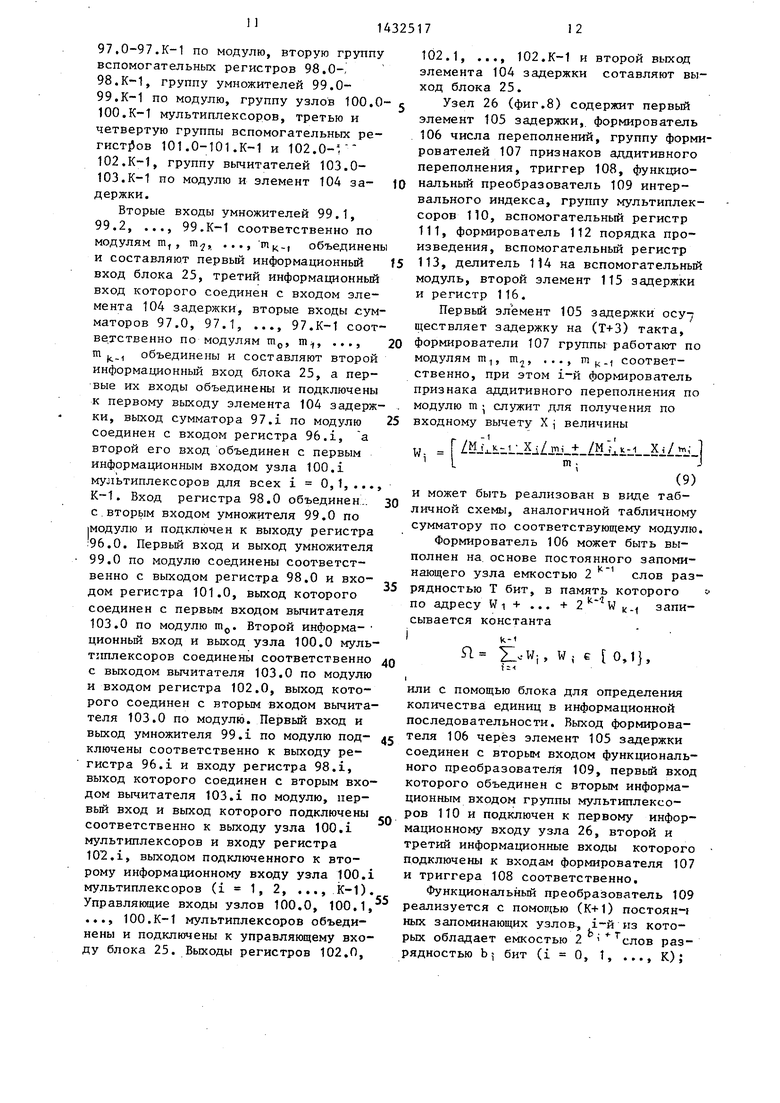

Формиро ватель 23 интегральных ха- рактеристик модулярного кода (фиг.6) содержит группу элементов ИЛИ 90.1 90.Кузел 91 определения интег., Х

I ральных характеристик, группу элемен тов и 92.1-92.К-2, группу мультиплек

: Серов 93, группу узлов 94.1-94.К-1

: формирования номера нормирующего мно; жителя и регистр 95.

; Узел 91 реализован по известной;.,

схеме и определяет поправку Амербаева ; бСХ), знак S(X), цифры симметрическо - ; го полиадического кода X (, Х, и машинный интервальньй индекс Iц(Х) входного числа Х е D. Быстродействие I узла 91 составляет Т+2 такТов -при I пропускной способности одна операция I в .

i Выходы поправки Амербаева, знака, ; числа и машинного интервального ин- декса числа являются соответственно ; первым, вторым и четвертым выхода ш I узла 91, а выходы цифр симметричного : полиа дического кода составляют его ; третий выход. Вьк,од мпадшей цифры ; симметрического полиадического кода узла 91 соединен с первым входом эле мента-ИЛИ 90,1, второй вход которого соединен с выходом второй цифры симметрического полиадического кода узла 9 1 , выход цифры симметрическо го полиади эеского кода которого подсоединен к входу элемента ИЛИ 90, (i 3, 4, .,., К).

Элемент И 92,1 (1 1, 2, .,., К-2) имеет (К-1) входов, первьш вход 1-го элемента И 92.1 соединен с прямым выходом 1-го элемента ИЛИ 9,0.1, а j-й вход (J 1, 2, ..., К-1) соединен с инверсным выходом элемента ИЛИ 90.i+j-1. На выходе элемента И 92,1 фор1 1ируется двухзначная величина .-

i ll; 1,Ч1 ... , (6)

где - и 7Г. - величины, формируемые на выходах j-ro элемента ИЛИ 90.j- (j 1, 2, ,..., К-1).

Узел 94.1 (i 2, 3, .... К-1) реализуется на основе постоянного запоминающего узла, обладающего емкостью 2 слов разрядностью log х xClog nM j.fC) бит. В его память по адресу X j + 2 -XjVi записывается величина

1 li т Мк-1Г .

li (7х н- хТГГшТ7То:5)1--1

(7)

М ,-.,

X

П D

j-- если х;

(т - 1)/2,

0

5

0

5

.с

Х-1 т, еслиХ(т1- О/2;

С (0,1,

m

i- 1

0

0

5

L I A} ««} ix«

Узел 94,1 вьтолненаналогичным образом, за исключениемтого, что в его память по адресу Х, +2 Х записы- I вается величина

; - /°%7xfflfl;;7- - «

Первый и второй входы узла 94.1 соедц нены соответственно с выходами 1-й и ()-й цифры симметрического полиадического кода блока 91, управляющий вход вьщачи кода узла 94.j (j 1, 2, ..., К-2) подключен к выходу элемента И 92.j, а управляющий вход вьщачи кода узла 94.К-1 соединен с прямым выходом элемента ИЛИ 90.К-1, выходы узлов 94.1 - 94.К-1 -соединены с входами регистра 95, выход которого является третьим выходом формирователя 23 интегральных характеристик модулярного кода. Первый вход узла 91 является первым информационньм входом формирователя 23, а второй вход соединен с выходом группы мультиплексоров 93, управляющий вход которой соединен с управляющим входом формирователя 23, первый и второй информационные входы группы мультиплексоров 93 подключены соответственно к четвертому выходу узла 91 и второму информационному входу формирователя 23, первый и второй вьпсоды узла 91 явля- ются соответственно вторым и первым выходами формирователя 23.

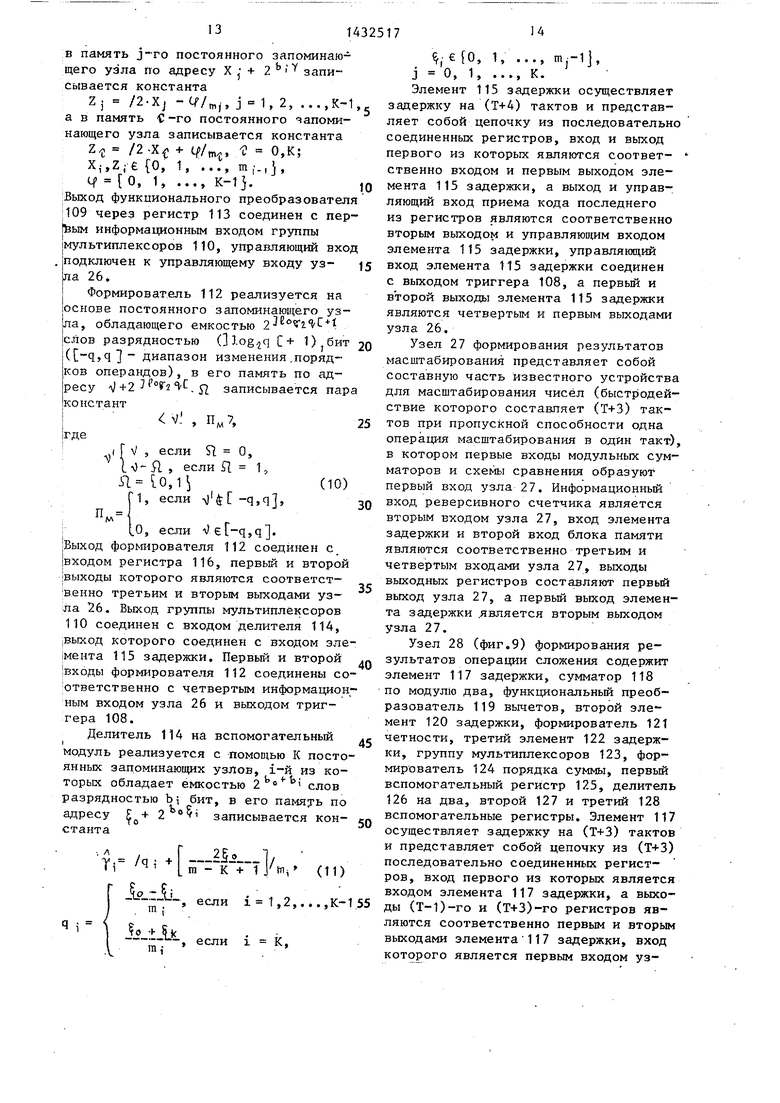

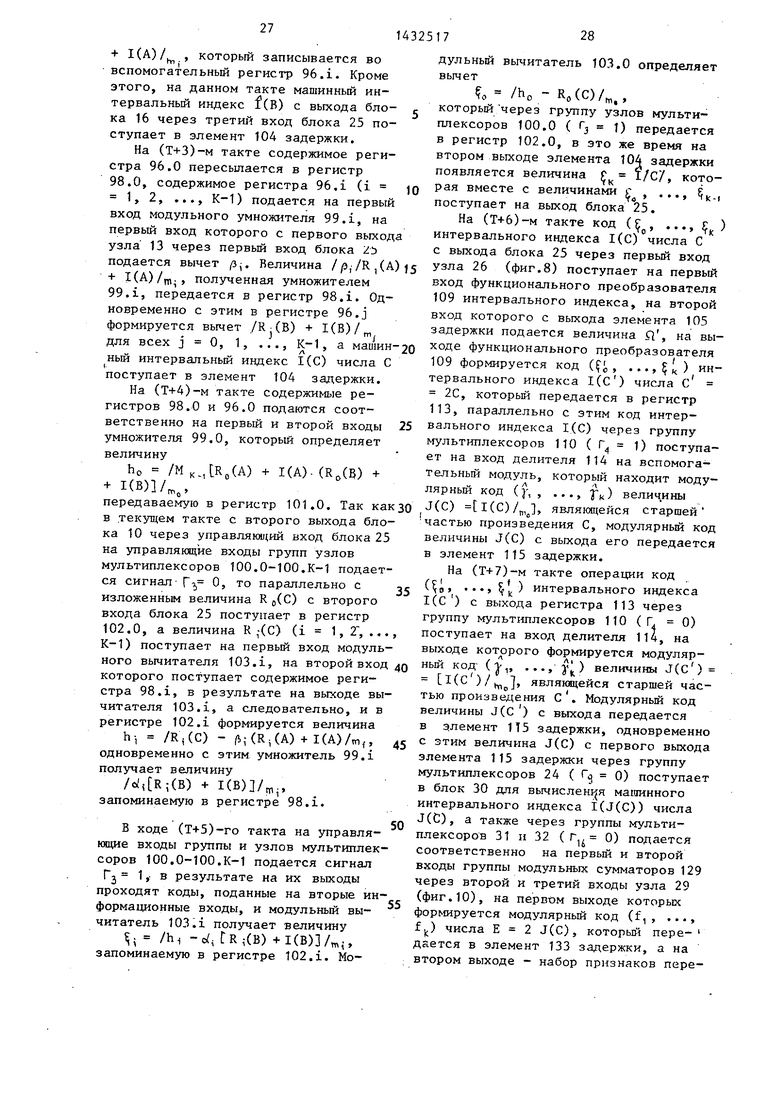

Блок 25 вычисления интервального индекса произведения (фиг.7) содержит первую группу вспомогательных регистров 96.0-96.К-1, группу сумматоров

97,0-97.К-1 по модулю, вторую группу вспомогательных регистров 98,0-, 98.К-1, группу умножителей 99.0- 99.К-1 по модулю, группу узлов 100.0- 100.К-1 мультиплексоров, третью и четвертую группы вспомогательных ре- 101.0-101.К-1 и 102.0-Г 102.К-1, группу вычитателей 103.0- 103.К-1 по модулю и элемент 104 за- держки.

Вторые входы умножителей 99.1, 99.2, ..., 99.К-1 соответственно по модулям т,, т,, .. объединены и составляют первый информационный вход блока 25, третий информационный вход которого соединен с входом элемента 104 задержки, вторые входы сумматоров 97.0, 97.1, ..., 97.К-1 соот- ве.тственно по модулям т, го;,, ...,

m |, объединены и составляют второй информационный вход блока 25, а первые их входы объединены и подключены к первому выходу элемента 104 эадерж- ки, выход сумматора 97.1 по модулю соединен с входом регистра 96.1, а второй его вход объединен с первым информационным входом узла 100.1 мультиплексоров для всех 1 0,1,..., К-1. Вход регистра 98.0 объединен. с.вторым входом умножителя 99.0 по

|модулю и подключен к выходу регистра :96.0. Первый вход и выход умножителя 99.0 по модулю соединены соответственно с выходом регистра 98.0 и входом регистра 101.0, выход которого соединен с первым входом вычитателя 103.0 по модулю т,. Второй информа- ционньй вход и выход узла 100.0 мультиплексоров соединены соответственно с выходом вычитателя 103.0 по модулю и входом регистра 102.0, выход которого соединен с вторым входом вычитателя 103.0 по модулю. Первый вход и вькод умножителя 99.1 по модулю под- ключены соответственно к выходу регистра 96.1 и входу регистра 98.1, выход которого соединен с вторым входом вычитателя 103.1 по модулю, первый вход и выход которого подключены соответственно к выходу узла 100.1 мультиплексоров и входу регистра 102.1, выходом подключенного к второму информационному входу узла 100.1 мультиплексоров (1 1, 2, ...,К-1). Управляющие входы узлов 100.0, 100.1, ..., 100.К-1 мультиплексоров объединены и подключены к управляющему входу блока 25. Выходы регистров 102,0,

Ю

J5 20

. 25 ЗО

Q 5

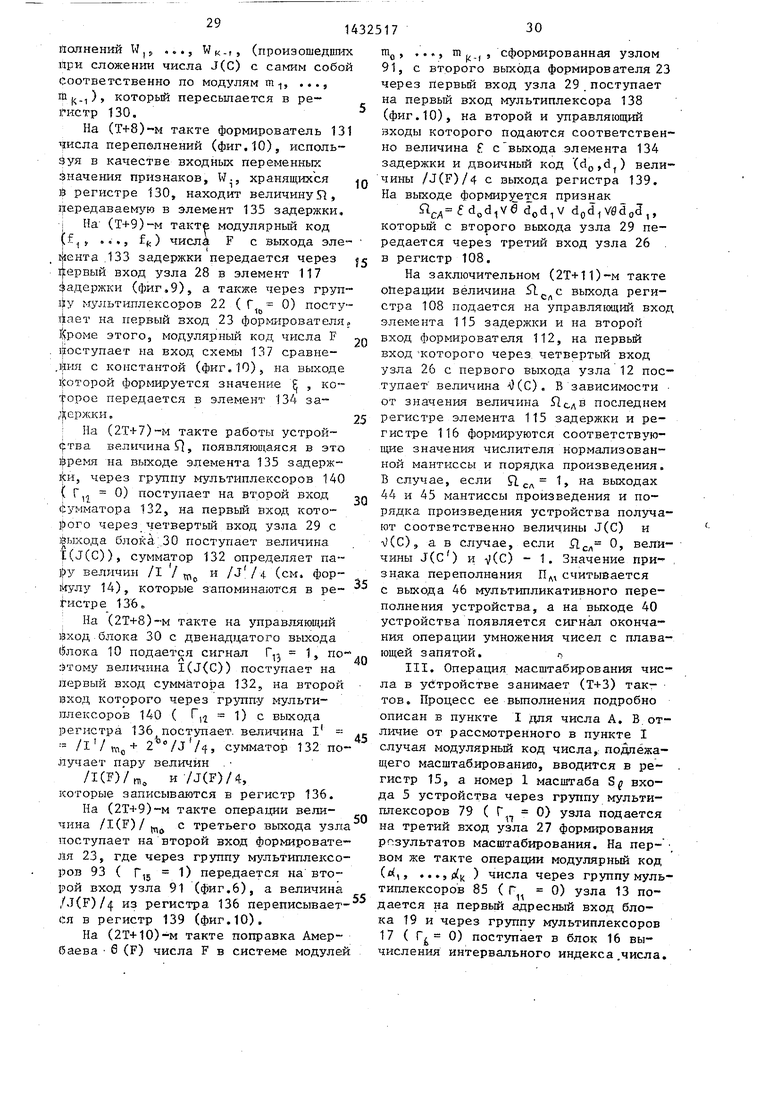

Узел 26 (фиг.8) содержит первый элемент 105 задержки,, формирователь 106 числа переполнений, группу формирователей 107 признаков аддитивного переполнения, триггер 108, функциональный преобразователь 109 интервального индекса, группу мультиплексоров ПО, вспомогательный регистр 111, формирователь 112 порядка произведения, вспомогательный регистр 113, делитель 114 на вспомогательный модуль, второй элемент 113 задержки и регистр 116.

Первьй элемент 105 задержки ocy-j ществляет задержку на (Т+3) такта, формирователи 107 группы работают по модулям ш, Шо, -, Гоц. соответственно, при этом 1-й формирователь признака аддитивного переполнения по модулю m ; служит для получения по входному вычету X величины

W Г /M f i L XjZ nLL± ZMjlb-J i/I jJ i т.J

(9)

и может быть реализован в виде табличной схемы, аналогичной табличному сумматору по соответствующему модулю.

Формирователь 106 может быть выполнен на. основе постоянного запомиk. 1

нающего узла емкостью 2 слов раз- 35 рядностью Т бит, в память которого 50

5

IC- Z

W

К-1

запипо адресу W i + ... -ь 2 сывается константа

Ik-t

Л XI-Wj, W; е 0,1},

i-1 I

или с помощью блока для определения количества; единиц в информационной последовательности. Выход формирователя 106 через элемент 105 задержки соединен с вторым входом функционального преобразователя 109, первый вход которого объединен с вторым информационным входом группы мультиплексоров 110 и подключен к первому информационному входу узла 26, второй и третий информационные входы которого подключены к входам формирователя 107 и триггера 108 соответственно.

Функциональный преобразователь 109 реализуется с помощью (К+1) постоян-f ных запоминающих узлов, 1-й из которых обладает емкостью 2 разрядностью Ь бит (, 1, ..., К);

в память J-TO постоянного запоминающего узла по адресу X + 2 записывается константа

Zj /Z-Xj -Q /m,-, j 1, 2, ...,К-1,5 a в память С-го постоянного запоминающего узла записывается константа Z /2-Х -f tf/m, /г О,К;

X,-,Z; (О, 1m ,.,,

Ч о, 1, ..., K-i}. ,0

;Выход функционального преобразователя ; 109 через регистр 113 соединен с первым информационным входом группы |мультиплексоров 110, управляющий вход |подключен к управляющему входу уз- J5

а 26.

Формирователь 112 реализуется на основе постоянного запоминающего уз- |ла, обладающего емкостью 2- i |слов разрядностью ( С+ 1) j бит 20

( диапазон изменения .порядков операндов), в его память по ад- jpecy V+2 У г VC. j записывается пара 1констант

h

v.: , .

|где

( Г V , если Я О, 1л)-Л , если Я П Я tO, 1, если л) -q,q.

(10)

П

0, если ef-qjq. |Выход формирователя 112 соединен с 1ВХОДОМ регистра 116, первый и второй чвыходы которого являются соответственно третьим и вторым выходами узла 26. Выход группы мультиплексоров 110 соединен с входом делителя 114, ;Вьпх;од которого соединен с входом зле 1мента 115 задержки. Первьй и второй :входы формирователя 112 соединены со ответственно с четвертым информационным входом узла 26 и выходом триггера 108.

Делитель 114 на вспомогательный

I

модуль реализуется с помощью К постоянных запоминающих узлов, i-й из которых обладает емкостью слов разрядностью bi бит, в его память по адресу 0+2 записывается кон- станта

Т,- /ч, (11)

j L;:Jj.

га

если i 1,2,...,К-155

ч

If-lJji

га,

если i К,

5

0

5

0

5

0

35

.-.

.,

4Э

JQ

55

. € fO, 1,..., m-lj, j О, 1К.

Элемент 115 задержки осуществляет задержку на (Т+4) тактов и представляет собой цепочку из последовательно соединенных регистров, вход и выход первого из которых являются соответ- ственно входом и первым выходом элемента 115 задержки, а выход и управляющий вход приема кода последнего из регистров являются соответственно вторым выходом и управляюп1им входом элемента 115 задержки, управляющий вход элемента 115 задержки соединен с выходом триггера 108, а первьй и второй выходы элемента 115 задержки являются четвертым и первым выходами узла 26.

Узел 27 формирования результатов масштабирования представляет собой составную часть известного устройства для масштабирования чисел (быстродействие которого составляет (Т+3) тактов при пропускной способности одна операция масштабирования в один такт), в котором первые входы модульных сумматоров и схемы сравнения образуют первый вход узла 27. Информационный вход реверсивного счетчика является вторым входом узла 27, вход элемента задержки и второй вход блока памяти являются соответственно третьим и четвертым входами узла 27, выходы выходных регистров составляют первьй выход узла 27, а первый выход элемента задержки .является вторым выходом узла 27.

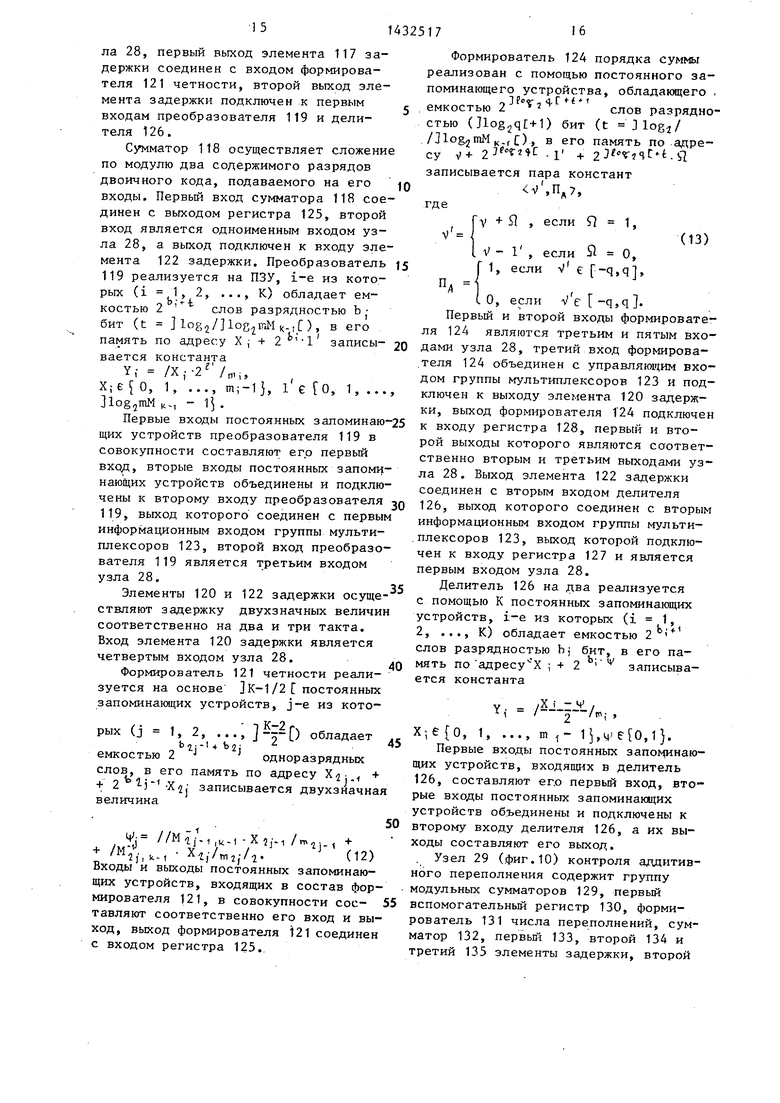

Узел 28 (фиг.9) формирования результатов операции сложения содержит элемент 117 задержки, сумматор 118 по модулю два, функциональный преобразователь 119 вычетов, второй элемент 120 задержки, формирователь 121 четности, третий элемент 122 задержки, группу мультиплексоров 123, формирователь 124 порядка суммы, первый вспомогательный регистр 125, делитель 126 на два, второй 127 и третий 128 вспомогательные регистры. Элемент 117 осуществляет задержку на (Т+3) тактов и представляет собой цепочку из (Т+3) последовательно соединенных регистров, вход первого из которых является входом элемента 117 задержки, а выходы (Т-1)-го и (Т+3)-го регистров являются соответственно первым и вторым выходами элемента 117 задержки, вход которого является первым входом уз

ла 28, первый выход элемента 117 задержки соединен с входом формирователя 121 четности, второй выход элемента задержки подключен к первым входам преобразователя 119 и делителя 126.

Cj MMaTop 118 осуществляет сложение по модулю два содержимого разрядов двоичного кода, подаваемого на его входы. Первый вход сумматора 118 соединен с выходом регистра 125, второй вход является одноименным входом узла 28, а выход подключен к входу элемента 122 задержки. Преобразователь 119 реализуется на ПЗУ, i-e из которых (i ,1, 2, ..., К) обладает емкостью 2 слов разрядностью b j- бит (t logj/jlog irJ-I к-,С), в его память по адресу Х,- + 2 1 записывается константа

Y f /X ,- 2 /pi i ( Х;е О, 1, ..,, т;-1}, 1 € о, 1, ... K,, - 1 .

Первые входы постоянных запоминаю- щих устройств преобразователя 119 в совокупности составляют его первый вход, вторые входы постоянных запоми- наю11(их устройств объединены и подключены к второму входу преобразователя 119, выход которого соединен с первым информационным входом группы мультиплексоров 123, второй вход преобразователя 119 является третьим входом узла 28.

Элементы 120 и 122 задержки осуществляют задержку двухзначных величин соответственно на два и три такта. Вход элемента 120 задержки является четвертым входом узла 28.

Формирователь 121 четности реализуется на основе К-1/2 постоянных запоминагацих устройств, j-e из которых (J 1, 2, ..., --) обладает ь.-иьг; 2

емкостью i одноразрядных слов, в его память по адресу Х/;. +

)

величина

записывается двухзначная

- -г

//M-ij-i ,1сИ - X 2j-i /т, , +

/М-/.,,., - X,,/,.,./,. (12)

Входы и выходы постоянных запоминающих устройств, входящих в состав формирователя 121, в совокупности сое- 55 тавляют соответственно его вход и выход, выход формирователя 121 соединен с входом регистра 125.,

0

.

Q 5

5 Q

, 5

0

5

Формирователь 124 порядка суммы реализован с помощью постоянного запоминающего устройства, обладакицего ,

««-,

емкостью I - слов разрядностью (Jlogjqt+l) бит (t Jlog2/ /Jlog mM ., С) в его память по адресу V+ - 1 + 2 5ЧС-.Я записывается пара констант

, v ,, где

(V + Я , если Я 1, (13) V - 1 , если S О, Г 1, если V е f-q,q,

А 1

I г т

С о, если V е L -q,q J. Первый и второй входы формирователя 124 являются третьим и пятым входами узла 28, третий вход формирователя 124 объединен с управляющим входом группы мультиплексоров 123 и подключен к выходу элемента 120 задержки, выход формирователя 124 подключен к входу регистра 128, первый и второй выходы которого являются соответственно вторым и третьим выходами узла 28. Выход элемента 122 задержки соединен с вторым входом делителя 126, выход которого соединен с вторым информационным входом группы мульти- .плексоров 123, выход которой подключен к входу регистра 127 и является первым входом узла 28.

Делитель 126 на два реализуется с помощью К постоянных запоминающих устройств, i-e из которых (, 2, ..., К) обладает емкостью 2 слов разрядностью hj бит, в его память по адресу Х ; -t 2 записывается константа

Y. - , 1 2 ;

Х;е {о, 1, ..., m - 15,,1}.

Первые входы постоянных запо1 наю- щих устройств, входящих в делитель 126, составляют его первьй вход, вторые входы постоянных запоминаклцих устройств объединены и подключены к второму входу делителя 126, а их выходы составляют его выход.

Узел 29 (фиг.10) контроля аддитивного переполнения содержит группу модульных сумматоров 129, первый вспомогательный регистр 130, формирователь 131 числа переполнений, сумматор 132, первьп 133, второй 134 и третий 135 элементы задержки, второй

вспомогательный регистр 136, схему 137 сравнения с константой, мультиплексор 138, третий вспомогательный регистр 139 и группу мультиплексоров j 140. Группа содержит сумматоры 129 по модулю т, ..., П1 j с формированием Признака переполнения, из которых (,2, ..,, К) может быть ре- 1ализован в виде табличной схемы, Вхо-|0 Йы первого и второго слагаемых сумма- торов 129 являются соответственно рвторым и третьим информационными входами узпА 19. Выходы суммы Z и пере- .

ролнения сумматоров 129 соединены 15 Соответственно с входами элемента 133 задержки и регистра 130, выход кото- Ього подключен к входу формировате- JiH 131.

I Формирователь 131 выполняется ана-20 Ьогично фор;мирователю 106, выход фор-- чирователя 131 соединен с входом эле- ента 135 задержки, I Сумматор 132 реализуется на основе

Достоянного запоминающего устройства,25 Ьбладающего емкостью 2 « 2 °к слов азрядностыо (Ьл + 2) бит, в его па- Иять по адресу 1 + 2 Х записывается hapa констант

,,

it I i.iiL.. 1/ ;

L MO J

f /X/lb

(14)

где

,л л I, если I

m

л

I - m

k

если

0

л 1

/ m.

Первый и второй входы сумматора 132 подключены соответственно к чет- Ьертому информационному входу уз ла 129 и выходу группы мультиплексоров 140, управляющий вход которой подключен к управляющему входу узла 29, выход сумматора 132 подключен к вхо- ду регистра 136.

Элементы 133 и 135 осуществляют задержку соответственно на два и (Т-1) тактов. Элемент 134 осуществля ет задержку величины ( ,1)) на (Т+2) такта.

Выход элемента 133 задержки соединен с входом схемы 137 сравнения с константой, выход йоторой подключен к входу элемента 134 задержки.

Схема 137 сравнения анализирует совпадение модулярного кода числа X с модулярным кодом числа -т-И(., На

0 .

5

0

5

0

5

40 45

-

ее выходе при совпадении формируется единичное значение величины Е,

Первьй и второй информационный и управляющий входы мультиплексора 138 соединены соответственно с первым информационным входом узла 29, с выходом элемента 134 задержки и с выходом регистра 139. Второй информационный вход группы мультиплексоров 140 и вход регистра 139 объединены и подключены к выходу регистра 136, Выходы элемента.133 задержки, мультиплексора 138 и регистра 136 являются соответственно выходами с первого по третий узла 29. Первый информацион- ньй вход группы мультиплексоров 140 соединен с выходом элемента 135 задержки.

Блок 30 вычисления интервального .индекса числа структурно аналогичен блоку 16, за исключением того, что вьпсодной регистр блока 30 имеет управляющий вход запрещения приема кода, который является управляющим входом блока 30.

Элемент 33 задержки представляет собой цепочку из двух последовательно соединенных регистров, вход и выход первого из которых являются соответственно входом и первым выходом элемента 33 задержки, а выход второго регистра является вторым выходом элемента 33 задержки.

Арифметическое устройство вьтол- няет операции сложения и умножения чисел а f/.(a) , v(a) ), b (b), C(b), представленных в форме с плавающей запятой, где (Lf(a) - А/М и fj(b) В/М - мантиссы, а V(a) и О(Ь) - порядки операндов d и b соответственно, а также операции масштабирования и определения знака числа X, А, В, X Б D; М тпМ «., V(a); V(b) eC-q, (а}/; /|W(b)/ 1. По сигналу с входа 3 устройства в блок 10 регистры 50-53 обнуляются, а триггер 67 посредством элемента ИЛИ 61 устанавливается в единичное состояние (фиг.2), тем самым устройство приводится в исходное рабочее состояние. Код Г операции, подлежащий выполнению (см, таблицу), с входа 2 кода операции устройства подается на входы дешифратора 48 и информационный вход триггера 54 блока 10, При этом, в случае Г О или 1 в мпадший разряд сдвигового регистра 50 посредством элемента ИЛИ 49,

а в случае 2, 3, А - в младшие разряды соответственно регистров. 51- 53 непосредственно записываются единицы, по сигналу Г, 1, подаваемому с входа 1 устройства на управляющий вход регистра 15, первый управляющий вход регистра 14, через второй вход узла 13 на второй вход грзшпы элементов 87 запрета и на первый вход элемента ИЛИ 66 блока 10 и нулевые входы триггеров 54 и 67, триггеры 54 и 67 обнуляются, на первом выходе блока 10 вырабатывается сигнал Г2 Ь

10

знак величины 1 V (а) - t (b), при этом знак sign(l) записывается в триггер 75, а величина /1/ через группу мультиплексоров 79, на управляющий вход которой подается сигнал Г,7 1, с второго выхода узла 12 (фиг.З) поступает на третий вход узла 27, где записывается в элемент задержки .

Для V(a) v(b) имеем sign(l) О, поэтому на втором такте величина А поступает с первого выхода регистра 15 на третий вход узла 13 (фиг.4) и

подаваемьш на второй управляющий вход }5 через группу мультиплексоров 82 записывается в элемент 86 задержки, а величина V(a), поступающая с второго выхода регистра 13 на второй вход узла 12 (фиг.З) через группы мультирегистра 14, в регистр 14 с входов 6 и 7 устройства принимаются модулярный код (/),, ... /3() числителя. В мантиссы |U (b) и двоичный код порядка,. V(b) второго операнда, а в регистр 2о плексоров 73 и 77 ( Г,, 0), записыт

15, с входов в и 9 устройства принимаются модулярный код ( /), . . . , О(к )

числителя А мантиссы jU (а) и двоичный код порядка v (a) первого операнзадержки. Одно- В (симвается в элемент 78 временно с этим величина вол означает + или -), поступаюп1ая с певрого выхода регистра .14 на второй информационньй вход узла 13 (фиг.4) через группы мультютлексо- ров 81 и 85 ( Г, 1), с второго выхода узла 13 через группу мул ьт1шлек- сора 17 ( Г О), поступает в блок 16, где в течение очередных Т тактов, считая текущий, в соответствии с формулой (1) вычисляется машинньа интервальный индекс 1(В) числа, а также подается на первый адресный вход блока 19 хранения констант, на второй адресный вход которого с второго выхода узла 27 подается номер 1 масштаба, а на управляющий вход с тринадцатого выхода блока 10 подается сигнал Г,4. Ь в результате на j-м выходе блока 19 фор1 1руется набор вычетов

да, и после этого начинается первый такт операции. При выполнении операций масштабирования и определения числа регистр 14 не использу-; етсяг.

На первом такте работы устройства модулярный код ( |jj, ..., р ) числа В с первого выхода регистра 14 через четвертый вход узла 13 поступает на вход формирователя 83 дополнительног кода (фиг.4), который получает моду- лярный код (-//3/т,, ..., числа -В, подаваемый через группу элементов 87 запрета с первого выход узла 13 на второй информационный вход регистра 14. Запись числа -В в регистр 14 произойдет лишь-тогда, когд вьтолняемой операцией является вычитание, так как в этом случае на первом выходе блока 10 вырабатывается сигнал Г2 1, подаваемый на второй управляющий вход регистра 14. Одно- , временно с этим порядки д) (а) первого и V(b) второго операндов с вторых выходов регистров 15 и 14 соответственно через первьй и второй входы узла 12 подаются на первый, и второй входы вычитателя 74, на первом я втором выходах которого формируются со- ответственно абсолютное значение и

знак величины 1 V (а) - t (b), при этом знак sign(l) записывается в триггер 75, а величина /1/ через группу мультиплексоров 79, на управляющий вход которой подается сигнал Г,7 1, с второго выхода узла 12 (фиг.З) поступает на третий вход узла 27, где записывается в элемент задержки .

Для V(a) v(b) имеем sign(l) О, поэтому на втором такте величина А поступает с первого выхода регистра 15 на третий вход узла 13 (фиг.4) и

о плексоров 73 и 77 ( Г,, 0), записыт

задержки. Одно- В (сим5

0

5

.

вается в элемент 78 временно с этим величина вол означает + или -), поступаюп1ая с певрого выхода регистра .14 на второй информационньй вход узла 13 (фиг.4) через группы мультютлексо- ров 81 и 85 ( Г, 1), с второго выхода узла 13 через группу мул ьт1шлек- сора 17 ( Г О), поступает в блок 16, где в течение очередных Т тактов, считая текущий, в соответствии с формулой (1) вычисляется машинньа интервальный индекс 1(В) числа, а также подается на первый адресный вход блока 19 хранения констант, на второй адресный вход которого с второго выхода узла 27 подается номер 1 масштаба, а на управляющий вход с тринадцатого выхода блока 10 подается сигнал Г,4. Ь в результате на j-м выходе блока 19 фор1 1руется набор вычетов

,г)

(B,l) (B,,l ),

0

,,,,1 )7,

5 определяемых по формулам (4) и (5), В J /B/«ij. Наборы вычетов ,), ..., w|,,(,) через блок 20 групп элементов ИЛИ, а набор вьиетов W,((B, 1) непосредственно поступают в соответствующие блоки 21 суммирования вычетов группы. На (Т+2)-м такте величина l(B), сформированная блоком 16, подается на четвертый вход узла 27, а на (.Т+3)-м такте на первый и второй 1входы узла 27 с выходов группы блоков 21 подаются соответственно наборы величинКд(В,1), ..., R,j(B,l), где Rj(,l) - сумма по модулю mj набора констант (B,l) и

5

числоб(В,1) переполнений, произо шедших в блоке суммирования вычетов по модулю in(5 m. Выполняя необходи-i мые действия над указанными входными величинами,, узел 27 по истечении (Т+А)-го такта формирует модулярный код оценки В дроби В/2 , который с первого вызсода узла 27 на (Т+5)-м I такте пересыпается в элемент 33 за- i держки.

I На (Т+6)-м такте работы устройства I величина А с третьего выхода узла 13 ; через группу мультиплексоров 31 ( Г 1) и величина с первого выхода элемента 33 задержки через группу I мультиплексоров 32 ( ,- О подается соответственно на первый и второй входы группы модульных сумматоров 129 I через второй и третий входы узла 29 I(фиг.10). Сумматоры 129 на первом своем вЬкоде формируют модулярный код (у,) числа С А + А-В, кото- |рын передается в элемент 133 задерж- |ки, а на втором выходе набор призна- ков переполнений W, ., ., W ((, , про изошедших при сложении чисел А и В iсоответственно по модулям т, ..., |т, которой пересьшается в регистр ИЗО, Одновременно с этим модулярный |код (о(, J ..., (| ) числа А с третьего I выхода узла 13 через группу мульти |плексоров 24 ( Гд 1) поступает в блок 30, где в течение очередных Т Iтактов, считая текущий, в соответст |вии с формулой (1) вычисляет машинный ;интервальный индекс 1(А) числа. На (Т+7)-м такте формирователь 13 |числа переполнений, используя в ка- ;честве входных переменных значения признаков W , ..., W(;., 5 хранящихся

в регистре 130, находит величину i k-f

W. передаваемую в элемент 135

i:i

задержки. Параллельно с этим модулярньй код числа В с второго выхода элемента 33 задержки через группу мультиплексоров 24 (а- 2) поступает в блок 30 для вычисления машинного интервального индекса 1() числа,

На (Т+8)--м такте модулярньй код (,..., Yk числа С с выхода элемента 133 задержки (фиг.10) передается через первьш вход узла 28 в эле

мент 117 задержки (фиг.9), а также через группу мультиплексоров 22 ( Г,д 0) поступает на первый вход формирователя 23. Кроме того, модулярный

Q

5 0

5

код числа С поступает на вход схемы 137 сравнения с константой, на выходе которой формируется величина Е, которая передается в элемент 134 задержки.

На (2Т+6)-м такте работы устройства величина, появляющаяся на выходе элемента 13.5 задержки, через группу мультиплексоров 140 ( Г, 0) поступает на второй вход сумматора 132, на первый вход которого через четвертьй вход узла 29 с выхода блока 30 поступает велргчина I(A)j сумматор 132 определяет пару величин . и /J 4, (см. формулу 14), которые запоминаются в регистре 136 (фиг.10).

На (2Т+7)-м такте работы величина l /l /nio+ 2 °Jj /4.c выхода .регистра 136 через группу мультиплексоров 140 ( Г,2 1) поступает на второй вход сумматора 132, на первый вход которого с выхода блока 30 поступает вычет 1(В), сумматор 132 получает пару величин /I(C)/mo и /J(C)/ 4 (си. формулу 14), которые записываются в регистр 136.. Одновременно с этим модулярный код числа С с первого выхода элемента 117 задержки узла 28 поступает на вход формирователя 121 четности, на выходе которого формируется набор двухзначных величин Ц , t V(cM. формулу 12), где г (К-1)/2С, которые записываются в регистр 125.

На (2Тн-8).-м такте величина /1(С)/ с третьего выхода узла 29 поступает на второй вход формирователя 23, где через группу мультиплексоров 93 ( 1) передается на второй вход узла 91, а величина /J(C)/4 из регистра 136 пересыпается в регистр 139. Одновременно с этим младшие разряды 0/0 и io соответственно величин /1(С) и /J(C)/4 с третьего выхода узла 29 через второй вход узла 28 подаются на второй вход сумматора 118, на первый вход которого с выхода регистра 125 поступают ц, ..., У, сумматор 118 формирует четность числа -

С V(C) /I

+ d + /2, кото

рая поступает в элемент 122 задержки. На (2Т+9)-м такте поправка Амер- баева О(С) в числа С в системе модулей Шр, ..., m ц., , сформированная узлом 91, с второго выхода формирователя 23 через первый вход узла 29 поступает на первьш вход мультиплексора 138, на второй и управляющий входы которого подаются соответствен- но величина Е с выхода элемента задержки и двоичный код (,(/i) величины yj(C)/4 с выхода регистра 139. На выходе мультиплексора 138 формируется признак аддитивного перепол- Q нения мантиссы |t/(C) Яс f |,сЦ fdx x d d(jd , который с второго выхода узла 29 передается через четвертый вход узла 28 в элемент 120 за- ержки.15

На (2Т+10)-м такте узел 91 на втором выходе формирует знак числа С, который может быть считан посредством выхода 43 устройства, а на третьем выходе формирует коэффициенты сим- 20 метрического полиадического кода числа С., при этом цифры Х и X поступают на первый и второй входы элемента ИЛИ 90.1, а цифры симметрического полиадического кода числа С посту-25 пают на вход элемента ИЛИ 90.-1 (J 3, 4, ..., К). На прямом и ин- BeptQHOM выходах i-ro элемента ИЛИ 90.i (i 1, 2, ..., К-1) формируются соответственно величины ТГ, и JT., а 30 на выходе t-ro элемента И.92.i (t 1, 2, ..., К-2) появляется двухзначная величина )|,(см. формулу 6), которая подается на управляняций вход вьщачи кода t-ro узла 94.t, а вели- ,c чина ,, , формируемая на пряном выходе элемента ИЛИ 90.К-1, подается на управляющий вход выдачи кода узла 94.К-1, на первый и второй входы узла 94.1 (, 2, ..., К-1) подают- 40 ся соответственно цифры симметрического полиадического кода числа СхГ и X Так как среди булевых величин t,, ..., L K, и F, единичное значение может принимать лишь одна 45 из них (обозначим ее номер через 6 1, 2, ..., К-1}), то ненулевая информация (номер l| нормирующего множителя (см. формулы 7 и 8) появляется лишь на выходе узла 94., при eg этом величина 1 записывается в регистр 95. На заключительном (2Т+11)-м такте операции модулярный код (,..., числа С с второго выхода -элемента 117 задержки (фиг.9) поступает на первые входы преобразователя 119 и делителя 126, на второй вход преобразователя 119 с третьего выхода формирователя 23 поступает величина ., а

55

Q 5

0 5 0 c 0 5 g

5

на второй вход делителя 126 с выхода элемента 122 задержки подается величина (f (C) . На выходе преобразователя 119 формируется модулярный код величины С , а на выходе делителя 126 модулярный код величины С ГС/2, которые поступают соответственно на первый и второй информационные входы группы мультиплексоров 123, на управляющий вход которой с выхода элемента 120 задержки подается двухзначная величина 7сл Одновременно с этим величина (а) с первого выхода узла 12 через пятый вход узла 28 поступает на первьй вход формирователя 124 порядка суммы, на второй и третий входы которого подаются

1 ГЛ

соответственно величины 1 v. и it

С8

В зависимости от значения величины регистрах 127 и 128 формируются соответствукнцие значения числителя нормализованной мантиссы результата, а также порядка результата и признака переполнения. В случае, если Лев Ь на выходе 34 мантиссы суммы и выходе

35порядка суммы устройства получают соответственно величины С и V (С) V(a) + 1, а в случае ЯсС соответственно величины и V(C)

)(a) - i;.

Значение признака переполнения П. может быть считано посредством выхода

36аддитивного переполнения устройства, а на выходе 39 устройства появляется сигнал ркончания операции сложения (вычитания) чисел с плавающей запятой,

II. Рассмотрим как в арифметическом устройстве - выполняется операция умножения с плавающей запятой.

На первом такте данной операции модулярный код (, ..., o(fc) числа А с первого выхода регистра 5 поступает на первый вход блока 11, на второй вход которого с первого выхода регистра 14 подается модулярный код (/,, ...,fik числа В, в выходном регистре блока 11 формируется модулярный код ( J , ..., 1 ) произведения С А В, модулярный код числа В также поступает на второй информационньй йход узла 13, где через группу мультиплексоров 80 ( Г,, 0) подается на вход элемента 84 задержки, порядки V(a) первого и V(b) второго операндов с вторых входов регистров 15 и 14 соответственно через первый и второй входы узла 12 поступают на первый i

второй входы сумматора 72 (фнг.З), который получает величину v(C) V(a) + V(b), передающуюся в регистр 76. Параллельно с этим модулярный код числа А, поступающий на первый информационньш вход узла 13 (фиг.4)9 через группу мультиплексоров 85 ( Г, 0) проходит на второй выход узла 13, откуда через группу мультиплексоров 17,( Г 0) поступает в блок 16, где в течение очередных тактов, счи- Ьая текущий, в соответствии с форму- |пой (1) вычисляется машинный интер- . |вальньш индекс I/A) числа А. Кроме Ьтого, модулярный код числа А подает- РЯ на первый адресный вход блока 18 Ьсрапени с констант, на первый и вто- |)ой управляющие входы которого с шес- h oro и седьмого выходов блока 10 Поступают соответственно сигналы Г-, 1 О и Pj 1j в результате па первом И (j + 1)-M выходах блока 18 4)ОрмируютЬ { соответственно наборы вычетов С) rл - / D .1) . r,tiJ

W

(А) (.V,, ..,, RO (-, )

li

VI

И|

(it

(А) (с/,), ..., .,),

jo, (c/j,, ),,.., (o/,, )7, |компонеиты которых определя отся по форг;улам (2) и (3) при Х- ei- ii J. 3 | Z О, При этом наборы вЬ Тчетов о(Л), (A), ..,, , (А) через группы элементов ИЛИ блока 20 переда- |к)тся соответственно в блоки 21 сумми:рования вычетов по модулям Год ,

m

группы, и по истечении (Т+1)-го

такта на первом их выходе формирует- ;ся набор величин RQ (А) , . ., R ц,, (А), ;где R,(A) - сумма по модулю П; набора |канстант w y (A) (j О, 1,..., ). : На втором такте модулярный код (с/15 .., k- числа А с первого выхода регистра 15 поступает на первый иифорнащ онный вход узла 13, где через группу 1-1ультиплексоров 80 ( Г, 1),, подается на вход элемента 84 задержки. Величина д) (С) с выхода регистра 76 через группу мультиплексоров 77 ( Г 1) передается в элемент 78 задержки, модулярный код числа С с выхода блока 11 через второй вход узла 26 поступает на входы формирователей 107, на выходе которых формируется набор признаков переполнения W , ..., W (см. формулу 9), которые записываются в регистр 111. Параллельно с этим модулярный код числа В с первого выхода регистра 14 через группу мультиплексоров 17 (Г

50

0

5

,

1) поступает на вход блока 16, который вычисляет машинный интервальный индекс 1(В) числа В, и на первый адресньй вход блока 18, при этом аналогично действиям, описанным на первом такте операции, по истечении (Т+2)-го такта блоки 21 суммирования вычетов группы получают набор величин RO(B), ..., R(.(B), определяемьш так же, как и для числа А..

На третьем такте работы устройства формирователь 106 числа переполнений (фиг.8), используя в качестве входных переменных значения признаков Wi, ,.., W ц, храняпщхся в .регистре

j ., находит величину Я .j.

i

передаваемую в элемент 105 задержки. Одновременно с этим модулярньй код (-j ,, ;.,, | ) числа С с выхода блока 11 через группу мультиплексоров 17 ( Г 2) поступает в блок 16 для вычисления машинного, интервального индекса 1(С) и на первый адресньй вход блока 18 хранения констант, на второй и третий адресные входы которого по- . даются соответственно коды чисел А и В, а на первьй и второй управляющие входы сигналы Гт 1 и Pg 1. В результате на первом и (j+1)-M выходах блока 18 формируются соответственно наборы констант

(C) Ro (j-,,

.,)

0

R

(1

Q k-1

R

01

,,--j 4-/ )( ° )i T ,,...,(3V,), компоненты которых определяются по формулам (2) и (3) при Х -j ; , Y ,- ( , Z) /Ь. . Суммируя наборы указанных вычетов по соответствующим модулям, блоки 21 суммирования вычетов группы по истечении (Т+3)-го такта получают набор величин R(j(C), .,., RK-,(C).

На (Т+1)-м машинньй интер- вапьньй индекс 1(А) числа А с выхода блока 16 через третий вход блока 25 (фиг.7) поступает в элемент 104 задержки.

На (Т+2)-м такте вычет 1(А) с первого выхода элемента 104 задержки поступает на первьй вход модульного сумматора 97.1, на второй вход которого с выхода группы блоков 21 суммирования вычетов через второй вход блока 25 подается величина R;(A), сумматор 97.1 находит вычет /R.,-(A) +

+ I(A)/ , который записывается во вспомогательный регистр 96.1. Кроме этого, на данном такте машинный интервальный индекс f(В) с выхода бло- ка 16 через третий вход блока 25 поступает в элемент 104 задержки.

На (Т+3)-м такте содержимое регистра 96.0 пересылается в регистр

для всех j 0, 1, ..., К-1, а машинный интервальный индекс 1(С) числа С поступает в элемент 104 задержки.

На (Т+4)-м такте содержимые регистров 98.0 и 96.0 подаются соответственно на первьй и второй входы умножителя 99.0, который определяет величину

ho /Мк-ДКо А) + I(A)-() +

+ KB)/.,,

передаваемую в регистр 101.0. Так как в текущем такте с второго выхода блока 10 через управляющий вход блока 25 на управлякщие входы групп узлов мультиплексоров 100.0-100.К-1 подается сигнал- Г О, то параллельно с изложенным величина R о(С) с второго входа блока 25 поступает в регистр 102.0, а величина R-(С) (1 1,2,... К-1) поступает на первый вход модульного вычитателя 103.1, на второй вход которого поступает содержимое регистра 98.1, в результате на выходе вычитателя 103.1, а следовательно, и в регистре 102.1 формируется величина

h-, /R, (С) - /ijCRiCA) + I(A)/m,, одновременно с этим умножитель 99.1 получает величину

/c,R;(B) + 1(В)/., запоминаемую в регистре 98.1.

В ходе (Т+5)-го такта на управляющие входы группы и узлов мультиплексоров 100.О-100.К-1 подается сигнал РЗ 1 , в результате на их выходы проходят коды, поданные на вторые информационные входы, и модульный вы- читатель 103.1 получает величину

. /hi -с/, I:R,-(B) +i(B),

запоминаемую в регистре 102.1. Мо k-f

дульный вьшитатель 103.0 определяет вычет

, /he - RO(C)/., который через группу узлов мультиплексоров 100.0 ( Tj 1) передается в регистр 102.0, в это же время на втором выходе элемента 104 задержки появляется величина Г I/C/, которая вместе с величинами г , ..., | поступает на выход блока 25.

На (Т+6)-м такте код (, ..., интервального индекса 1(С) числа С с выхода блока 25 через первый вход узла 26 (фиг.8) поступает на первый вход функционального преобразователя 109 интервального индекса, на второй вход которого с выхода элемента 105 задержки подается величина Я , на выходе функционального преобразователя 109 формируется код ( , . .., j ) интервального индекса I(C ) числа с 2С, который передается в регистр 113, параллельно с этим код интервального индекса 1(С) через группу мультиплексоров 110 ( Г 1) поступает на вход делителя 114 на вспомогательный модуль, который находит моду- лярньш код (f, , ..., f) величины J(C) l(C)/, являюп(ейся старшей :частью произведения С, модулярный код величины J(C) с выхода его передается в элемент 115 задержки.

На (Т+7)-м такте операции код (0, ..., 1) интервального индекса 1(С ) с выхода регистра 113 через группу мультиплексоров 110 (Г 0) поступает на вход делителя 114, на выходе которого формируется модулярный код (1, ..., 3 J, ) величины J(c ) 1(С ) / ty, являющейся старшей частью произведения С . Модулярный код величины J(C ) с выхода передается в элемент 1Т5 задержки, одновременно с этим величина J(C) с первого выхода элемента 115 задержки через группу мультиплексоров 24 ( Г 0) поступает в блок 30 для вьгчислен1 я машинного интервального индекса I(J(C)) числа J(C), а также через группы мультиплексоров 31 и 32 ( Гц 0) подается соответственно на первьш и второй входы группы модульных сумматоров 129 через второй и третий входы узла 29 (фиг.10), на первом выходе которых формируется модулярный код (f, , ..., fj.) числа Е 2 J(C), который пере- дается в элемент 133 задержки, а на втором выходе - набор признаков перейолнений W

I

j K-i, (произошедших ири сложении числа J(C) с самим собой еоответственно по модулям т, ..., а ц.,), который пересылается в ре- fHcrp 130,

На (Т+8)-м такте формирователь 131 числа перепелнений (фиг,10), используя в качестве входных переменных значения признаков, W., хранящихся Q и регистре 130, находит величину Я, цередаваемую в элемент 135 задержки, ч На (Т+9)-м такте модулярный код (f, ..., f ;) числа F с выхода эле- йента .133 задержки передается через j ijtepBMH вход узла 28 в элемент 117 адержки (фиг,9), а также через груп™ liy мультиплексоров 22 ( Г, 0) поступает на первый вход 23 формирователя Кроме этого, модулярный код числа F поступает на вход схемы 137 сравне- фия с константой (фиг,10), на выходе 1|соторой формируется значение , ко- форое передается в элемент 13А за™ ;| ержки,25

: На ()м такте работы устрой- фтва величина Я 5 появляющаяся в это фремя на выходе элемента 135 задерж™ jjtH, через группу мультиплексоров 140

20

{ Г, 0) поступает на второй вход (Ьумматора 132, на первый вход кото- 1|)ого через четвертый вход узла 29 с з ыхода блока;,30 поступает величина t(J(C)), сумматор 132 определяет па- jj)y величин /I / вд и /J /i (см. фор- 14), которые запоминаются в ре Гистр е 13 б „

На (2Т+8)--м такте на управляющий вход блока 30 с двенадцатого выхода йлока 10 подается сигнал Г,} 1 по этому величина I(J(C)) поступает на первый вход сумматора 132,, на второй йход которого через группу мультиплексоров 140 ( Г,2 1) с выхода регистра 136 поступает, величина I /l /mo+ 2 Vj /f, сумматор 132 получает пару величин .

/()/„, и7я(Р)/4, которые записываются в регистр 136.

На (2Т-}-9)-м такте операции вели

чина /I(F)/ с третьего выхода узла поступает на второй вход формирователя 23, где через группу мультиплексоров 93 ( Г,5 1) передается на второй вход узла 91 (фиг.6), а величина /J(F)/4 из регистра 136 переписывается в регистр 139 (фиг.10),

На (2Т+10)-м такте поправка Амер- баева б (F) числа F в системе модулей

5

0

0

5

0

5

0

Шд , .,., m ,, I , сформированная узлом 91, с второго выхода формирователя 23 через Первьй вход узла 29.поступает на первьй вход мультиплексора 138 (фиг.10), на второй и управляющий входы которого подаются соответственно величина f с выхода элемента 134 задержки и двоичный код () величины /J(F)/4 с выхода регистра 139. На выходе формируется признак

n(f ,,

который с второго выхода узла 29 передается через третий вход узла 26 . в регистр 108,

На заключительном (2Т+11)-м такте операции величина выхода регистра 108 подается на управлянвдий вход элемента 115 задержки и на второй вход формирователя 112, на первьй вход -которого через, четвертый вход узла 26 с первого выхода узла 12 поступает величина л)(С), В зависимости от значения величина Ясл последнем регистре элемента 115 задержки и регистре 116 формируются соответствующие значения числителя нормализованной мантиссы и порядка произведения. В случае, если S1 ел выходах 44 и 45 мантиссы произведения и порядка произведения устройства получают соответственно величины J(C) и ;(С), а в случае, если Ясл величины J(C ) и v(C) - 1. Значение при- , знака переполнения П, считывается с выхода 46 мультипликативного переполнения устройства, а на выходе 40 устройства появляется сигнал окончания операции умножения чисел с плавающей запятой, п

III. Операция масштабирования числа в устройстве занимает (Т+3) такг тов. Процесс ее вьтолнения подробно описан в пункте I для числа А. В. отличие от рассмотренного в пункте I случая модулярный код числа, подлежащего масштабированию, вводится в ре- , гистр 15, а номер 1 масштаба Sf входа 5 устройства через группу мультиплексоров 79 ( Г 0) узла подается на третий вход узла 27 формирования результатов масштабирования. На пер- вом же такте операции модулярный код (f,, .,.,0(, ) числа через группу мультиплексоров 85 ( Г 0) узла 13 подается на первый адресный вход блока 19 и через группу мультиплексоров 17 ( Г, 0) поступает в блок 16 вычисления интервального индекса.числа.

Далее для числа А выполняются действия, аналогичные описанным в пункте I для числа В. По окончании операции промасштабированное значение числа А снимается с выхода 47, а на выходе 41 арифметического устройства вырабатывается единичный сигнал.

IV, Рассмотрим вьтолнение операций определения знака числа.

Модулярный код (/,, ..., о( ) числа А, знак которого нужно определить, вводится в регистр 15. На первом такте модулярный код числа А с первого выхода регистра 15 через группу мультиплексоров 22 ( Г,о 1) поступает на первый вход формирователя 23 интервальных характеристик модулярного кода (фиг.6), где передается на первый вход узла 91. На (Т+1)-м такте работы машинный интервальный индекс i (А) числа А с третьего выхода узла 91 через группу мультиплексоров 93 ( fjj 0) подается на второй вход узла 91, на вто- ром выходе которого по истечении (Т+2)-го такта формируется знак S(A), числа А, передающийся на знаков выход 43, а на вькоде 42 устройства вырабатывается единичный сигнал, Операция определения знака в предлагаемом устройстве может быть начата, если на выходе 38 устройства вырабаты-

вается сигнал Г

18

О,

При реализации в предлагаемом арифметическом ус.тройстве операции сложения (вычитания) с плавающей запятой на выходе 37 появляется единица уже на втором такте, в случае операции умножения с плавакяцей запятой - на третьем и на первом такте (для операций масштабирования и определения знака числа). Это означает что, начиная с указанных моментов времени, в устройстве может быть инициирована любая новая операция.

Формула изобретения

Арифметическое устройство в модулярной системе счисления, содержащее блок синхронизации, блок модульного умножения, узел предварительной обработки мантисс, регистры первого и второго операндов, первый блок вычисления интервального индекса, три группы мультиплексоров, два блока хранения констант, блок групп элементов ИЛИ, группу блоков суммирования

е

5 0 5 о

5

п c

0

5

вычетов, формирователь интегральных характеристик модулярного кода, блок вычисления интервального индекса произведения, узел формирования результатов операции умножения, узел формирования результатов масштабирования, узел формирования результатов операции сложения и элемент задержки, причем установочный вход устройства, вход кода операции устройства, вход сброса устройства и тактовый вход устройства соединены соответственно с установочным входом, входом задания режима, входом обнуления и тактовым входом блока синхронизации, установочный вход устройства соединен с входом разрешения приема регистра первого операгща и с первым входом разрешения приема регистра второго операнда, второй вход разрешения приема которого соединен с первым выходом блока синхронизации, входы мантиссы первого и второго операндов устройства соединены соответственно с первыми информационными входами регистров первого и второго операндов, первые выходы которых соединены соответственно с первым и вторым информационными входами узла предварительной обработки мантисс, первый выход регистра первого операнда соединен с входом первого сомножителя блока модульного умножения, вход второго сомножителя которого соедине н с первым выходом регистра второго операнда, второй информационный вход которого соединен с первым выходом узла предварительной обработки мантисс, второй выход которого соединен с первым информационным входом мультиплексоров первой группы, выходы которых соединены с входом первого блока вычисления интервального ивдекса и с первым адресным входом первого блока хранения констант, второй адресный вход которых соединен с первым адресным входом блока хранения констант и с вторым выходом узла предварительной обработки мантисс, первый выход регистра второго операнда соединен с вторыми информационными входами мультиплексоров первый группы и с третьим адресным входом первого блока хранения констант, в ыходы которого соединены соответственно с входами первой группы блока групп элементов ИЛИ, входы второй группы которого соеди- нещл соответственно с выходами, кроме

старшего, второго блока хранения констант, выходы блока групп элементов ИЛИ и старший выход второго блока хранения констант соединены соответ- Ственно с входами блоков суммирования вычетов группы, выходы суммы и Мисла переполнений которых соединены роответственно с первым и вторым вхо- узла формирования результатов Масштабирования 5 первый выход которо- о является выходом результата мас- птабирования устройства, второй выход узла формирования результатов масштабирования соединен с вторым ад ресным входом второго блока хранения констант, выход блока модз льного умножения соединен с третьим информаци- энным входом мультиплексоров первой группы, выход блока вычисления интерЬального индекса произведения и выход Злока модульного умножения соединены соответственно с первым и вторым ин I )ормационны чи входами узла формирова- результатов операции умножения, п ервый и второй выходы которого является соответственно выходом мантиссы произведения устройства и выходом чультикативного переполнения устрой- ртва, выход мантиссы суммы которого роедннен с первым выходом узла формирования результатов операции сложения lepBbrfi выход форг-шрователя интеграль- кых характеристик модулярного кода лвляется знаковым выходом устройства выходы блока синхронизагдии с второго то девятьш соединены соответственно р управляющим входом блока вычислени Интервального индекса произведения, р управляющим входом узла формирова- Иия результатов умножения, с выходом ригнапа готовности устройства, с управляющими входам - мультиплексоров Первой группы, с первым и вторым входами разрешения вьщачи первого блока хранения констант, с управлякяцими входами мультиплексоров третьей группы, с управляющими входами мультиплексоров второй группы, отличающееся тем, что, с целью расши- рения области применения ,за счет обработки операндов, представленных в форме с плавающей запятой, оно содержит узел обработки операндов, узе контроля аддитивного переполнения, второй блок вычисления интервального ивдекса, четвертую и пятую группы мультиплексоров, причем входы порядков первого и второго операндов сое

- с

5

динены соответственно с вторым информационным входом регистра первого операнда и третьим информационным входом регистра второго операнда, вторые выходы регистров первого и второго операндов соединены соответственно с первым и вторым информационными входами узла обработки порядков, третий информационный вход которого является входом номера масштаба устройства, первьй выход узла контроля аддитивногр переполнения соединен с первым входом узла формирования результатов операции сложения и с первыми информахщонными входами мультиплексоров второй группы, вторые информационные входы которых соединены с первым выходом регистра первого операнда, выходы мультиплексоров второй группы соединены с первым информационным входом формирователя интегральных характеристик модулярного кода, второй выход которого соединен с первым информационным входом узла контроля аддитивного переполнения, второй, третий и четвёртый информационные входы которого соединены соответственно с вьгходами мультиплексоров четвертой и пятой групп, с выходом второго блока вычисления интервального индекса, информационный вход которого соединен с выходами мульти- : плексоров третьей .группы, третий и четвертый выходы узла формирования результатов операции умножения соединены соответственно с выходом порядка произведения устройства и с первыми информационными входами мультиплексоров третьей группы, вторые информационные входы которых соединены с третьим выходом узла предварительной обработки мантисс, четвер- тьй выход которого соединен с первым информационным входом блока вычисления интервального индекса произведения, второй, третий информационные входы которого соединены соответственно с выходами суммы блоков суммирования вычетов группы и с вьпсодом первого блока выч исления интервального индекса, первьй выход узла формирования результатов масштабирования соединен с входом элемента задержки, четвертьй выход узла формирования результатов операции умножения соединен с первыми информационными входами мультиплексоров четвертой и пятой групп, первый и второй выходы элемента задержки соединены соответственно с вторыми информационными входами мультиплексоров пятой группы и с третьими информационными входами мульти плексоров третьей группы, вторые ин- формационные входы которых соединены соответственно с вторыми информационными входами мультиплексоров четвертой группы, второй выход угла кон троля аддитивного переполнения и первый выход узла обработки порядков соединены соответственно с третьим и четвертым информационными входами узла формирования результатов операции умножения, второй и третий выходы узла обработки порядков соединены соответственно с тре,тьим входом узла формирования результатов масштабирования и с первым управляющим входом узла предварительной обработки мантисс, входы с второго по пятый узла формирования соединены соответственно с третьим выходом узла контроля аддитивного переполнения, с третьим выходом формирователя интегральных характеристик модулярного кода, с вторым выходом узла контроля аддитивного переполнения и с первым выходом узла обработки порядков, третий выход узла контроля аддитивного переполнения соединен с вторым информационным входом формирователя интегральных характеристик модулярного кода, выход первого блока вычисления интервального индекса соединен с четвертым входом узла формирования результатов масштабирования, второй и третий выходы узла формирования результатов операции сложения являются выходом порядка суммы устройства и выходом аддитивного переполнения устройства, вькоды с десятого по двадцать первьй блока синхронизации соединены соответственно с вторым управляющим входом узла предварительной обработки мантисс, с управляющим входом узла контроля аддитивного переполнения, с управлянхцим входом второго блока вычисления интервального индекса, с входом разрешения вьщачи второго блока хранения констант, с управляющим входом формирователя интегральных характеристик модулярного кода, с объединенными управляющш т входами мультиплексоров четвертой и пятой групп, с управляющим входом узла обработки порядков, с выходами сигнала запрета, сигнала окончания операции типа сложения, сигнала окончания операции типа сложения, сигнала окончания операции умножения, сигнала окончания операции масштабирования, сигнала окончания операции определения знака устройства, установочный вход которого соединен с третьим управляющим входом узла предварительной обработки мантисс.

3f 35

43

S ЦВ «7

ФигЛ

)

10S:

i07

т

103

fO

/f;

т

т

т

| Арифметическое устройство в системе остаточных классов | 1979 |

|

SU857992A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1356821, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1988-10-23—Публикация

1987-02-16—Подача