входом второго элемента ИЛИ, с вторым входом второго сдвигового регистра и с первым выходом третьего коммутатора, соединенного входом через формирователь импульсов с первым входом блока управления, вторым выходом с соответствующим вторым выходом блока управления, другой второй выход которого соединен с третьим входом первого элемента ИЛИ и с первым выходом триггера ошибок, второй выход KOToi ro соединен с пятым входом второго элемента ИЛИ, а вход - с соответствующим ВТО1ЯФ1 выходом блока управления, с четвертым выходом и с третьим входом сдвигового регистра, выходы счетчика адреса, третьего,, четвертого и пятого элементов ИЛИ соединены соответственно с пятым, третьим и четвертым выходами блока управления.

2.Устройство по п, 1, о т Ли чающееся тем, что первый коммутатор содержит транзисторы, соединенные коллекторами с вторил выводом коммутатора, базами - с соответствующими третьими выводами коммутатора, эмиттералш - с соответствующими первыми выводами коммутатора.

3.Устройство по п. 1 и 2, о т личающееся тем, что блок сброса содержит элемент памяти и транзистор, соединенный коллектором с выходом блока сброса, эмиттером с общей шиной устройства, базой - с выходом элемента памят соединенного первым и вторым входами соответственно с первым и вторым входами блока сброса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля сопротивления изоляции электромонтажа | 1982 |

|

SU1167547A1 |

| Устройство для автоматического контроля сопротивления изоляции электромонтажа | 1985 |

|

SU1267301A1 |

| Устройство для автоматического контроля электромонтажа | 1985 |

|

SU1272286A1 |

| Устройство для контроля монтажа | 1986 |

|

SU1312616A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2341850C1 |

| Устройство для трассировки межсоединений | 1984 |

|

SU1208560A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Устройство сопровождения и адресования объектов на конвейере | 1990 |

|

SU1813687A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| Устройство для контроля правильности соединений электромонтажа | 1988 |

|

SU1553927A1 |

1, УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МОНТАЖА, содержащее блок питания, блок управления, соединенный первым выходом с первым входом блока программ, вторыми выходами - с первыми входами блока регистрации, первый коммутатор, соединенный первыми.выводами с соответствующими клеммами для подключения контролируемого монтажа, первый и второй регистры, первый и второй дешифраторы, отличающееся тем, что, с целью повышения надежности и быстродействия устройства, в него введены резистор нагрузки., блок сброса, блок элементов И и конденсаторы, соединенные первыми выводами с общей шиной устройства, вторыми выводами с соответгствующими первыми выводами первого коммутатора, соединенного вторым выводом через нагрузочный резистор с выходом блока питания, непосредственно с первым входом блока управления и с выходом блока сброса, соединенного первым и вторым входами соответственно с первыми и вторыми входами первого и второго регистров и с третьим и четвертым выходами блока управления, соединенного пятым выходом с третьими входами первого и второго регистров, вторым и третьим входами соответственно с первым и вторым выходами блока программ, соединенного вторым и третьим выходами с соответствующими вторым и третьим входами блока регистрации- и сдответствуквдими входами первого и второго дешифраторов , соединенных выходами с четвертыми входами соответственно первого и второго де114ифраторов, выходы которых соединены с третьими выводами первого коммутатора, причем блок управления содержит Формирователь импульсов, второй и третий коммутаторы, триггер режима, триггер ошибки, первый, второй, третий, четвертый и пя.тый элементы ИЛИ, первыйи второй сдвиговые регистры и задающий генератор, соединенный выходом с первым входом второго коммутатора, соединенного вторым входом с рторым входом блока управления и с первым входом третьего коммутатора, третьим вхолдом - с выходом триггера режима и с СО вторым входом третьего коммутатора, первым выходом - с первыми входами первого и второго элементов ИЛИ, вторым выходом - с вторым входом второго элемента ИЛИ и с первым входом третьего элемента ИЛИ, третьим выходом - с первым входом первого сдвигового регистра, четвертым входом с первым входом второго сдвигового 1; : :л регистра, соединенного первым выходом с первым входом четвертого эле- мента ИЛИ, вторым выходом - с вторым входом третьего элемента ИЛИ, третьим выходом - с первым входом пятого элемента ИЛИ, соединенного вторым Э входом с nepBfciM выходом первого сдвигового регистра, второй выход которого соединен с вторым входом четвертого элемента ИЛИ, третий выход - с третьим входом третьего элемента ИЛИ, четвертый выход - с собственным вторым входом и с третьим входом второго элемента ИЛИ, соединенного выходом с первым входом счетчика адреса, соединенного вторым входом с третьим - входом блока управления и с входом триггера режима, третьим-входом - с .выходом первого элемента ИЛИ, соедиIjjeHHoro вторым входом с четвертым

Изобретение относится к контрольно-измерительной технике и может быть использовано для проверки электрического монтажа различных радиоэлектронных узлов и блоков, содержащих большое количество монтажных точек ,

Известны устройства для автоматической проверки монтажа, работающие по принципу выявления и распознавания всех монтажных соединений, имеющихся в проверяемом изделии, и сравнении найденных связей с эталоном.

Известно устройство для проверки монтажа, содержащее регистр, счетчик регистратор гальванических связей, блок управления и блок сравнения 1

Недостатком известного устройства является низков быстродействие вследствие длительного контроля каждого контакта относительно другого.

Наиболее близким к изобретению техническим решением является устройство для контроля монтажа, содержащее блок питания, блок управления, соединенный первьш выходом с первым входом блока программ, вторыми выходами - с первыми входами блока регистрации, первый кс 1мутатор, соединенный первьк4и выводами с соответствующими клеммами для подключения контролируемого монтажа, первый и второй регистры, первый и второй дешифраторы 2.

Недостатками известного устройства являются низкая надежность и быстродействие. Низкая надежность обусловлена нг1личием второго коммутатора

число элементов коммутации которого велико, и для монтажа, содержащего тысячи контролируемых точек, исчисляется также тысячами, а низкое быстродействие обусловлено тем, что проверка монтажа для каждой иэ точек осуществляется заданием возбуждающего воздействия на эту точку и опросом состояний всех других точек, что

0 приводит к значительному числу проверок .Цель изобретения - повышение на,дежности и быстродействия устройства.

Поставленная цель достигается тем,

- что в устройство для контроля монтажа, содержгицее блок питания, блок уп-. равления, соединенный первым выходом с первЕлм входом блока -прогргимм, вторыми выходами - с первыми входами

0 блока регистрации, первый коммутатор, соединенный первыми выводами с соот-г «ветствуюадими клеммами для подключе. ния контролируемого монтажа, первый и второй регистры, первый и второй

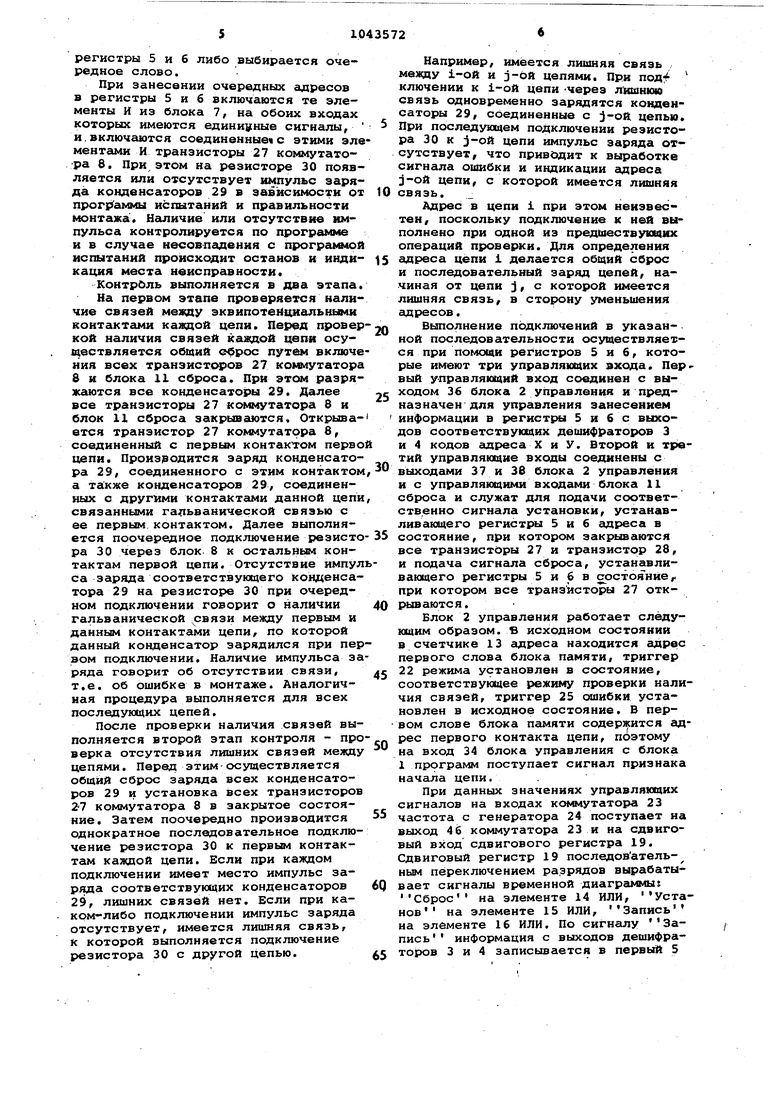

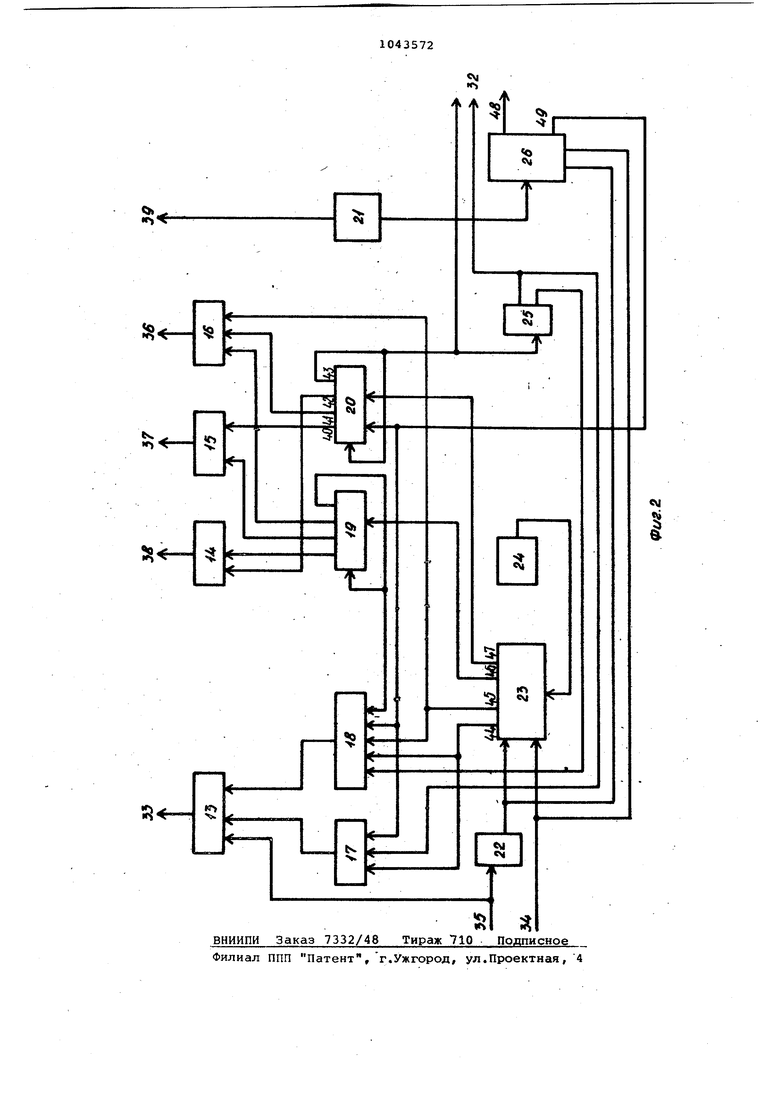

5 деишфраторы, введены резистор нагрузки, блок сброса, блок элементов И и конденсато яд, соединенные первыми выводами с общей шиной устройства, вторыми выводами с соответствующими первыми выводами первого коммутатора, соединенного вторым выводом через нагрузочный резистор с выходом блока питания. Непосредственно с первым входом блока управления и с выходом 5 блока сброса, соединенного первым и вторым входами соответственно с первыми и вторыми входами первого и вто рого регистров и с третьим и четвештым выходами блока управления, соеди ненного пятым выходом с третьими вхо дами первого и второго регистров, вторым и третьим входами соответственно с первым и вторым выходами бло ка программ, соединенного вторым и третьим выходами с соответствующими вторым и третьим входами блока регистрации и соответствующими входами первого и второго дешифраторов, соединенных выходами с четвертыми входа ми соответственно первого и второго дешифраторов, выходы которых соедине ны с третьими выводами первого комму татора, причем блок управления содер жит формирователь импульсов, второй и третий коммутаторы, триггер режима, триггер ошибки, первый, второй, третий, четвертый и пятый элементы ИЛИ, первый и второй сдвиговые регистры и Зёщающий генератор, соединенный выходом с первым входом второго коммутатора, соединенного вторым входом с вторым входом блока управления и с первым входом Третьего коммутатора, третьим входом - с выходом триггера режима и с вторым входом третьего коммутатора, первымвыходом - с первыми входами первого и второго элементов ИЛИ, вторым выходом - с вторым входом второго элемента ИЛИ и с первым входом третьего элемента ИЛИ, третьим выходом - с первым входом первого сдвигового регистра, четвертым входом - с первым входом второго сдвигового регистра, соединенного первым выходом с первым входом четвертого элемента ИЛИ, вторым выходом - с вторым входом третье го элемента ИЛИ, третьим выходом - с первым входом пятого элемента ИЛИ, соединенного вторым входом с первым выходом первого сдвигового регистра второй выход которого соединен с вто рым входом четвертого элемента ИЛИ, третий выход - с третьим входом трет его элемента ИЛИ, четвертый выход - с собственным вторым входом и с трет им входом второго элемента ИЛИ, соединенного выходом с первым входом счетчика адреса, соединенного вторым входом с третьим входом блока управления и с входом триггера режима, третьим входом - с выходом первого элемента ИЛИ, соединенного вторым . входом с четверты л входом второго элемента ИЛИ, с вторым входом второго сдвигового регистра и с первым , выходом третьего коммутатора, соединенного входом через формирователь импульсов с первым входом блока управления, вторым выходом с соответствующим вторым выходом блока управ ления, другой второй выход которого соединен с третьим входом первого элемента ИЛИ и с первым выходом три гера ошибок, второй выход которого соединен с пятым входом второго эле мента ИЛИ, а вход с соответствующим вторым выходом блока управления, с четвертым выходом и с третьим входом второго сдвигового регистра, выходы счетчика адреса, третьего, четвертого и пятого элементов ИЛИ соединены соответственно с пятым, третьим и четвертым выходами блока управления. Причем первый коммутатор содержит транзисторы, соединенные коллекторами с вторым выводом коммутатора, базами - с соответствующими третьими выводами коммутатора, эмиттерами - с соответствующими первыми выводами коммутатора. Кроме того, блок сброса содержит элемент памяти и транзистор,.соединенный коллектором с выходом блока сброса, эмиттером - с общей шиной устройства, базой - с- выходом элемента памяти, соединенного первым и вторым входами соответственно с первым и вторым входами блока сброса. На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2 схема блока управления. Устройство содержит блок 1 программ, блок 2 управления, первый 3 и второй 4 дешифраторы,первый 5 и второй 6 регистры, блок 7 элементов и первый коммутатор 8, объект 9 контроля, блок 10 регистрации, блок 11 сброса, элемент 12 памяти, счетчик 13 адреса, пятый 14, четвертый 15,. третий 16, первый 17 и второй 18 элементы ИЛИ, первый 19 и второй 20 сдвиговые регистры, формирователь 21 импульсов, триггер 22 режима, второй коммутатор 23, задающий генератор 24, триггер 25 ошибки, третий ксялмутатор 26, первые транзисторы 27, второй транзистор 28, конденсаторы 29, нагрузочный рези.стор 30, блок 31 пита- ния, второй выход 32, первый выход 33, второй вход 34, третий вход 35, пятый выход 36, третий выход 37, чет1вертый вьисод 38, первый вход 39 блока 2 управления, выходы 40-43 регистра 20, выходы 44-47 коммутатора 23, :выходы 48 и 49 коммутатора 26. Блок программ может быть реализован, например, на блоке памяти. Устройство работает следующим образом. В блоке 1 хранится программа контроля монтажа, представляющая собой слова, каждое из которых включает коды адресов (коды адреса X и коды адреса У) эквипотенциальных контактов и записанный в виде кода в последнем разряде слова признак. По сигналам блока 2 из блока 1 выбирается очерёдное слово,первые X разрядов которого дешифруются дешифратором 3, вторые У разрядов - дешифратором 4. В зависимости от значения последнего разряда слова адреса X и У с выходов дешифраторов записываются а регистры 5 и 6 либо выбирается очередное слово. При занесении очередных адресов в регистры 5 и б включаются те элементы И из блока 7, на обоих входах которых имеются единичные сигналы, и.включаются соединенные с этими эл ментами И транзисторы 27 коммутатора 8. При этом на резисторе 30 появляется или отсутствует импульс заряда конденсаторов 29 в зависимости от прогр аммы испытаний и правильности монтажа, Нсшичие или отсутствие импульса контролируется по программе и в случае несовпадения с програ ««ой испытаний происходит останов и индикация места неисправности. Контроль выполняется в два этапа На первом этапе проверяется наличие связей меяву эквипотей1шальными контактами каяздой цепи. Перед провер кой наличия связей каждой цепи осуществляется общий оброс путем вкдооче ния всех транэистс ов 27 коммутатора S и блока II сброса. При этшл разряжаются все конденсаторы 29. Далее все транзисторы 27 коммутатора 8 и блок 11 сброса закрываются. Открывается транзистор 27 коммутатора 8, соединенный с первым контактом перво цепи. Производится заряд конденсатора 29, соединенного с этим контактом а также конденсаторов 29, соединенных с другими контактами данной цепи связанными гальванической связью с ее первым контактом. Далее выполняется поочередное подключение резисто ра 30 через блок 8 к остальным контактам первой цепи. Отсутствие импул са заряда соответствующего конденсатора 29 на резисторе 30 при очередном подключении говорит о наличии гальванической связн между первым и данным контактами цепи, по которой данный конденсатор зарядился при пер вом подключении. Наличие импульса за ряда говорит об отсутствии связи, т.е. об ошибке в монтаже. Аналогичная процедура выполняется для всех последующих цепей. После проверки наличия связей выполняется второй этап контроля - про верка отсутствия лишних связей между цепями. Перед этим осуществляется общий сброс заряда всех конденсаторов 29 и установка всех транзисторов 27 коммутатора 8 в закрытое состояние. Затем поочередно производится однократное последовательное подключение резистора 30 к первым контактам каждой цепи. Если при каждом подключении имеет место импульс заряда соответствующих конденсаторов 29, лишних связей нет. Если при каком-либо подключении импульс заряда отсутствует, имеется лишняя связь, к которой выполняется подключение резистора 30 с другой цепью. Например, имеется лишняя связь между i-ой и j-бй цепями. При под ключении к i-ой цепи Через лишнюю связь одновременно зарядятся конденсаторы 29, соединенные с j-ой цепью. При последующем подключении резистора 30 к j-ой цепи импульс заряда отсутствует, что приводит к выработке сигнала ошибки и индикации адреса j-ой цепи, с которой имеется лишняя связь. Адрес в цепи 1 при этом неизвестен, поскольку подключение к ней выполнено при одной из предшеству1а1|1ис операций проверки. Для определения адреса цепи 1 делается общий сброс и последовательный заряд цепей, начиная от цепи j f с которой имеется лишняя связь, в сторону уменьшения гщресов. Выполнение подключений в указанной последовательности осуществляется при помощи регистров 5 и б, которые имеют три управляющих входа. Пер вый управляющий вход соединен с выходом 36 блока 2 управления и предназначен для управления занесением информации в регистры 5 и б с выходов соответствующих дешифраторов 3 и 4 кодов адреса X и У. Второй и третий управляющие входы соединены с выходами 37 и 38 блока 2 управления и с управляющими входами блока 11 сброса и служат для подачи соответственно сигнала установки, устанавливающего регист1ил 5 и б адреса в состояние, при котором заклеиваются все транзисторы 27 и транзистор 28, и подача сигнала сброса, устанавливающего регистры 5 и б в состояние,, при котором все транзисторы 27 открываются. Блок 2 управления работает следующим образом. В исходном состоянии в счетчике 13 адреса находится адрес первого слова блока памяти, триггер 22 режима установлен в состояние, соответствующее режиму проверки наличия связей, триггер 25 (яиибки установлен в исходное состояние. В первом слове блока памяти содержится адрес первого контакта цепи, поэтому на вход 34 блока управления с блока 1 программ поступает сигнал признака начала цепи. При данных значениях управляющих сигналов на входах коммутатора 23 частота с генератора 24 поступает на выход 46 коммутатора 23 и на сдвиговый вход сдвигового регистра 19. Сдвиговый регистр 19 последовательным переключением разрядов вырабатывает сигналы временной диаграммы; Сброс на элементе 14 ИЛИ, Установ на элементе 15 ИЛИ, Запись на элементе 16 ИЛИ. По сигналу Запись информация с выходов дешифраторов 3 и 4 записывается в первый 5

и второй 6 регистры, открьшается транзистор 27 коммутатора 8, соединенный с перовым контактом цепи, и заряжаются все конденсаторы 19, сов диненные с первым контактом.

При этом на нагрузочном резисто-- ре появляется импульс заряда, который поступает на вход формирователя 21,приводящего этот импульс к стандартному виду; С выхода формирователя 21 импульс поступает на вход коммутатора 26, состояние управляющих входов которого, соединенных с входа ш 34 и 35 блока 2 в режиме проверки наличия связей с первым контактом цепи, запрещает дальнейшее прохождёние импульса.

Последний разряд сдвигового регистра 19 соединен с входом элемента 18 ИЛИ, через который подается импульс, увеличивающий код адреса; записанный в счетчике 13, на единицу,, после зтого на выходе блока 1 появляется код адреса след пощего контакта первой цепи, урове.нь на входе 34 блока 2 меняется и тактовые импульсы начинают поступать с выхода 45 коммута тора 23 на счетчик 13 и элемент 16 ИЛИ для записи адреса в регистры 5 и 6 и для выбора слова из блока 1 памяти. Если при этом на входе формирователя 21 появляется импульс заряда конденсаторов 29, через коммутатор 26 этот импульс поступает в блок 10 регистрации, где фиксируется ошибка - отсутствие связи и адрес контакта, находящегося в отрыве, поступающий с блока 1. Если ошибки нет, выбирается адрес следукяцего контакта первой цепи и выполняются те же операции.

Аналогично проверяются все контакты первой цепи и другие цепи.

В последнем слове, поступающем из блока 1 программ на блок 2, содержится признак Конец массива , который поступает на вход 35 блока 2 управления, перебрасывает триггер 22 режима и устанавливает счетчик 13 адреса в единичное состояние, :

При считывании адресов пёрвьЬс коитактов цепей в режиме проверки отсучствия лишних связей коммутатор 23 переключен сигналами по входам 34 и 35 на выход 47, импульсы с которого поступают на сдвиговый вход сдвигового регистра 20, а при считывании адресов вторых и последующих контактов цепей коммутатор 23 переключен на выход 44

с которого сигнал поступает на вход счетчика 13, при этом производится считывание следующего слова без ввода его в регистры 5. В этом режиме анализируются связи только между первыми контактами цепей.

Сдвиговый регистр 20 формирует временную последовательность Установка - Запись. После сигнала -Запись на вход формирователя 21 должен поступить импульс заряда конденсаторов 29, при этом с выхода формирователя 21 импульс через коммутатор 26 поступает на установочный вход сдвигового регистра 20, переводя его в исходное состоян11е, и через элемент 18 ИЛИ на .счетный вход счетчика 13. Если импульс заряда конденсаторов 29 на вход 39 блока 2 управления не поступает, что является признаком лишней связи., переключаются следующие разряды сдвигового регистра 20 и вырабатываются сигналы сброса (выход 42) регистра 20 и установки триггера 25 ошибки (выход 42).

В блоке 10 регистрации сигнал с выхода триггера 25 ошибки включает (сигнализацию наличия лишней связи и адреса цепи, с которой имеется лишняя связь. , ,

Далее производится второй цикл переключений сдвигового регистра 20, причем адрес в счетчике 13 остается прежним. На втором цикле после сигнала Запись импульс с входа 39 блока 2 поступает на вход формирователя 21, так как на первом цикле выполнен общий сброс. После этого выполняется последовательность oneраций, отличающаяся от указанной тем что изменение адреса в счетчике 13 происходит в сторону уменьшения адреса, так как импульсы- подаются на вычитающий вход счетчика 13 через первый элемент 17 ИЛИ ввиду измене,ния состояния триггера 25 ошибки. При подключении резистора 30 к лишней связи триггер 25 повторно вырабатывает сигнал ошибки, который поступает в блок 10 регистрации.

Таким образом, использование конденсаторов 29, блока 11 сброса и резистора 30 позволяет исключить из устройства второй коммутатор, что повьваает его нгщежность, и производить опрос каждой точки однократно, повышая тем самым быстродействие устройства.

«ft

M

f «o Ч

J±

D

«М

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ОБНАРУЖЕНИЯ НЕИСПРАВНОСТЕЙ В ЭЛЕКТРИЧЕСКОМ МОНТАЖЕ | 0 |

|

SU288420A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для проверки электрических соединений | 1972 |

|

SU507835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-09-23—Публикация

1982-05-28—Подача