Изобретение относится к вычислительной технике и может быть использовано для автоматического проектирования межсоединений элементов при разработке печатных плат, при построении изображения принципиальных и блок-схем на экране индикационного устройства, а также для определения траектории движения.

Цель изобретения - упрощение устройства.

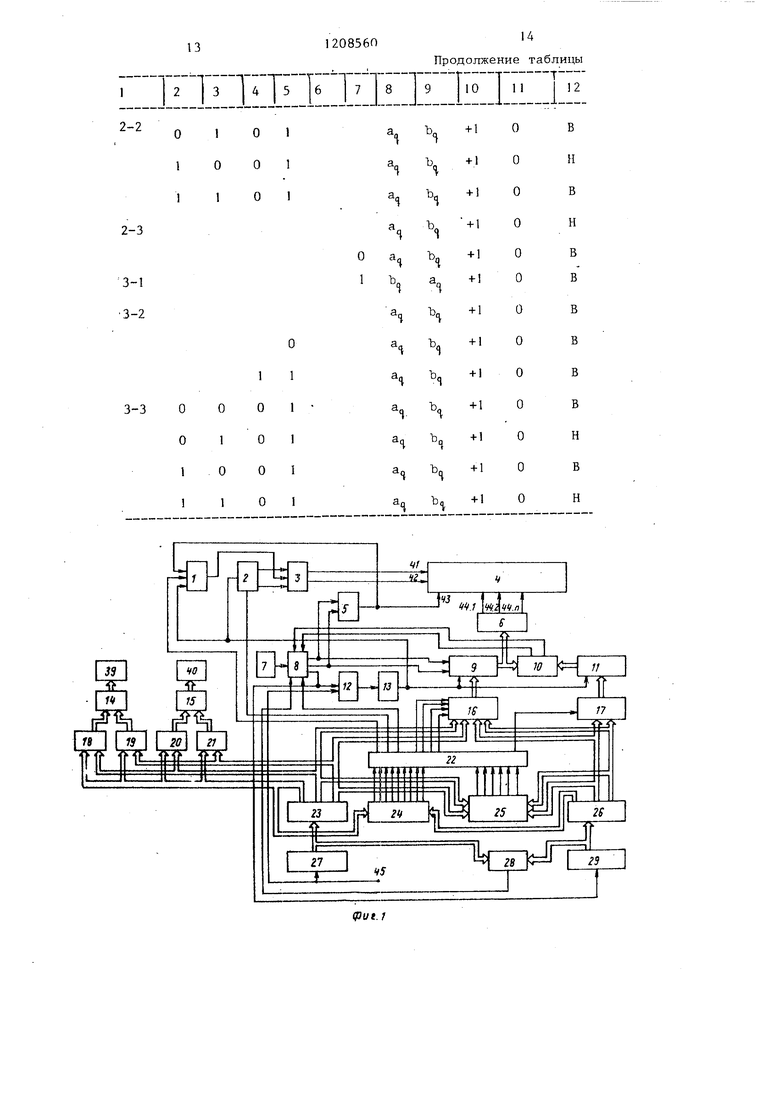

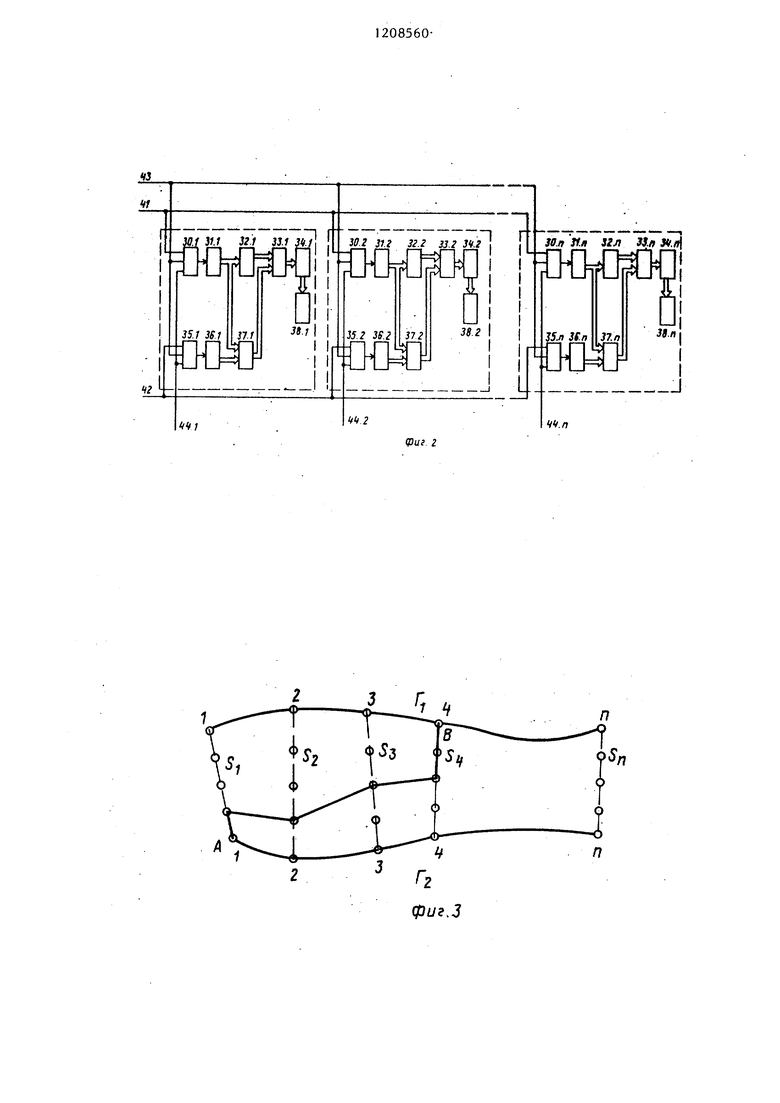

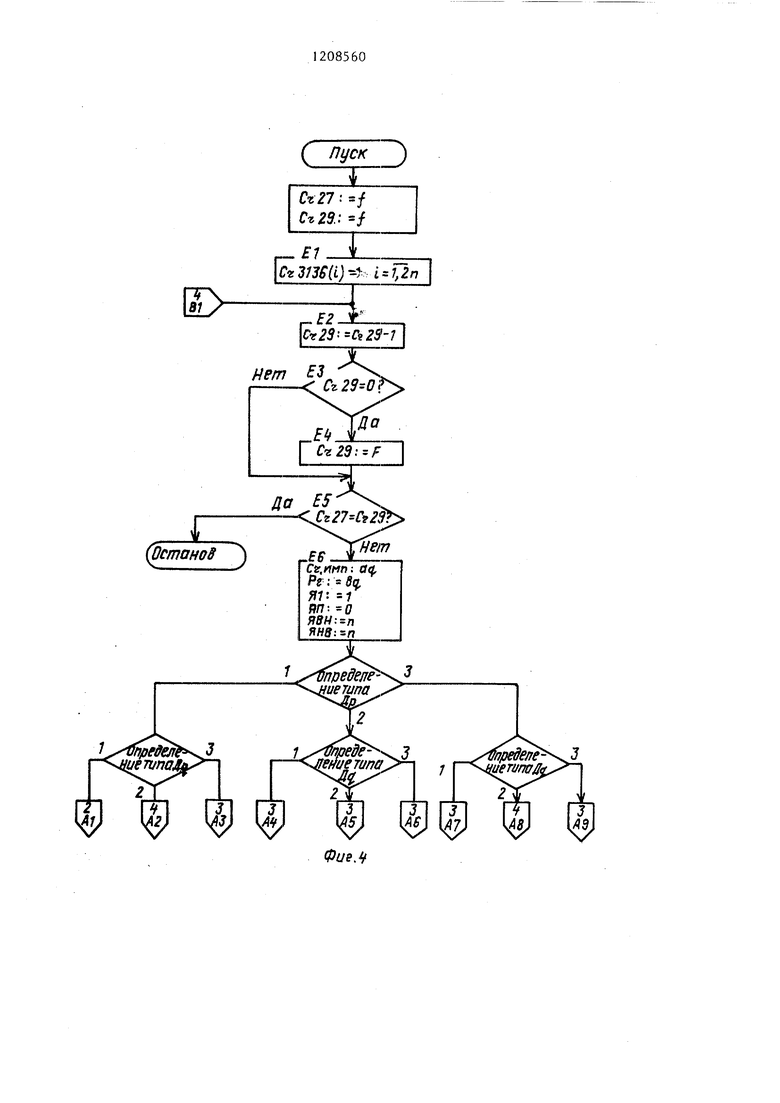

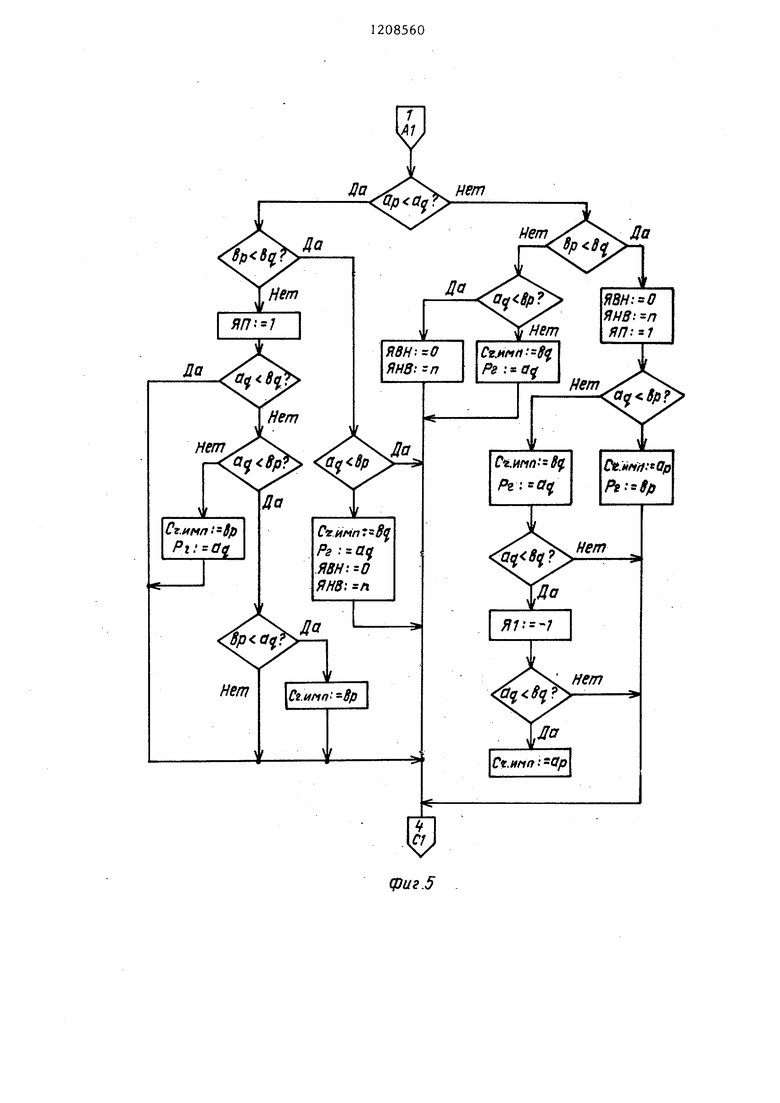

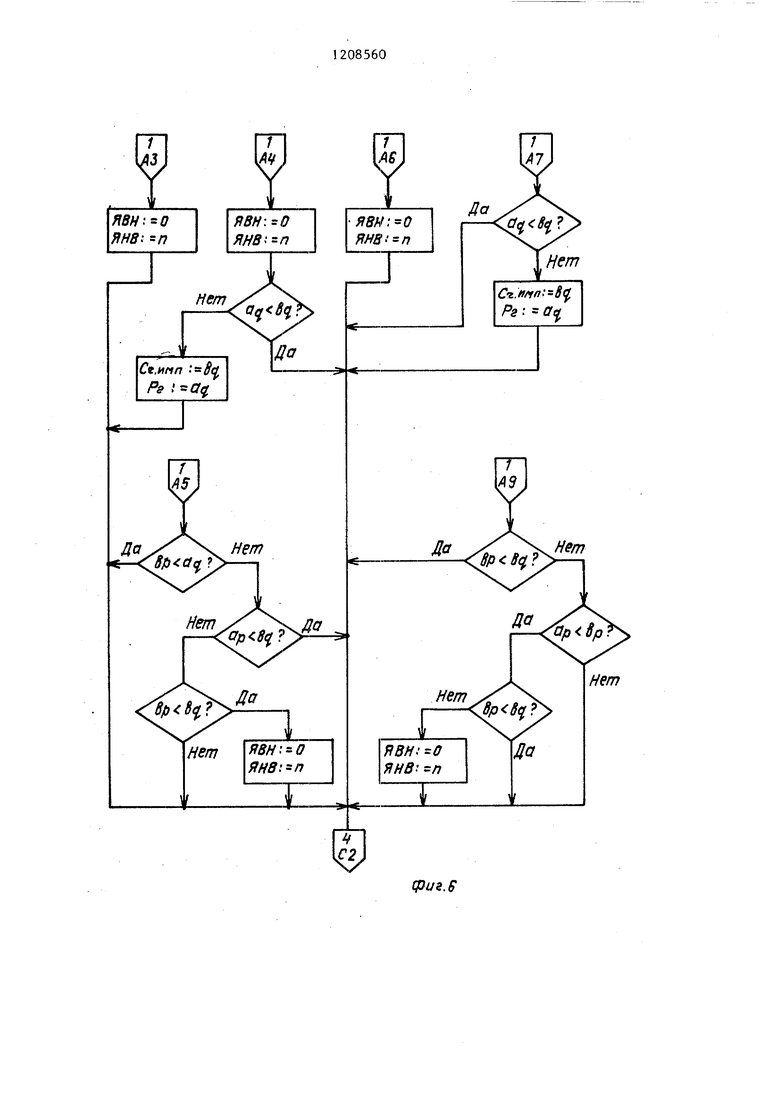

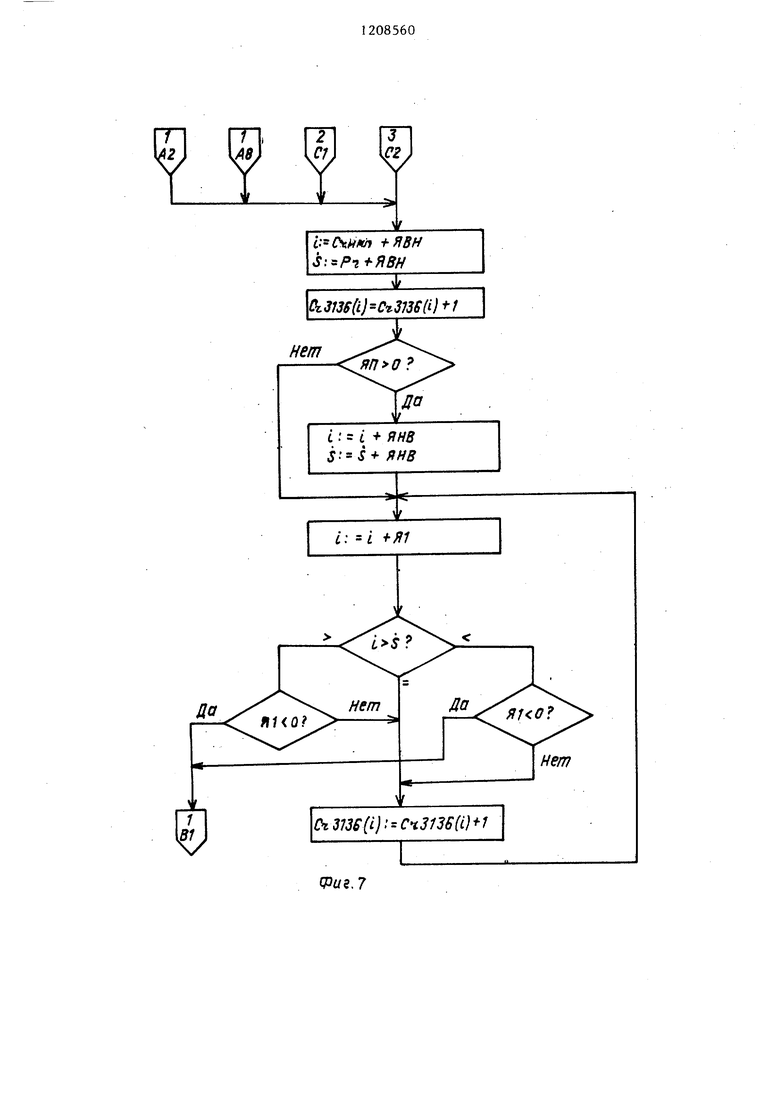

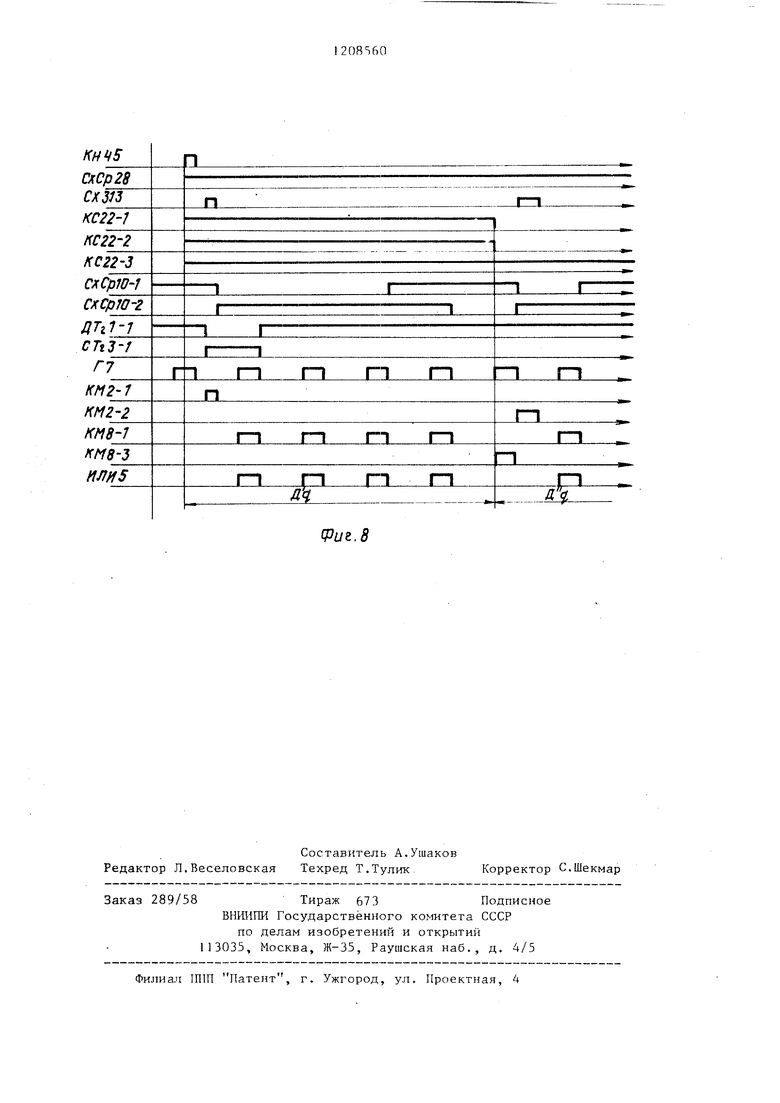

На фиг. 1 приведена функциональная схема устройстваi на фиг. 2 - функциональная схема операционного блока на фиг. 3 - пример проведения очередного соединения; на фиг.4 7 - алгоритм работы устройства; на фиг. 8 - временные диаграммы работы устройства.

Устройство содержит первый триггер. 1, второй коммутатор 2, второй триггер 3, операционный блок 4, первый элемент 5 ИЛИ, первый дешифратор 6, генератор 7 тактовых импульсов, первый коммутатор 8,, реверсивный счетчик 9, вторую схему 10 сравнения, регистр 11, второй элемент 12 ИЛИ, элемент 13 задержки, первую 14 и вторую 15 группы элементов ИЛИ, первый и второй мультиплексоры 16 и 17, третий-шестой дешифраторы 18-21, шифратор 22, первый блок 23 памяти, второй дешифратор 24, блок 25 сравнения, второй блок 26 памяти, первый счетчик 27 адреса, первую схему 28 сравнения, второй счетчик 29 адреса.

Операционный блок 4 содержит и решающих ячеек, каждая из которых включает первый элемент 30.1 И (,п), первый счетчик 31 .i, умножитель 32,1 на константу, делитель 213., дешифратор 34.i, второй элемент 35.1 И, второй счетчик 36.i сумматор 37.1, группу элементов 38.t индикации.

Кроме того, устройство содержит первую и вторую группы элементов индикации 39 и 40, первый и второй входы 4 и 42 выбора режима блока 4, вход 43 синхронизации блока 4 и входы 44.1-44.П разрядов информационного входа блока 4, вход.45 перезапуска устройства.

Устройство работает следующим образом.

Трассировка выполняется меясду .двумя ЛИ1ШЯМИ - верхней и нижней.

на которых расположены контакты, которые могут являться концами соединений. Количество контактов на верхней и нижней линиях одинаково

5 и равно и. Один контакт может являться концом только одного соединения. Соединением является непрерывная линия, концами которой являются два контакта. Каждому кон- такту на верхней линии соответству- €;т один элемент индикации из первой группы 39 элементов индикации, а каждому контакту на нижней линии - элемент из второй группы 40 элементов

5 индикации. Контакты на верхней и нижней линиях пронумерованы слева направо. Между контактами, имеющими одинаковые номера i , расположены в линию Я-2,1 +2 группы элементов

20 индикации 38.i.

Трассы разных соединений получаются последовательно. Для очередного соединения на каждой полоске включается один элемент индикации.

25 Кроме того, включаются два элемента индикации, соответствующие контактам на верхней или на нижней или один на верхней, а другой на нижней линиях. Эти элементы инди30 кации отмечают конечные точки соединения. Остальные точки соединения получаются путем проведения отрезков прямых линий между сосед- ними включенными элементами инди35 кации, лежащими между конечными точками. После получения трассы одного соединения происходит перезапуск устройства и получается трасса следующего соединения. Причем трассы

40 получаются такими, что у любых двух соединений имеется не более одной

общей точки - точки пересечения. Следовательно, при данных условиях соединения проводятся с минимумом пересе- 45 чений, причем проводятся все заданные соединения.

Пример проведения очередного соединения показан на фиг. 3.

Буквами Г, и Г обозначены со- 50 ответственно верхняя и нижняя линии, а конечные точки соединения обозначены буквами А и В. Полоски обозначены буквами S, ,3, . . . ,S, а элементы индикации обозначены кружками. 55 принцип получения трасс заключается в следующем.

При построении трассы очередно- го соединения рассматриваются ос3

тальные соединения и на каждом отрезке S-, через который проводится соединение, определяется, сколько соединений проводится выше, сколько ниже, отрезок делится в соответствующей пропорции и определяется номер элемента индикации, который должен быть включен. Поэтому на каждом отрезке S- цпя каждого соединения включаются разные элементы индикации. Этим обеспечивается отсутствие совпадений частей соединений, кроме конечного числа точек. Каждому отрезку S; соответствует своя решающа ячейка в блоке 4, причем в счетчике 31. получается код числа В-, равного числу соединений, проводящихся выше очередного соединения плюс единица, в счетчике 36,i - увеличенный на единицу код числа соединений, расположенных ниже очередного соединения, решающая ячейка

(B;+1)-R

реализует функцию

S +Hi+2

На

выходе делителя 33. i получается код элемента индикации, который дешифрируется дешифратором 34.i дпя включения одного элемента из группы 38 . В группе 38J содержится R-2 элементов индикации.

Код в первых 31.1-31.П и вторых 36.1-36.П счетчиках для каждого соединения получается следующим образом. В исходном состоянии счетчики содержат единицу. Далее при паове- дении одного соединения последовательно рассматриваются остальные соединения.

При рассмотрении одного соединения единица прибавляется в счетчики с индексами, значение которых принадлежит интервалу, концами которого являются номера контактов, являющихся концами рассматриваемого соединения. Причем единица может прбавляться только в первые, только во вторые или в первые и вторые счечики. В последнем случае между проводимым и рассматриваемым соединениями имеет место пересечение.

Каждое соединение представлено описанием,i которое содержит три числа. Первое число является кодом, обозначающим тип соединения. Считается, что имеются три типа соединений: соединения, связываюш 1е между собой контакты, лежащие на верхней и нижней линиях; соединения связывающие контакты, лежащие на

08560

верхней линии: соединения, связывающие контакты, лежащие на нижней линии. Вторым и третьим числами описания являются номера контактов, . которые являются концами соединения, Причем для соединения первого типа второе число описания является номером контакта, лежащего на верхней линии, а третье - номером кон10 такта на нижней линии, для соединений двух других типов второе число описания меньше третьего..

Описания соединений записаны в первом 23 и вторе.1 26 блоках памя12 ти, которые являются идентичными и содержат идентичную информацию. На первых выходах блоков 23 и 26 образуется код типа соединения, а на вторых и третьих выходах - вто2Q рые и третьи числа описания соединения. Соединение идентифицируется по его адресу в блоке памяти. Адрес очередного проводимого соединения получается в первом счетчике

25 27 адреса, адрес рассматриваемого соединения - во втором счетчике 29 адреса.

Выбор элементов индикации для обозначения концов соединения осуществляется по описанию соединения. Дпя этой цели в устройство введены дешифраторы 18 и 21 и группы элементов И 14 и 15. С помощью кода типа соединения определяются два дешифратора, которые выполняют

35 дешифрацию поступающих на их вторые входы номеров конечных контактов соединения. Если соединение относит- . СИ к второму типу, то сигнал образуется на выходах третьего .18 и

четвертого 19 дешифраторов и включаются два элемента индикации из элементов 39 индикации, для соединения третьего типа включаются два элемента из элементов 40 инди 5 кации, для первого - по одному элементу 39 и 40 групп.

При рассмотрении очередного соединения, описание которого получено на выходах второго блока 26 па50 мяти, единица прибавляется в счетчики 31.1 и 36.j () импульсами с выхода генератора 7. Код значе- шгя индекса i (или. j ) образуется на выходах счетчика 9, который де55 шифрируется первым дешифратором 6. В счетчик 9 в начале рассмотрения записывается один из четырех номеров контактов, которые являются

концами проводимого и рассматриваемого соединений, с помощью первого мультиплексора 16. Далее содер- яшмое счетчика импульсов меняется задним фронтом импульсов, поступающих на его суммирующий или вычитающий входы с первого или второго выходов первого коммутатора 8. Если в счетчике 9 записан код i , то единица прибавляется в первый 31,i либо во второй 36.1 счетчик передним фронтом импульсов, поступающих с выхода элемента 5 ИЛИ. Подача импульсов на первый или второй выходы первого 8 коммутатора прекращается тогда, когда содержимое счетчика 9 будет так отличаться от содержимого регистр 11, что следующий импульс увеличил бы рассогласование. Это обеспечивается схемой 10 и коммутатором 8, на третий управляющий вход которого поступает сигнал У, направляющий импульсы на первый или на второй выходы первого коммутатора 8, а на первый и второй управляющие входы поступает код знака разности между содержимым счетчика 9 и содержимым регистра 11. При согласовании кода знака и сигнала УЗ шифратора следующий импульс поступает на третий выход первого коммутатора 8, при этом изменяется содержимое второго счетчика 29 адреса и выбирается описание следующего соединения .Тот же импульс с третьего выхода первого коммутатора 8 через второй элемент ИЛИ 12 и элемент 13 задержки устанавливает исходное состояние счетчика 9, регистра 11, триггера и через второй коммутатор 2 устанавливает второй триггер 3. Состояние триггера 3 определяет, в какой счетчик решающей ячейки будет прибавлена, единица при данном коде t в счетчике 9: в первый счетчик 31.i 1-тя во второй счетчик 36. . Первоначальное состояние триггера 3 устанавливается выходом У шифратора. Далее проходит импульс через элемен ШШ 5, с помощью которого увел:ичи- вается на единицу код в одном из первых или вторых счетчиков 31.1 или 36.1, а также изменяется на противоположное либо остается неизменным состояние триггера 1 в зависимости от состояния выхода У шифратора 22, Если состояние триггера 1 меняется на противоположное

то меняется на противоположное и состояние триггера 3. В этом случае меняется наименование счетчико в которые прибавляются единицы по- 5 следующими импульсами с выхода первого элемента ИЛИ 5.

Прохождение импульсов на выходы первого коммутатора 8 продолжается до тех пор, пока очередной импульс

10

с третьего выхода первого коммутатора 8 не устанавливает код во втором счетчике 29 адреса равным коду в первом счетчике 27 адреса. В этом случае сигнал с выхода первой схе- мы 28 сравнения запрещает дальнейшее прохождение импульсов через первый коммутатор 8. Для построения трассы следующего соединения необходимо выполнить перезапуск устройства по входу 45, что приведет к изменению кода первого счетчика 27 адреса, а импульсами с третьего выхода первого коммутатора 8 содержимое второго счетчика 29 адреса

будет меняться в противоположную сторону до тех пор, пока после циклического пересчета коды счетчиков 27 и 28 адреса не сравняются.- Таким образом для очередного соединения рассматриваются все остальные соединения.

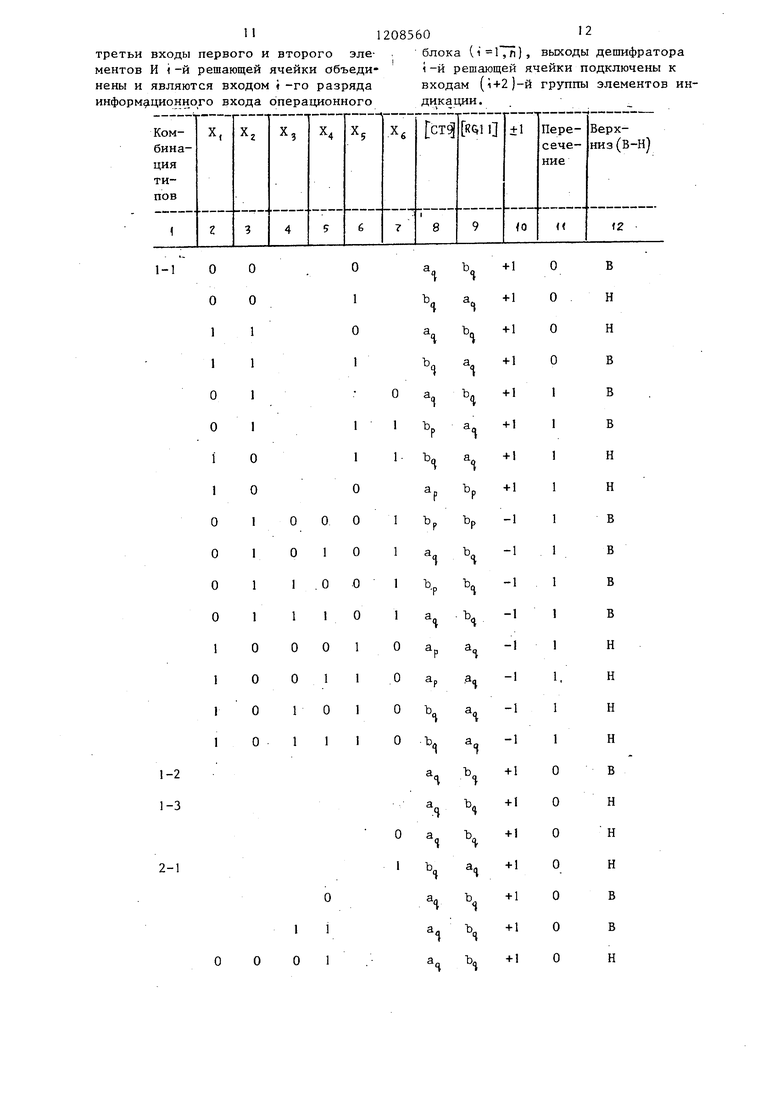

Шифратор 22, второй дешифратор 24, блок 25 сравнения являются уп- равляющей частью предлагаемого устройства. Каждый выход второго дешифратора 24 соответствует одной комбинации типов соединений. Поскольку число типов равно трем, то существует девять возможных комбинаций. Будем применять знак -.для указания соответствия. Например выход Xj дешифратора 24 равен единице в том случае, если комбинация типов равна 1-1, и нулю - в противном случае. Это обозначается . Аналогично , X,-- 2-3, X,, Х„-3-2, Х,,, Х,,, , Х,5-1-3.

Выходы блока 25 сравнения соответствуют комбинации из двух чисел, входящих в описание проводимого и рассматриваемого соединений. Пусть второе число описания проводимого соединения обозначается через а,

а третье - через Ър, второе число описания рассматриваемого соединения обозначается через а,,, а третье через Ъл. Функция f(c,d) от двух

рациональных чисел c,d, равна 1. если c7d, и нулю в противном -случае. Тогда X,f(ap,a.), (Ър,Ъ) X.(a Ъ„), Х,-(Ъ а ), (a Ър X Г(а,Ъ).

В шифраторе 22 заложена определенная система правил, которая устанавливает взаиморасположение двух любых соединений. Эта система должна обладать следующими свойствами: быть обратимой (если при проведении i-го соединения j-е соединение располагается выше, то при проведении j-го соединения i -е соединение должно располагаться ниже), быть непротиворечивой (если при проведении соединения а соединение Ъ располагается вьше, при проведении соединения Ъ соединение с располагается выше,то при проведении соединения а соединение с располагается выше, между любыми двумя соединениями должно быть не более одной точки пересечения.

Выполнение этих условий тождественно однозначной фиксадии точки пересечения между соединениями.

Точка пересечения между соединениями комбинаций типов 1-2, 1-3, 2-2, 3-3, 2-1, 3-1, 2-3, 3-2 лежит на отрезке Sj , одним из концов которого является контакт какого-то соединения. Точка пересечения между соединениями комбинации типов -1 лежит между двумя отрезками . S; и S , причем по крайней мере один из концов отрезков S; или S,-, является контактом соединения. Для того, чтобы однозначно зафиксироват точку пересечения между соединениям комбинации типов 1-1, изменение содержимого в счетчике 9 импульсов осуществляется для некоторой комбинации параметров в режиме вычитания

При составлении булевых функций, описывающих комбинационную схему, применяется представленная таблица.

В таблице единица в графе Пересечение указывает на то, что при рассмотрении одного соединения единица прибавляется в один из первых или вторых счетчиков (это определяется графой ерх-низ ), и в другие счетчики противоположного наименования. Нуль в графе Пересечение указывает, что единица прибавляется в счетчики только одного наименования, определяемого

графой Верх-низ , причем индек085608

сы счетчиков лежат между числами, записанными в графах Счетчик импульсов и Регистр. Графа t указывает,, в каком режиме работает 5 счетчик 9 импульсов - в режиме сдо- жения или вычитания. Состояния незаполненных клеток таблицы могут быть произвольными.

Таким образом, шифратор 22 дол- 10 жен реализовывать следующие логические выражения на своих с первого по восьмой выходах:

(

У Х, ,. Х2Х,-Х7+Х Х.. i5 ,,,,,ix,,+X,- У Х, У, Х,Х2Х5Х,+Х,Х,ХзХ5ХбХ7; ,XeX,X,X,+X,,X5X,X;,

,

20 У, X,X,X5X,+X,,+X,X,XjX

XgX,+X,X,,+X,X,+X,X,, Уц XjX +Xj,Xu+XgX|,.

Формула изобретения

1. Устройство для трассировки межсоединений, содержащее первый блок памяти, первый счетчик адреса, две группы элементов индикации, причем счетный вход первого счетчика адреса является входом перезапуска устройства, отличающееся тем, что, с целью упрощения устройства, в него введены второй счетчик адреса, второй блок памяти, две схемы сравнения, генератор тактовых импульсов, блок сравнения, шесть дешифраторов, две группы элементов ИЛИ, шифратор, дв мультиплексора, два коммутатора,

два триггера, два элемента ИЛИ, элемент задержки, регистр, реверсивный счетчик, операционный блок, выход первого счетчика адреса подключен к адресному входу первого

блока памяти и к первому входу первой схемы сравнения, выход признака Неравно которой подключен к входу разрешения первого коммутатора, нформационный вход которого под50

ключен к выходу генератора тактовых

импульсов, первый, второй и третий выходы первого коммутатора подключены к суммирующему и вычитающему входам реверсивного счетчика и к 55 счетному входу второго счетчика адреса соответственно,выход которого подключен к адресному входу второго блока памяти и к второму входу первой схемы сравнения, первый, второй и третий выходы первого ком14утатора п«дключены к первому и второму входам первого элемента ИЛИ и к первому входу второго элемента ШШ со- .ответственно, второй вход которого подключен к входу перезапуска устройства, выход второго элемента ШШ подключен через элемент задержки к входам сброса первого триггера, реверсивного счетчика, регистра и к информационному входу второго коммутатора, первый и второй выходы которого подключены к входам установки и сброса второго триггера, прямой и инверсный выходы которого подключены к первому и второму входам выбора режима операционного блока, выход первого элемента ИЛИ подключен к входам синхрониза дии первого триггера и операционного блока, информационный вход которого подключен к выходу первого деишф- ратора, вход которого соединен с первым входом второй схемы сравнения и с выходом реверсивного счетчика, выходы признаков Больше или равно и Меньше или равно второй схемы с равнения подключены к первому и второму управляющим входам первого коммутатора, третий управляющий вход которого подключен к первому выходу шифратора, второй и третий выходы которого подключешл соответственно к управляющему входу второго коммутатора и к информационному . входу первого триггера., с четвертого по восьмой выходы шифратора подключены соответственно к первому по четвертый управляюнщм входам первого мультиплексора и к управляющему входу второго мультиплексора соответственно, выход которого через регистр подключен к второму входу второй схемы сравнения, выходы первой группы первого блока памяти подключены к входам первой группы с второго по шестой дешифраторов, выходы первой группы второго блока памяти подключены к входам второй-группы второго дешифратора, выходы которого подключены к входам первой группы шифратора, выходы второй группы первого блока памяти подключены к информационным входам первой группы первого мультиплексора, блока сравнения и к входам вторых групп третьего и пятого дешифраторов, выходы которых под120856010

ключены к входам первой группы элементов ИЛИ первой и второй групп соответственно, выходы третьей группы первого блока памяти подключены

5 к информационным входам второй груп- пь1 первого мультиплексора, блока сравнения и к входам вторых групп четвертого и шестого дешифраторов, )зыходы которых подключены к входам .10 второй группы элементов ИЛИ первой и второй групп соответственно, выхода которых подключены к входам элементов индикации первой и второй групп соответственно, выходы второй

ts группы второго блока памяти подключены к информационным входам первой группы второго мультиплексора, третьей группы блока сравнения и третьей группы первого мультиплексора,

20 выход которого подключен к установочному входу реверсивного счетчика, выходы третьей группы второго блока памяти подключены к информационным входам второй группы второго

25 мультиплексору, четвертой группы первого мультиплексора и четвертой группы блока сравнения, выходы признаков сравнения которого под- ключены к входам второй группы шиф3Q ратора, выход первого триггера под- . ключен к счетному входу второго триггера.

2. Устройство по п. 1, о т л и- чающееся тем, что операционный блок содержит я оешаюших ячеек.

35

каждая из которых содержит два

40

45

элемента И, первый и второй счетчики, умножитель на константу, сумматор, делитель, группу элементов индикации и дешифратор, вход которого подключен к выходу делителя, вход делимого и делителя которого подключены к выходам умножителя на константу и сумматора соответственно, входы первого и второго слагаемых которого подключены к выходам первого и второго счетчиков, счетные входы которых подключены к выходам первого и BTQporo элементов И соответственно, выход первого

50 счетчика подключен к входу умножителя на константу, первые входы первых и вторых элементов И решающих ячеек являются первым и вторым входами выбора режима операционного блока

55 соответственно, вторые входы первых и вторых элементов И решающих ячеек объединены и являются входом синхронизации операционного блока.

2. Устройство по п. 1, о т чающееся тем, что опера ный блок содержит я оешаюших яч

каждая из которых содержит два

0

5

элемента И, первый и второй счетчики, умножитель на константу, сумматор, делитель, группу элементов индикации и дешифратор, вход которого подключен к выходу делителя, вход делимого и делителя которого подключены к выходам умножителя на константу и сумматора соответственно, входы первого и второго слагаемых которого подключены к выходам первого и второго счетчиков, счетные входы которых подключены к выходам первого и BTQporo элементов И соответственно, выход первого

0 счетчика подключен к входу умножителя на константу, первые входы первых и вторых элементов И решающих ячеек являются первым и вторым входами выбора режима операционного блока

5 соответственно, вторые входы первых и вторых элементов И решающих ячеек объединены и являются входом синхронизации операционного блока.

П120856012

третьи входы первого и второго эле- . блока () выходы дешифратора ментов И i-и решающей ячейки объеди- i-и решающей ячейки подключены к йены и являются входом i-го разряда входам (1+2)-й группы элементов ининформ ьционного входа операционного

ди кации.

13

1208560

--|---7з уГ7з 1б 7 8 9.

14 Продолжение таблицы

12

ЗОл Ня 32л 3J./f Л г N

З8.п

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Устройство для диспетчерской дуплексной связи | 1985 |

|

SU1293853A1 |

| Устройство для контроля монтажа | 1982 |

|

SU1043572A1 |

| СТЕНД ДЛЯ ИЗУЧЕНИЯ ЭЛЕКТРОННЫХ СРЕДСТВ АВТОМАТИЗАЦИИ | 2005 |

|

RU2279718C1 |

| Устройство для формирования гистограммы случайных чисел | 1988 |

|

SU1702391A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Устройство для контроля цифровых узлов | 1985 |

|

SU1238085A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля операционных усилителей в электронных блоках | 1988 |

|

SU1674018A1 |

Изобретение относится к области вычислительной техники и позволяет сократить затраты оборудова НИН при трассировке межсоединений. Устройство содержит первый и второй триггеры, первый и второй коммутаторы, операционный блок первый и второй элементы ИЛИ, первый, второй и с третьего по шестой дешифраторы, генератор тактовых импульсов, реверсивный счетчик, первую и вторую схемы сравнения, регистр, элемент задержки, первую и вторую группы элементов ИЛИ, первый и второй мультиплексоры, шифратор, первый и второй блоки памяти, блок сравнения, первый и второй счетчики адреса, 1 з.п. ф-лы, 8 ил. to о 00 СП а

3 г.

п

( Пдск

нет -f.

j

Е. Са.инт ал, , ftr- l ЙП: 0

Фае.

оа : //й

(риг.5

cpus.ff

Г,

2

С1

Т Т t

i:-(K/t i-ЯВН

ОсЗШ(1)Сг3135(П1 1

3

JC2 .

7

нет

L t ffHB S - S+ ЙНВ

Сгте(1).сч313бЦ) 1-1

CPUS.

иг.8

Составитель А.Ушаков Редактор Л. Веселовская Техред Т.Тулик, Корректор С.Шекмар

Заказ 289/58Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиан ШИТ Патент, г. Ужгород, ул. Проектная, 4

| Ячейка однородной сети для трассировки межсоединений радиоэлектронных схем | 1973 |

|

SU476563A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для трассировки межсоединений элементов радиоэлектронной аппаратуры | 1973 |

|

SU489111A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-30—Публикация

1984-04-21—Подача