11ПИ, выход первого триггера разрешения соединен с первым, вторым входа ш запрета первого элемента И-ИЛИ и с третьим входом третьего элемента ИЛИ, выход второго триггера разрешения соединен с первым, вторым входами запрета второго элемента И-ИЛИ и с третьим входом шестого элемента ИЛИ, информационный вход первого триггера, разрешения соединен с выходом третьего элемента И, информационный вход второго триггера соединен с выходом седьмого элемента И, выход третьего элемента -ИЛИ соедине15 с первым входо третьего элемента И, выход шестого элемента ИЛИ соединен с первым входом седьмого элемента И, выход чет- . вертого элемента И соединен с вторым входом запрета третьего элемента И, выход восьмого элемента И соединен с вторым входом запрета седьмого элемента И третьи входы запрета третьего и седьмого элементов И соединены с шиной останова-запуска этого же разряда, выход первого элемента ИЛИ соединен с первым входом запрета первого элемента И, выход второго элемента ИЛИ соединен с первым входом запрета второго элемента И, выход четвертого элемента Ш1И соединен с первым входом запрета пятого элемента И, выход пятого элемента ИЛИ соединен с первым входом запрета шестого элемента И,, информационные входы первого и второго триггеров памяти соединены с третьими входами первого и второго элементов И-ИЛИ и с шиной управления этого же разряда, выход первого триггера памяти соединен с четвертым входом первого элемента И-ИЛИ, выход второго триггера памяти соединен с четвертым входом второго элемента И-ИЛИ, выход первого элемента И-ИЛИ соединен с вторыми входами первого и второго элементов И-ИЛИ, выход второго элемента И-ИЛИ соединен с вторыми входами пятого и шестого элементов И, входы первого элемента ИЛИ каждого разряда соединены каждый со своим выходами первых элементов ИШШ всех разрядов, имеющих номер меньше данного разряда, входы второго элемента ИЛИ каждого разряда соединены каждьй со своим выходами первых элементов И-ИЛИ всех разрядов, имеющих иомер больше данного разряда, входы четвертого элемента ИЛИ каждого разряда соединены каждый со своим выходами вторых элементов

И-ИЛИ всех разрядов, инеюцих номер меньше данного разряда, входы пятого элемента ИЛИ каждого разряда соединены каждый со своим выходами вторых элементов И-ИЛИ всех разрядов, имеющих номер больше данного разряда, входы первого выходного элемента ИЛИ соединены калздый со своим выходами первых элементов И-ИЛИ всех разрядов, входы второго выходного элемента ИЛИ соединены каждый .со своим выходами вторых элементов ИШШ всех разрядов, выход первого выходного элемента ИЛИ соединен.с первым управлякщим входом триггера цикла с первым входом запрета первого отдельного элемента ИЛИ и с первым входом запрета первого отдельного элемента И, выход второго выходного элемента ИЛИ соединен с вторым управляющим входом триггера цикла, с первым входом запрета второго отдельного элемента ИЛИ и с первым входом запрета второго отдельного элемента И, прямой выход триггера цикла соединен с вторым входом первого отдельного элемента ИЛИ, с вторым входом второго отдельного элемента И и с шиной синхронизации, инверсный выход триггера цикла соединен с вторым входом второго отдельного элемента ИЛИ и с вторчым входом первого отельного элемента И, выход первого отдельного элемента ИЛИ соединен с третьими входами пятого, шестого элементов И всех разрядов, с первыми входами четвертых элементов И всех разрядов и с первыми входами запрета восьмых элементов И всех разрядов, выход второго отдельного элемента ИЛИ соединен с третьими входами первого, второго элементов И всех разрядов, с вторыми входами запрета четвертых элементов И всех азрядов и с вторыми входами восьых элементов И всех разрядов, выход первого отдельного элемента И соеинен с V -входами первых триггеров памяти всех разрядов, с четвертыми входами запрета третьгос элементов И всех разрядов и с V -входом первого

триггера направления, выход второго отдельного элемента И .соединен с -входами) вторых триггеров памяти всех разрядов, с четвертыг входами запрета седьмых элементов И всех разрядов и с V -входом второго триггера направления, выход первого отдельного элемента И-ИЛИ соединен с четвертьюш входами перв элементов И всехразрядов и с четвертыми входами запрета вторых элементов И всех разрядов выход второго отдельного элемента ИИЛИ соединен с чeтвepты в входами пятых элементов И всех разрядов и с чeтвepты flк входами запрета шестых элементов И всех разрядов, первые входы первого, второго отдельных элементов И-ИПИ соединены с инфот ма1 и-; онньвш входами первого, второго триг геров направления и с шиной выбора направления опроса,второй вход первого отдельного элемента И-ИЛИ соединен с выходом первого триггера направления, второй вход второго отдельного элемента И-ИЛИ соединен с выходом второго триггера направления, третьи прямые входы и четвертые входы запрета первого и второго отдельных элементов И-ИЛИ соединены с пятыми прямыми входами, с шестыми входами запрета первого и второго элементов И-ИЛИ всех разрядов, с входом переключения триггера цикла и с {ВИНОЙ включения непосредственного доступа, тактовые входы .первого, второго триггеров разрешения всех разрядов, первого, второго триггеров памяти всех разрядов, первого, второго триггеров направления соединены с тактовой шиной, входы уста-. новки первого, второго триггеров разрешения всех разрядов, первого, второго триггеров памяти всех разрядов и триггера цикла соединены с

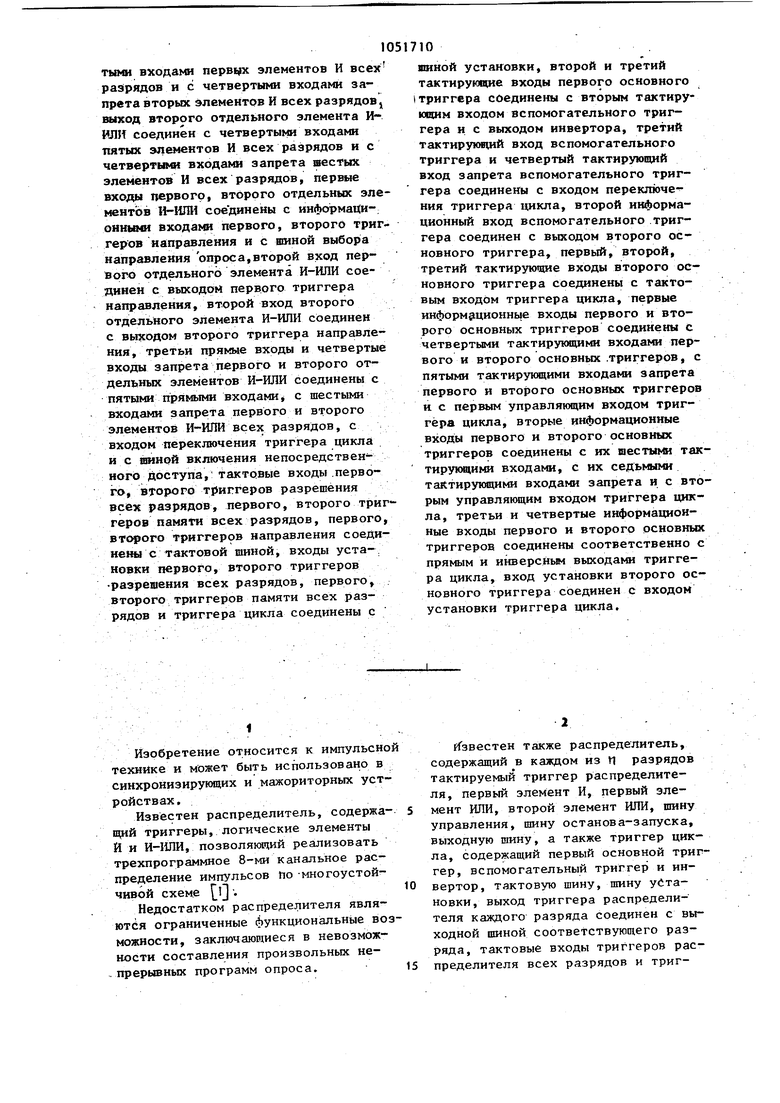

аганой установки, второй и третий тактирукпше входы первого основного (триггера соединены с вторым тактирующим входом вспомогательного триггера и с выходом инвертора, третий тактирукиций вход вспомогательного триггера и четвертый тактирующий вход запрета вспомогательного триггера соединены с входом переключе ния триггера цикла, второй информационный вход вспомогательного триггера соединен с выходом второго основного триггера, первый, второй, третий тактирующие входы второго основного триггера соединены с тактовым входом триггера цикла, первые информационные входы первого и второго основных триггеров соединены с четвертыми тактирукищми входами первого и второго основных .триггеров, с пятыми тактирующими входаьш запрета первого и второго основных триггеров и с первым управляющим входом триггера цикла, вторые информационные входы первого и второго основных триггеров соединены с их шестыми тактирующими входами, с их седьмыми таКтирукяцими входами запрета и с вторым управляющим входом триггера цикла, третьи и четвертые информационные входы первого и второго основных триггеров соединены соответственно с прямым и инверсным выходами триггера цикла, вход установки второго основного триггера соединен с входом установки триггера цикла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель | 1981 |

|

SU1001474A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Система телемеханики для циклического опроса рассредоточенных объектов | 1977 |

|

SU691912A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

| Адаптивная телеметрическая система | 1979 |

|

SU783825A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1990 |

|

SU1727126A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для сравнительного анализа п чисел | 1978 |

|

SU736090A1 |

| Способ для циклического опроса рассредоточенных объектов | 1974 |

|

SU519753A1 |

Изобретение относится к импульсно технике и может быть использовано в синхронизирующих и мажориторных устройствах.

Известен распределитель, содержащий триггеры, логические элементы И и И-ИЛИ, позволяющий реализовать трехпрограммное 8-ми канальное распределение импульсов По -многоустойчивой схеме Q .

Недостатком распределителя являютбя ограниченные бункционапьные возможности, заключающиеся в невозможности составления произвольных не. прерывных программ опроса.

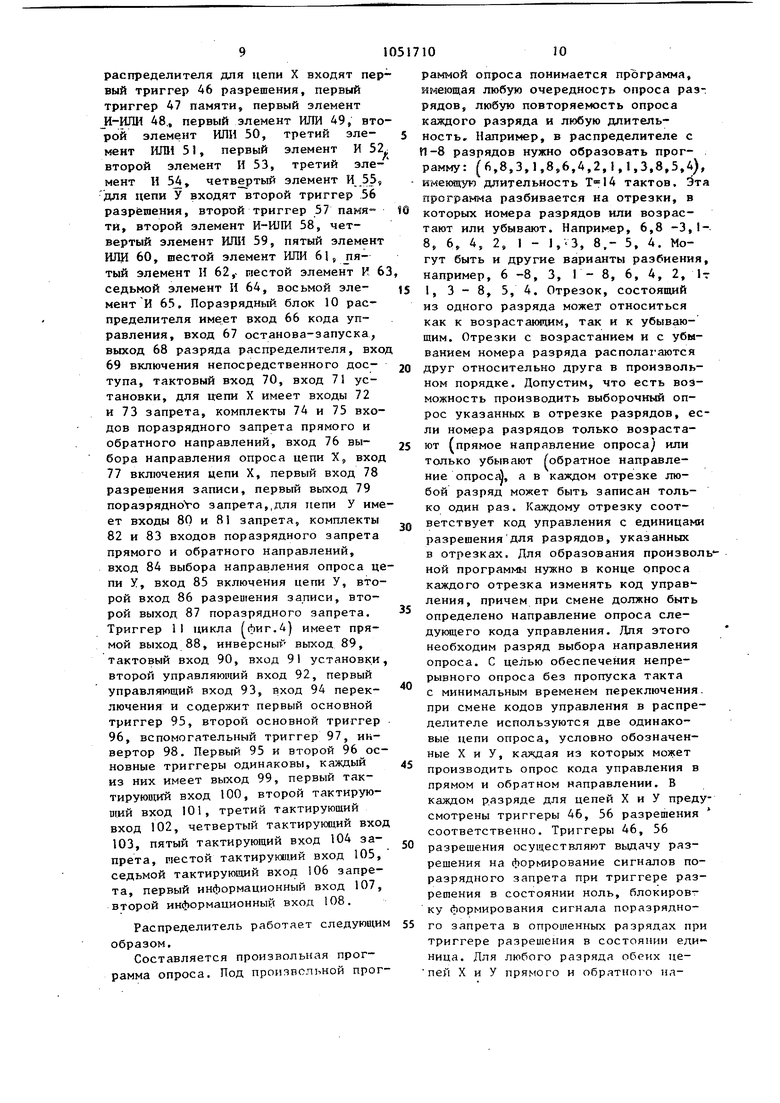

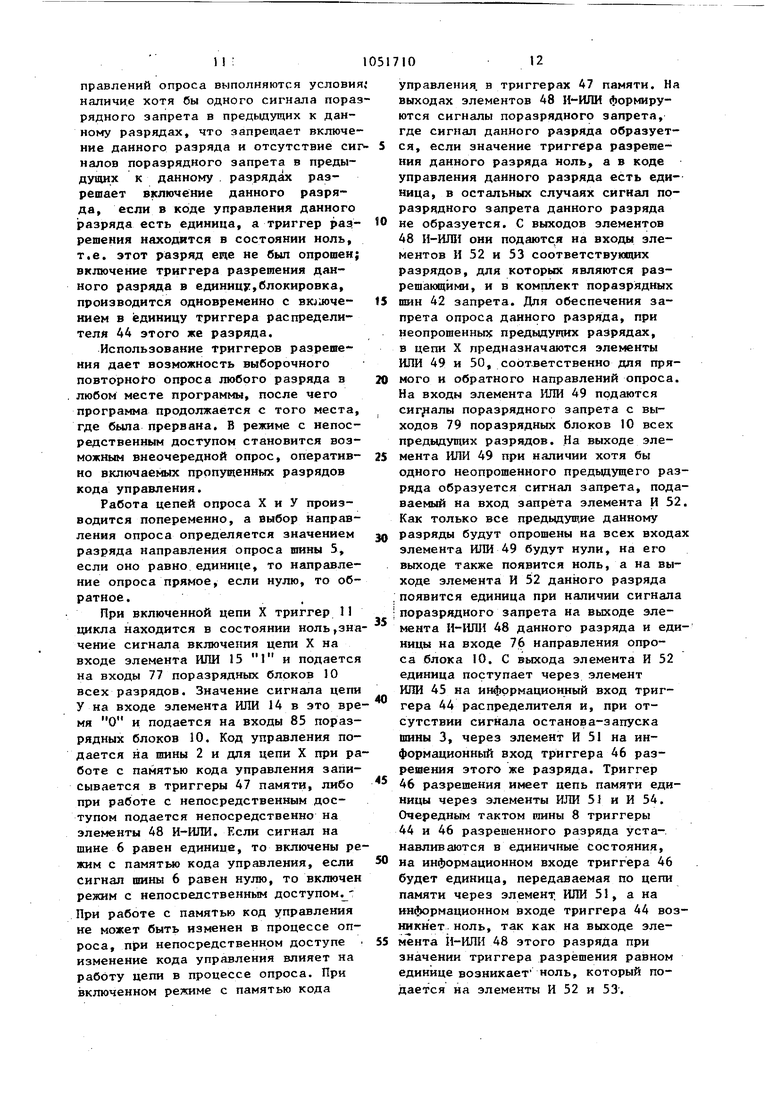

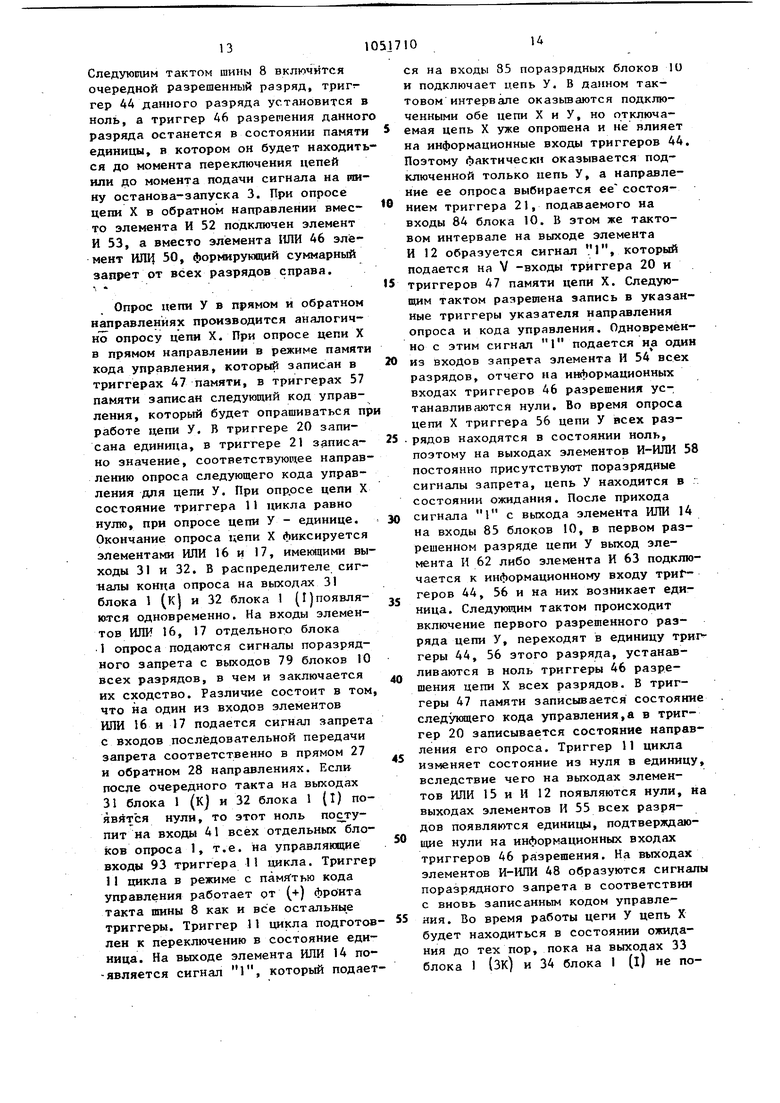

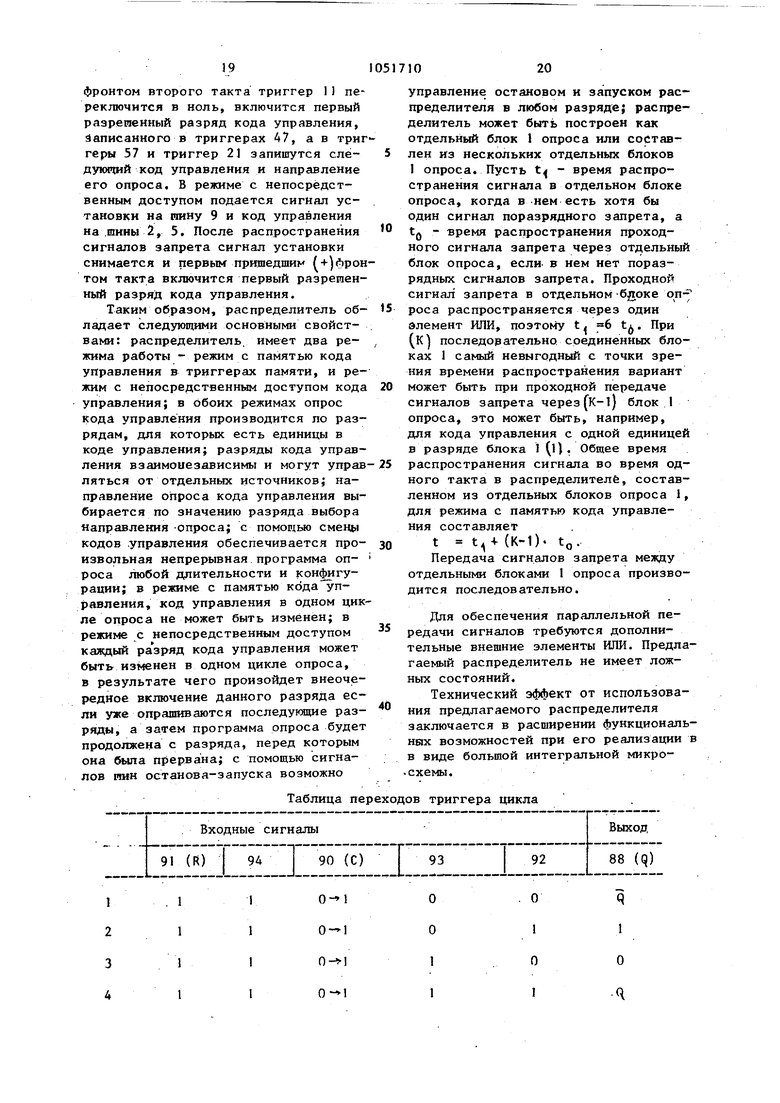

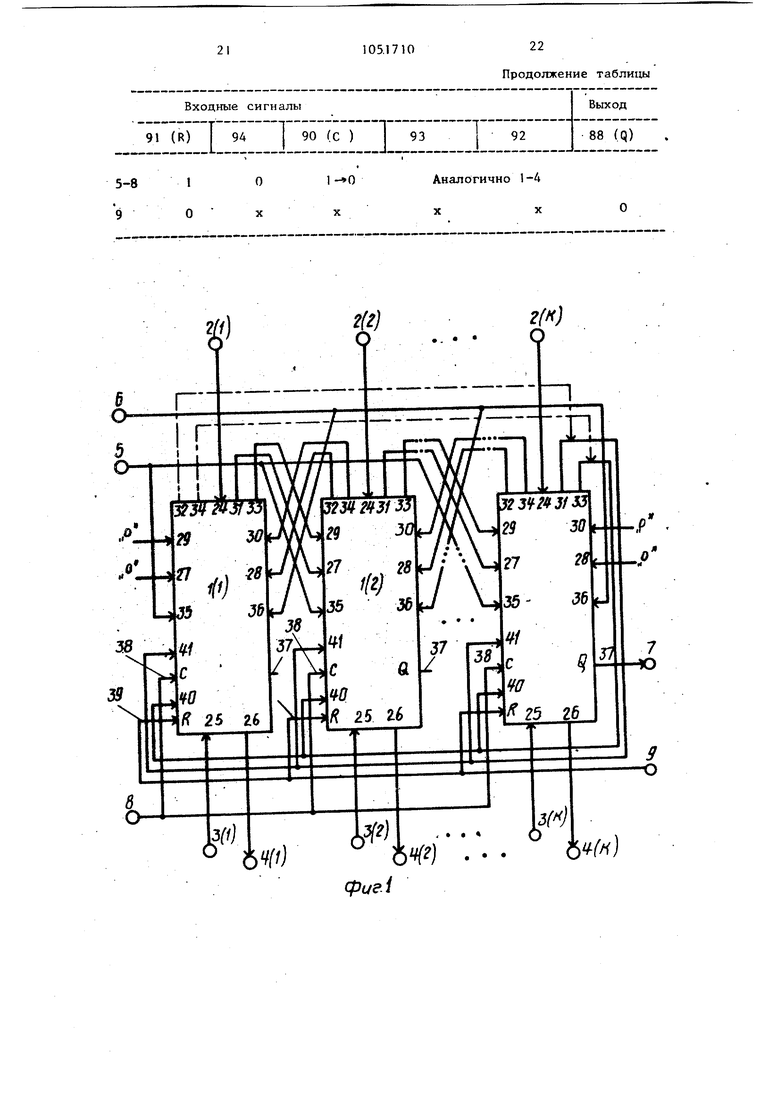

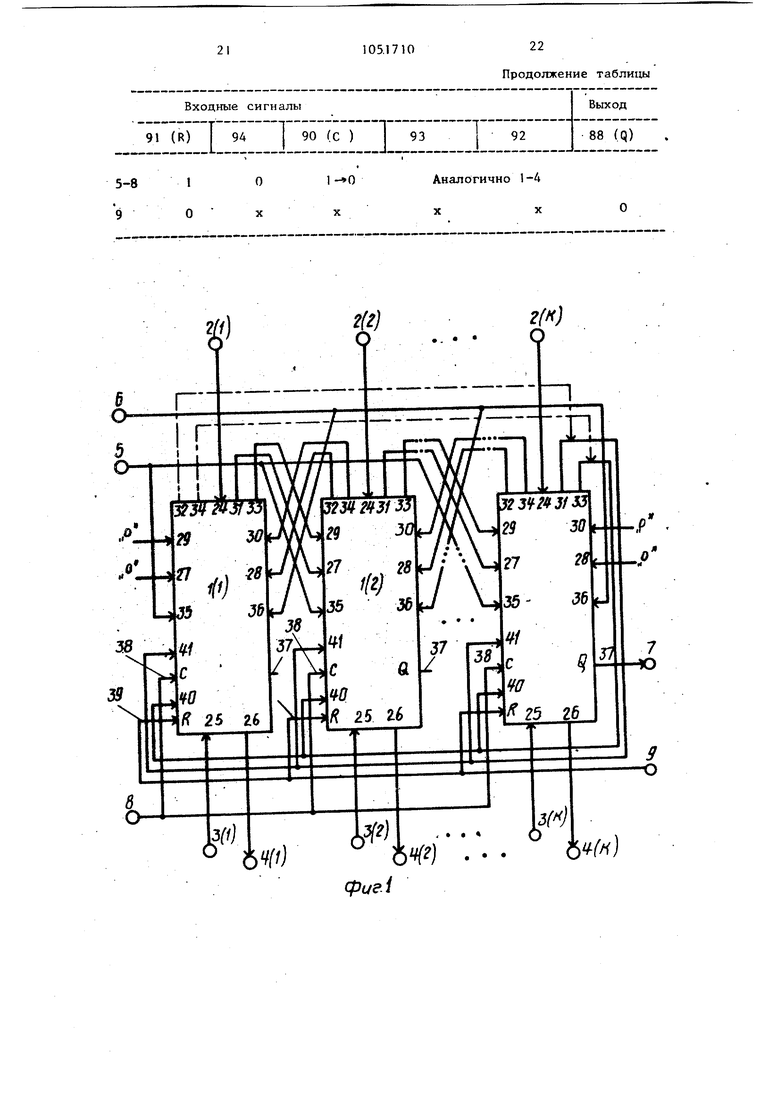

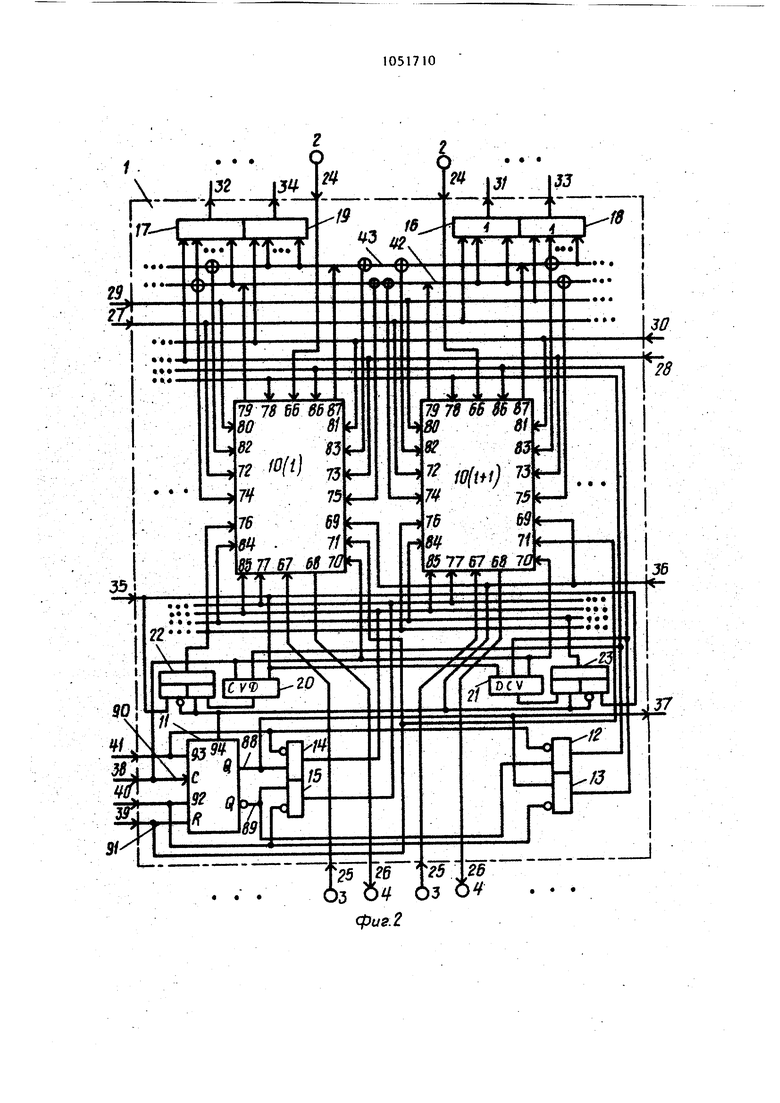

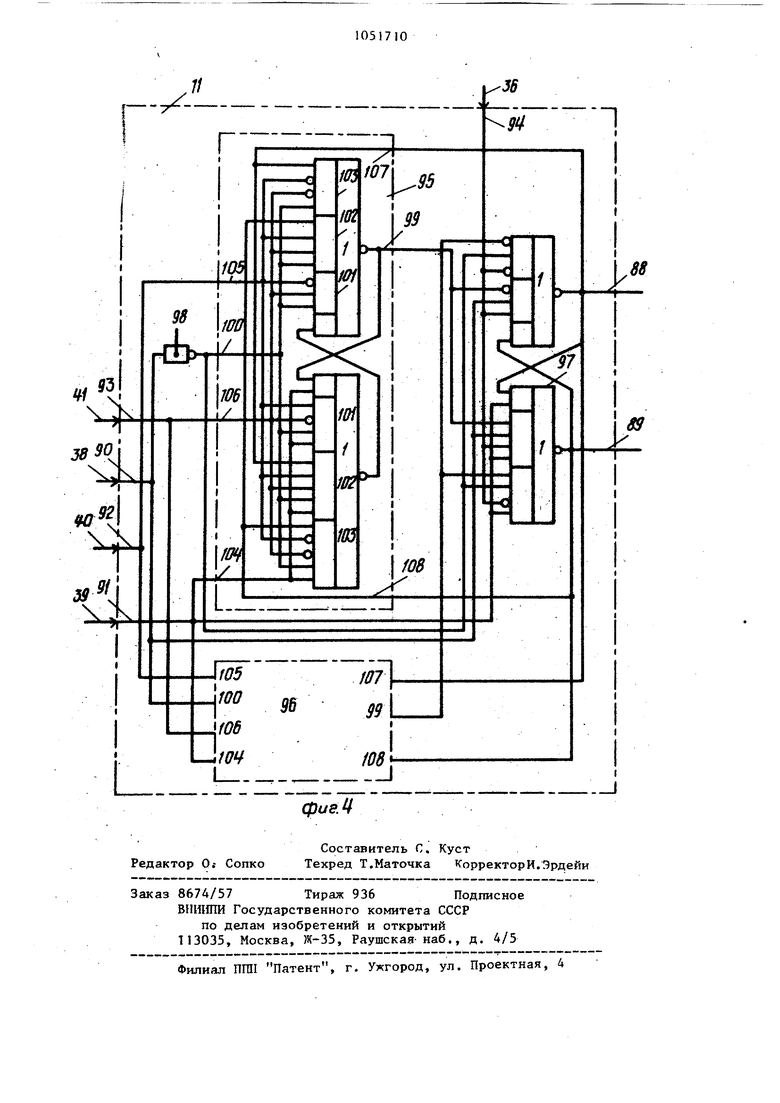

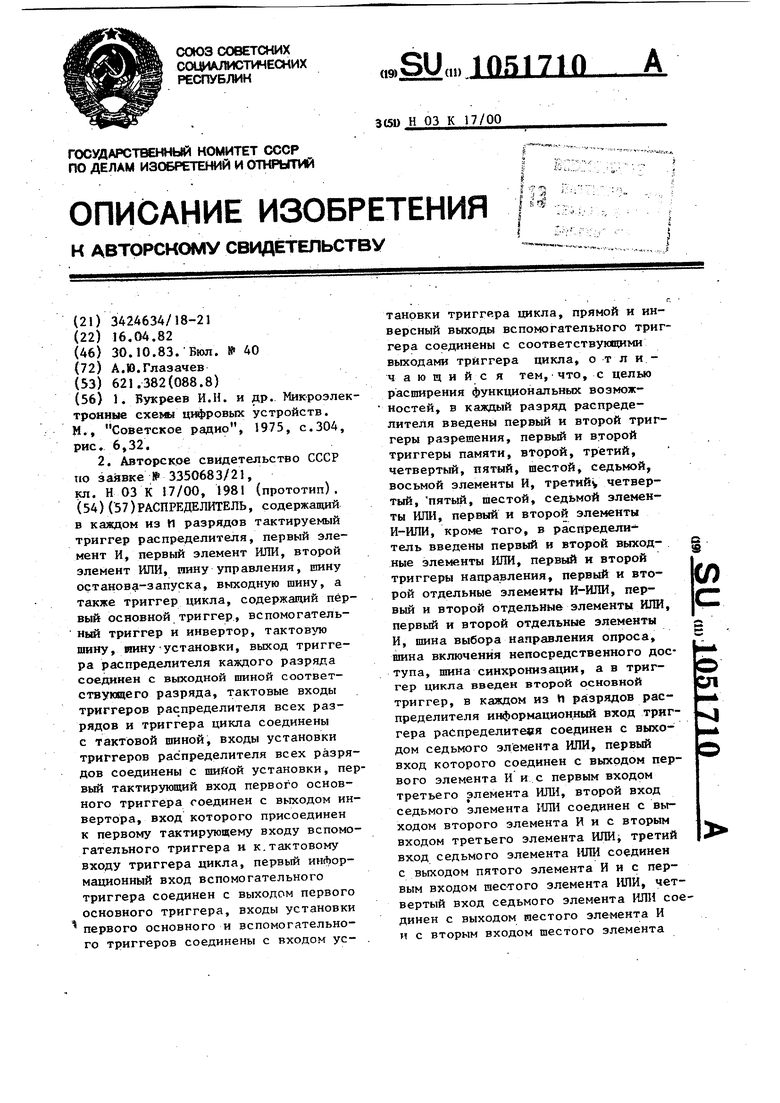

Известен также распределитель, содержащий в каждом из Ц разрядов тактируемый триггер распределителя, первый элемент И, первый элемент ИЛИ, второй элемент ИЛИ, шину управления, щину останова-запуска, выходную шину, а также триггер цикла, содержащий первый основной триггер, вспомогательный триггер и инвертор, тактовую шину, шину уйтановки, выход триггера распределителя каждого разряда соединен с выходной шиной соответствующего разряда, тактовые входы триггеров распределителя всех разрядов и триг3гера цикла соединены с тактовой шиной, входы установки триггеров распределителя всех разрядов соединены с шиной установки, первый тактирующий вход первого основного триг- гера соединен с выходом инвертора, вход которого присоединен к первому тактирующему входу вспомогательного триггера и к тактовому входу триггера цикла, первый информационный вход вспомогательного триггера соединен с выходом первого основног триггера, входы установки первого о новного и вспомогательного триггеро соединены с входом установки триггера цикл, прямой и инверсный выходы вспомогательного триггера соединены с соответствующими выходами триггера цикла 2, Однако такой переключатель харак теризуется ограниченными функционал ными возможностями, заключающикшся в отсутствии возможности составления произвольных непрерывных программ опроса, Пель изобретения - расширение функциональных возможностей распределителя , Поставленная цель достигается те что в распределителе содержащем в каждом из Я разрядов тактируемый триггер распределителя, первый элемент И, первый элемент ИЛИ, второй элемент ИЛИ, шину управления, шину останова-запуска, выходную гаину, а также триггер цикла, содержащий пер вый основной триггер, вспомогательный триггер и инвертор, тактовую шину, шину установки, выход триггера распределителя каждого разряда соединен с выходной-тпиной соответствующего разряда, тактовые входы триггеров распределителя всех разрядов и триггера цикла соединены с тактовой шиной, входы установки триггеров распределителя всех разрядов соединены с шиной установки первый тактирующий вход первого основного триггера соединен с выходом инвертора, вход которого присоедине к первому тактирующему входу вспомо гательного триггера и к тактовому входу три.ггера цикла, первый информационный вход вспомогательного триггера соединен с выходом, первого .основного триггера, входы установки первого основного и вспомогательног триггеров соединены с входом устано ки триггера цикла, прямой и инверс7104ный выходы вспомогательного триггера соединены с соответствующим выходом триггера цикла, в каждый разряд распределителя введены первый и второй триггеры разрешения первый и второй триггеры памяти, второй, тре- тий четвертый, пятый, шестой, седьмой, восьмой элементы И, третий, четвертый, пятый, шестой, седьмой элементы ИЛИ, первый и второй элементы И-ШШ; кроме того, в распределитель введены первый и второй выходные элементы ИЛИ, первый и второй триггеры направления, первый и второй отдельные элементы И-ШШ, первый и второй отдельные элементы ИЛИ, первый и второй отдельные элементы И, шина выбора направления опроса, шина включения непосредственного доступа,шина синхронизации,а в триггер цикла введен второй основной триггер в каждом из П разрядов распределителя информационный вход триггера распределителя соединен с выходом седьмого элемента ИЛИ, .первый вход которого соединен с выходом первого элемента И и с первым входом третьего элемента ИЛИ, второй вход седьмого элемента ИЛИ соединен с выходом второго элемента И и с вторым входом третьего элемента ИЛИ, третий вход седьмого элемента ИЛИ соединен с выходом пятого элемента И и с первым входом шестого элемента ИЛИ, четвертый вход седьмого элемента ИЛИ соединен с выходом шестого элемента И н с вторым входом гаестого элемента ИШ1, выход первого триггера разрешения соединен с первым, вторым входами запрета первого элемента И-ИЛИ и с третьим входом третьего элемента ИЛИ, выход второго триггера разрешения соединен с первым, вторым входами запрета второго элемента ИШШ и с третьим входом шестого элемента ИЛИ, информационный вход первого триггера разрешения соединен с выходом третьего элемента И, информационный вход второго триггера разрешения соединен с выходом седьмого элемента И, выход третьего элемента ИЛИ соединен с первым входом третьего элемента И, выход шестого элемента ИЛИ соединен с первым входом седьмого элемента И, выход четвертого элемента И соединен с вторым входом запрета третьего элемента И, выход восьмого элемента И соединен с вторым входом запрета седьмого элемента И, третьи входы запрета третьего и седьмого элементов И соединены с шиной останова-запуска этого же разряда, выход первого элемента ИЛИ соединен с первым входом запрета первого элемента И, выход второго элемента ИЛИ соединен с первым входом запрета второго элемента И, выход четвертого элемента ИЛИ соединен с первым входом запрет пятого элемента Н, выход пятого эле мента ИЛИ соединен с первым, входом запрета шестого э лемента И, информащюнные входы первого и второго триггеров памяти соединены с третьи ми входами первого и второго элемен тов И-ИЛИ и с шиной управления этого же разряда, выход первого триггера памяти соединен с четвертым входом первого элемента И-ИЛИ, выход второго триггера памяти соединен с четвертым входом второго элемента И-ИЛИ, выход первого элемента И-НЛИ соединен с вторыми входами первого и второго элементов И-ИЛИ, выкод второго элемента И-ИЛИ соединен с вторыкм входа1«1 пятого и шестого элементов И, входы первого эле мента ИЛИ каждого разряда соединены каждый со своим выходами первых эле ментов И-ИЛИ всех разрядов, имеющих номер меньшего данного разряда, вхо ды второго элемента ИЛИ каждого раз ряда соединены-каждый со своим выхо дами первых элементов И-НЛИ всех разрядов, имеющих номер больше данного разряда, входы четвертого эле,мента ИЛИ каждого разряда соединены каждый со своим выходами вторык элементов И-ИЛИ всех разрядов, имею щих номер меньше данного разряда, входы пятого элемента ИЛИ каждого разряда соединены каждый со своим выходами вторых элементов И-ИЛИ все разрядов, имеющих номер больше данного разряда, входы первого выходного элемента ИЛИ соединены каждый со своим выходами первых элементов И-ИЛИ всех разрядов, входы второго выходного элемента ИЛИ соединены ка дый со своим выходами вторых элементов И-ИЛИ всех разрядов,выход первого выходного элемента HHfi соединен с первым управляющим входом триггера цикла, с первым входом запрета первого отдельного элемента ИЛИ и с первым входом запрета первого отдельного элемента И, выход .второго выходного элемента ИЛИ соединен с вторым управляницим входом триггера цикла, с первый входом запрета второго отдельного элемента ШШ и с первым входом запрета второго отдельного элемента И, прямой выход триггера цикла соединен с вторым входом первого отдельного элемента ИЛИ, с вторым входом второго отдельного элемента И и с шиной синхронизации, инверсный выход триггера цикла соединен с вторым входом второго отдельного элемента ИЛИ и с вторым входом первого отдельного элемента И, выход первого отдельного элемента ИЛИ соединен с третьими входами пятого, шестого элементов И всех разрядов, с первыми входами четвертых элементов И всех разрядов и с первыми входами за- . прета ВОСЬМЫХ элементов И всех разрядов, выход второго отдельного элемента ИШ1 соединен с третьими входами первого, второго элементов И всех разрядов, с вторыми входами запрета четвертых элементов И всех разрядов и с вторыми входами восьмых элементов И всех разрядов, выход первого отдельного.элемента И соединен с f -входами первых триггеров памяти всех разрядов, с четвертыми входами запрета третьих элементов И всех разрядов и cV -входом первого триггера направления, выход второго отдельного элемента И соединен cV - входами вторых триггеров памяти всех разрядов, с четвертыми входами запрета седьмых элементов И всех разрядов и с V -входом второго триггере направления, выход первого отдельного элемен-ка И-РШИ сйэединен с четвертыми входами первых элементов И всех разрядов и с четвертыми входами запрета вторых элементов И всех разрядов, выход второго отдельного элемента И-ИЛИ соединен с четвертыми входами пятых элементов И всех разрядов и с четвертыми входами запрета шестых элементов И всех разрядов, первые входы первого, второго отдельных элементов И-ИЛР соединены с информационными входами первого, второго триггеров направления и с шиной выбора направления опроса, второй вход первого отдельного элемента И-ИЛИ соединен с выходом первого триггера направления, второй вход второго отдельного элемента И-ИЛИ соединен с выходом второго триггера направления третьи прямые входы и четвертые входы запрета первого и второго отдель ных элементов И-НЛ11 соединены с пятыми прямыми входами,с шестыми входами запрета первого и второго элементов Н-ИЛИ всех разрядов, с входо переключения триггера цикла и с шиной включения непосредственного дос тупа, тактовые входы первого, второго триггеров разрешения всех раэр дов, первого, второго трнггеров пам ти всех разрядов, первого, второго триггеров направления соединены с тактовой шиной, входы установки пер вого, второго триггеров разрешения всех разрядов, первого, второго триггеров памяти всех разрядов и триггера цикла соединены с шиной установки, второй и третий тактирующие входы первого основного триггера соединены с вторым тактирующим входом вспомогательного триггера и с выходом инвертора, третий тактирукщий вход вспомогательного триггера и четвертый тактирующий вход запрета вспомогательного триггера соединены с входом переключения триггера цикла, второй информационный вход вспомогательного триггера соединен с выходом второго основного триггера, первый, второй, третий тактирующие входы второго ос новного триггера соединены с тактовым входом триггера цикла, первые информационные входы первого и второго основных триггеров соединены с четвертыми тактирующими входами пер вого и второго основных триггеров, с пятыми тактирующими входами запре та первого и второго основных триггеров и с первым управляющим входом триггера цикла, вторые информационные входы первого и второго основных триггеров соединены с их шестыми тактирующим входами, с их седььяями тактирующими входами запрета и со вторым управляющим входом тригге ра цикла, третьи и четвертые информационные входы первого и второго основных триггеров соединены соответственно с прямым и инверсным выходами триггера цикла, вход установ ки второго основного триггера соединен с входом установки триггера цикла. На фиг. 1 представлена функционал ная схема И--разрядного распределителя, составленной из -разрядных отдельных блоков опрося; на фиг. функциональная схема f -разрядного отдельного блока опроса; на фиг.Зфункциональная схема поразрядного блока распределителя; иа фиг. 4 схема триггера цикла. Распределитель имеет tl -разрядов и может быть составлен из 1( и -разрядных отдельных блоков t опроса или же выполнен в виде отдельного блока 1 опроса. Разряды пронумерованы слева направо, на фиг.1 нумерация по индексу К, иа фиг.2 - по нндексу . Распределитель содержит П шин 2 управления, и гаин 3 останова-запуска, П-выходных шин 4, игину 5 выбора направления опроса, шииу 6 включения непосредственного доступа, шину 7 синхронизации, тактовую тину 8, шииу 9 установки. Распределитель имеет в своем составе две одинаковые цепи опроса, условно обозначенные X и У. Отдельный блок 1 опроса содержит поразрядных блоков 10 распределителя, по одному для каждого разряда, триггер 11 цикла, первый отдельный злемент И 12, второй отдельный элемент И 13, первый отдельный злемент КПИ 14, второй отдельный злемент ИЛИ 15, первый выходной злемент 16,третий выходной злемент ИЛИ 17,второй выходной элемент ИЛИ ИЛИ 18, четвертый выходной злемент ИЛИ 19, первый триггер 20 направления, второй триггер 21 направления, первый отдельный элемент И-ИЛИ 22, второй отдельный злемент И-ИЛИ 23. Отдельный блок 1 опроса имеет для каждого разряда входы 24 кода управления, входа 25 остановазапуска, выходы 26 разрядов распределителя, кроме того, входы 27 и 28 запрета цепи X, входы 29 и 30 запрета цепи У, выходы 31 и 32 запре- . та цепи X, входы 33 и 34 запрета цепи У, вход 35 выбора направления опроса, вход 36 включения непосредственного доступа, выход 37 цикла, тактовый вход 38, вход 39 установки, второй управляю11ий вход 40 (для включения п.епи Х) первый управляющий вход 41 /для включения цепи у) и содержит первый комплект 42 поразрядных пшн запрета 1тепи X, второй комплект 43 поразрядных шин запрета цепи У. Поразрядный блок 10 распределитея содержит тактируемый триггер 44 распределителя, седьмой элемент ИЛИ 45. В состав поразрядного блока 10 распределителя для цепи X входят пер вый триггер 46 разрешения, первый триггер 47 памяти, первый элемент И-ИЛИ 48., первый элемент ИЛИ 49, вто рой элемент ИЛИ 50, третий элемент ИЛИ 51, первый элемент И 52 второй элемент И 53, третий элемент И 5, четвертый элемент И .55, для цепи У входят второй триггер .56 разрешения, второй триггер 57 памяти, второй элемент И-ИЛИ 58, четвертый элемент ИЛИ 59, пятый элемент ИЛИ 60, шестой элемент ИЛИ 61, пятый элемент И 62, шестой элемент И 6 седьмой элемент И 64, восьмой элемент И 65, Поразрядный блок 10 распределителя имеет вход 66 кода управлеиия, вход 67 останова-запуска, выход 68 разряда распределителя, вхо 69 включения непосредственного доступа, тактовый вход 70, вход 71 установки, для цепи X имеет входы 72 и 73 запрета, комплекты 74 и 75 входов поразрядного запрета прямого и обратного направлений, вход 76 выбора направления опроса цепи Х, вход 77 включения цепи X, первый вход 78 разрешения записи, первый выход 79 поразрядноУо запрета,,для цепи У име ет входы 80 и 81 запрета, комплекты 82 и 83 входов поразрядного запрета прямого и обратного направлений, вход 84 выбора направления опроса це пи У, вход 85 включения цепи У, второй вход 86 разрешения записи, второй выход 87 поразрядного запрета. Триггер 11 цикла фиг,4 имеет прямой выход 88, инверсный выход 89, тактовый вход 90, вход 91 установки, второй управляющий вход 92, первый управляющий вход 93, вход 94 переключения и содержит первый основной триггер 95, второй основной триггер 96, вспомогательный триггер 97, инвертор 98. Первый 95 и второй 96 основные триггеры одинаковы, каждый из них имеет выход 99, первый тактирующий вход 100, второй тактирующий вход 101, третий тактирующий вход 102, четвертый тактирующий вход 103, пятый тактирующий вход 104 запрета, пестой тактирующий вход 105, седьмой тактирующий вход 106 запрета, первый информационный вход 107, второй информационный вход 108. Распределитель работает следующим образом. Составляется произвольная программа опроса. Под произвольной программой опроса понимается программа, имеющая любую очередность опроса разрядов, любую повторяемость опроса каждого разряда и любую длительность. Например, в распределителе с 11-8 разрядов нужно образовать программу: (6,8,3,1,8,6,4,2,1,1,3,8,5,4), имеющую длительность тактов. Эта программа разбивается на отрезки, в которых номера разрядов или возрастают или убывают. Например, 6,8 -3,18, 6, 4, 2, 1 - ,V3, 8,- 5, 4. Могут быть и другие варианты разбиения, например, 6 -8, 3, Г- 8, 6, 4, 2, 1т 1, 3-8, 5, 4. Отрезок, состоящий из одного разряда может относиться как к возрастающим, так и к убывающим. Отрезки с возрастанием и с убыванием номера разряда располагаются друг относительно друга в произвольном порядке. Допустим, что есть возможность производить выборочный опрос указанных в отрезке разрядов, если номера разрядов только возрастают (прямое направление опроса) или только убывают (обратное направление опрос аи, а в каждом отрезке любой разряд может быть записан только один раз. Каждому отрезку соответствует код управления с единицами разрещениядля разрядов, указанных в отрезках. Для образования произволь ной программы нужно в конце опроса каждого отрезка изменять код управ ления, причем при смене должно быть определено направление опроса следующего кода управления. Для этого необходим разряд выбора направления опроса. С целью обеспечения непрерывного опроса без пропуска такта с минимальным временем переключения. прн смене кодов управления в распределителе используются две одинаковые цепи опроса, условно обозначенные X и У, каждая из которых может производить опрос кода управления в прямом и обратном направлении. В каждом разряде для цепей X и У предусмотрены триггеры 46, 56 разрешения соответственно. Триггеры 46, 56 разрешения осуществляют выдачу разрешения на формирование сигналов поразрядного запрета при триггере разрешения в состоянии ноль, блокировку формирования сигнала поразрядного запрета в опрошенных разрядах при триггере разрешения в состоянии ели ница. Для любого разряда обеих цепей X и У прямого и обратного нлправлений опроса выполняютг-я услови наличи.е хотя бы одного сигнала пора рядного запрета в предыдущих к данному разрядах, что запрещает включе ние данного разряда и отсутствие си налов поразрядного запрета в предыдущих к данному . разрядах разрешает включение данного разряда, если в коде управления данного разряда есть единица, а триггер разрешения находится в состоянии ноль, т.е. этот разряд еще не был опрошен; включение триггера разрешения данного разряда в единиц};,блокировка, производится одновремеино с включекием в единицу триггера распределителя 44 этого же разряда. Использование триггеров разрешения дает возможность выборочного повторного опроса любого разряда в любом месте программы, после чего программа продолжается с того места, где была прервана. В режиме с непосредственным доступом становится возможным внеочередной опрос, оперативно включаемых пропущенных разрядов кода управления. Работа цепей опроса X и У производится попеременно, а Выбор направления опроса определяется значением разряда направления опроса шины 5, если оно равно единице, то направление опроса прямое, если нулю, то обратное. При включенной цепи X триггер П цикла находится в состоянии ноль,зна чение сигнала включения цепи X на входе элемента ИЛИ 15 1 и подается на входы 77 поразрядных блоков 10 всех разрядов. Значение сигнала цепи У на входе элемента ИЛИ 14 в это вре мя О и подается на входы 85 поразрядных блоков 10. Код управления подается на шины 2 и для цепи X при ра боте с памятью кода управления записывается в триггеры 47 памяти, либо при работе с непосредственным доступом подается непосредственно на элементы 48 И-ИЛИ. Если сигнал на шине б равен единице, то включены ре жим с памятыо кода управления, если сигнал шины 6 равен нулю, то включен режим с непосредственным доступом. При работе с памятью код управления не может быть изменен в процессе опроса, при непосредственном доступе изменение кода управления влияет на работу цепи в процессе опроса. При включенном режиме с памятью кода управления, в триггерах 47 памяти. На выходах элементов 48 И-ИЛИ формируются сигналы поразрядного запрета, где сигнал данного разряда образуется, если значение триггера разрешения данного разряда ноль, а в коде управления данного разряда есть единица, в остальных случаях сигнал поразрядного запрета данного разряда не образуется. С выходов элементов 48 И-ИЛИ они подаются на входы элементов И 52 и 53 соответствующих разрядов, для которых являются разрешающими, и в комплект поразрядных шин 42 запрета. Для обеспечения запрета опроса данного разряда, при неопрошенных предыдущих разрядах, в цепи X предназначаются элементы ИЛИ 49 и 50, соответственно для прямого и обратного направлений опроса. На входы элемента ИЛИ 49 подаются сиг;1алы поразрядного запрета с выходов 79 поразрядных блоков 10 всех предыдущих разрядов. На выходе элемента ИЛИ 49 при наличии хотя бы одного неопрошенного предьодущего разряда образуется сигнал запрета, подаваемый на вход запрета элемента И 52. Как только все пред1адущие данному разряды будут опрошены на всех входах элемента ИЛИ 49 будут нули, на его выходе также появится ноль, а на выходе элемента И 5i2 данного разряда появится единица при наличии сигнала поразрядного запрета на выходе элемента И-ИЛИ 48 данного разряда и единицы на входе 76 направления опроса блока 10. С выхода элемента И 52 единица поступает через элемент ИЛИ 45 на информационный вход триггера 44 распределителя и, при отсутствии сигнала останова-запуска шины 3, через элемент И 51 на информационный вход триггера 46 разрешения этого же разряда. Триггер 46 разрешения имеет цепь памяти единицы через элементы ИЛИ 51 и И 54. Очередным тактом шины 8 триггеры 44 и 46 разрешенного разряда устанавливаются в единичные состояния, на информационном входе триггера 46 будет единица, передаваемая по цепи памяти через элемент. ИЛИ 51, а на информационном входе триггера 44 возникнет, ноль, так как на выходе элемента И-ИЛИ 48 этого разряда при значении триггера разрешения равном единице возникает ноль, который подается на элементы И 52 и 53. Следующим тактом шины 8 включится очередной разрешенный разряд, тригггер 44 данного разряда установится ноль, а триггер 46 разрепения данно разряда останется в состоянии памят единицы, в котором он будет находит ся до момента переключения цепей или до момента подачи сигнала на гаи ну останова запуска 3. При опросе цепи X в обратном направлении вместо элемента И 52 подключен элемент И 53, а вместо элемента ИЛИ 46 элемент ИЛИ 50, формирующий суммарный запрет от всех разрядов справа. V Опрос цепи У в прямом и обратном направлениях производится аналогичн опросу цепи X. При опросе цепи X в прямом направлении в режиме памят кода управления, который записан в триггерах 47 памяти, в триггерах 57 памяти записан следующий код управления, который будет опрашиваться п работе цепи У. В триггере 20 записана единица, в триггере 21 записано значение, соответствующее направ лению опроса следующего кода управления для цепи У. При опр.осе цепи X состояние триггера 11 цикла равно нулю, при опросе цепи У - единице. Окончание опроса цепи X фиксируется элементами ИЛИ 16 и 17, имеющими вы ходы 31 и 32. В распределителе сигналы конца опроса на выходах 31 блока 1 (к| и 32 блока 1 (Ппоявляются одновременно. На входы элементов ИЛИ 16, 17 отдельного блока 1 опроса подаются сигналы поразрядного запрета с выходов 79 блоков 10 Всех разрядов, в чем и заключается их сходство. Различие состоит в том что на один из входов элементов ИЛИ 16 и 17 подается сигнал запрета с входов последовательной передачи запрета соответственно в прямом 27 и обратиом 28 направлениях. Если после очередного такта на выходах 31 блока 1 (к) и 32 блока 1 (I) появятся нули, то этот ноль поступит на входы 41 всех отдельных блоков опроса 1, т.е. на управляющие входы 93 триггера 11 цикла. Триггер 1 1 цикла в реткиме с памятью кода управления работает от (+) фронта такта шины 8 как и все остальные триггеры. Триггер 11 цикла подготов лен к переключению в состояние единица. На выходе элемента ИЛИ 14 по- является сигнал 1, который подает ся на входы 85 поразрядных блоков 10 и подключает цепь У. В данном тактовом интервале оказьшаются подключенными обе цепи X и У, но отключаемая цепь X уже опрошена и не влияет на информационные входы триггеров 44. Поэтому фактически оказывается подключенной только цепь У, а направление ее опроса выбирается ее состоянием триггера 21, подаваемого на входы 84 блока 10. В этом же тактовом интервале на выходе элемента И 12 образуется сигнал 1, который подается на V -входы триггера 20 и триггеров 47 памяти цепи X. Следующим тактом разрешена запись в указанные триггеры указателя направления опроса и кода управления. Одновременно с этим сигнал 1 подается на один из входов запрета элемента И 54 всех разрядов, отчего на информационных входах триггеров 46 разрешения устанавливаются нули. Во время опроса цепи X триггера 56 цепи У всех разрядов находятся в состоянии ноль, поэтому на выходах элементов И-ИЛИ 58 постоянно присутствуют поразрядные сигналы запрета, цепь У находится в .. состоянии ожидания. После прихода сигнала 1 с выхода элемента ИЛИ 14 на входы 85 блоков 10, в первом разрешенном разряде цепи У выход элемента И 62 либо элемента И 63 подключается к информационному входу триггеров 44, 56 и на них возникает единица. Следующим тактом происходит включение первого разрешенного разряда цепи У, переходят в единицу три1 геры 44, 56 этого разряда, устанавливаются в ноль триггеры 46 разрешения цепи X всех разрядов. В триггеры 47 памяти записьшается состояние следующего кода управления,а в триггер 20 записывается состояние направления его опроса. Триггер 11 цикла изменяет состояние из нуля в единицу, вследствие чего на выходах злементов ИЛИ 15 и И 12 появляются нули, на выходах элементов И 55 всех разрядов появляются единицы, подтверждающие нули на информационных входах триггеров 46 ра зрешения. На выходах элементов И-111Ш 48 образуются сигналы поразрядного запрета в соответствии с вновь записанным кодом управления. Во время работы цепи У цепь X будет находиться в состоянии ожидания до тех пор, пока на выходах 33 блока 1 (ЗК) и 34 блока I (l) не появятся нули, означающие окончание опроса цепи У. Сигнал с выхода 33 блока 1 (г) подается на входы 40 вс отдельных блоков Т опроса, т.е. на управляющие входы 92 триггера цикла Происходит образование переключающи сигналов для включения в работу цеп X и отключения цепи У аналогично оп санному выше включению, цепи У и отключения цепи X. Режим работы с нёпосредственным до тупом, В этом режиме на шине 6 должен быть сигнал О, тогда код управления подается для формирования сиг налов поразрядного запрета минуя триггеры 47, 57 памяти непосредстве но на элементы И-ИЛИ 48,58, а значения разрядов направления опроса н посредственно на элементы И-ИЛИ 22 и 23. Непосредственный доступ дает возможность оперативно изменять про грамму в процессе опроса или просто производить внеочередное подключени соответствующего разряда. В этом ре жиме триггер I1 цикла срабатьшает по (- фронту такта, а все остальные триггеры распределителя по поло жительному фронту такта.Для упорядочения этого изменения его следует проводить по (- фронту такта или в конце опроса данного цикла по срабатыванию триггера 11 цикла. Допустим, что идет цепи X в прямом направлении, все триггеры 56 разрешения цепи У в состоянии ноль, Ня соответствуюрдах выходах элементо И-ИЛИ 58 будут сигналы поразрядного запрета, а на выходах 33 и 34 единицы. На выходах 31 и 32 возникнет ноль тогда, кода будут опрошены все разряды кода управления (с учетом подключенных в процессе опроса). Этот ноль возникает по (+) фронту такта и поступает на вход 93 триггера 11 цикла, а.также на элементы ИЛИ 14 и И 12. В режиме непосредственным доступом опережаюшего подключения вно включаемой цепи не требуется, поэтому в данном такте выходные значения элементов ИЛИ 14 и И 12 не учитываются. По отрицательному фронту такта срабатьшает триггер 11 цикла и устанавливается в единицу. На выходе элемента ИЛИ 14 появляется еди ница, на выходе элемента ИЛИ 15 ноль, а на выходе элемента И 12 зна чение единицы меняется на ноль. На шинах 2 появляется новый код управления, в цепи У формируются сигнапы поразрядного запрета и подготавливаются единицы на информационных входах триггеров 44, 56 первыхг-разрешенных разрядов. На входы элементов И 55 всех разрядов подаются сигналы с выходов элементов ИЛИ 14 и 15, которые образуют на выходах элементов И 55 единицы, дающие на информационных входах триггеров 46 разрешения нули. По положительному фронту такта триггеры 44, 56 первого разрещенного. разряда цепи У включаются в единицу, а все триггеры разрешения 46 цепи X устанавливаются в ноль. Обратное Ттёрёключение цепей происходит аналогично по нулевым значениям сигналов выходов 33 блока 1 (ICJ и 34 блока 1 (I) .Действие шин останова-запуска 3 основано на управлении состоянием информационных входов триггеров 46, 56 разрешения. Сигнал останова-запуска шины 3 с уровнем единицы подается на входы запрета элементов И 54 64, отчего на информационных входах триггеров разрешения появляются нули. Если сигнал останова-запуска подан до опроса данного разряда, то произойдет останов на данном разряде, т.е. будет опрапшваться данный разряд до снятия сигнала останова-запуска. Если сигнал останова-запуска подан после опроса данного разряда, то первым пришедшим после этого тактом триггер разрешения данного разряда устанавливается в ноль, а вторым тактом начнется внеочередной опрос данного разряда (запуск. После снятия сигнала останова-запуска программа опроса будет продолжаться с того разряда, перед опросом которого она была прервана. Работа триггера 11 цикла описывается таблицей переходов. В зависимости от состояния сигнала входа 94 переключения, подаваемого с шины 6 включения непосредственного доступа, триггер I1 цикла может работать либо от положительного фронта такта, либо от отрицательного. В остальном функционирование триггера цикла совпадает по возможностям с функционированием К-триггера. Различием является то, что в режиме памяти триггера цикла состояние вспомогательного триггера 97 записывается в основные триггеры 95 и 96 и поэтому выход из режима памяти при изменеиии сигналов на входах 92 и 93 независим о уровня тактового сигнала, тогда как в ЗК-триггере он независим только при одном из значений тактового сиг нала. Возможность работы триггера цикла П от (+) и(-) фронтов такта поз воляет в режиме с памятью кода управления минимизировать время распространения сигналов запрета, а в режима с непосредственным доступом обеспечить возможность получения непрерывной программы без пропуска такта при переключении цепей X и У. Быстродействие распределителя оп ределяется минимально возможной дли тельностго такта, соответствующей максимальному времени распростр-анения сигнала через элементы распределителя в течение одного такта. В режиме с запоминанием кода управления ив режиме с непосредственным доступом время распространения сигнала различно. Рассмотрение производится из условия, что.весь распределитель представляет собой отдельный блок i опроса. Резетм с памятью кода управления. Код управления шин 2 и разряд направления опроса пины 5 изменяет сво значение сразу после изменения уровня сигнала на шине 7 синхронизации, т.е. сразу после срабатывания триггера 11 цикла, Например, при опросе цепи X в прямом направлении после включения (+) фронтом такта триггеров 44, 46 в единицу, цепь распространения сигнала наибольшей длины выглядит следующим образом: от триггера 46 данного разряда сигнал распространяется через элементы И-И.11И (48)- ИЛИ(49)р- И(52)р-1ШИ(51)р -И(54)р- Д - вход триггера (46)р,тде д - данный разряд, р - следующий раз решенный разряд. Аналогично для обратного направления цепи X и обеих направлений цепи У.при соответствующих им элементах. Рассмотренная цепь распространения сигнала остается такой до окончания опроса кода управления. При возникновении нуля на выходе 31 блока 1(к)цепь распространения наибольшей длины меняется и от триггера 46 данного разряда сигнал распространяется через элементы И-ИЛИ(48}д- ИЛИ(16) - ИЛИ(14) - И(6 63)р- miH(6Up- И(б4)р U - вход триггера(5б)р, где без индекса пока, заны. элементы, не относящиеся к по10разрядному блоку 10. Цепь распространения сигнала в конце опроса кода управления имеет на один элемент больше и поэтому определяет максимальное время распространения сигнала в одном тактовом интервале. Это время соответствует минимальной длительности такта в режиме с памятью кода управления. В режиме с непосредственным доступом смена каждого из разрядов кода управления должна производиться по (-)фронту такта, а в конце цикла опроса по изменению состояния триггера 11 цикла или по (-) фронту такта, но в этом случае нужно анализировать на равенство нулю сигналы выходов 31(32) и 33 (34) . Допустим, что идет опрос цепи У в прямом направлении. После возникновения нуля на выходе 33 блока 1 (к) он поступает на вход 92 триггера 11 цикла, распространение сигнала через элементы ИЛИ 15 и И 13 в данном случае можно не учитьшать. По (-) фронту такта срабатывает триггер 1,1 цикла, происходит переключение цепей. Длительность(+) уровня такта не должна быть менее времени распространения сигнала от триггера 56 через элементы И-ИЛИ(58Уг ИЛИ (18) - вход 92 триггера (П) . После срабатывания триггера цикла П происходит смена кода управления, сигналы запрета, с учетом времени срабатывания триггера I1 цикла, распространяются по цепи максимальной длины через элементы TP(ll)- И- . ИЛИ (48) д- Ш1И (49)р - И (52) р - ИЛИ(51)- И(54)р- Л - вход триггера. (46). Длительность (-) уровня такта не должна быть менее времени распространения через рассмотренную цепь. Обрат-. Ное переключение цепей происходит аналогично. Программа.начинается следующим образом. В режиме с памятью кода управления на шину 9 установки подается сигнал ноль, устанавливающий триггеры 44, 46, 56, 47, 57 н триггер 11 цикла в состояние ноль. На выходах 31(32) блоков 1 (к), 1 (l) и на выходах 33 (34) блоков 1(К), 1 (1) появляются нули. Первым положительным фронтом такта после снятия сигнала установки триггер 11 переключится в единицу, а в триггеры 47 памяти и триггер 20 запишутся код управления и направление его опроса. Положительным фронтом второго такта триггер 11 переключится в ноль, включится первый разреиенный разряд кода управления, Написанного в триггерах 47, а в трнг геры 57 и триггер 21 запишутся слёдуюршй код управления и направление его опроса, В режиме с непосредственным доступом подается сигнал установки на шину 9 и код управления на .шины 2, 5, После распространения сигналов запрета сигнал установки снимается и первым пришедшим ()Лрон том такта включится первый разреиенный разряд кода управления. Таким образом, распределитель обладает следующими основными свойствами: распределитель, имеет два режима работы - режим с памятью кода управления в триггерах памяти, и режим с непосредственным доступом кода управления; в обоих режимах опрос кода управления производится по разрядам, для которьк есть единицы в коде управления; разряды кода управления взаимоиезависимы и могут управ ляться от отдельных источников; направление опроса кода управления выбирается по значению разряда выбора направления опроса; с помощью смены кодов управления обеспечивается произвольная непрерывная программа опроса любой длительности и конфигураций; в режиме с памятью кода управления, код управления в одном цик ле опроса ие может быть изменен; в режиме с непосредственным доступом каждый разряд кода управления может быть изменен в одном цикле опроса, в результате чего произойдет внеочередное включение данного разряда если уже опрашиваются последующие разряды, а затем программа опроса будет продолжена с разряда, перед которым она была прервана; с помощью сигналов иин останова-запуска возможно

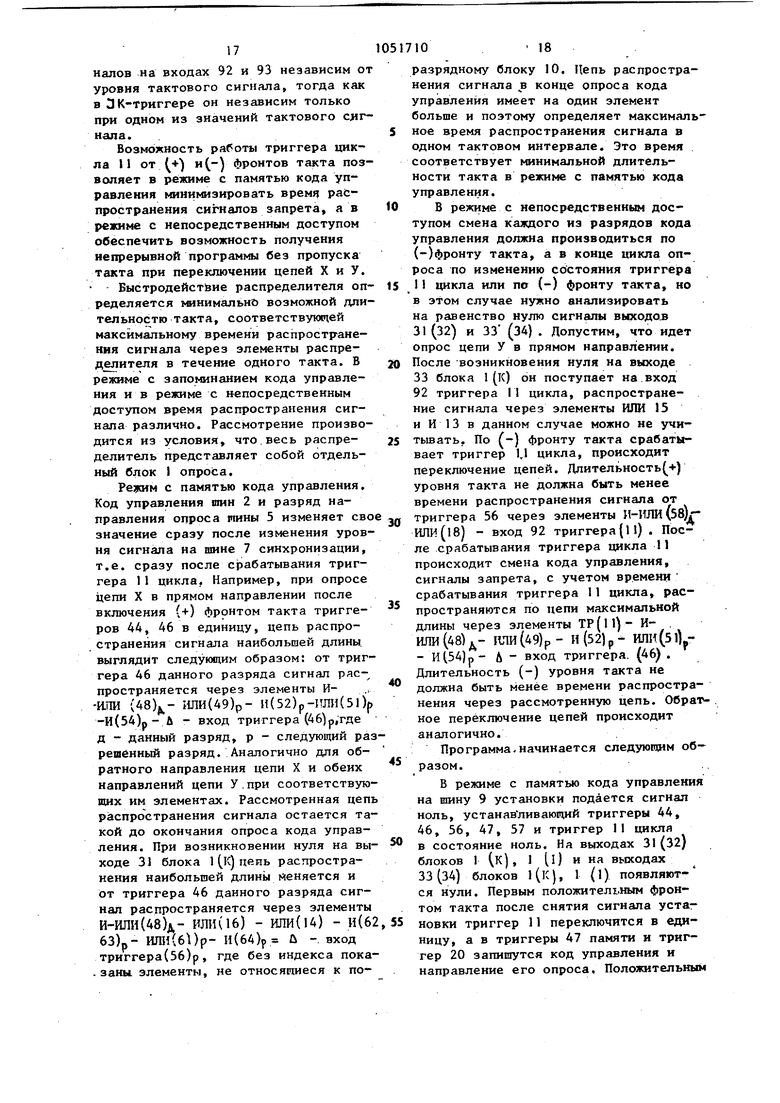

Таблица переходов триггера цикла управление остановом и запуском распределителя в любом разряде; распределитель может быть построен как отдельный блок опроса или составлен из нескольких отдельных блоков 1 опроса. Пусть t - время распространения сигнала в отдельном блоке опроса, когда в нем есть хотя бы один сигнал поразрядного запрета, а tg - время распространения проходного сигнала запрета через отдельный блок опроса, если в нем нет поразрядных сигналов запрета. Проходной сигнал запрета в отдельном-бдоке оп- роса распространяется через один элемент ИЛИ, поэтому t 6 tx. При (к последоэательно соединенных блоках 1 самый невыгодный с точки зрения времени распространения вариант может быть при проходной передаче сигналов запрета через(K-l) блок I опроса, это может быть, например, для кода управления с одной единицей в разряде блока 1 (1). Общее время распространения сигнала во время одного такта в распределителе, составленном из отдельных блоков опроса 1, для режима с памятью кода управления составляет t (К-1). tg. Передача сигналов запрета между отдельными блоками 1 опроса производится последовательно, Для обеспечения параллельной передачи сигналов требуются дополнительные внешние элементы ИЛИ. Предлагаемый распределитель не имеет ложных состояний:. Технический эффект от использования предлагаемого распределителя заключается в расширении функциональних возможностей при его реализации в в виде большой интегральной микросхемы.

21

22 Продолжение таблищл

cpL/e.i

Cpu8.2

фигЗ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Вукреев И.Н | |||

| и др | |||

| Микроэлектронные цифровых устройств | |||

| М., Советское радио, 1975, с.304, рис | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3350683/21, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-10-30—Публикация

1982-04-16—Подача