ных блоков формирования подготовительных функций одинаковы и содержат основной триггер, вспомогательный триггер, построенные на элементах И-ИЛИ-НЕ, первый, второй, третий и четвертый элементы НЕ, кроме того, в устройство введены шина на-: правления ввода делимого, шина направления ввода делителя, шина синхронизации ввода, шина синхронизации считывания, шины счетчика записи, шина счетчика считывания, в каждом поразрядном блоке формирования подготовительных функций вьпсод элемента памяти делителя соединен с входом первого элемента НЕ и первым входом сумматора прямой цепи, выход первого элемента НЕ соединен с первым входом сумматора инверсной цепи, выход сумматора прямой цепи соединен с первыми входами элемента И и элемента ИЛИ прямой цепи, вторые входы элемента И и элемента ИЛИ прямой цепи соединены с выходом первого элемента И блокировки, вторые входы элемента И и элемента ИЛИ инверсной цепи соединены с выходом элемента ШШ дополнения, выходы элементов И, РШИ прямой цепи и элементов И, ШШ инверсной цепи соединены с первыми входами соответственно второго, третьего, четвертого и пятого элементов И блокировки, вторые входы которых соединены с выходом второго элемента НЕ, выходы четвертого и пятого элементов И блокировки соединены с первыми информационными входами соответственно элементов памяти переноса и разрешения, выходы второго и третьего элементов И блокировки соединены с вторыми информационными входами соответственно элементов памяти переноса и разрешения, третий информационный вход памяти переноса соединен с выходом сумматора по модулю два, первый вход которого соединен с выходом первого элемента И-ИЛИ, третий информационный вход элемента памятиразрешения, соединен с выходом элемента И дополнения, второго элемента И-ИЛИ соединен с информационным входом элемента памяти делителя, выход элемента памяти разрядности соединен с первым входом элемента ШШ дополнения, с первым входом первого элемента И блокировки данного разряда и с входом второго

элемента НЕ предыдущего разряда, вто рой вход элемента ИЛИ дополнения соединен с выходом переноса сумматора -инверсной цепи предьщущего разряда, второй вход первого элемента И блокировки соединен с выходом переноса сумматора прямой цепи предьщущего разряда, информационный вход элемента памяти разрядности данного разряда соединен с первым входом элемента И дополнения предыдущего разряда и с соответствующим выходом блока регистров памяти разрядности, выход элемента памяти переноса данного разряда соединен с вторыми входами сумматоров прямой и инверсной цепей следующего более старшего разряда и с соответствующими входами элементов И-ИЛИ блока определения цифр частного, выход элемента памяти разрешения данного разряда соединен с третьими входами сумматоров прямой и инверсно цепей следующего более старшего разряда и с соответствующими входами элементов И-ИЛИ блока определения цифр частного, входы управления элементов памяти переноса, разрешения, делителя и разрядности поразрядных блоков формирования подготовительных функций соединены с входами управления элементов памяти знаков делимого и делителя узла анализа знаков, с информационным входом триггера Т+2 состояния, с входом управления режимами первого регистра и с выходом первого элемента ШШ, первые входы выбора элементов памяти переноса и разрешения всех поразрядных блоков соединены с выходом элемента памяти знака делителя и с первым входом первого сумматора по модулю два узла анализа знаков, вторые входы выбора элементов памяти переноса и разрешения всех поразрядных блоков соединены с выходом переноса блока образования цифр частного, вторые входы элементов И дополнения и сумматора по модулю два каждого поразрядного блока формирования подготовительных функций соединены с выходом элемента ИИЛИ узла анализа знаков, первый инверсный и второй прямой входы первого элемента И-ИЛИ всех поразрядных блоков соединены с выходом второго сумматора по модулю два узла анализа знаков, третий вход первого элемента И-ИЛИ каждого поразрядного

блока соединен с соответствующим выходом первого канала двухканального переключателя нескольких входов на один выход блока входных регистров, четвертый вход первого элемента И-ИЛИ каждого поразрядного блока соединен с соответствующим выходом первого канала двухканального переключателя, взятого со сдвигом на один разряд в сторону младших разрядов, первый инвер ый и второй входы второго элемента И-ИЛИ всех поразрядных блоков соединены с выходом третьего сумматора по модулю два узла анализа знаков, третий вход второго элемента И-ИЛИ каждого поразрядного блока соединен с соответствукицим выходом второго канала двухканального переключателя нескольких входов на один выход блока входных регистров, четвертый вход второго элемента И-ИЛИ калсдого по разрядного блока соединен с соответствукицим выходом второго канала двухканального переключателя, взятого со сдвигом на один разряд в сторону младших разрядов, в блоке анализа знаков выход элемента памяти знака делимого соеданен с вторым входом первого сумматора по модулю два, первый вход второго сумматора по модулю два соединен с информационным входом элемента памяти знака делимого, с первым инверсным, с втррым прямым входами элемента И-ИЛИ блока анализа знаков и с выходом старшего разряда первого канала двухканального переключателя блока входных регистров, второй вход второго сумматора по модулю два узла анализа знаков соединен с выходом предстаршёго разряда первого канала двухканального переключателя блока входных регистров, первый вход третьего сумматора по модулю два узла анализа знаков соединен с информационным входом элемента памяти знака делителя, с третьим и четвертым входами элемента И-ИЛИ узла анализа знаков и с выходом старшего разряда второго канала двухканального переключателя блока входных регистров, второй вход третьего сумматора по модулю два узла анализа знаков соединен с выходом предстаршего разряда второго канала двухканального переключателя блока входных регистров, выход первого сумматора по модулю два узла анализа знаков соединен с первым инверсным входом первого элемента И-ШШ и с первым прямым входом второго элемента И-ШШ блока определения цифр частного, вьпсод второ.го элемента И-ИЛИ блока определения цифр частного соединен с шиной частного, вторые входы, третьи четвертые и пятые инверсные входы первого и второго элементов И-ИЛИ блока определения цифр частного соединены с выходом триггера Т+2 состояния, остальные одноименные входы первого и второго элементов И-ИЛИ объединены и соединены с соответствующими выходами элементов сигналов переноса и разрешения переноса предьщущих разрядов , входы каждого элемента И-ИЛИ соединены с соответствующими выходами элементов сигналов переноса и разрешения переноса предыдущих разрядов, числовые входы входных регистров с нечетными номерами соединены с шиной делимого,числовые входы входных регистров с четными номерами соединены с шиной делителя, -входы направления ввода входных регистров с нечетными номерами соединены с шиной направления ввода делимого, входы направления ввода входных регистров с четными номерами соединены с шиной направления ввода делителя, выходы разрядов входных регистров с нечетными номерами соединены с соответствующими входами первого канала двухканального переключателя нескольких входов на один выход, выходы разрядов входных регистров с четными номерами соединены с соответствующими входами второго канала двухканального переключателя нескольких входов на один выход, входы выбора входных регистров, взятых с номерами по порядку счета, соединены попарно, каждая пара - со своим входом выбора соответствукщего регистра блока памяти разрядности и с соответствующим выходом дешифратора записи, входы управления двухканального переключателя блока входных регистров соединены с соответствующими входами одноканапьного переключателя блока регистров памяти разрядности и с соответствующими выходами дешифратора считывания, входы управления записи всех входных регистров соединены с соответствующими выходами второго регистра, с соответствующими входами многовходового элемента ИЛИ-НЕ и с соответствуннцими информационньти входами всех ре- .гистров блока памяти разрядности, входы разрешения записи всех регистров блока памяти разрядности соединены с информационным входом триггера 11+1 состояния, с выходом перво го элемента И, с выходом управления счетом счетчика записи и с первым входом второго элемента И, выходы разрядов блока регистров памяти разрядности соединены с соответствующими входами одноканального. переключателя нескольких входов на один выход, в калсдом входном регистре информационный вход разрядного триггера соединен ,с выходом элемента ИИЛИ этого же разряда, выход триггера является выходом соответствующего разряда регистра и соединен с первым вторым входами элемента И-ИДИ этого же разряда, а также с третьим входом элемента И-ИЛИ более младшего разряда, четвертые входы элементов И-ИЛИ всех разрядов и третий вход элемента И-НЛИ старшего разряда соединены и являются числовым входом входного регистра, пятьй инверсный, шестой и седьмой входы всех элементов И-ИЛИ входного регистра объединены и являются входом направления ввода, восьмой, девятый и десятый инверсный входы всех элементов И-ИЛИ входного регистра объединены и являются вхот дом выбора, одиннадцатый вход и двенадцатый инверсный вход элемента ИИЛИ каждого разряда объединены и являются для каждого разряда входом управления записи, первый вход первого элемента И соединен с К-входом триггера установки и с выходом третьего элемента И, второй инверсный вход первого элемента И соединен с первым инверсным входом четвертого элемента И, с входом блокировки дешифратора записи,, с выходом пятого элемента И и с шиной переполнения, второй вход четвертого элемента И соединен с шиной запуска, а его выход с 3-входом триггера установки, первый вход третего элемента И соединен с шиной управления, а его второй вход соединен с выходом триггера установки, с входом управления установкой в ноль второго регистра и с шиной синхронизации записи, выход многовходового элемента ИПИ-НЕ соединен с входом .второго регистра, выход триггера п+1 состояния соединен с первым входом шестого элемента И, входы установки триггера установки, триггера п+1 состояния, триггера Т+2 состояния, триггера синхронизации считывания, первого регистра, счетчика считывния, счетчика записи соединены с шиной установки, выходы счетчика ,записи соединены с соответствующими входами дешифратора записи, схемы сравнения и с соответствующими шинами счетчика записи, выходы счетчика считывания соединены с соответствующими входами дешифратора, считывания схемы сравнения и соответствующими шинами счетчика считывания, выход схемы сравнения соединен с первым инверсным входом седьмого элемента И, с вторым инверсным входом шестого элемента И, с вторым входом второго элемента И и с первым входом пятого элемента И, выход седьмого элемента И соединен с первым входом первого элемента ИЛИ, выход шестого элемента И соединен с вторым входом первого элемента ИЛИ, выход триггера Т+1 состояния соединен с вторым входом седьмого элемента И и с третьим инверсным входом шестого элемета И, выход многовходового элемента ИЛИ соединен с вторым входом пятого элемента И, с четвертым инверсным входом шестого элемента И и с третьим инверсным входом второго элемента И, выход второго элемента И соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с информационным входом триггера Т+1 состояния, с входом управления счетом считчика считьшания и с последовательным выходом первого регистра, выходы разрядов первого регистра соединены с соотвествующими входами многовходового элемента ИЛИ, параллельные входы первого регистра соединены с соответствующими выходами одноканального переключателя нескольких входов на один выход блока регистров памяти разрядности, являющимися выходами блока регистров памяти разрядности, выход второго элемента ИЛИ соединен с информационным входом триггера синхронизации считывания, выход которого соединен с шиной синхронизации считывания, в элементах памяти переноса и разрешения информационный вход вспомогательного триггера соединен с выходом основного триггера, а выход в.спомогательного триггера является выходом элемента памяти переноса и разрешения, тактирующий вход вспомогательного триггера соединен с входом первого элемента НЕ и является тактов м входом элемента памяти переноса и разрешения, выход первого элемента НЕ соепинен с первым тактирующим входом основного триггера, первый и второй информационные входы основного триггера объединены и являются первым информационным входом элемента памяти переноса и разрешения, третий и .четвертый информационные входы основного триггера объединены и являются вторым информационньм входом элемента памяти переноса и разрешения, пятый информационный вход основного триггера является третьим информационным входом элемента памяти переноса и разрешения, второй и третий тактирующие входы основного триггера соединекь с входом второго элемента НЕ и являются первым входом выбора элемента памяти переноса и разрешения , четвертый и пятый тактирующие

входы основного триггера соединены с выходом второго элемента НЕ, шестой и тактирующие входы основного триггера соединены с входом Третьего элемента НЕ и являются вторым входом выбора элемента памяти переноса и разрешения, восьмой и девятый тактирующие входы основного триггера соединены с выходом третьег элемента НЕ, десятый тактирующий вход основного триггера соединен с входом четвертого элемента НЕ и является входом управления элемента памяти переноса и разрешения, выход четвертого элемента НЕ соединен с одиннадцатым, двенадцатым, тринадцатым и четырнадцатым тактирующими входами основного триггера, тактовые входы элементов памяти делителя, разрядности, переноса и разрешения всех поразрядных блоков формирования подготовительных функций, элементов памяти знаков делимого и делителя узла анализа знака, всех входных регистров блока входных регистров, всех регистров памяти разрядности блока регистров памяти разрядности, триггера установки, триггера п+1 состояния, триггера Т+1 состояния, триггера Т+2 состояния, траггера синхронизации считывания, счетчика записи и счетчика считьгоания соединены с выходом генератора тактовой частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Делительное устройство | 1983 |

|

SU1176324A1 |

| Устройство для деления чисел | 1985 |

|

SU1287149A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для деления чисел | 1981 |

|

SU970356A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления чисел | 1986 |

|

SU1417010A1 |

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

:ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО, со- . держащее генератор тактовых импульсов, первый и второй регистры, узел анализа знаков, первый и второй элементы ИЛИ, первый, второй и третий элементы И, причем выход генератора тактовых импульсов соединен с тактовыми входами первого и второго регистров, отличающееся тем, что, с целью повышения быстродействия, в устройства введены М+2 поразрядных блоков формирования подготовительных функций, блок определения цифр частного, блок входных регистров, блок регистров памяти разрядности, причем каждый поразрядный блок формирования подготовительных функций содержит элемент памяти делителя, элемент памяти разрядности, элемент памяти переноса, элемент памяти разрешения, первый и второй элементы И-ИЛИ, сумматор по модулю два, одноразрядный комбинационный сумматор прямой цепи, одноразрядный комбинационный сумматор инверсной цепи, элемент И прямой цепи, элемент И ин вареной цепи, элемент ИЛИ прямой цепи, элемент ИЛИ инверсной цепи, эле- . менты И и ИЛИ дополнения, первый, второй, третий, четвертый и пятый элементы И блокировки, первый и второй элементы НЕ, блок определения цифр частного содержит три яруса элементов формирования переноса и разрешения переноса и два элемента ИИЛИ, выходы которых являются соответственно сигналами переноса и частного, блок входных регистров содержит N пар входных m + 1 разрядных регистров , где пара состоит из входного регистра делимого и входного регистора делителя, двухканальный . переключатель нескольких входов на один выход, каждый канал которого додержит m + 1.разрядов, каладый ряд входного регистра содержит тактируемый двухступенчатый триггер и (Л элемент И-ИЛИ, блок регистров памяти разрядности содержит для каждой пары входных регистров один статический регистр памяти разрядности из (т-К) разрядов и одноканальный переключатель нескольких входов на один выход, где канал имеет. (т-К) разрядов,в со 00 ел устройство также введены многовходовой элемент ШШ-НЕ, триггер установки, триггер п+1 состояния, счетчик записи, дешифратор записи, счетto чик считывания, дешифратор считывания, схема сравнения, триггер Т-И состояния, триггер Т+2 состояния, триггер синхронизации считьшания, многовходовый элемент ИЛИ, четвер тый, пятый, шестой и седьмой элемен- , ты И, в узел анализа знака введены элементы памяти знака делимого, элемент памяти знака делителя, элемент И-ИЛИ, первый,,второй и третий сумматоры по модулю два, элементы памяти переноса и разрешения поразряд

1

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих вычислительных систем.

Цель изобретения - повьш1ение быст- родействия устройства.

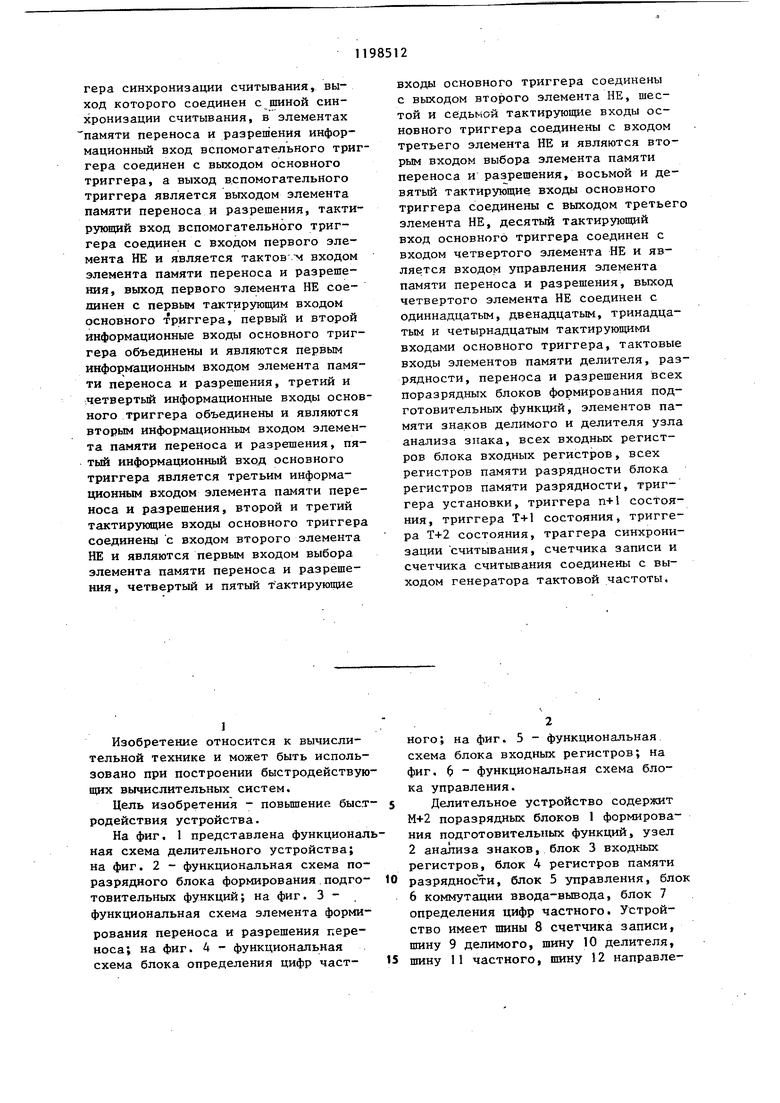

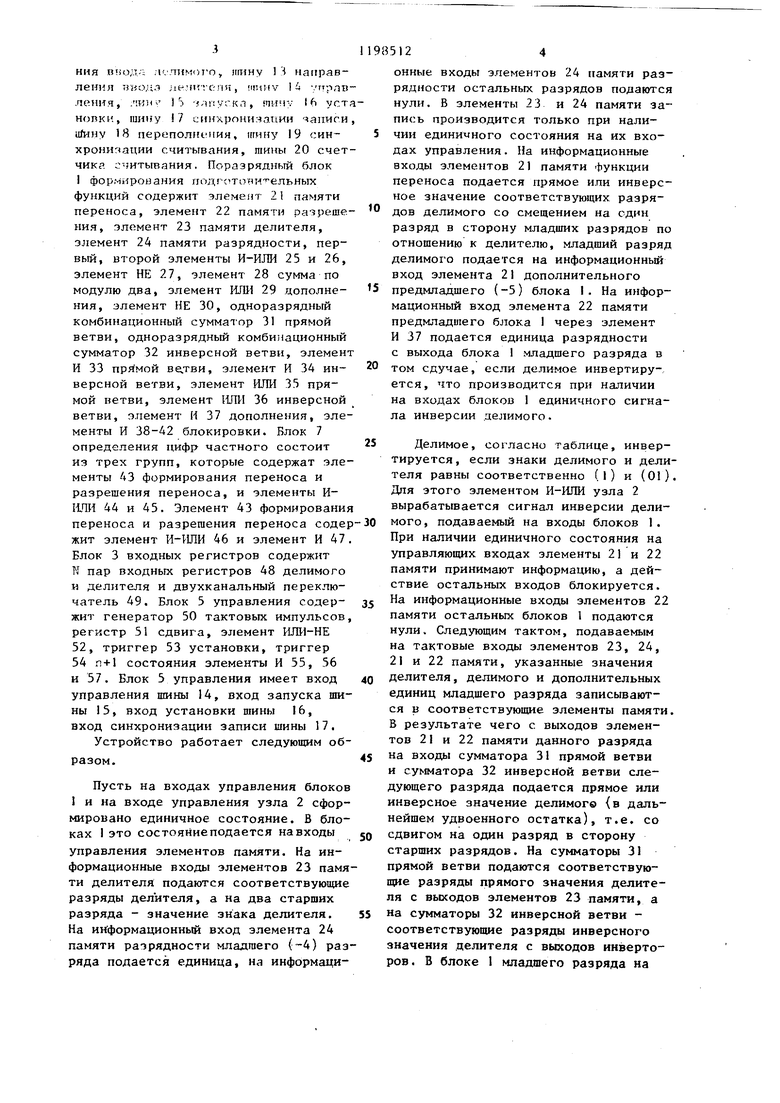

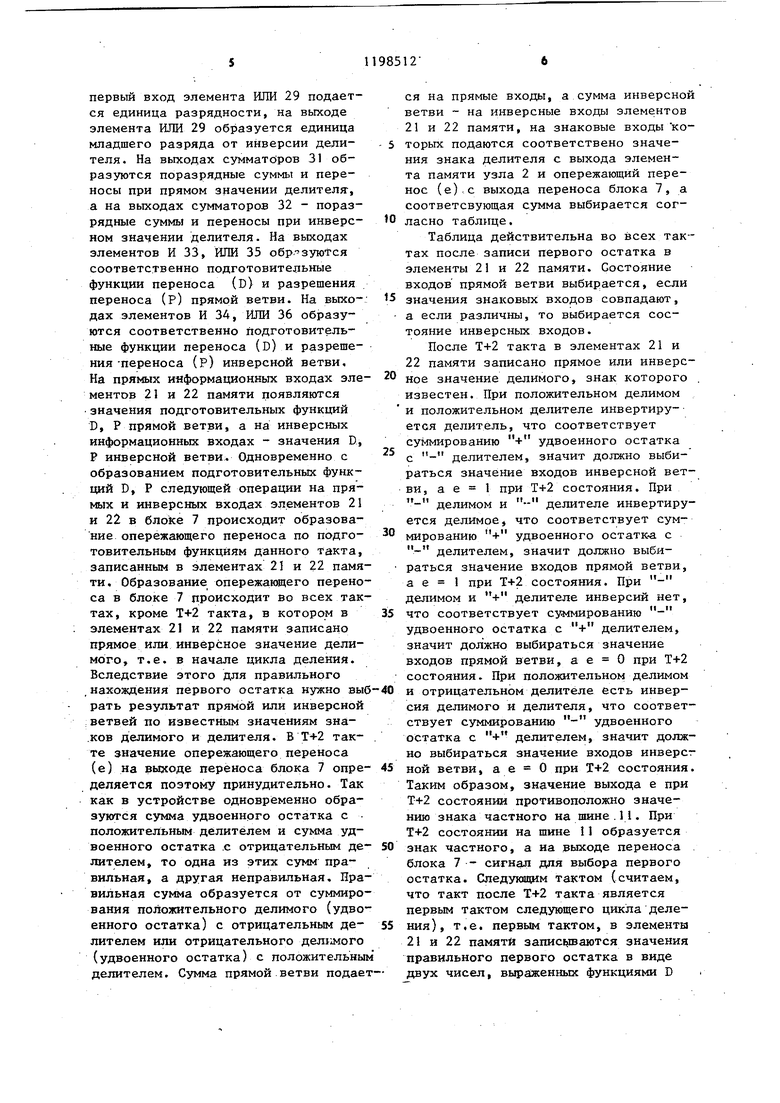

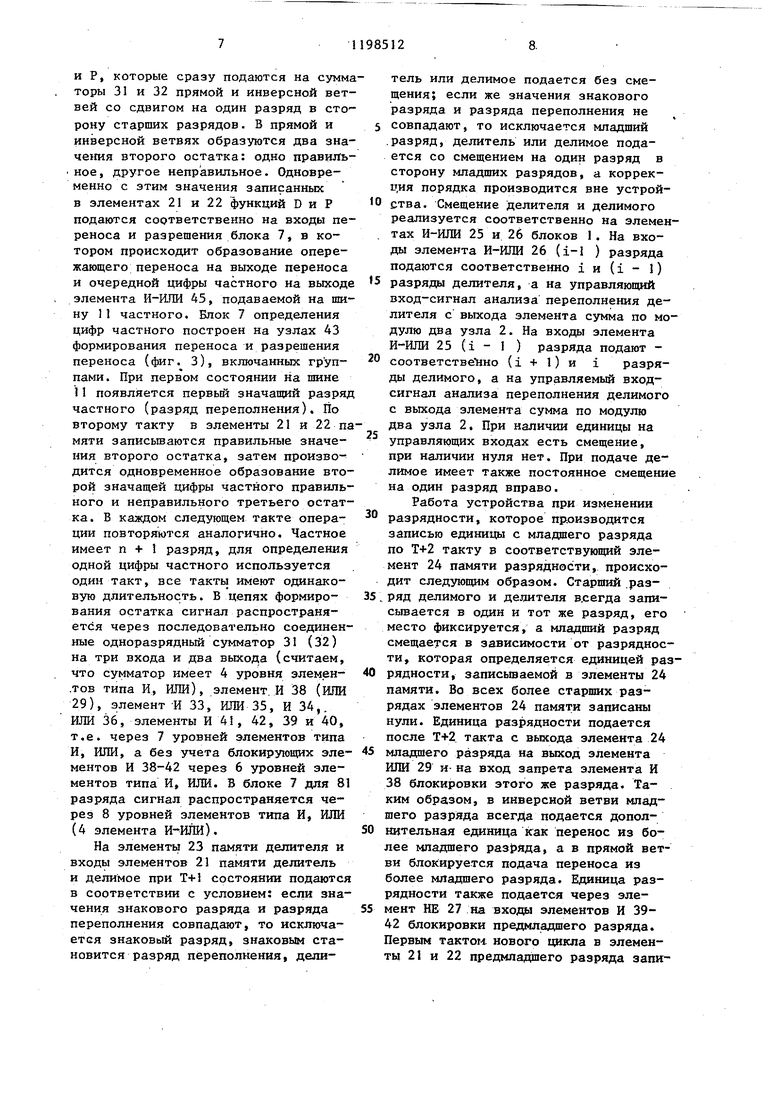

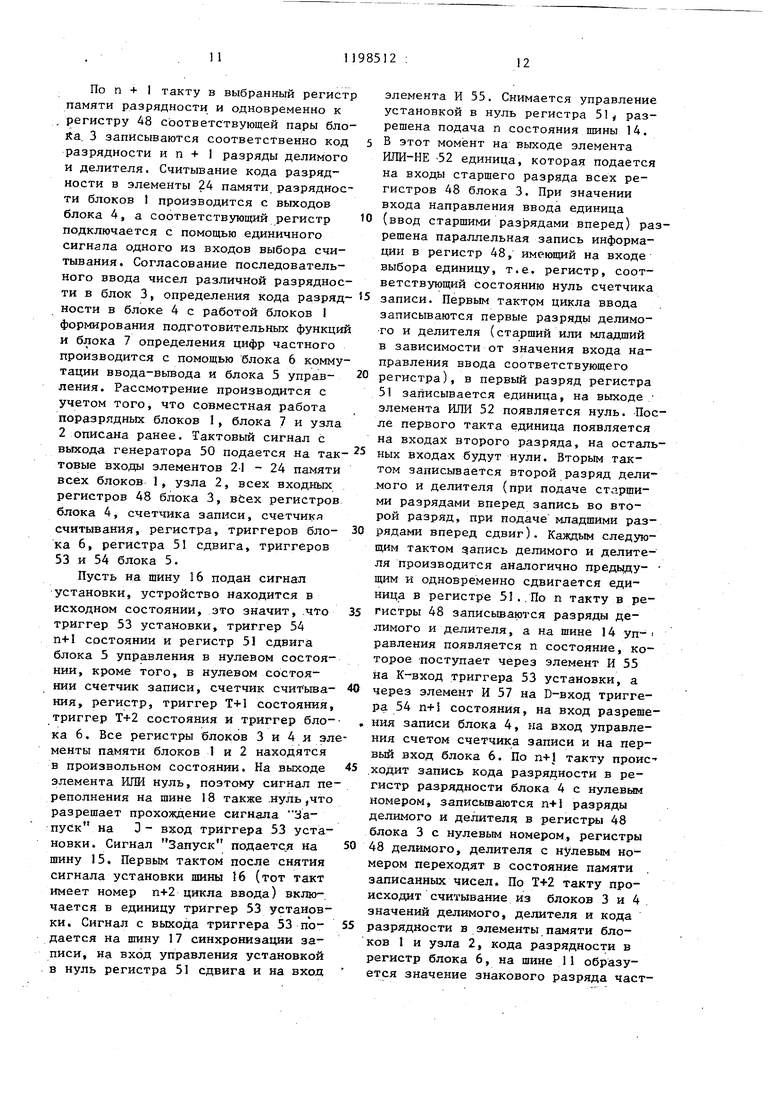

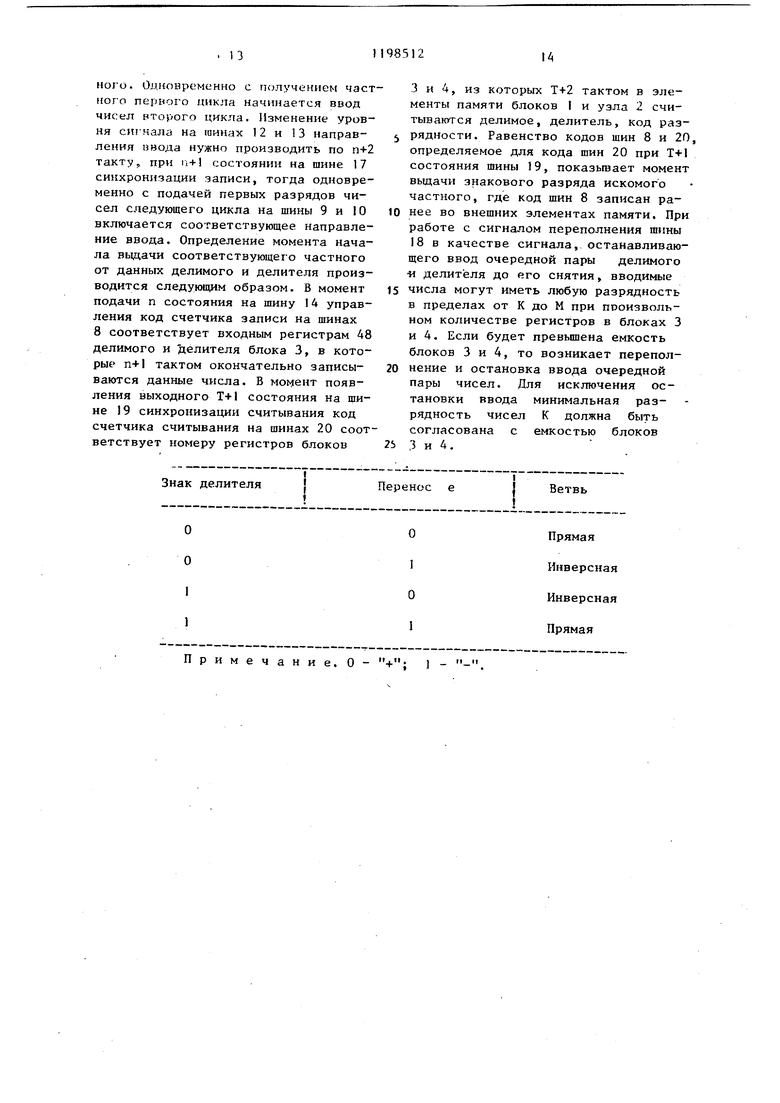

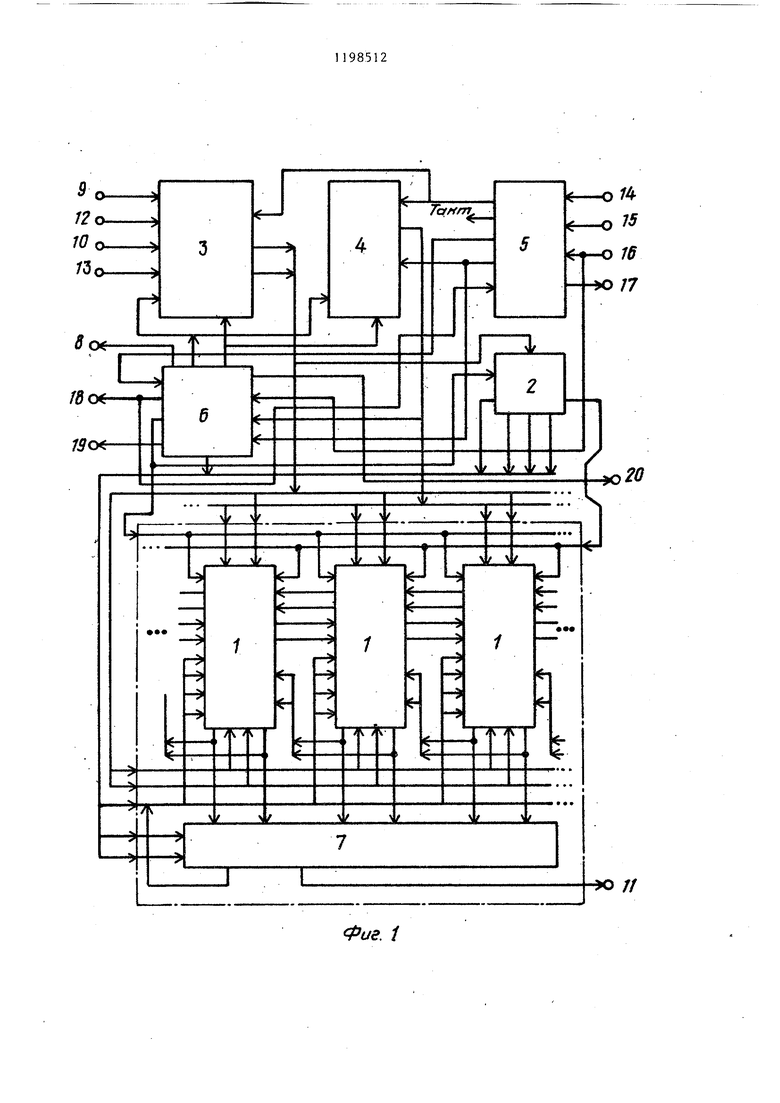

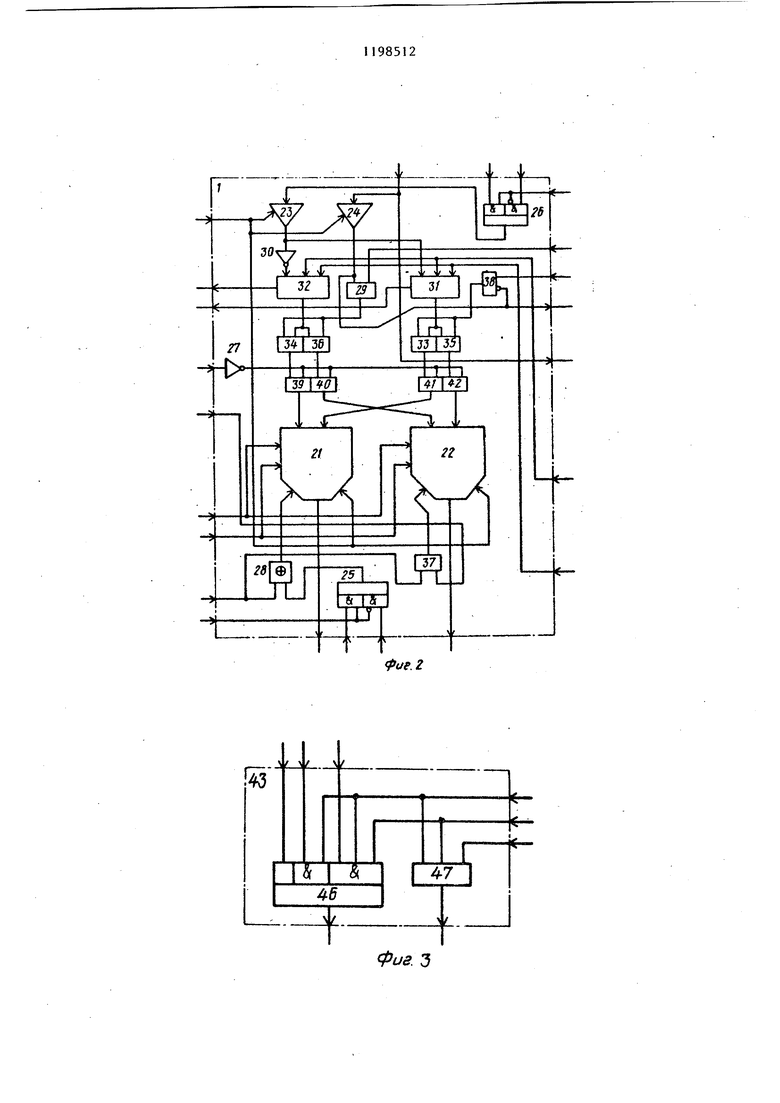

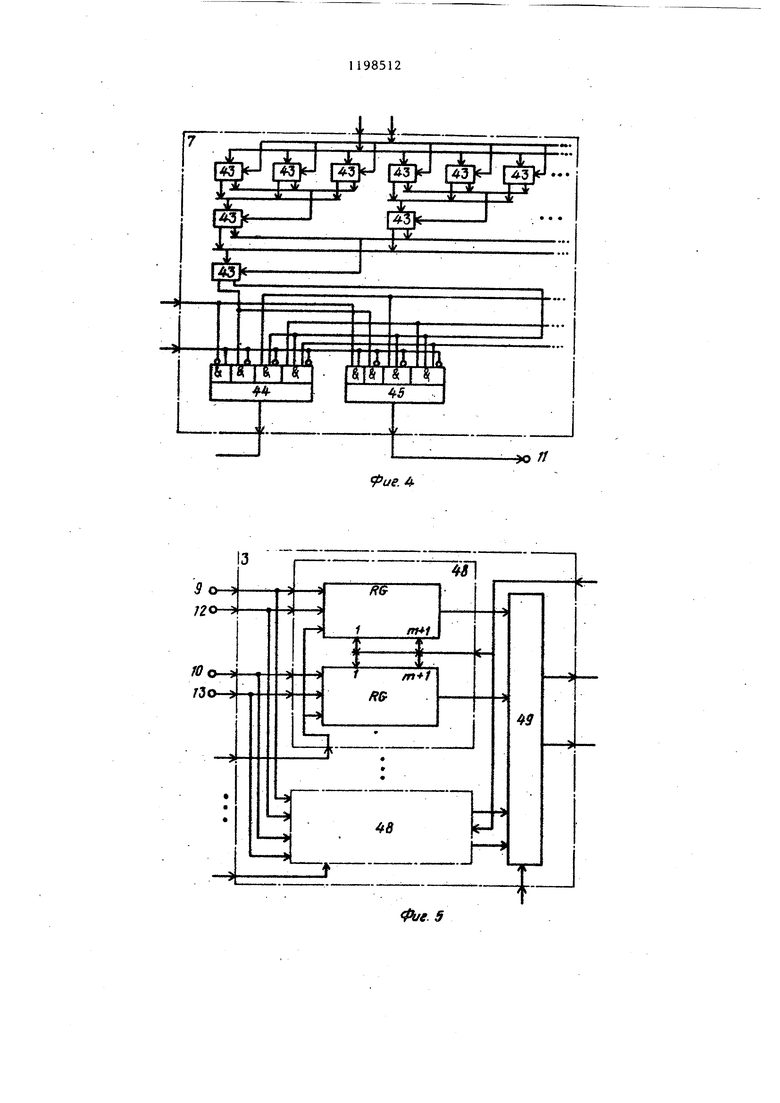

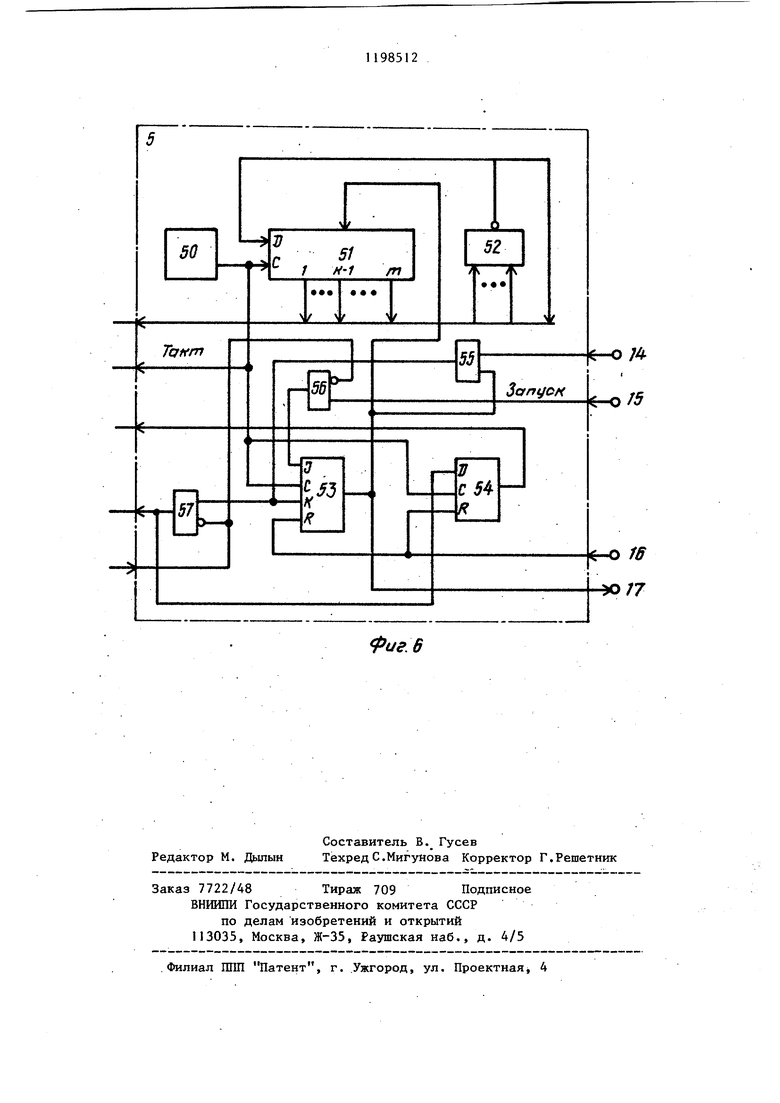

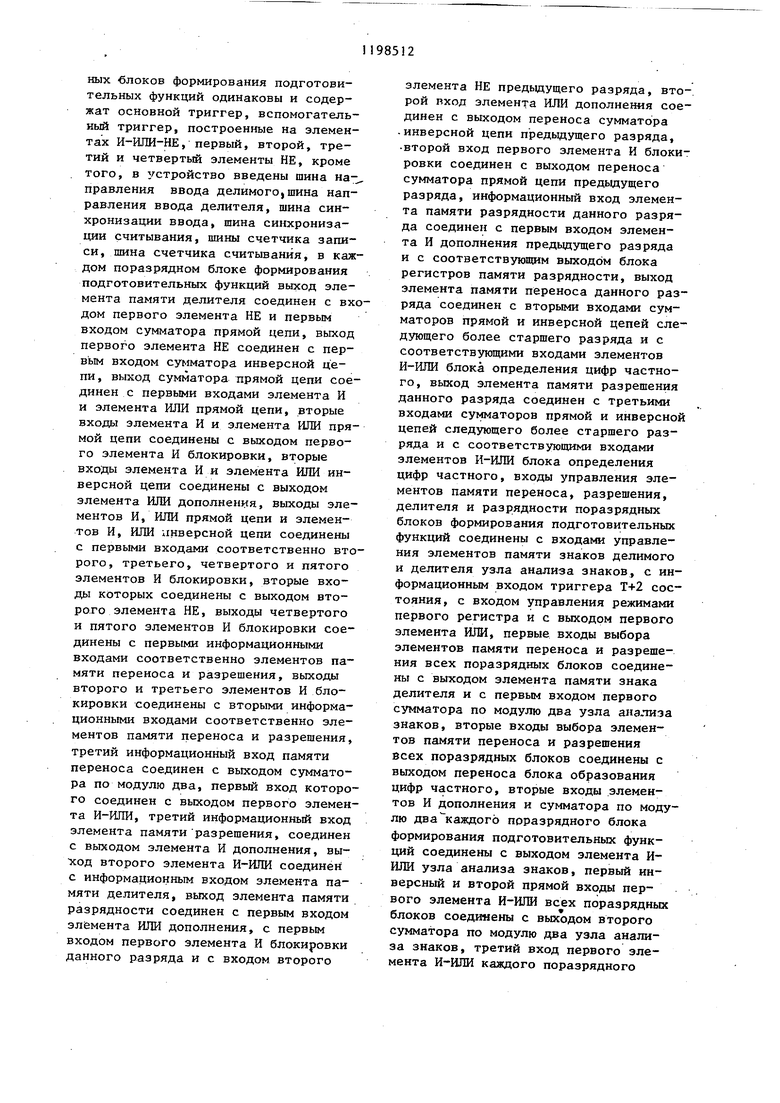

На фиг, 1 представлена функциональная схема делительного устройства; на фиг. 2 - функциональная схема поразрядного блока формирования подготовительных функций; на фиг. 3 функциональная схема элемента формирования переноса и разрешения переноса; на фиг. 4 - функциональная схема блока определения цифр частного; на фиг. 5 - функциональная схема блока входных регистров; на фиг. 6 - функциональная схема блока управления.

Делительное устройство содержит М+2 поразрядных блоков 1 формирования подготовительных функций, узел 2 анализа знаков, блок 3 входных регистров, блок 4 регистров памяти разрядности, блок 5 управления, бло 6 коммутации ввода-вывода, блок 7 определения цифр частного. Устройство имеет шины 8 счетчика записи, шину 9 делимого, шину 10 делителя, шину 11 частного, шину 12 направле3

ния .i;.l-i а-лимото, нгнну 14 направления тгвол.т лелителч, sir.iMV li уттрлв .пения, .iH)(i S , пглму 16 устя нопки, шину 17 сннхрпнняо.тшн чаписи и/ину 18 перепожниия, игину 19 синхрониг ации считывания, пшиы 20 счетчика считывания. Поразрядный блок I фор,миро4зания подгчтояи ельных функций содержит элемент- 21 памяти переноса, элемент 22 памяти рачрешения, элемент 23 памяти делителя, элемент 24 памяти разрядности, первый, второй элементы И-ИЛИ 25 и 26, элемент НЕ 27, элемент 28 сумма по модулю два, элемент ИЛИ 29 дополнения, элемент НЕ 30, одноразрядный комбинационный сумматор 31 прямой ветви, одноразрядный комбинационный сумматор 32 инверсной ветви, элемент И 33 прямой , элемент И 34 инверсной ветви, элемент ИЛИ 33 прямой ветви, элемент ШШ 36 инверсной ветви, элемент И 37 дополнения, элементы И 38-42 блокировки. Блок 7 определения цифр частного состоит из трех групп, которые содержат элементы 43 формирования переноса и разрешения переноса, и элементы ИИПИ 44 и 45. Элемент 43 формирования переноса и разрешения переноса содер жит элемент И-РШИ 46 и элемент И 47. Блок 3 входных регистров содержит N пар входных регистров 48 делимого и делителя и двухканальный переключатель 49. Блок 5 управления содержит генератор 50 тактовых импульсов, регистр 51 сдвига, элемент ИЛИ-НЕ 52, триггер 53 установки, триггер 54 п+1 состояния элементы И 55, 56 и 57. Блок 5 управления имеет вход управления шины 14, вход запуска шины 15, вход установки шины 16, вход синхронизации записи шины 17.

Устройство работает следующим образом.

Пусть на входах управления блоков 1 и на входе управления узла 2 сформировано единичное состояние. В блоках 1 это состояниеподается на входы

управления элементов памяти. На информационные входы элементов 23 памяти делителя подаются соответствующие разряды делителя, а на два старших разряда - значение знака делителя. На информационный вход элемента 24 памяти разрядности младшего (-4) разряда подается единица, на информаци1985124

онные входы элементов 24 памяти разрядности остальных разрядов подаются нули. В элементы 23 и 24 памяти запись производится только при наличии единичного состояния на их входах управления. На информационные входы элементов 21 памяти Функции переноса подается прямое или инверсное значение соответствующих разрядов делимого со смещением на един разряд в сторону младших разрядов по отношению к делителю, младший разряд делимого подается на информационный вход элемента 21 дополнительного

5 предмладшего (-5) блока I. На информационный вход элемента 22 памяти предмладшего блока 1 через элемент И 37 подается единица разрядности с выхода блока 1 младшего разряда в

20 том сдучае, если делимое инвертируется, что производится при наличии на входах блоков 1 единичного сигнала инверсии делимого.

25 Делимое, согласно таблице, инвертируется , если знаки делимого и делителя равны соответственно (l) и (01). Дпя этого элементом И-ИЛИ узла 2 вырабатывается сигнал инверсии делимого, подаваемый на входы блоков 1. При наличии единичного состояния на управляющих входах элементы 2) и 22 памяти принимают информацию, а действие остальных входов блокируется.

На информационные входы элементов 22 памяти остальньпс блоков 1 подаются нули. Следующим тактом, подаваемым на тактовые входы элементов 23, 24, 21 и 22 памяти, указанные значения

0 делителя, делимого и дополнительных единиц младшего разряда записываются в соответствующие элементы памяти. В результате чего с выходов элементов 2I и 22 памяти данного разряда

5 на входы сумматора 31 прямой ветви и сумматора 32 инверсной ветви следующего разряда подается прямое или инверсное значение делимого {в дальнейшем удвоенного остатка), т.е. со

0 сдвигом на один разряд в сторону старших разрядов. На сумматоры 31 прямой ветви подаются соответствующие разряды прямого значения делителя с выходов элемеитов 23 памяти, а

5 на сумматоры 32 инверсной ветви соответствующие разряды инверсного значения делителя с выходов инверторов. В блоке 1 младшего разряда на

первый вход элемента ИЛИ 29 подается единица разрядности, на выходе элемента ИЛИ 29 образуется единица младшего разряда от инверсии делителя. На выходах сумматс ров 31 образуются поразрядные суммы и переносы при прямом значении делителя:, а на выходах сумматоров 32 - поразрядные суммы и переносы при инверсном значении делителя. На выходах элементов И 33, ИЛИ 35 обр.-зуются соответственно подготовительные функции переноса (D) и разрешения переноса (Р) прямой ветви. На выходах элементов И 34, ИЛИ 36 образуются соответственно подготовительные функции переноса (В) и разрешения-переноса (Р) инверсной ветви, На прямых информационных входах элементов 21 и 22 памяти появляются значения подготовительных функций D, Р прямой ветви, а на инверсных информационных входах - значения D, Р инверсной ветви. Одновременно с образованием подготовительных функций D, Р следующей операции на прямых и инверсных входах элементов 21 и 22 в блоке 7 происходит образование опережающего переноса по подготовительным функциям данного такта, записанным в элементах 2 и 22 памяти . Образование опережа нвдего переноса в блоке 7 происходит во всех тактах, кроме Т+2 такта, в котором в элементах 21 и 22 памяти записано прямое или инверсное значение делимого, т.е. в начале цикла деления. Вследствие этого для правильного ,нахождения первого остатка нужно выбрать результат прямой или инверсной :ветвей но известным значениям зна.ков делимого и делителя. В Т+2 такте значение опережающего переноса (е) на выходе переноса блока 7 определяется поэтому принудительно. Так как в устройстве одновременно образуются сумма удвоенного остатка с положительным делителем и cyNMa удвоенного остатка .с отрицательным делителем, то одна из этих сумм правильная, а другая неправильная. Правильная сумма образуется от суммирования положительного делимого (удво енного остатка) с отрицательным делителем или отрицательного делимого (удвоенного остатка) с положительным делителем. Сумма прямой ветви подается на прямые входы, а сумма инверсной ветви - на инверсные входы элементов 21 и 22 памяти, на знаковые входы ко5 торых подаются соответствено значения знака делителя с выхода элемента памяти узла 2 и опережающий перенос (е),с выхода переноса блока 7, а соответсвующая сумма выбирается согласно таблице.

Таблица действительна во всех тактах после записи первого остатка в элементы 21 и 22 памяти. Состояние входов прямой ветви выбирается, если

значения знаковых входов совпадают, а если различны, то выбирается состояние инверсных входов.

После Т+2 такта в элементах 21 и 22 памяти записано прямое или инверсное значение делимого, знак которого .

известен. При положительном делимом и положительном делителе инвертируется делитель, что соответствует суммированию + удвоенного остатка с - делителем, значит должно выбираться значение входов инверсной ветви, а е 1 при Т+2 состояния. При - делимом и - делителе инвертируется делимое, что соответствует суммированию + удвоенного остатк-а с - делителем, значит должно выбираться значение входов прямой ветви, а е 1 при Т+2 состояния. При - делимом и + делителе инверсий нет,

что соответствует суммированию - удвоенного остатка с + делителем, значит должно выбираться значение входов прямой ветви, а е О при Т+2 состояния. При положительном делимом

и отрицательном делителе есть инверсия делимого и делителя, что соответствует суммированию - удвоенного остатка с + делителем, значит должно выбираться значение входов инверсг

ной ветви, а е О при Т+2 состояния. Таким образом, значение выхода е при Т+2 состоянии противоположно значению знака частного на шине . 11. При Т+2 состоянии на шине 11 образуется

энак частного, а на выходе переноса . блока 7 - сигнал для выбора первого остатка. Следующим тактом (считаем, что такт после Т+2 такта является первым тактом следующего цикла делекия), т.е. первым тактом, в элементы 21 и 22 памяти запис гшаются значения правильного первого остатка в виде двух чисел, выраженных функциями D

и Р, которые сразу подаются на сумматоры 31 и 32 прямой и инверсной ветвей со сдвигом на один разряд в сто рону старших разрядов. В прямой и инверсной ветвях образуются два значе1тя второго остатка: одно правильное , другое неправильное. Одновременно с этим значения записанных в элементах 21 и 22 функций D и Р подаются соответственно на входы переноса и разрешения блока 7, в котором происходит образование опережающего переноса на выходе переноса и очередной цифры частного на выходе элемента Й-И.ПИ 45, подаваемой на шину 11 частного. Блок 7 определения цифр частного построен на узлах 43 формирования переноса и разрешения переноса (фиг. З), включанных группами. При первом состоянии на шине I1 появляется первый значащий разряд частного (разряд переполнения). По второму такту в элементы 21 и 22 памяти записьшаются правильные значения второго остатка, затем производится одновременное образование второй значащей цифры частного правильного и неправильного третьего остатка. В каждом следующем такте операции повторяются аналогично. Частное имеет п + 1 разряд, для определения одной цифры частного используется один такт, все такты имеют одинаковую длительность. В цепях формирования остатка сигнал распространяется через последовательно соединенные одноразрядный сумматор 31 (32) на три входа и два выхода (считаем, что сумматор имеет 4 уровня элемен.тов типа И, или), элемент. И 38 (ШШ 29), элемент И 33, ИЛИ 35, И 34,. ШШ 36, элементы И 4, 42, 39 и 40, т.е. через 7 уровней элементов типа И, ИЛИ, а без учета блокирующих элементов И 38-42 через 6 уровней элементов типа И, ИЛИ. В блоке 7 для 81 разряда сигнал распространяется через 8 уровней элементов типа И, ИЛИ (4 элемента И-ИЛИ).

На элементы 23 памяти делителя и входы элементов 21 памяти делитель и делимое при Т+1 состоянии подаются в соответствии с условием: если значения знакового разряда и разряда переполнения совпадают, то исключается знаковый разряд, знаковым становится разряд переполнения, делитель или делимое подается без смещения; если же значения знакового разряда и разряда переполнения не совпадают, то исключается младший .разряд, делитель или делимое подается со смещением на один разряд в сторону младших разрядов, а коррекция порядка производится вне устройства. Смещение делителя и делимого реализуется соответственно на элементах И-ИЛИ 25 и 26 блоков 1. На входы элемента И-ИЛИ 26 (i-1 ) разряда подаются соответственно i и (i - 1)

разряды делителя, а на управляющий вход-сигнал анализа переполнения делителя с выхода элемента сумма по модулю два узла 2. На входы элемента И-ИЛИ 25 (i - I ) разряда подают cooTBeTCTBeijHo (i + 1) и i разряды делимого, а на управляемый входсигнал анализа переполнения делимого с выхода злемента сумма по модулю два узла 2, При наличии единицы на управляющих входах есть смещение, при наличии нуля нет. При подаче делимое имеет также постоянное смещение на один разряд вправо.

Работа устройства при изменении

разрядности, которое производится записью единицы с младшего разряда по Т+2 такту в соответствующий элемент 24 памяти разрядности, происходит следующим образом. Старший .разряд делимого и делителя в.сегда записывается в один и тот же разряд, его место фиксируется, а младший разряд смещается в зависимости от разрядности, которая определяется единицей разрядности, записьюаемой в элементы 24 памяти. Во всех более старших разрядах элементов 24 памяти записаны нули. Единица разрядности подается после Т+2 такта с выхода элемента 24

младшего разряда на выход элемента ШШ 29 и- на вход запрета элемента И 38 блокировки этого же разряда. Таким образом, в инверсной ветви младшего разряда всегда подается дополнательная единица как перенос из более младшего разряда, а в прямой ветви блокируется подача переноса из более младшего разряда. Единица разрядности также подается через элемент НЕ 27 на входы элементов И 3942 блокировки предмЛадшего разряда. Первым тактом новаго цикла в элементы 21 и 22 предмладщего разряда запишутся нули, которые будут в них записьтаться каждым тактом вплоть до следующего T-i-2 такта. После первого такта младший разряд данной разряд- 5 ности полностью отключается от предыдуцих разрядов и на его значение и значения более старших разрядов

предыдущие младшему разряды не влияют вне зависимости от состояния эле- Ю ментов 23, 24, 21 и 22 памяти предыдущих младшему разрядов, кроме эле- . ментов 21, 22 памяти предмладшего разряда, в которьрс после первого также обязательно записань нули. С выхо- 5 дов элементов 21 и 22 предмладшего разряда после первого такта нули подаются также на соответствующие входы переноса и разрешения блока 7 об- ,. разования цифр частного, что запреща- 20 ёт распространение опережающего переноса из всех предыдушлх младшему разрядов, а до первого такта после Т+2 такта опережающий перенос на выходе переноса блока 7 определяется принудительно. Значения элементов . 21 - 24 (с учетом нулей в элементах 21 и 22 предмладшего разряда) предыдущих младшему разрядов данной разрадности могут быть произвольными.Буферным устройством, осуществляющим согласование между работой блоков 1 и 7 и последовательным вводом делимого и делителя, является 35 блок 3 входных регистров, а управление разрядностью данного цикла работы блоков 1 и 7 производит блок 4 регистров памяти разрядности. Блок 3 входных регистров содержит N пар 0 входных регистров 48 делимого и делителя ,: которые необходимы для промежуточного хранения чисел при работе с переменной разрядностью, определяемой в момент прихода п состояния по шине 14 управления. Делимое и делитель вводятся последовательно, синхронно, по одному разряду за такт, каждое в свой входной регистр одной пары 48. Делитель и делимое не- 50 зависимо друг от друга могут вводи . ться как старшими разрядами вперед, так и младшими разрядами вперед при условии, что ввод синхронный, а разрядность делимого и делителя одина- 55 кова. Вследствие этого возникают 4 комбинации последовательного синхронного ввода. Разряды делимого подаются на шину 9, а направление его ввода выбирается состоянием .шины 12, если оно нуль, то делимое вводится младшими разрядами вперед, если единица, то старшими разрядами вперед. Разряды делителя подаются на шину 10, а направление его ввода выбирается состоянием шины 13 аналогично выбору направления делимого. Пара регистров, в которые производится ввод делимого и делителя, выбирается единичным сигналом соответствующего .входа переключения записи, сигнал переключения записи присутствует только на одном из входов, а подается на эти входы с выходов дешифратора записи блока 6. Каждый входной регистр пары выполняет следующие функции. При значении входа выбора нуль все разряды регистра находятся в состоянии памяти, при значении входа выбора единица, а входа направления ввода нуль регистр работает как сдвиговый регистр для ввода числа младшими разрядами вперед. При значении входа выбора единица, входа направления ввода единица BxojtjHoe ; значение числа поступает одновременн на все разряды регистра, а запись производится только в тот разряд, на входе управления записи которого ест .единица, остальные разряды останутся в состоянии памяти. Если единица на входах управления записи с каждым тактом последовательно сдвигается от входного старшего разряда к младше- . му, то в данном режиме регистр работает как регистр для ввода числа старшими разрядами. При любом направлении ввода старший разряд числа любой разрядности записывается в старший разряд регистра. Двухканальный переключатель 49 блока 3 по единичному сигналу одного из входов переключения считывания подключает к выходам делимого и делителя блока 3 соответствующие выходы регистров 48 делимого и делителя. В блоке 4 per гистров памяти разрядности содержится несколько статических регистров памяти, по одному для каждой пары входных регистров блока 3. При появлении состояния на входе разрешения записи возможна запись параллельного кода разрядности в регистр, выбран ный единичным сигналом одного из входов выбора записи.

По n + 1 такту в выбранный регист памяти разрядности и одновременно к , регистру 48 соответствующей пары блойа. 3 записываются соответственно код разрядности и п + I разряды делимого и делителя. Считывание кода разрядности в элементы 24 памяти разрядности блоков 1 производится с выходов блока 4, а соответствующий регистр подключается с помощью единичного сигнала одного из входов выбора считывания. Согласование последовательного ввода чисел различной разрядности в блок 3, определения кода разряд ности в блоке 4 с работой блоков I формирования подготовительных функций и блока 7 определения цифр частного производится с помощью блока 6 коммутации ввода-вывода и блока 5 управления. Рассмотрение производится с учетом того, что совместная работа поразрядных блоков 1 , блока 7 и узла 2 описана ранее. Тактовый сигнал с выхода генератора 50 подается на тактовые входы элементов 2-1 - 24 памяти всех блоков 1, узла 2, всех входных регистров 48 блока 3, всех регистров блока 4, счетчика записи, счетчикя считывания, регистра, триггеров блока 6, регистра 51 сдвига, триггеров 53 и 54 блока 5.

Пусть на шину 16 подан сигнал установки, устройство находится в исходном состоянии, это значит, .что триггер 53 установки, триггер 54 n+I состоянии и регистр 5 сдвига блока 5 управления в нулевом состоянии, кроме того, в нулевом состоянии счетчик записи, счетчик считьюания, регистр, триггер Т+1 состояния, триггер Т+2 состояния и триггер блока 6. Все регистры блоков 3 и 4 и элементы памяти блоков 1 и 2 находятся в произвольном состоянии. На выходе элемента РШИ нуль, поэтому сигнал переполнения на шине 18 также .нуль ,что разрешает прохождение сигнала Запуск на 3- вход триггера 53 установки. Сигнал Запуск подается на шину 15. Первым тактом после снятия сигнала установки шины 16 (тот такт имеет номер п+2 цикла ввода) вклю-. чается в единицу триггер 53 установки. Сигнал с выхода триггера 53 подается на шину 17 синхронизации записи, на вход управления установкой в нуль регистра 51 сдвига и на вход

элемента И 55, Снимается управление установкой в нуль регистра 51 разрешена подача п состояния шины 14. В этот момент на выходе элемента ИЛИ-НЕ -52 единица, которая подается на входы старшего разряда всех регистров 48 блока 3. При значении входа направления ввода единица (ввод старшими разрядами вперед) разрешена параллельная запись информации в регистр 48, имеющий на входе выбора единицу, т.е., регистр, соответствующий состоянию нуль счетчика записи. Первым тактом цикла ввода записываются первые разряди делимого и делителя (старший или младший в зависимости от значения входа направления ввода соответствующего регистра), в первый разряд регистра 51 записывается единица, на выходе элемента ИЛИ 52 появляется нуль. -После первого такта единица появляется на входах второго разряда, на остальных входах будут нули. Вторым тактом записьгаается второй разряд делимого и делителя (при подаче старшими разрядами вперед запись во второй разряд, при подаче младшими разрядами вперед сдвиг). Каждым следующим тактом запись делимого и делителя производится аналогично предыдущим и одновременно сдвигается единица в регистр е 51.. По п такту в регистры 48 записываются разряды делимого и делителя, а на шине 14 управления появляется п состояние, которое -поступает через элемент И 55 на К-вход триггера 53 установки, а через элемент И 57 на D-вход триггера 54 n+i состояния, на вход разрешения записи блока 4, на вход управления счетом счетчика записи и на первый вход блока 6. По п+1 такту проис .ходит запись кода разрядности в регистр разрядности блока 4 с нулевм номером, записьшаются n+l разряды делимого и делителя в регистры 48 блока 3 с нулевым номером, регистры 48 делимого, делителя с нулевым номером переходят в состояние памяти записанных чисел. По Т+2 такту происходит считывание из блоков 3 и 4 значений делимого, делителя и кода разрядности в элементы памяти блоков I и узла 2, кода разрядности в регистр блока 6, на шиие 11 образуется значение знакового разряда частHoro. Одновременно с получением частного периого цикла начинается ввод чисел второго цикла. Изменение уровня сигнала на шинах 12 и 13 направления ввода нужно производить по п+2 такту, при 11+1 состоянии на шине 17 синхронизации записи, тогда одновременно с подачей первых разрядов чисел следующего цикла на шины 9 и 10 включается соответствующее направление ввода. Определение момента начала вьщачи соответствующего частного от данных делимого и делителя производится следующим образом. В момент подачи n состояния на шину 14 управления код счетчика записи на шинах 8 соответствует входным регистрам 48 делимого и делителя блока 3, в которые п+1 тактом окончательно записываются данные числа. В момент появления выходного T+l состояния на щине 19 синхронизации считывания код счетчика считывания на шинах 20 соответствует номеру регистров блоков

Примечание. О- 1 - -,

3 и 4, из которых Т+2 тактом в элементы памяти блоков I и узла 2 считываются делимое, делитель, код разрядности. Равенство кодов шин 8 и 20, определяемое для кода шин 20 при состояния шины 19, показьгаает момент выдачи знакового разряда искомого частного, где код шин 8 записан ранее во внешних элементах памяти. При работе с сигналом переполнения шины 18 в качестве сигнала,, останавливающего ввод очередной пары делимого и делителя до его снятия, вводимые

числа могут иметь любую разрядность в пределах от К до М при произвольном количестве регистров в блоках 3 и 4. Если будет превьш1ена емкость блоков 3 и 4, то возникает переполнение и остановка ввода очередной пары чисел. Для исключения остановки ввода минимальная разрядность чисел К должна быть согласована с емкостью блоков

3 и 4.

/fo10/Зо.

a

Ч t

f3 (

-

- -

vr k

Фаг. 1

/4

-о 75 t-o W

17

( t

/

f t

f

j

f f

e-

$

/Г7Г

k //

фиг. Ъ

Фие 5

50

5/

t ; H-1

Ы

Tcftfm

Н

e-074

3cfngcH

k-0/5

J

R

V

С 54 /

ue 6

| Устройство для деления | 1980 |

|

SU903867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Папернов А.А | |||

| Логические основы ЦВТ | |||

| -М.: Сов | |||

| радио, 1972, с | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-12-15—Публикация

1983-02-15—Подача