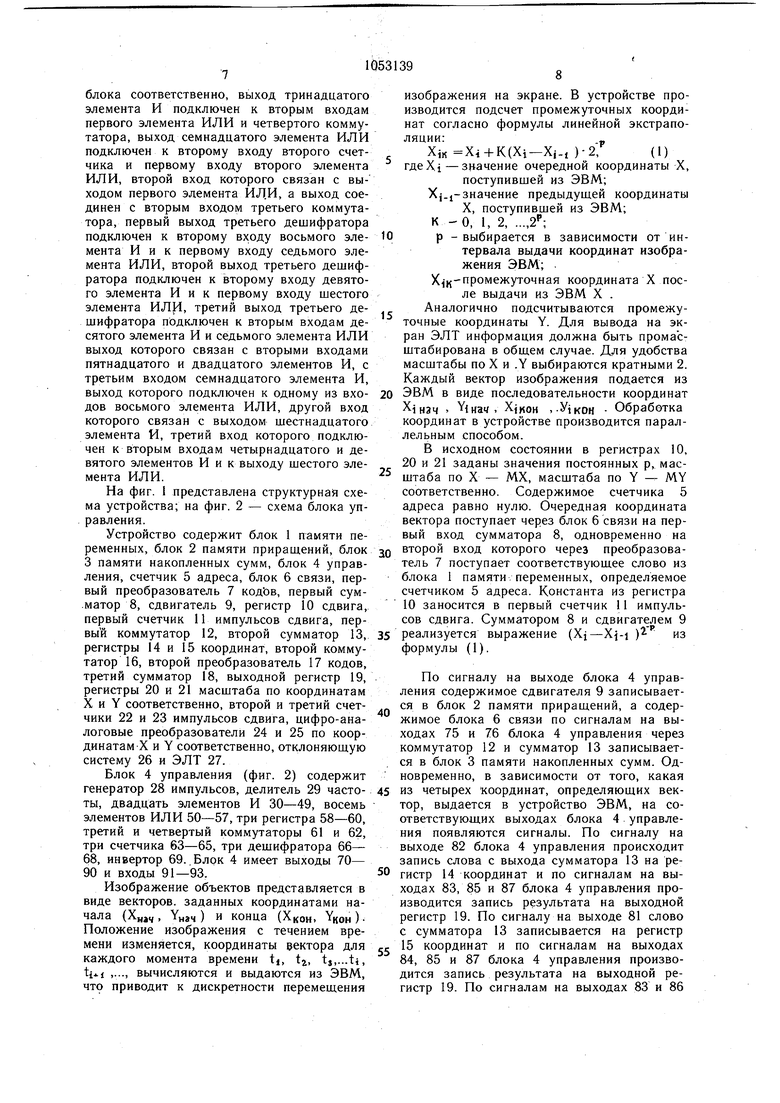

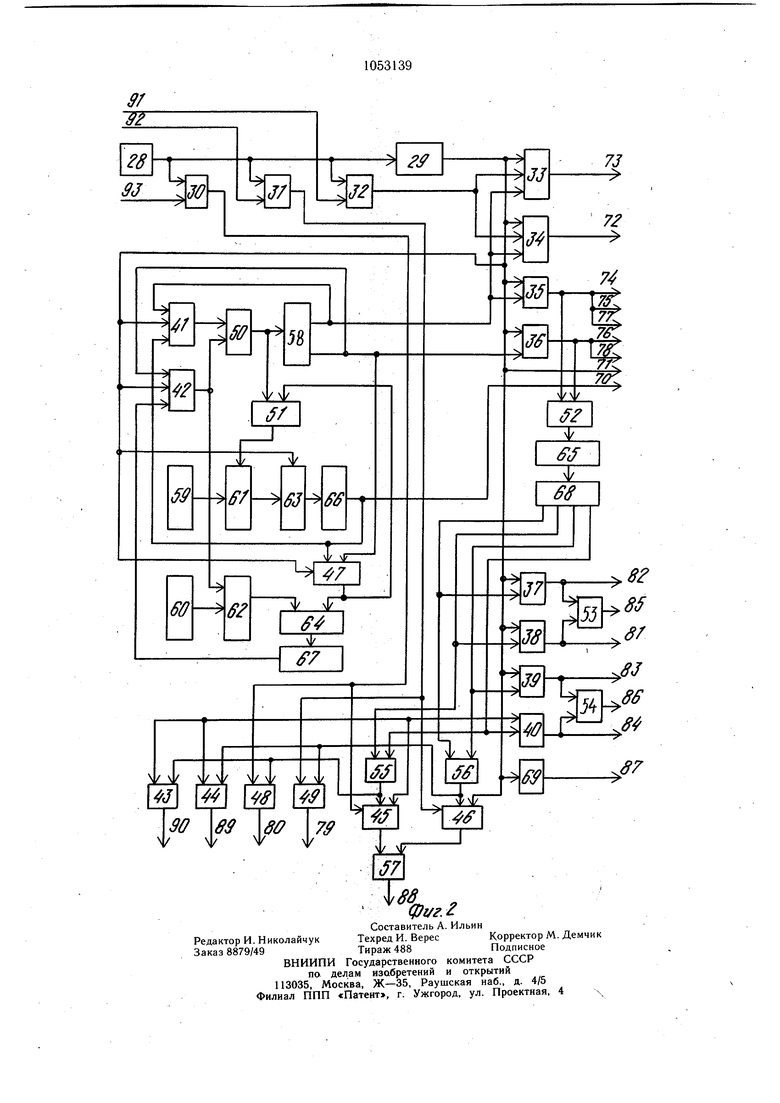

2. Устройство по п. 1, отличающееся тем, что блок управления содержит двадцать элементов И, восемь элементов ИЛИ, три регистра, три счетчика, три дешифратора, третий и четвертый коммутаторы, инвертор, делитель частоты и генератор импульсов, выход которого подключен к входу делителя частоты, первым входам первого, второго и третьего элементов И, вторые входы которых являются первым, вторым и третьим входами блока соответственно, выход делителя частоты подключен, к первым входам с четвертого по двадцатый элементов И, первому счетчику и инвертору, выход двенадцатого элемента И, подключен к первому входу первого элемента ИЛИ, выход которого связан с первым входом второго элемента ИЛИ и входом первого регистра, один из выходов которого подключен к вторым входам четвертого, пятого, шестого и двенадцатого элементов И, другой выход - к вторым входам седьмого тринадцатого и восемнадцатого элементов И, последовательно соединенные второй регистр, третий коммутатор, первый счетчик и Первый дешифратор, выход которого подключен к третьим входам- двенадцатого и восемнадцатого элементов И и является первым выходом блока, выход делителя частоты является вторым выходом блока, последовательно соединенные третий регистр, четвертый коммутатор, второй счетчик и второй дешифратор, выход которого подключен к третьему входу тринадцатого элемента И, выход которого связан с вторыми входами первого элемента ИЛИ и четвертого коммутатора, выход первого элемента И подключен к первому входу девятнадцатого элемента И и второму входу шестнадцатого элемента И, выход второго элемента И связан с первым входом двадцатого элемента И и вторым входом семнадцатого элемента И, выход третьего элемента И подключен к третьим входам пятого и четвертого элементов И, выходы которых являются третьим и четвертым выходами блока соответственно, выход шестого элемента И является пятым, шестым и восьмым выходами блока и подключен к первому входу третьего элемента ИЛИ, выход седьмого элемента И является седьмым и, девятым выходами блока и подключен к второму входу третьего элемента ИЛИ, выход которого через третий счетчик связан с дешифратором, выходы двадцатого и девятнадцатого элементов И являются десятым и одиннадцатым выходами блока соответственно, выходы девятого и весьмого элементов И являются двенадцатым и тринадцатым выходами блока соответственно и подключены к входам четвертого элемента ИЛИ, выходы десятого и одиннадцатого элементов И являются четырнадцатым и пятнадцатым выходами блока соответственно и подключены к входам пятого элемента ИЛИ, выходы четвертого и пятого элементов ИЛИ, инвертора, восьмого элемента ИЛИ, пятнадцатого и четырнадцатого элементов И являются шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым выходами блока соответственно, выход тринадцатого элемента И подключен к вторым входам первого элемента ИЛИ и четвертого коммутатора, выход восемнадцатого элемента И подключен к второму входу второго счетчика и первому входу второго элемента ИЛИ второй вход которого связан с выходом первого элемента ИЛИ, а выход соединен с вторым входом третьего коммутатора, первый выход третьего дешифратора подключен к второму входу восьмого элемента И и к первому входу седьмого элемента ИЛИ, второй выход третьего дешифратора подключен к второму входу девятого элемента Ии к первому входу шестого элемента ИЛИ, третий выход третьего дешифратора подключен к вторым входам десятого элемента И и седьмого элемента ИЛИ, выход которого связан с вторыми входами пятнадцатого и двадцатого элементов И, с третьим входом семнадцатого элемента И, выход которого подключен к одному из входов восьмого элемента ИЛИ, другой вход которого связан с выходом шестнадцатого элемента И, третий вход которого подключен к вторым входам четырнадцатого и девятнадцатого элементов И и к выходу шестого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1983 |

|

SU1254535A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU941987A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Способ отображения графической информации и устройство для его осуществления | 1984 |

|

SU1327154A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Устройство для управления маркером на экране электронно-лучевой трубки | 1988 |

|

SU1689982A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1982 |

|

SU1091177A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки (элт) | 1980 |

|

SU951378A1 |

| Телевизионный имитатор | 1981 |

|

SU965020A1 |

| Генератор векторов | 1985 |

|

SU1278926A1 |

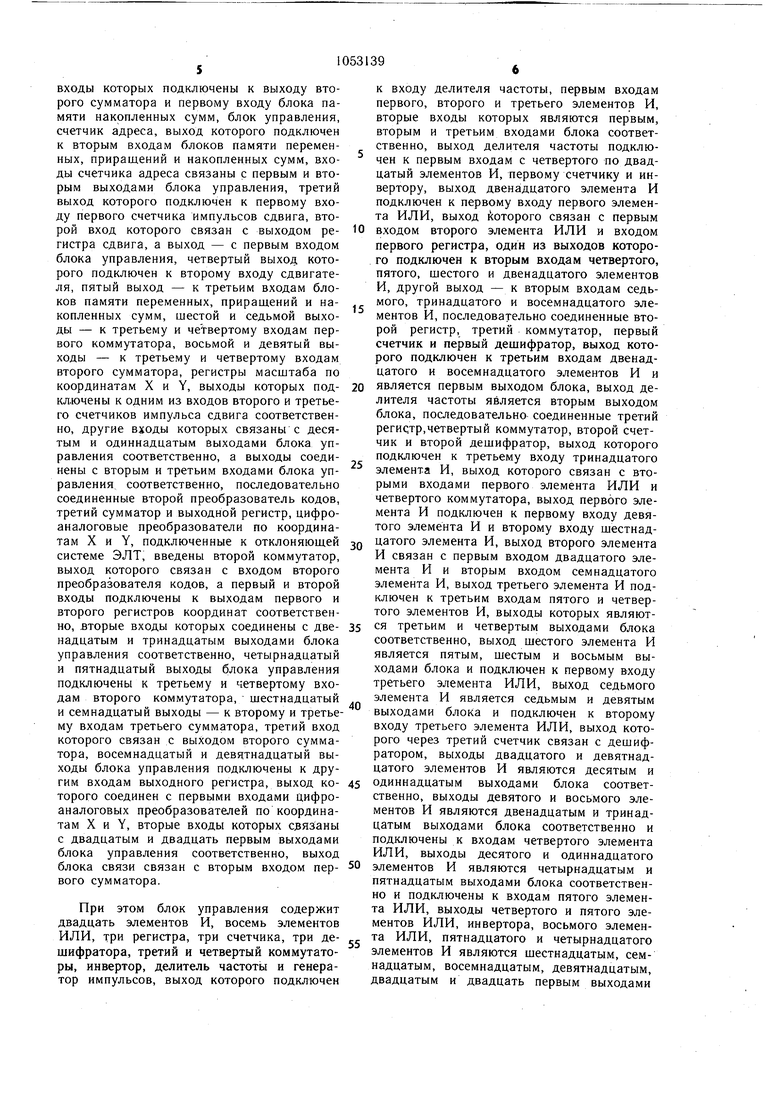

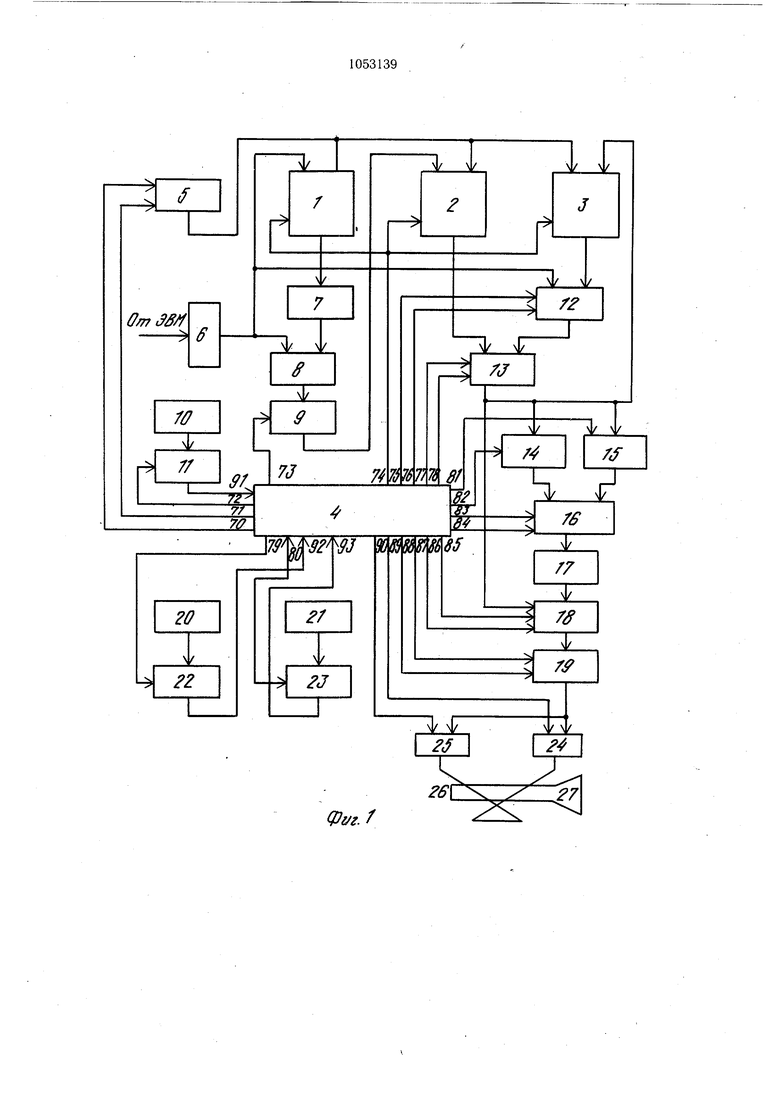

1. УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ НА ЭКРАНЕ ЭЛЕКТРОННО-ЛУЧЕВОЙ ТРУБКИ (ЭЛТ), содержащее последовательно соединенные блок памяти переменных, первый преобразователь кодов, первый сумматор, сдвигатель, блок памяти приращений и второй сумматор, первый коммутатор, выход которого подключен к второму входу второго сумматора, блок памяти накопленных сумм, выход которого связан с первым входом первого коммутатора, блок связи, вход которого является входом устройства, а выход подключен к первому входу блока памяти переменных и второму входу первого коммутатора, первый и второй регистры координат, первые входы которых подключгень к выходу второго сумматора, и первому входу блока памяти накопленных сумм, блок управления, счетчик адреса, выход которого подключен к вторым входам блоков памяти переменных, приращений и накопленных сумм, входы счетчика адреса связаны с первым и вторым выходами блока управления, третий выход которого подключен к первому входу первого счетчика импульсов сдвига, второй вход которого связан с выходом регист4)а сдвига, а выход - с первым входом блока управления, чет-, вертый выход которого подключен к второму входу сдвигателя, пятый выход - к третьим входам блоков памяти переменных, приращений и накопленных сумм, щестой и седьмой выходы - к третьему и четвертому входам первого коммутатора, восьмой и девятый выходы - к третьему и четвертому входам второго сумматора, регистры масщтаба по координатам X и Y, выходы которых подключены к одним из входов второго и третьего счетчиков импульсов сдвига соответственно, другие входы которых связаны с десятым и одиннадцатым выходами блока управления соответственно, а выходы соединены с вторым и третьим входами блока управления соответственно, последовательно соединенные второй преобразователь кодов, третий сумматор и выходI ной регистр, цифро-аналоговые преобразователи по координатам X и Y, подключен(Л ные к отклоняющей системе ЭЛТ, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит второй коммутатор, выход которого связан с входом второго преобразователя кодов, а первый и второй входы подключены к вь1ходам первого и второго регистров координат соответственно, вторые входы которых соединены с двенадцатым и тринадцатым выходами блока управления соответственно, чеел тырнадцатый и пятнадцатый выходы блока со управления подключены к третьему и четвертому входам второго коммутатора, шестнадцатый и семнадцатый выходы - к втосо со рому и третьему входам третьего сумматора, третий вход которого связан с выходом второго сумматора, восемнадцатый и девятнадцатый выходы блока управления подключены к другим входам выходного регистра, выход которого соединен с первыми входами цифро-аналоговых преобразователей по координатам X и Y, вторые входы которых связаны с двадцатым и двадцать первым выходами блока управления соответственно, выход блока связи связан с вторым входом первого сумматора.

Изобретение относится к автоматике, вычислительной технике и может быть использовано при построении устройств для отображения графической информации на экране ЭЛТ. Известно устройство для отображения информации на экране ЭЛТ, используемое для

вывода графической информации из вычислительных машин, содержащее цифро-аналоговые преобразователи по координатам. X и Y, подключенные к отклоняющей системе, световой карандаш, формирователи кодов по осям X и Y, формирователь слова по оси .У, блок сравнения по оси X. блок связи, блок памяти, сумматоры приращений, вычитающий счетчик, сумматор координаты Y, регистр слова по осям X и Y, реверсивный счетчик, блок управления и ЭЛТ Однако при отображении информации быстропротекающих процессов наблюдается прерывность изображения, что снижает точность воспроизведения информации и ухудшает восприятие ее оператором. Наиболее близким- к изобретению по технической сущнрсти является устройство, содержащее цифро-аналоговые преобразователи по координатам, подключенные через отклоняющую систему к ЭЛТ, блок связи, подключенный к электронно-вычислительной мащине и первому сумматору, преобразователь кодов, соединенный с первым сумматором и выходом блока памяти переменных, информационный вход которого подключен к блоку связи, сдвитатель, -соединенный с выходом первого сумматора, информационным входом блока памяти приращений и четвертым выходом блока управления, коммутатор, второй вход которого соединен с выходом блока памяти накопленных сумм, третий и четвертый входы соединены с шестым и седьмым выходами блока управления соответственно, а выход - с вторым входом второго (;умматор.а. первый вход которого соединен с выходом блока памяти приращений, третий и четвертый входы - с восьмым и девятым выходами блока управления соответственно, а выход соединен с информационным входом блока памяти накопленных сумм и с первым и вторым регистрами координат, счетчик адреса, первый и второй входы которого соединены соответственно с первым и вторым выходами блока управления, .а выход соединен с адресными входами блоков памяти, управляющие входь которых подключены к пятому выходу блока управления, первый, второй и третий счетчики импульсов сдвига, первые входы которых соединены с регистром сдвига, регистром маештаба по X и регистром маштаба по Y соответственно, вторые входы соединены с третьим, двадцатым и двадцать первым выходами блока управления соответственно, а выходы соединены соответственно с первым, вторым и третьим входами блока управления, второй преобразователь кодов, соединенный с третьим сумматором, который подключен к выходному регистру. Данномуустройству соответствует блок управления, содержащий генератор такто1вых импульсов, четыре группы элементов И, элемент И, семь элементов ИЛИ, регистр уп равляющих кодов, регистр кодов количества векторов, регистр кодов экстраполяции, две коммутатора, три дешифратора, счетчик количества векторов, счетчик экстраполяции, счетчик координат, делитель частоты, причем генератор тактовых импульсов соединен с делителем частоты и первыми входами первого, второго и третьего элементов И первой группы, вторые входы которых являются соответственно третьим, вторым и первым входами блока управления, выходы делителя частоты соединены с первыми прямыми входами первого, второго, четвертого и инверсным входом третьего элементов И второй группы, вторыми инверсными ВХОг дами элементов И третьей группы, счетчиком количества векторов, инверсным входом элемента И, выход третьего элемента И первой группы соединен с вторыми прямым и, инверсным входами первого и второго элементов И второй группы, рыходы которых являются соответственно четвертым и третьим выходами блока управления, третий коммутатор соединен с регистром кодов количества векторов и счетчиком количества векторов, соединенным с вторым дешифратором, выход которого является первым выходом блока управления, связан с элементом И и первым элементом И третьей группы, четвертый коммутатор соединен с выходами регистра кодов экстраполяции и второго элемента И третьей группы, с выходом счетчика экстраполяции, выход которого подключен к третьему дешифратору, соединенному с вторым элементом И третьей группы, первый элемент ИЛИ подключен к регистру управляющих кодов и второму элементу ИЛИ, подключенному к третьему коммутатору, выход элемента И соединен с входами счетчика экстраполяции и второго элемента ИЛИ, счетчик координат вектора соединен с выходом третьего элемента ИЛИ и входом первого дешифратора 2. Однако в известном устройстве в началь 01 состоянии производится заполнение блоков памяти переменных и приращений без вывода информации на экран, за счет чего снижается быстродействие устройства, а обработка координат последовательно-параллельным способом требует наличии нескольких регистров, преобразователей кодов, сумматоров. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ), содержащее последовательно соединенные блок памяти переменных, первый преобразователь кодов, первый сумматор, первый коммутатор, выход которого подключен к второму входу второго сумматора, блок памяти накопленных сумм, выход которого связан с первым входом первого коммутатора, блок связи, вход которого является входом устройства, а выход подключен к первому входу блока памяти переменных и второму входу первого коммутатора, первый и второй регистры координат, первые входы которых подключены к выходу второго сумматора и первому входу блока памяти накопленных сумм, блок управления, счетчик адреса, выход которого подключен к вторым входам блоков памяти переменных, приращений и накопленных сумм, входы счетчика адреса связаны с первым и вторым выходами блока управления, третий выход которого подключен к первому входу первого счетчика импульсов сдвига, второй вход которого связан с выходом регистра сдвига, а выход - с первым входом блока управления, четвертый выход которого подключен к второму входу сдвигателя, пятый выход - к третьим входам блоков памяти переменных, приращений и накопленных сумм, щестой и седьмой выходы - к третьему и четвертому входам первого коммутатора, восьмой и девятый выходы - к третьему и четвертому входам второго сумматора, регистры масщтаба по координатам X и Y, выходы которых подключены к одним из входов второго и третьего счетчиков импульса сдвига соответственно, другие входы которых связаны с десятым и одиннадцатым выходами блока управления соответственно, а выходы соединены с вторым и третьим входами блока управления соответственно, последовательно соединенные второй преобразователь кодов, третий сумматор и выходной регистр, цифроаналоговые преобразователи по координатам X и Y, подключенные к отклоняющей системе ЭЛТ, введены второй коммутатор, выход которого связан с входом второго преобразователя кодов, а первый и второй входы подключены к выходам первого и второго регистров координат соответственно, вторые входы которых соединены с двенадцатым и тринадцатым выходами блока управления соответственно, четырнадцатый и пятнадцатый выходы блока управления подключены к третьему и четвертому входам второго коммутатора, шестнадцатый и семнадцатый выходы - к второму и третье му входам третьего сумматора, третий вход которого связан с выходом второго сумматора, восемнадцатый и девятнадцатый выходы блока управления подключены к другим входам выходного регистра, выход которого соединен с первыми входами цифроаналоговых преобразователей по координатам X и Y, вторые входы которых связаны с двадцатым и двадцать первым выходами блока управления соответственно, выход блока связи связан с вторым входом первого сумматора. При этом блок управления содержит двадцать элементов И, восемь элементов ИЛИ, три регистра, три счетчика, три дешифратора, третий и четвертый коммутаторы, инвертор, делитель частоты и генератор импульсов, выход которого подключен к входу делителя частоты, первым входам первого, второго и третьего элементов И, вторые входы которых являются первым, вторым и третьим входами блока соответственно, выход делителя частоты подключен к первым входам с четвертого по двадцатый элементов И, первому счетчику и инвертору, выход двенадцатого элемента И подключен к первому входу первого элемента ИЛИ, выход которого связан с первым входом второго элемента ИЛИ и входом первого регистра, один из выходов которого подключен к вторым входам четвертого, пятого, шестого и двенадцатого элементов И, другой выход - к вторым входам седьмого, тринадцатого и восемнадцатого элементов И, последовательно соединенные второй регистр, третий коммутатор, первый счетчик и первый дешифратор, выход которого подключен к третьим входам двенадцатого и восемнадцатого элементов И и является первым выходом блока, выход делителя частоты является вторым выходом блока, последовательно соединенные третий регистр,четвертый коммутатор, второй счетчик и второй дешифратор, выход которого подключен к третьему входу тринадцатого элемента И, выход которого связан с вторыми входами первого элемента ИЛИ и четвертого коммутатора, выход первого элемента И подключен к первому входу девятого элемента И и второму входу шестнадЦ того элемента И, выход второго элемента И связан с первым входом двадцатого элемента И и вторым входом семнадцатого элемента И, выход третьего элемента И подключен к третьим входам пятого и четвертого элементов И, выходы которых являются третьим и четвертым выходами блока соответственно, выход шестого элемента И является пятым, шестым и восьмым выходами блока и подключен к первому входу третьего элемента ИЛИ, выход седьмого элемента И является седьмым и девятым выходами блока и подключен к второму входу третьего элемента ИЛИ, выход которого через третий счетчик связан с дешифратором, выходы двадцатого и девятнадцатого элементов И являются десятым и одиннадцатым выходами блока соответственно, выходы девятого и восьмого элементов И являются двенадцатым и тринадцатым выходами блока соответственно и подключены к входам четвертого элемента ИЛИ, выходы десятого и одиннадцатого элементов И являются четырнадцатым и пятнадцатым выходами блока соответственно и подключены к входам пятого элемента ИЛИ, выходы четвертого и пятого элементов ИЛИ, инвертора, восьмого элемента ИЛИ, пятнадцатого и четырнадцатого элементов И являются шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым выходами блока соответственно, выход тринадцатого элемента И подключен к вторым входам первого элемента ИЛИ и четвертого коммутатора, выход семнадцатого элемента ИЛИ подключен к второму входу второго счетчика и первому входу второго элемента ИЛИ, второй вход которого связан с выходом первого элемента ИДИ, а выход соединен с вторым входом третьего коммутатора, первый выход третьего дешифратора подключен к второму входу восьмого элемента Инк первому входу седьмого элемента ИЛИ, второй выход третьего дешифратора подключен к второму входу девятого элемента Инк первому входу шестого элемента ИЛИ, третий выход третьего дешифратора подключен к вторым входам десятого элемента И и седьмого элемента ИЛИ выход которого связан с вторыми входами пятнадцатого и двадцатого элементов И, с третьим входом семнадцатого элемента И, выход которого подключен к одному из входов восьмого элемента ИЛИ, другой вход которого связан с выходом шестнадцатого элемента И, третий вход которого подключен к вторым входам четырнадцатого и девятого элементов И и к выходу шестого элемента ИЛИ. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - схема блока управления. Устройство содержит блок 1 памяти переменных, блок 2 памяти приращений, блок 3 памяти накопленных сумм, блок 4 управления, счетчик 5 адреса, блок 6 связи, первый преобразователь 7 кодов, первый сум.матор 8, сдвигатель 9, регистр 10 сдвига, первый счетчик 11 импульсов сдвига, первый коммутатор 12, второй сумматор 13, регистры 14 и 15 координат, второй коммутатор 16, второй преобразователь 17 кодов, третий сумматор 18, выходной регистр 19, регистры 20 и 21 масштаба по координатам X и Y соответственно, второй и третий счетчики 22 и 23 импульсов сдвига, цифро-аналоговые преобразователи 24 и 25 по координатам X и Y соответственно, отклоняющую систему 26 и ЭЛТ 27. Блок 4 управления (фиг. 2) содержит генератор 28 импульсов, делитель 29 частоты, двадцать элементов И 30-49, восемь элементов ИЛИ 50-57, три регистра 58-60, третий и четвертый коммутаторы 61 и 62, три счетчика 63-65, три дешифратора 66- 68, инвертор 69. Блок 4 имеет выходы 70- 90 и входы 91-93. Изображение объектов представляется в виде векторов, заданных координатами начала (Х„„, нач ) и конца (Хкон. кон)Положение изображения с течением времени изменяется, координаты ректора для каждого момента времени tj, tj, tj,...ti, ,..., вычисляются и выдаются из ЭВМ, что приводит к дискретности перемещения изображения на экране. В устройстве производится подсчет промежуточных координат согласно формулы линейной экстраполяции:XiK Xi-fK(Xi-Xi..t )-2,(1) гдеХ.1 - значение очередной координаты X, поступившей из ЭВМ; Xj.j-значение предыдушей координаты X, поступившей из ЭВМ; К -О, 1, 2, ...,2 р -выбирается в зависимости от интервала выдачи координат изображения ЭВМ; Xijj-промежуточная координата X после выдачи из ЭВМ X . Аналогично подсчитываются промежуточные координаты Y. Для вывода на экран ЭЛТ информация должна быть промасштабирована в общем случае. Для удобства масштабы по X и .У выбираются кратными 2. Каждый вектор изображения подается из ЭВМ в виде последовательности координат 1нач {нач , XJKOH .-ViKOH Обработка координат в устройстве производится параллельным способом. В исходном состоянии в регистрах 10, 20 и 21 заданы значения постоянных р, масштаба по X - MX, масштаба по У - МУ соответственно. Содержимое счетчика 5 адреса равно нулю. Очередная координата вектора поступает через блок 6 связи на первый вход сумматора 8, одновременно на второй вход которого через преобразователь 7 поступает соответствующее слово из блока 1 памяти/переменных, определяемое счетчиком 5 адреса. Константа из регистра 10 заносится в первый счетчик 11 импульсов сдвига. Сумматором 8 и сдвигателем 9 реализуется выражение (Xj-Х|-1 ) из формулы (1). По сигналу на выходе блока 4 управления содержимое сдвигателя 9 записывается в блок 2 памяти приращений, а содержимое блока 6 связи по сигналам на выходах 75 и 76 блока 4 управления через коммутатор 12 и сумматор 13 записывается в блок 3 памяти накопленных сумм. Одновременно, в зависимости от того, какая из четырех координат, определяющих вектор, выдается в устройство ЭВМ, на соответствующих выходах блока 4 управления появляются сигналы. По сигналу на выходе 82 блока 4 управления происходит запись слова с выхода сумматора 13 на регистр 14 координат и по сигналам на выходах 83, 85 и 87 блока 4 управления производится запись результата на выходной регистр 19. По сигналу на выходе 81 слово с сумматора 13 записывается на регистр 15 координат и по сигналам на выходах 84, 85 и 87 блока 4 управления производится запись результата на выходной регистр 19. По сигналам на выходах 83 и 86

блока 4 управления на первый вход сум: матора 18 поступает слово с сумматора 13, а на второй вход через преобразователь 17 и коммутатор 16 поступает слово с регистра 14 координат. Таким образом вычисляется приращение по X и по сигналу на выходе 87 блока 4 управления производится запись результата на выходной регистр 19. По сигналам на выходах 84 и 86 на первый вход сумматора 18 поступает слово с сумматора 13 и на второй вход через преобразователь 17 и, коммутатор 16 поступает слово с регистра координат 15. Таким образом вычисляется приращение по Y, и по сигналу на выходе блока 4 управления производится запись результата на выходной регистр 19. Каждый раз при этом содержимое регистров 20 и 21 записывается в счетчики 22 и 23 импульсов сдвига и осуществляется сдвиг содержимого выходного регистра 19 согласно заданным масштабам MX, MY. Содержимое выходного регистра по сигналам на выходах блока 4 управления преобразуется в напряжение в блоках 24 или 25 и через отклоняющую систему 26 выводится на экран ЭЛТ 27. Содержимое счетчика 5 адреса по сигналу на выходе блока 4 управления увеличивается на «I, и процесс повторяется. Когда блок 3 памяти накопленных, сумм заполнится значениями координат, выданных с ЭВМ, счетчик 5 адреса устанавливается в «О. Устройство переходит в режим вычисления промежуточных координат.

По сигналу на выходе 76 блока 4 управления информация с блока 3 памяти через коммутатор 12 поступает на второй вход сумматора 13, на первый вход которого поступает соответствующее слово из блока памяти 2 приращений. По сигналу на выходе 78 блока 4 управления на сумматоре 13 реализуется формула (1). По сигналу на выходе 74 блока 4 управления производится запись содержимого сумматора 13 в блок 3 памяти и параллельно, аналогично описанному выще, производится запись на регистры 14 и 15 координат и вывод информации на ЭЛТ. После вывода очередной координаты содержимое счетчика 5 адреса увеличивается на «1. После заполнения блока 3 памяти в нем записаны первые промежуточные значения координат, счетчик 5 адреса устанавливается в «О, и про-, цесс повторяется для К 2,4....

В исходном состоянии в регистре записано количество преобразуемых векторов, в регистре 60 - число к 2. Работу блока управления рассмотрим для случая,когда в регистре 10 задано значение , в регистр 20 занесена «4, а в регистр 21 - «2 (фиг. 1).

Генератор 28 тактовых импульсов формирует серию сигналов С1 с частотой f ,

а на выходе делителя 29 частоты образуется серия сигналов С2 с частотой 4f}.

В работе блока 4 управления выделяем два расстояния. В исходном положении в регистре 58 первый разряд установлен в «1, что определяет первое состояние работы блока управления. По сигналам элементами .32 и 33 на выходе 73 блока 4 управления вырабатывается сигнал сдвига, который поступает на сдвигатель 9, обеспечивая реализацию выражения (Xj-Xij)

По сигналам элементами 34 и 32 на выходе 72 блока 4 управления вырабатывается сигнал, который поступает на первый счетчик 11 импульсов сдвига, и содержимое счетчика уменьшается на «1. Эта операция повторяется четыре раза до установления счетчика 11 в «О. Таким образом реализуется выражение (Х -Xi- ) На выходах 75 и 77 элементом И 35 формируются сигналы, разрешающие прохождение данных с блока 6 связи через коммутатор 12 и запрещающий операцию суммирования на сумматоре 13 (фиг. I).

По сигналу С-2 элементом И 35 на выходе 74 формируется сигнал, осуществляющий запись в блок 2 памяти содержимого сдвигателя 9 и содержимого блока 6 связи в блоки 1 и 2 памяти. С выхода элемента И 35 через элемент ИЛИ 52 поступает сигнал на счетчик 65, увеличивая его содержимое на «1. В зависимости от состояния счетчика появляется сигнал на одном из четырех выходов дешифратора 68, определяющих обработку координат соответственно Хизч , -ti34 , XKOH , ОН По

сигналу на первом выходе дешифратора 68 элементом И 37 формируется сигнал записи в регистр координат 14 на выходе 82 блока управления, а также элементом ИЛИ 53 - сигнал на выходе 85, запрещающий сложение на сумматоре 18.

По сигналу на втором выходе дешифратора 68 элементом 38 формируется сигнал записи в регистр 15 координат на выходе 81 блока 4 управления, а также схемой ИЛИ 53 - сигнал на выходе 85, запрещающий суммирование на сумматоре 18.

По сигналу на третьем выходе дешифратора 68 элементом И 39 формируется сигнал на выходе 83 блока 4 управления, разрещающий прохождение информации с регистра координат 14 через коммутатор 16 и преобразователь 17 на вход сумматора 18, элементом ИЛИ 54 на выходе 86 блока 4 управления формируется сигнал, разрещающий вычисление прираи.1ений по координате X.

По сигналу на четвертом выходе дещифратора 68 элементом И 40 формируется сигнал на выходе 84 блока 4 управления, разрешающий прохождение информации с регистра 15 координат через коммутатор 16 и

преобразователь 17 на вход сумматора 18, элементом ИЛИ 54 на выходе 86 блока 4 управления формируется сигнал, разрешающий вычисление п{)иращений по координате Y. По сигналу С2 инвертором формируется сигнал записи в выходной регистр 19 на выходе 87 блока 4 управления.

По сигналам С2 С1 и сигналам на первом и третьем выходах дешифратора 68 элементами И 31 и 46, элементами ИЛИ 56 и 57 .на выходе 88 блока управления формируется сигнал сдвига на один разряд содержимого выходного регистра 19 в соответствии с содержимым второго счетчика 22 импульсов сдви,га.

По сигналам и сигналам на втором и четвертом выходах дешифратора 68 элементами И 30 и 45, элементами ИЛИ 55, и 57 на выходе 88 блока управления формируется сигнал сдвига на один разряд выходного регистра 19 в соответствии с содержимым третьего счетчика 23 импульсов сдвига.

По сигналам элементами И 31 и 49 формируется сигнал на 79 выходе блока управления, а элементами И 30,48 формируется сигнал на выходе 80 блока 4 управления, по которым содержимое второго и третьего счетчиков импульсов сдвигасоответственно уменьшается на «1.

По сигналу С2 элементом И 44 на вь1ходе 89 блока 4 управления формирует(я управляюший сигнал для цифро-аналогового преобразователя 24, а элементом И 43 на выходе 90 блока управления - управляющий сигнал для цифро-аналогового преобразователя 25. На выходе 71 блока 4 управления формируется сигнал увеличения на «1 содержимого счетчика 5 адреса.

Сигнал С2, поступая на счетный вход 63, уменьшает его содержимое на «1.Описанный процесс продолжается до установления его в «О, о чем свидетельствует сигнал на выходе 70 блока 4 управления, срабатываюший счетчик 5 адреса в .«О. По этому же сигналу через элемент И 41 и элемент ИЛИ 50 осуществляется сдвиг «1 в регистре 58 во второй разряд, определяя этим переход блока 4 управления во второе состояние. Параллельно элементом ИЛИ 51 формируется сигнал перезаписи содержимого регистра 59 кодов чфез коммутатор 61 в счетчик 63. Во втором состоянии по сигналу С2 элементам 36 формируются сигналы на выходах 76 и 78 блока 4 управления, поступающие соответственно на коммутатор 12 и сумматор 13, разрешая прохождение слова с блока 3 памяти накопленных сумм и суммирование со словом, считанным с блока 2 памяти приращений. Остальные сигналы на выходах блока 4 управления вырабатываются аналогично первому состоянию. На выходах 75 и 77 блока 4 управления сигналы не вырабатываются.

По сигналу С2 содержимое счетчика 63 становится равным «О, и сигналом с выхода элемента И 47 через элемент ИЛИ 51 осуществляется перезапись содержимого регистра 59 в счетчик 63, а содержимое счетчика 64 уменьшается на «1. Весь процесс повторяется для нового значения к.

Когда счетчик 64 установится в «О, элементом И 42 и элементои ИЛИ 50 вырабатывается сигнал сдвига для регистра 58 управляющих кодов и «I из второго разряда сдвигается в первый разряд (сдвиг циклический), т. е. блок управления переходит в первое состояние.

Таким образом, при параллельной обработке информации вывод изображения осуществляется непосредственно с момента выдачи слов информации из ЭВМ без предварительной их записи в блок памяти накопленных jCyMM и формирования кодов координат и их приращений по координатам X и Y на выходных регистрах, что приводит к повышению быстродействия устройства а следовательно, и к улучшению качества изображения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1973 |

|

SU449355A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для отображения графической информации на экране электронно-лучевой трубки | 1980 |

|

SU941987A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-11-07—Публикация

1982-05-07—Подача