Изобретение относится к автоматике и вычисл.ительной технике и может быть использовано при построении устройств для отображе ния графической информации, станков с ЧПУ и др.

Цель изобретения - повышение точности генератора.

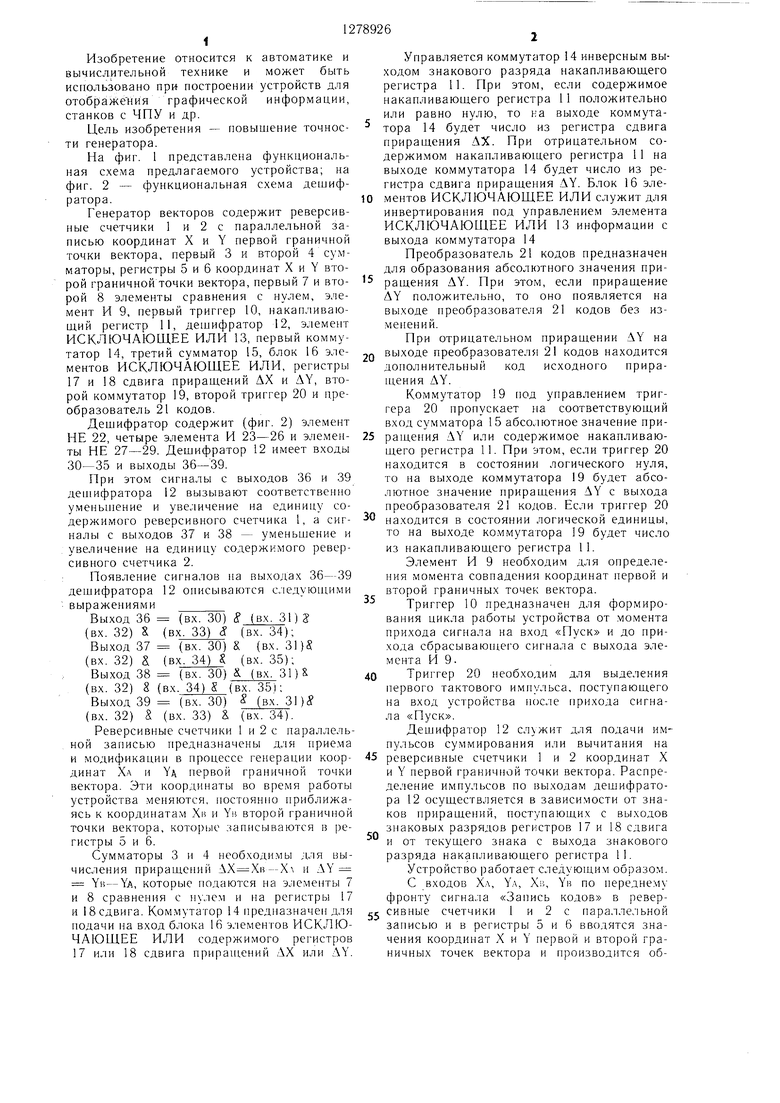

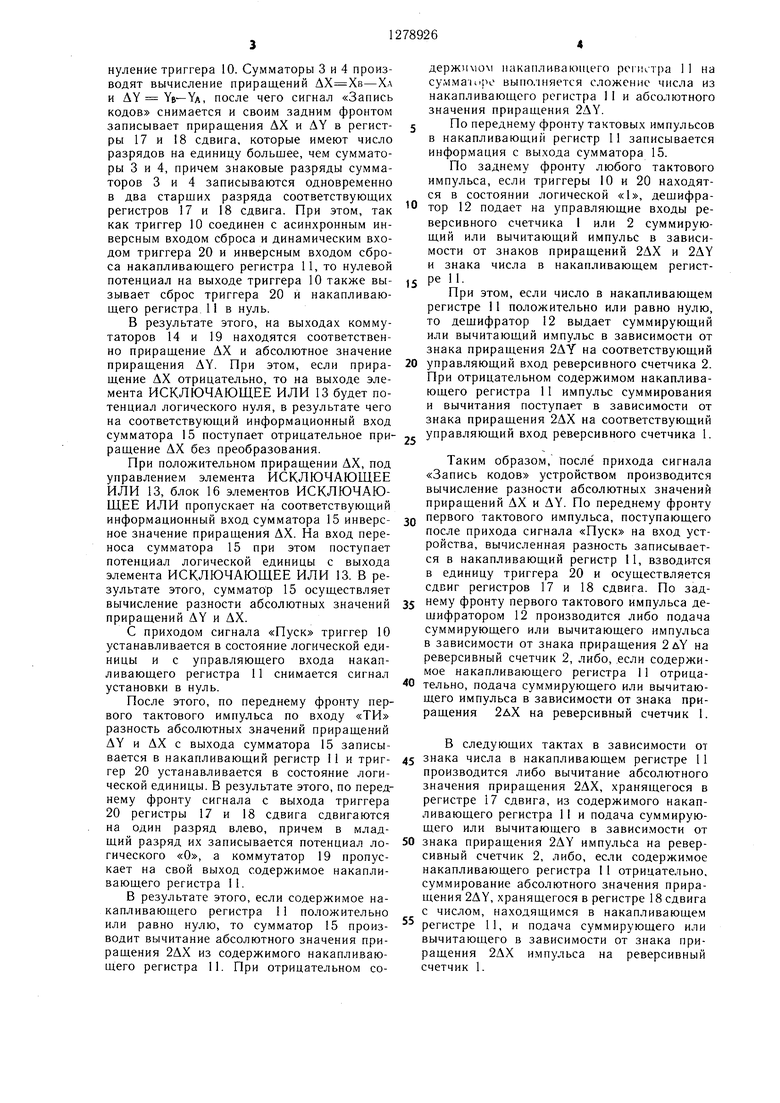

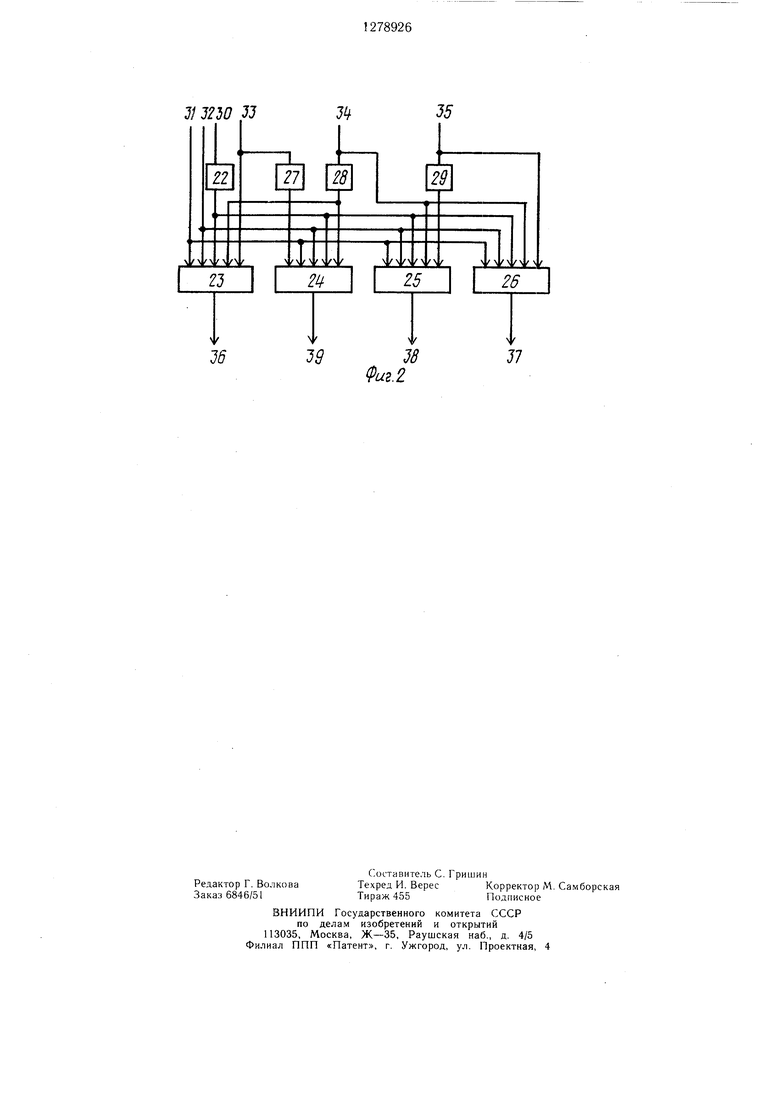

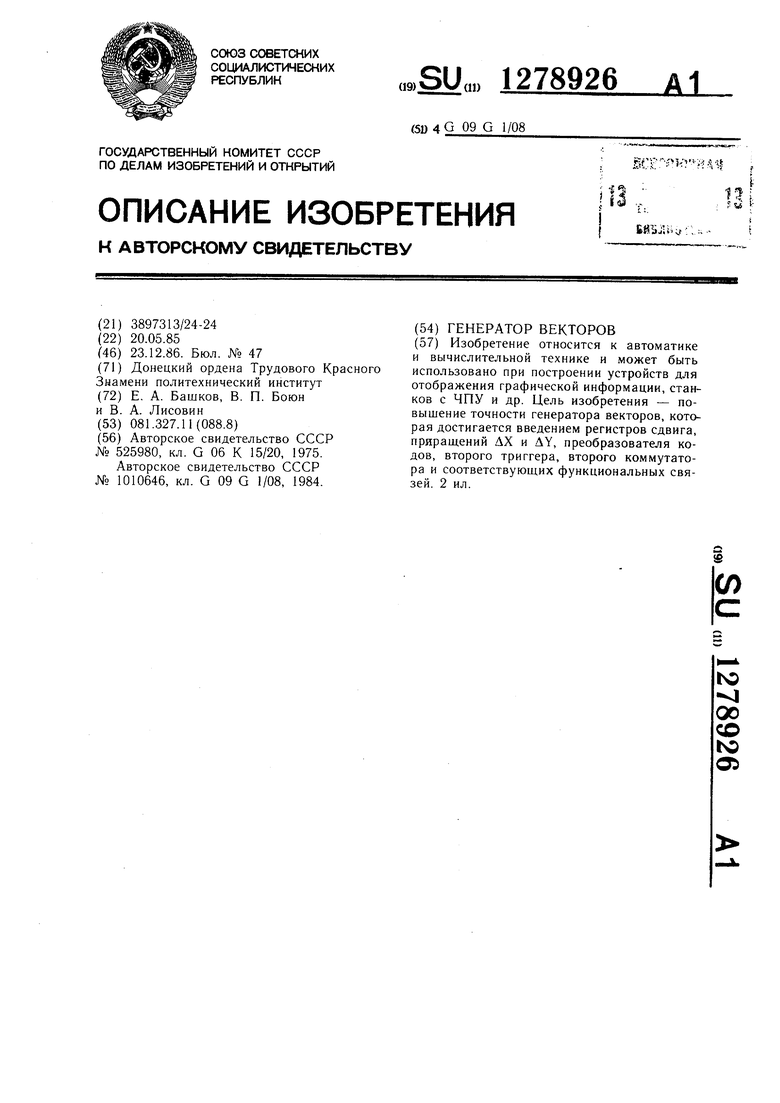

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема дешифратора.

Генератор векторов содержит реверсивные счетчики 1 и 2 с параллельной записью координат X и Y первой граничной точки вектора, первый 3 и второй 4 су.м- маторы, регистры 5 и 6 координат X и Y второй граничной точки вектора, первый 7 и второй 8 элементы сравнения с нулем, элемент И 9, первый триггер 10, накапливающий регистр 11, дешифратор 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первый коммутатор 14, третий сумматор 15, блок 16 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, регистры 17 и 18 сдвига прираш,ений ЛХ и z vY, второй коммутатор 19, второй триггер 20 и преобразователь 21 кодов.

Дешифратор содержит (фиг. 2) элемент НЕ 22, четыре элемента И 23-26 и элементы НЕ 27-29. Дешиф|ратор 12 имеет входы 30-35 и выходы 36-39.

При этом сигналы с выходов 36 и 39 депшфратора 12 вызывают соответственно уменьшение и увеличение на единицу содержимого реверсивного счетчика 1, а сигналы с выходов 37 и 38 - уменьшение и увеличение на единицу содержимого реверсивного счетчика 2.

: Появление сигналов на выходах 36-39 дешифратора 12 онисываются с-ледующими выражениями

Выход 36 (вх. 30) (вх. 32) Е (вх. 33) 8.

Выход 37 (вх. 32) &

Выход 38 (вх. 32) 8

Выход 39

(вх. 32) а

(вх. 30)

(вх. 34) S

(вх. 30)

(вх. 34) S

(вх. 30)

(вх. 33) X

ВХ. З1)г

(вх. 34); & (вх. 31)S

(вх. 35); & (вх. 31)&

вх.

35); (вх.

31)

Реверсивные счетчики

ной записью предназначены для приема и модификации в процессе генерации координат Хл и Уд первой граничной точки вектора. Эти координаты во вре.мя работы устройства меняются, постоянно приближаясь к координатам Хи и Ун второй граничной точки вектора, кото1)ые записываются в регистры 5 и 6.

Сумматоры 3 и 4 необходимы для вычисления прирашепий ЛХ Хи--Х и ЛУ Ун-УА, которые подаются на элементы 7 и 8 сра-внения с нулем и на регистры 17 и 18 сдвига. Коммутатор 14 предназначен для подачи на вход блока 16 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ содержимого регистров 17 или 18 сдвига приращений ДХ или ЛУ.

вх. 34).

и 2 с параллель

0

5

0

5

0

5

0

5

Управляется коммутатор 14 инверсным выходом знакового разряда накапливающего регистра 11. При этом, если содержимое накапливающего регистра 11 положительно или равно нулю, то ка выходе коммутатора 14 будет число из регистра сдвига приращения ДХ. При отрицательном содержимом накапливаю1цего регистра 11 на выходе коммутатора 14 будет число из регистра сдвига приращения ДУ. Блок 16 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ служит для инвертирования под управлением элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 информации с выхода коммутатора 14

Преобразователь 21 кодов предназначен для образования абсолютного значения приращения АУ. При этом, если приращение ДУ положительно, то оно появляется на выходе преобразователя 21 кодов без изменений.

При отрицательном приращении ДУ на выходе преобразователя 21 кодов находится дополнительный код исходного прира- Н1,ения ДУ.

Коммутатор 19 под управлением триггера 20 пропускает на соответствующий вход сумматора 15 абсолютное значение приращения ДУ или содержимое накапливающего регистра 11. При этом, если триггер 20 находится в состоянии логического нуля, то на выходе коммутатора 19 будет абсолютное значение приращения ДУ с выхода преобразователя 21 кодов. Если триггер 20 находится в состоянии логической единицы, то на выходе коммутатора 19 будет число из накапливающего регистра 11.

Элемент И 9 необходим для определения момента совпадения координат первой и второй граничных точек вектора.

Триггер 10 предназначен для формирования цикла работы устройства от момента прихода сигнала на вход «Пуск и до прихода сбрасываюпхег О c пнaлa с выхода элемента И 9.

Триггер 20 необходим для выделения первого тактового импульса, поступающего на вход устройства после прихода сигнала «Пуск.

Дешифратор 12 служит для подачи импульсов суммирования или вычитания на реверсивные счетчики 1 и 2 координат X и У первой граничной точки вектора. Распределение импульсов по выходам дешифратора 12 осуществляется в зависимости от знаков приращений, поступающих с выходов знаковых разрядов регистров 17 и 18 сдвига и от текущего знака с выхода знакового разряда накапливающего регистра И.

Устройство работает следуюпщм образом.

С входов Хл, У., Xii, Ув по переднему фронту сигнала «Запись кодов в реверсивные счетчики 1 и 2 с параллельной записью и в регистры 5 и 6 вводятся значения координат X и Y первой и второй граничных точек вектора и производится обнуление триггера 10. Сумматоры 3 и 4 производят вычисление приращений АХ Хв-Хл и AY YB-YA, после чего сигнал «Запись кодов снимается и своим задним фронтом записывает приращения ЛХ и AY в регистры 17 и 18 сдвига, которые имеют число разрядов на единицу больщее, чем сумматоры 3 и 4, причем знаковые разряды сумматоров 3 и 4 записываются одновременно в два старших разряда соответствующих регистров 17 и 18 сдвига. При этом, так как триггер 10 соединен с асинхронным инверсным входом сброса и динамическим входом триггера 20 и инверсным входом сброса накапливающего регистра 11, то нулевой потенциал на выходе триггера 10 также вызывает сброс триггера 20 и накапливающего регистра 11 в нуль.

В результате этого, на выходах коммутаторов 14 и 19 находятся соответственно приращение ДХ и абсолютное значение приращения AY. При этом, если приращение АХ отрицательно, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 будет потенциал логического нуля, в результате чего на соответствующий информационный вход сумматора 15 поступает отрицательное приращение АХ без преобразования.

При положительном приращении АХ, под управлением элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13, блок 16 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ пропускает на соответствующий информационный вход сумматора 15 инверсное значение приращения АХ. На вход переноса сумматора 15 при этом поступает потенциал логической единицы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13. В результате этого, сумматор 15 осуществляет вычисление разности абсолютных значений приращений AY и АХ.

С приходом сигнала «Пуск триггер 10 устанавливается в состояние логической единицы и с управляющего входа накапливающего регистра 11 снимается сигнал установки в нуль.

После этого, по переднему фронту первого тактового импульса по входу «ТИ разность абсолютных значений приращений AY и АХ с выхода сумматора 15 записывается в накапливающий регистр 11 и триггер 20 устанавливается в состояние логической единицы. В результате этого, по переднему фронту сигнала с выхода триггера 20 регистры 17 и 18 сдвига сдвигаются на один разряд влево, причем в млад- щий разряд их записывается потенциал логического «О, а коммутатор 19 пропускает на свой выход содержимое накапливающего регистра 11.

В результате этого, если содержимое накапливающего регистра 11 положительно или равно нулю, то сумматор 15 производит вычитание абсолютного значения приращения 2АХ из содержимого накапливающего регистра II. При отрицательном содержимом накапливающего роги1.-тра 1 1 на сумма 11 4 выпо.чняется сложение числа из накапливающего регистра 1 I и абсолютного значения приращения 2AY.

По переднему фронту тактовых импульсов

в накапливающий регистр 11 записывается информация с выхода сумматора 15.

По заднему фронту любого тактового импульса, если триггеры 10 и 20 находятся в состоянии логической «1, дещифра- 0 тор 12 подает на управляющие входы реверсивного счетчика 1 или 2 суммирующий или вычитающий импульс в зависимости от знаков приращений 2АХ и 2AY и знака числа в накапливающем регист5 Р

При этом, если число в накапливающем

регистре 11 положительно или равно нулю, то дешифратор 12 выдает суммирующий или вычитающий импульс в зависимости от знака приращения 2AY на соответствующий 0 управляющий вход реверсивного счетчика 2. При отрицательном содержимом накапливающего регистра 11 импульс суммирования и вычитания поступает в зависимости от знака приращения 2АХ на соответствующий управляющий вход реверсивного счетчика 1.

Таким образом, после прихода сигнала «Запись кодов устройством производится вычисление разности абсолютных значений приращений АХ и AY. По переднему фронту

Q первого тактового импульса, поступающего после прихода сигнала «Пуск на вход устройства, вычисленная разность записывается в накапливающий регистр 11, взводится в единицу триггера 20 и осуществляется сдвиг регистров 17 и 18 сдвига. По заднему фронту первого тактового импульса дешифратором 12 производится либо подача суммирующего или вычитающего импульса в зависимости от знака приращения 2 AY на реверсивный счетчик 2, либо, .если содержимое накапливающего регистра 11 отрицательно, подача суммирующего или вычитающего импульса в зависимости от знака приращения 2АХ на реверсивный счетчик 1.

В следующих тактах в зависимости от 5 знака числа в накапливающем регистре 11 производится либо вычитание абсолютного значения приращения 2АХ, хранящегося в регистре 17 сдвига, из содержимого накапливающего регистра II и подача суммирующего или вычитающего в зависимости от 0 знака приращения 2AY импульса на реверсивный счетчик 2, либо, если содержимое накапливающего регистра I 1 отрицательно, суммирование абсолютного значения приращения 2AY, хранящегося в регистре 18 сдвига с числом, находящимся в накапливающем 5 регистре 11, и подача суммирующего или вычитающего в зависимости от знака приращения 2АХ импульса на реверсивный счетчик 1.

Цикл работы продолжается до поступления на элемент И 9 сигналов с выходов элементов 7 и 8 сравнения с нулем, говорящих о том, что текущие координаты X и Y первой граничной точки вектора, находящиеся в реверсивных счетчиках 1 и 2, стали равны координатам X и Y второй граничной точки вектора, записанным в регистры 5 и 6. Элемент И 9 при этом сбрасывает триггер 10, на чем работа устройства заканчивается.

Формула изобретения

Генератор векторов, содержащий реверсивные счетчики с параллел1зной записью

с выходом третьего сумматора, первый и второй входы которого соединены соответственно с выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы блока элементов ИСКЛЮЧА5 ЮЩЕЕ ИЛИ соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым выходом первого коммутатора, второй выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

to первый выход накапливающего регистра соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третьим входом первого коммутатора и третьим входом дешифратора, выходы которого соединены с третьим и четвертым входами соответственно реверкоординат X и Y первой граничной точки 15 сивнь х счетчиков с параллельной записью

координат X и Y первой граничной точки вектора, отличающийся тем, что, с целью повышения точности, он содержит регистры сдвига приращений ДХ и AY, первые входы

вектора, первые входы которых являются входами подачи координат первой граничной точки вектора генератора, выходы которых подключены соответственно к одним из входов первого и второго сумматоров, другие которых подключены к выходам соответствходы которых подключены к выходам соответствующих регистров координат X и Y второй граничной точки вектора, первые входы которых являются входами подачи координат второй граничной точки вектора генератора, а вторые входы реверсивных счетчиков с параллельной записью координат X и Y первой граничной точки вектора являются входом «Запись кодов генератора, выходы первого и второго сумматоров соединены с первыми входами первого и втовенно первого и второго сумматоров, вторые входы являются входом «Запись кодов генератора, первые выходы соединены соответственно с четвертым и пятым входами де- щифратора, второй триггер, первый вход 25 которого является входом «ТИ генератора, а второй вход соединен с выходом первого триггера, и последовательно соединенные преобразователь кодов, вход которого подключен к второму выходу регистра сдвига приращения AY, связанного с первым входом

рого элементов сравнения с нулем соот- 30 первого коммутатора, второй вход которого

ветственно, выходы которых соединены с входами элемента И, выход которого подключен к первому входу первого триггера, второй вход которого является входом «Пуск, а третий вход - входом «Запись кодов

связан с вторым выходом регистра сдвига приращения АХ, и второй коммутатор, второй вход которого подключен к второму выходу накапливающего устройства, третий вход - к выходу второго триггера, свягенератора, выход первого триггера соеди- занному с шестым входом дешифратора и

нен с первыми входами накапливающего регистра и дешифратора, вторые входы которых являются входом «ТИ устройства, третий вход накапливающего регистра соединен

с выходом третьего сумматора, первый и второй входы которого соединены соответственно с выходами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым выходом первого коммутатора, второй выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,

первый выход накапливающего регистра соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третьим входом первого коммутатора и третьим входом дешифратора, выходы которого соединены с третьим и четвертым входами соответственно реверсивнь х счетчиков с параллельной записью

которых подключены к выходам соответственно первого и второго сумматоров, вторые входы являются входом «Запись кодов генератора, первые выходы соединены соответственно с четвертым и пятым входами де- щифратора, второй триггер, первый вход 25 которого является входом «ТИ генератора, а второй вход соединен с выходом первого триггера, и последовательно соединенные преобразователь кодов, вход которого подключен к второму выходу регистра сдвига приращения AY, связанного с первым входом

30 первого коммутатора, второй вход которого

связан с вторым выходом регистра сдвига приращения АХ, и второй коммутатор, второй вход которого подключен к второму выходу накапливающего устройства, третий вход - к выходу второго триггера, связанному с шестым входом дешифратора и

третьими входами регистров сдвига приращений АХ и AY, выход второго коммутатора соединен с третьим входом третьего сумматора.

Ц. Залисд

J/ Jf JJ

J

Редактор Г. Волкова Заказ 6846/51

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

J5

Составитель С. Гришин

Техред И. ВересКорректор М. Самборская

Тираж 455Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор векторов | 1986 |

|

SU1361613A1 |

| Генератор векторов | 1985 |

|

SU1264232A1 |

| Генератор векторов | 1985 |

|

SU1300541A1 |

| Генератор векторов | 1988 |

|

SU1596375A2 |

| Генератор векторов | 1989 |

|

SU1654863A1 |

| Генератор векторов | 1987 |

|

SU1462403A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Устройство для поворота изображе-Ния СиМВОлОВ | 1979 |

|

SU841030A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении устройств для отображения графической информации, станков с ЧПУ и др. Цель изобретения - повышение точности генератора векторов, которая достигается введением регистров сдвига, приращений ДХ и ДУ, преобразователя кодов, второго триггера, второго коммутатора и соответствующих функциональных связей. 2 ил. 1С 00 UD ю О)

| Генератор векторов для системы отображения графической информации | 1974 |

|

SU525980A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор векторов | 1981 |

|

SU1010646A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-12-23—Публикация

1985-05-20—Подача