сд

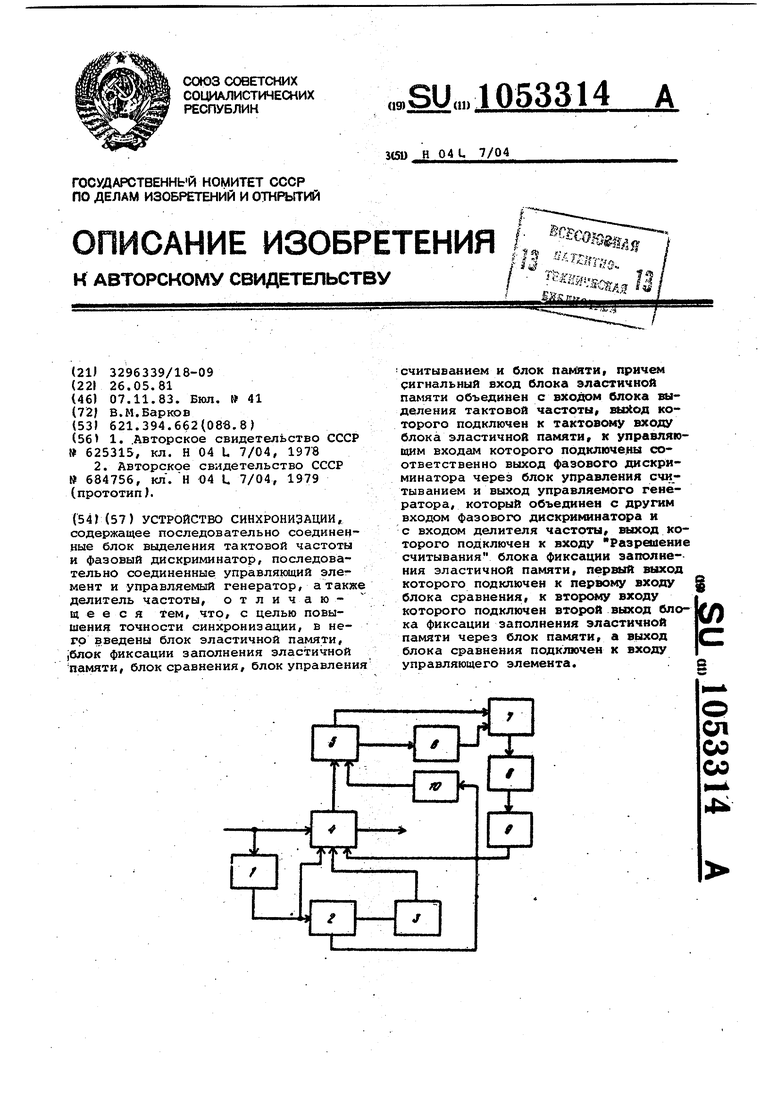

00 со Изобретение относится к технике связи и может быть использовано для синхронизации генераторов через симплексный канал цифровой связи, а также в системах радиосвязи с врейенным уплотнением. Известно устройство синхронизации содержащее последовательно соединенные блок приемо-передачи, блок фазовой автоподстройки частоты (ФАПЧ, фазовый дискриминатор, фильтр-экстраполятор и перестраиваемый генератор, а также генератор цифровых сигналов, при этом другой .выход блока приемо-передачи подключен к другo л входу фазового дискриминатора, выход перестраиваемого генератора через последовательно соединенные смеситель и полосовой фильтр подключен к входу генератора цифровых сигналов причем выход блока ФАПЧ подключен к дpyгo 5y входу смесителя С13 Недостаток известного устройства низкая точность синхронизации. Наиболее близким техническим решением к изобретению является устрой Ьтво синхронизации, содержащее после довательно соединенные блок выделени тактовой частоты и фазовый дискриминатор, последовательно соединенные управляющий элемент и управляемый генератор, а также делитель частоты, включенный между выходом управляющего элемента и фазовым дискриминатором, последовательно соединенные дополнительный делитель частоты и элемент ИЛИ, другой вход которого соеди .йен с выходом блока выделения Tsuxtoвой частоты, а выход элемента ИЛИ подключен к управляющему входу управляющего элемента С2. Недостатком известного устрСйства является низкая точная синхронизация Цель изобретения - повьлаение точности синхронизации. Цель достигается тем что в устройство синхронизации,-содержащее последовательно соединенные блок выделения тактовой частоты и фазовый дискриминатор, последовательно соеди ненные управляющий элемент и управляемый генератор, а также делитель частоты, введены блок эластичной памяти, блок фиксации заполнения эластичной памяти, блок сравнения, блок управления считыванием и блок памяти причем сигнальный вход блока эластичной памяти объединен с входом бло ка выделения тактовой частоты, выход которого подключен к тактовому входу блока эластичной памяти,, к управляющим входам которого подключены соответственно выход фазового дискримина тора через блок управления считыванием и выход управляемого генератора, который объединен с другим вхо дом фазового дискриминатора и с входом делителя частоты, выход которого подключен к входу Разрешение считывания блока фиксации заполнения эластичной памяти, первый выход которого подключен к первому входу блока сравнения, к второму входу которого подключен второй выход блока фиксации заполнения эластичной памяти через блок памяти, а выход блока сравнения подключен к входу управляющего, элемента. На чертеже представлена структурная электрическая схема Лредложенного устройства. Устройство синхронизации содержит блок 1 выделения тактово й частоты, фазовый дискриминатор 2, блок 3 управления считыванием, блок 4 эластичной памяти, блок 5 фиксации заполнения эластичной памяти, блок б памяти, блoк 7 сравнения, управляющий элемент 8, управляемый генератор 9 и делитель частоты 10. Устройство работает следующим образом. Информационный сигнал поступает на вход блока 4 эластичной памяти и на блок выделения тактовой частоты, который выделяет тактовую частоту из информационного сигнала. Выделенная тактовая частота поступает на второй вход блока 4 эластичной памяти и на первый вход фазового дисг криминатора 2, на другой вход кото-г рого поступает тактовая частота уп-.. равляемого генератора 9. В результате сравнения фаз тактовой частоты входного сигнала и управляемого генератора 9 формируется сигнал рассогласования фаз. Этот сигнал поступает; на вход блока 3 управления считыванием, который дает команду на считывание с соответствующей ячейки блока 4 эластичной памяти при расхождении фаз между тактовой частотой входного сигнала и управляемого генератора 9 больше определенной величины (в -сторону увеличения задержки при увеличении расхождения и уменьшения задержки при уменьшении расхождения), управляя считыванием можно изменить величину задержки сигнала в блоке 4 эластичной памяти. Таким образом, компенсация изменения задержки сигнала в линии происходит при помощи переключения ячеек блока 4 эластичной памяти, причем при увеличении задержки сигнала в линии задержки сигнгша в блоке 4 эластичной памяти уменьшается, и наоборот. Поэтому величина задержки сигнала на выходе блока 4 эластичной памяти одинакова и не зависит от.изменения задержки сигнала в линии. Считанная информация с первого выхода блока 4 эластичной памяти поступает на выход устройства, а с второго выхода - на вход блока 5 фиксации заполнения эласти 4г.

НОЙ памяти, управляемый с выхода : управляемого генератора 9 через делитель 10 частоты, который формирует период подстройки. Сформированный сигнсш на выходе делителя 10 частоты состоит из пачки мпульсов, частота которых равна частоте подстройки управляемого генератора , а количество импульсов в пачке соответствует количеству ячеек в блоке 4 эластичной памяти. С помощью этого сигнала поступает разрешение на считывание информации, заключенной в блоке 5 фиксации заполнения эластичной памяти, который фиксирует последовательно те ячейки эластичной памяти , с которых считывалась информация за период под; стройки упрдвляе- мого reHepaiTopa 9. Количество разных ячеек блока 4 эластичной с которых считывалась информация за рассматриваемый период, определяет длительность импульса, который формируется в блоке 5 фиксации заполнения эластичной памяти, с выхода которого информация поступает на вхол блока 7 сравнения и.на вход блока 6 памяти. Поступающая на эти блоки информация представляет собой последовательность импульсов, причем чем больше количество импульсов.

тем больше из;1енение задержки сигнала в блоке 4 эластичной па:ляти имело место за рассматриваемый период. После считывания информации о задержке производится сброс. На другой вход блока 7 сравнения поступает сигнал с выхода блока б памя- та, который обеспечивает запоминание информации.от блока 5 фиксации заполнения эластичной Памяти на

0 один период работы устройства .синхронизации, при.чем он запоминает то количество тактовых иьшульсов которое поступает от блока 5 фиксации заполнения эластичной пвалятя,

5

Блок 7 сравнения по разности между сравниваемыми сигналами; вырабатывает сигнал подстройки частоты, который поступает на управляющий элемент 8, в котором форгдаруется сигнал для подстройки частоты управляе0мого генератора 9

Предлагаемое устройство синхронизации позволяет синхронизировать генераторы на приеме независимо от

5 изменения задержки в линии, .кроме того, данное устройство позволяет принимать сигналы точного времени через, например, спутниковые каналы с высокой точностью

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство асинхронного ввода двоичной информации в цифровой канал связи | 1982 |

|

SU1059633A1 |

| Устройство выделения тактовых импульсов | 1982 |

|

SU1062880A1 |

| Устройство тактовой синхронизации регенератора радиоканала | 1980 |

|

SU882012A1 |

| Устройство взаимной синхронизации тактовых генераторов сети связи | 1979 |

|

SU773945A1 |

| Устройство для приема дискретнойиНфОРМАции | 1979 |

|

SU794768A1 |

| Цифровой когерентный демодулятор сигналов относительной фазовой модуляции | 1975 |

|

SU557508A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Устройство для приема дискретной информации | 1983 |

|

SU1111260A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

УСТРОЙСТЮ СИНХРОНИЗАЦИИ, содержащее последовательно соединенные блок выделения тактовой частоты и фазовый дискриминатор, последовательно соединенные управляющий элемент и управляемый генератор, а также делитель частоты, отличающееся тем, что, с целью повышения точности синхронизации, в негр введены блок эластичной памяти, ;блок фиксации заполнения эластичной памяти, блок сравнения, блок управления считыванием и блок памяти, причем сигнальный вход блока эластичной памяти объединен с входом блока выделения тактовой частоты, выЯод которого подключен к тактовому входу блока эластичной памяти, к управляющим входам которого подключе.ны соответственно выход фазового дискриминатора через блок управления считыванием и выход управляемого генератора, который объединен с другим входом фазового дискриминатора и с входом делителя частоты, выход которого подключен к входу Разрешение считывания блока фиксации заполне-ния эластичной памяти, первый выход которого подключен к первому входу блока сравнения, к входу которого подключен второй выход блока фиксации заполнения эластичной памяти через блок памяти, а выход блока сравнения подключен к входу управляющего элемента.

Авторы

Даты

1983-11-07—Публикация

1981-05-26—Подача