к входам второго элемента ИЛИ, примем второй выход дешифратора подключен к первым входам блока триггеров, вторые входы которого соединены с соответствующими вторыми выходами формирователей импульсов, а выходы блока

триггеров через третий элемент, ИЛИ подклюмены к первому входу четвертого элемента ИЛИ втррой вход которого соединен с .выходом первого рлемента И, а выход четвертого элемента ИЛИ соединен с входом шифратора, шина сброса через ключ сброса соединена с вторым входом формирователей импульсов и является вторым выходом блока управления, выход третьего элемента И является первым выходом блока управления, выход второго элемента И является третьим выходом блока управления, выход первого элемент-а И является, четвертым выходом блока управления, выходы второго и третьего элементов ИЛИ являются соответственно пятым и шестым выходами блока управления, а выход шифратора является седьмым выходом , .блока управления,вход счетчику импульсов является первым входом блока управления, а третьи входы формирователей импульсов являются вторыми входами блока управления,

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для ввода информации | 1983 |

|

SU1092486A1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| Шифратор | 1985 |

|

SU1298802A2 |

| Полевая телеметрическая сейсмическая станция | 1986 |

|

SU1368837A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| УСТРОЙСТВО ДЛЯ ОБЪЕДИНЕНИЯ ЛЕКСИЧЕСКИХ МНОЖЕСТВ | 1990 |

|

RU2022354C1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для управления сортировкой штучных изделий | 1982 |

|

SU1375535A1 |

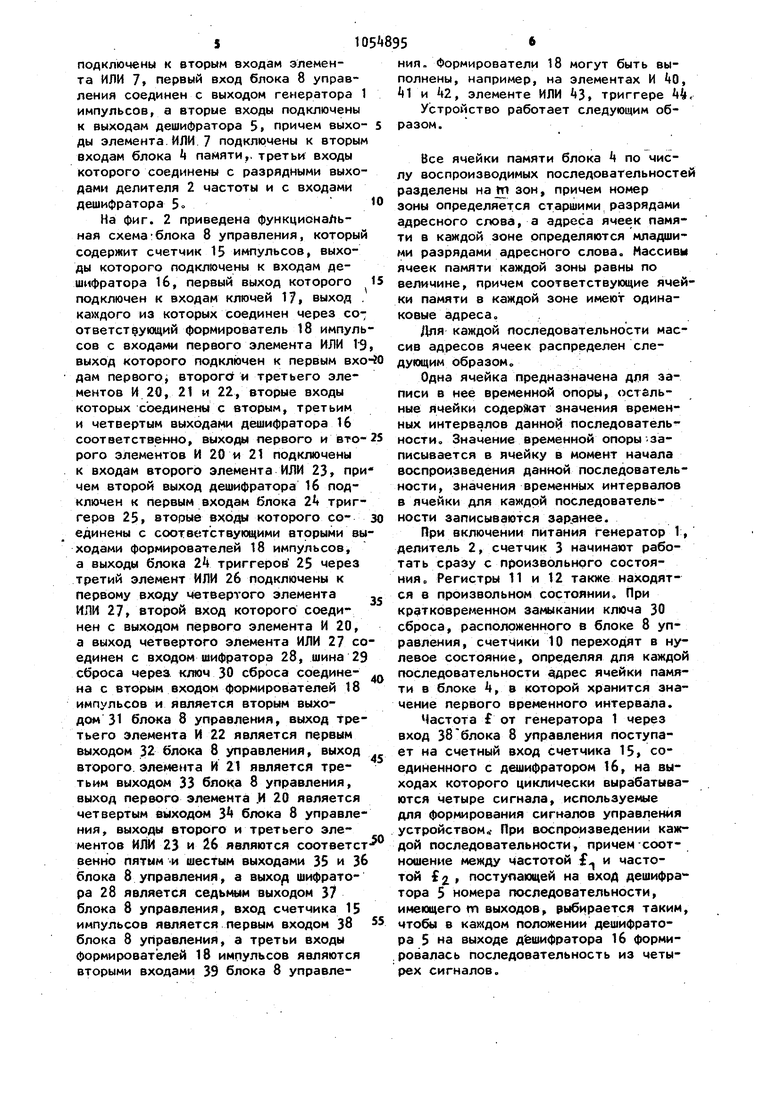

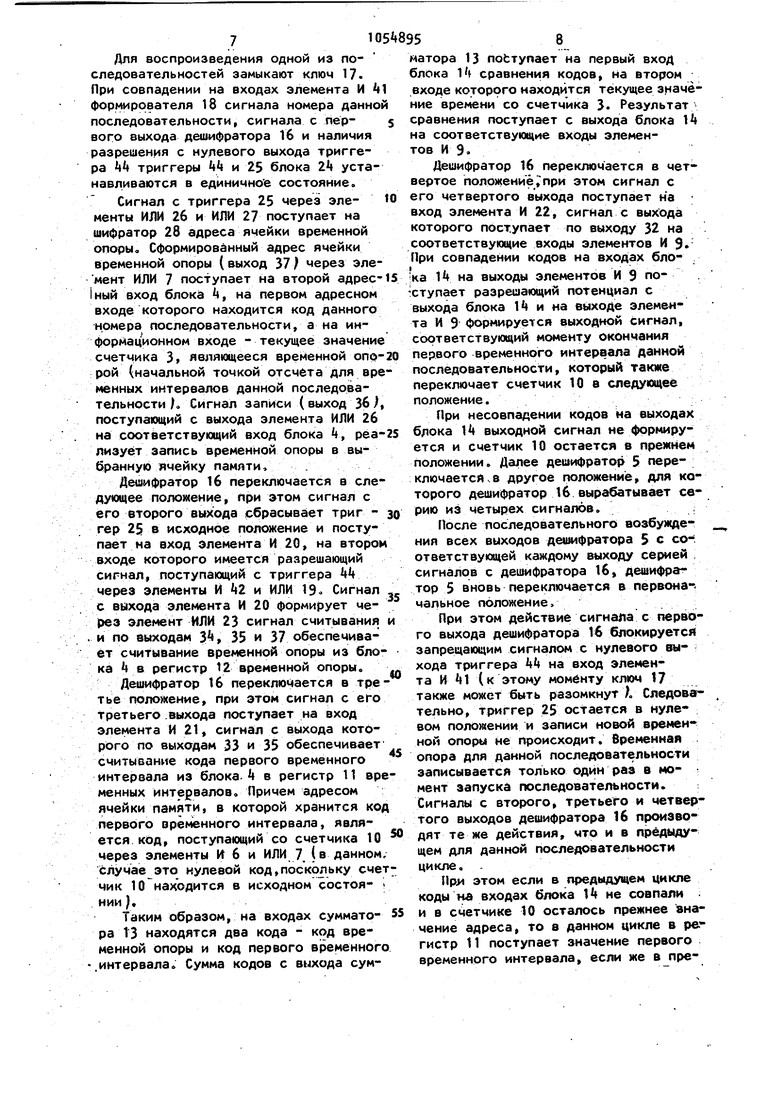

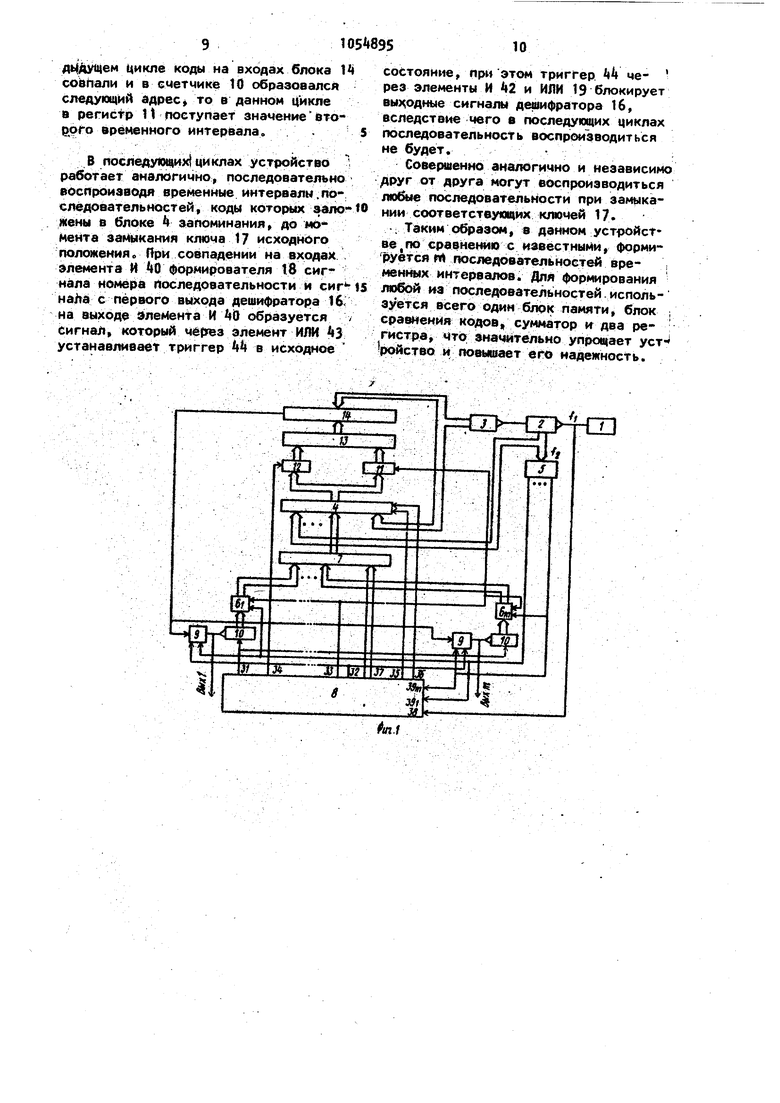

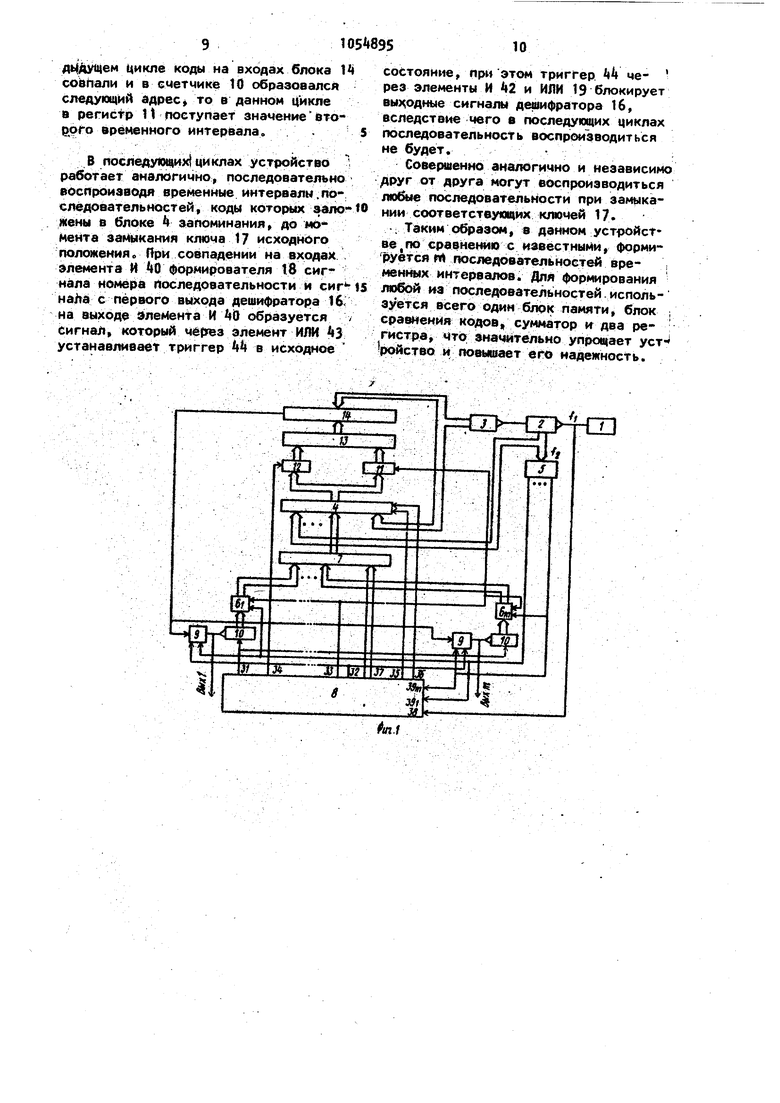

Изоб| етение относится к импульсно технике и может быть использовано в различных устройствах для формирования In независимых последовательносте временных интервалов в аналого-цифро вой вычислительной технике и в блоках программного управления различны ми технологическими процессами. Известно устройство, формирующее временные интервалы, содержащее гене jpaTop импульсов,пе| еёчетное устройство, мультиплвксор7 триггер, элементы И, регистр tlj Однако для получения m независимых последовательностей необходимо применить m указанных устройств, что приводит к увеличению количества , оборудования. Наиболее близким к предлагаемому по технической CJ HOCTH является устройство для формирования последовательностей временных интервалов, с держащее генератор импульсов, выход которого подключен квходу делителя частоты, выход которого соединен с входом счетчика импульсов, выходы счетчика импульсов подключены к первым входам блока памяти, дешифратор, выходы которого подключены к первым входам первых элементов И, -выходы ко торых соединены с первыми входами элемента ИЛИ, блок управления С23. Недостатком данного устройства является то, что оно не обеспечивает получение hi последовательностей вре менных интервалов, а для получения их требуетей Hfi данных устройств, что значительно усложняет устройство и уменьшает его надежность. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство для формирования последовательностей временных интервал лов, содержаи1ее генератор импульсов, выход которого подключен к входу делителя частоты, выход которого соединен с входом счетчиКа импульсов, выходы счетчика импульсов подключены к первым входам блока памяти, дешифра-; тор, выходы которого подключены к первым входам первых элементов И, выходы которых соединены с первыми входами элемента ИЛИ, блок управления, дополнительно введены вторые-элементы И, счетчики импульсов, два регистра, сумматор и блок сравнения кодов, первая группа входов которого соединена с выходами счетчика импульсов, вторая группа входов соединена с выходами сумматора, а выхЬд подключ ен к первым входам вторых элементов И, вторые входы которых подключены к выxoдa 4 дешифратора, третьи входы соединены с первым выходом блоке управления, а выход каждого второго элемента И соединен с входом соответствующего дополнительного счётчика импульсов, управляющий вход каждого из которых подключен к второму выходу блока управления, выходы каждого дополнительного счетчика импульсов подключены к вторым входам соответствующего первого элемента И, третьи входы которых подключены к третьему выходу блока управления и к входу первого регистра, разрядные входы которого соединены с выходами блока памяти и с разрядными входами второго регистра, выходы регистров подключены к первой группе входов сумматора соответственно, а вход второго регистра ; соединен с четвертым выходом блока уп i равления, пятый и шестой выходы которого подключены к первому и второму управляющим входам блока памяти, а седьмые выходы блока управления подключены к вторым входам элемента ИЛИ, первый вход блока управления соединен , с выходом генератора импульсов, а вто рые входы подключены к выходам дешифратора, причем выходы элемента ИЛИ подключены к вторым входам блока памя ти, третьи входы которого соединены с разрядными выходами делителя частоты и с входами дешифратора:, Блок управления содержит счетчик импульсов, выходы которого подключены к входам дешифратора, первый выход ко торого подключен к входам ключей, выход каждого из которых соединен через соответствующий формирователь импульсов с входами первого элемента ИЛИ, выход которого подключен к первым вхо дам первого, второго и третьего элементов И, вторые входы которых соединены с вторым, третьим и Четвертым выходами дешифратора соответственно, выходы первого и второго элементов И подключены к входам второго элемента ИЛИ, причем второй выход дешифратора подключен к первым входам блока триггеров, вторые входы которого соединены с соответствующими вторыми выходами формирователей импульсов, а выходы блока триггеров через третий элемент ИЛИ подключены к первому входу четвертого элемента ИЛИ, втЬрой вход которого соединен с выходом первого элемента И, а выход четвертого элемента ИЛИ соединен с входом шифратора шина сброса через ключ сброса соединена с вторым входом формирова телей импульсов и является вторым выходом блока управления, выход третьего элемента И является первым выходом блока управления, выход второго элемента И является третьим выходом блока управления, выход первого элемента И является четвертым выходом блока управления, выходы второго и третьего элементов ИЛИ являются соответственно пятым и шестым выходами блока управления, а выход шифратора является седьмым выходом блока управления, вход счетчика импульсов является первым входом блока управления, а третьи входы формирователей импульсов являются вторыми входами блока управления. На фиг. 1 приведена функциональная схема устройства для формирования последовательностей временных интервалЬв; на фиг. 2 - пример выполнения блока управления. Устройство (фиг. 1 содержит генератор 1 импульсов, выход которого соединен с входом делителя 2 частоты, подключенного к счетчику 3 им- . пульсов, соединенного с блоком k памяти, дешифратор S, соединенный с первыми входами соответствующих первых элементов И 6, подключенных к первым входам элемента ИЛИ 7 блок 8 управления, вторые элементы И 9, дополнительные счетчики 10 импульсов, два регистра 11 и 12, сумматор 13 и блок 1 сравнения кодов,:первая группа входов которого соединена с выходами счетчика 3 импульсов, вторая группа входов соединена с выходами сумматора 13, а выход подключен к первым входам вторых элементов И Э вторые-ВХОДЫ которых подключены квыходам дешифратора 5 третьи входы соединены с первым выходом блока 8 управления, а выход каждого второго элемента И 9 соединен с входом соответствующего дополнительного счетчика 10 импульсов, управляющий вход каждого из которых подключен к второму выходу блока 8 управления, выходы каждо-; го дополнительного счетчика.10 импульсов подключены к вторым входам соответствующего первого элемента И 6, третьи входы которых подключены к третьему выходу блока 8 управления и к входу первого регистра 11, разрядные входы которого соединены с выходами блока k памяти и разрядными входами второго регистра 12,выходы регистров 1-1 и 12 подключены к первой группе входов сумматора 13 соответственно, а вход второго регистра 12 соединен с четвертым выходом блока 8 управления, пятый и шестой выходы которого подключены к первому и второму управляющим входам блока памяти, а седьмые выходы блока 8 управления подключены к вторым входам элемента ИЛИ 7, первый вход блока 8 управления соединен с выходом генератора 1 импульсов, а вторые входы подключены к выходам дешифратора 5 причем выходы элемента.ИЛИ 7 подключены к вторым входам блока i памяти,, третьи входы которого соединены с разрядными выходами делителя 2 частоты и с входами дешифратора На фиг. 2 приведена функциональная схема-блока 8 управления, который содержит счетчик 15 импульсов, выходы которого подключены к входам дешифратора 16, первый выход которого подключен к входам ключей 17, выход . ка хдого из которых соединен через соответст укйций формирователь 18 импуль сов с входами первого элемента ИЛИ IS выход которого подключен к первым вхо дам первого, второго и третьего элементов И 20, 21 и 22, вторые входы которых соединены с вторым, третьим и четвертым выходами дешифратора 16 соответственно, выходы первого и второго элементов И 20 и 21 подключены к входам второго элемента ИЛИ 23, при чем второй выход дешифратора 16 подключен к первым входам блока 2 триггеров 25, вторые входа которого соединены с соответствующими вторыми вы ходами формирователей 18 импульсов, а выходы блока 24 триггеров 23 через третий элемент ИЛИ 26 подключены к первому входу четвертого элемента ИЛИ 27, второй вход которого соединен с выходом первого элемента И 20, а выход четвертого элемента ИЛИ 27 со единен с входом шифратора 28, шина 29 сброса через, ключ 30 сброса соединена с вторым входом формирователей 18 импульсов и является вторым выходом 31 блока 8 управления, выход tpeтьего элемента И 22 является первым выходом 32 блока 8 управления, выход второго элемента И 21 является третьим выходом 33 блока 8 управления, выход первого элемента .И 20 является четвертым выходом 3 блока 8 управления, выходы второго и третьего элементов ИЛИ 23 и 26 являются соответст венно пятим .и шестым выходами 35 и Зб блока 8 управления, а выкор шифратора 28 является седьмым выходом 37 блока 8 управления, вход счетчика 15 импульсов является первым входом 38 блока 8 управления, а третьи входы формирюватёлей 18 импульсов являются вторыми входами 39 блока 8 управле Qs ния. Формирователи 18 могут быть выполнены, например, на элементах И tO, 41 и 42, элементе ИЛИ 43, триггере 44. Устройство работает следующим образом. Все ячейки памяти блока 4 по числу воспроизводимых последовательностей разделены на зон, причем номер зоны определяется старшими разрядами адресного слова, а адреса ячеек памяти в каждой зоне определяются младшими разрядами адресного слова Массивы ячеек памяти каждой зоны равны по величине, причем соответствующие ячейки памяти в каждой зоне имеют одинаковые адреса. . Для каждой последовательности массив адресов ячеек распределен следующим образом Одна ячейка предназначена для записи в нее временной опоры, остальные ячейки содерЯсат значения временных интервалов данной последовательности Значение временной опоры .записывается в ячейку в момент начала воспроизведения данной последовательности, значения временных интервалов в ячейки Для каждой последовательности записываются зар.анее. При включении питания генератор 1, делитель 2, счетчик 3 начинают работать сразу с произвольного состояния. Регистры 11 и 12 также находятся в произвольном состоянии. При кратковременном зa ыкaнии ключа 30 сброса, расположенного в блоке 8 управления, счетчики 10 переходят в нулевое состояние, определяя для каждой последовательности ЭАРес ячейки памяти в блоке 4, в которой хранится значение первого временного интервала. Частота f от генератора 1 через вход 38блока 8 управления поступает на счетный вход счетчика 15, соединенного с дешифратором 16, на выходах которого циклически вырабатываются четыре сигнала, используемые для формирования сигналов управления устройством,- При воспроизведении каждой последовательности, причем-соотношение между частотой f и частотой f 2 поступающей на вход дешифра тора 5 номера гюследовательности, имеющего m выходов, рыбирается таким, чтобы в каждом полсякении дешифратора 5 на выходе дешифратора 16 формировалась последовательность из четырех сигналов. Для воспроизведения одной из последовательностей замыкают ключ 17. При совпадении на входах элемента И Ц формирователя 18 сигнала номера данно последовательности, сигнала с первого выхода дешифратора 16 и наличия разрешения с нулевого выхода триггера i триггеры kk и 25 блока 2 устанавливаются в единичное состояние. Сигнал с триггера 25 через элементы ИЛИ 26 и ИЛИ 27 поступает на шифратор 28 адреса ячейки временной опоры. Сформированный адрес ячейки временной опоры (выход 37) через элемент ИЛИ 7 поступает на второй адрес1ный вход блока t, на первом адресном входе которого находится код данного номера последовательности, а на информационном входе - текущее значение счетчика Зг являющееся временной onQрой (начальной точкой отсчета для вре менных интервалов данной последовательности /. Сигнал записи (выход 36), поступающий с выхода элемента ИЛИ 26 на соответствующий вход блока k, peaлизуёт запись временной опоры в выбранную ячейку памяти, . Дешифратор 16 переключается в следующее положение, при этом сигнал с его второго выхода сбрасывает триг гер 25 в исходное положение и поступает на вход элемента И 20, на втором входе которого имеется разрешающий сигнал, поступающий с триггера kk через элементы И и ИЛИ 19 Сигнал с выхода элемента И 20 формирует через элемент ИЛИ 23 сигнал считывания .и по выходам 3 35 и 37 обеспечивает считывание временной опоры из блока t в регистр 12 временной опоры. Дешифратор 16 переключается в тре тье положение, при этом сигнал с его третьего .выхода поступает на вход элемента И 21, сигнал с выхода которого по выходам 33 и 35 обеспечивает считывание кода первого временного интервала из блока, t в регистр 11 вре менных интервалов. Причем адресом : ячейки памяти, в которой хранится код первого временного интервала, является кйд, поступающий со счетчика 10 через элементы И 6 и ИЛИ 7. (в данном случае это кулевой код,поскольку счет чик 10 находится в исходном состоя- i Таким образом, на входах сумматора 13 находятся два кода - код временной опоры и код первого временного .интервала. Сумма кодов с выхода сумнатора 13 поЬтупает на первый вход блока Т сравнения кодов, на втором входе которого находится текущее значение времени со счетчика 3. Результат сравнения поступает с выхода блока 14 на соответствующие входы элементов ИЗ. Дешифратор 16 переключается в четвертое положение;при этом сигнал с его четвертого выхода поступает на вход элемента И 22, сигнал с выхода которого поступает по выходу 32 на соответствующие входы элементов И 9 При совпадении кодов на входах бло;ка 1 на выходы элементов ИЗ поступает разрешающий потенциал с выхода блока 1 и на выходе элемента И 9 формируется выходной сигнал, соответствующий моменту окончания первого временного интервала данной последовательности, который также переключает счетчик 10 в следующее положение. При несовпадении кодов на выходах блока И выходной сигнал не формируется и счетчик 10 остается в прежнем положении. Далее дешифратор 5 переключается .в другое положение, для которого дешифратор 16 вырабатывает серию из четырех сигналов. , После последовательного возбуждения всех выходов д вифратора 5 с со-. ответствующей каждому выходу серией сигналов с дешифратора 16, дешифратор 5 вновь переключается в первоначальное положение. При этом действие сигнала с первого выхода дешифратора 16 блокируется запрещающим сигналом с нулевого выхода триггера kk на вход элемента И ijl (к этому моменту ключ 17 также может быть разомкнут 7. Следовательно, триггер 25 остается в нулевом положении и записи новой времен ной опоры не происходит. Временная опора для данной последовательности записывается только один раз в мо- : мент запуска последовательности. Сигналы с второго, третьего и четвертого выходов дешифратора 16 производят те же действия, что и в предыдущем для данной последовательности цикле. Пря этом если в предыдущем цикле коды на входах блока k не совпали и в счетчике 10 осталось прежнее значение адреса, то в данном цикле в регистр 11 поступает значение первого временного интервала, если же в предЦДуШем цикле коды на входах блока 1 совпали и в ечетчике 10 образовался следующий адрес то в данном цикле в регистр 1Г поступает знамениевторого временного интервала.

В послеАУ «их| циклах устройство работает аналогично, последовательно восшроизводя временные интервалы.последовательностей, коды которых заложены в блоке запоминания, до момемта замыкания ключа 17 исходного положения, ffpH совпадении на входах элемента И 40 формирователя 18 сигнала Номера последовательности и с первого выхода дешифратора 16 на выходе элемента И D образуется сигнал, который элемент ИЛИ 3 устанавливает триггер в исходное

состояние, при этом триггер че- рез элементы И и ИЛИ 19 блокирует вы)одные сигналы дешифратора 16, вследствие чего в последующих циклах последовательность воспроизводиться не будет.

Совершенно аналогично и независимо tpyr от друга могут воспроизводиться пОбые последовательности при замыкании соответствующих кгиочей 17.

; Таким образом, в данном устройстве , по сравнению с известными, формируется nt последовательностей вре- i менНых интервалов. Для формирования любой из последовательностей.используется всего один блок памяти, блок сравнения кодов, сумматор и два регистра, что днамйтельно упрощает уст(юйство и повышает его надежность.

aSf

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-11-15—Публикация

1981-10-27—Подача