ства, вход регистра операций является третьим информационным входом устройства, выход регистра операций соединен с информационным входом формирователя кода операций, с управляющими входами формирователя синхронизирующих сигналов, шифратора кода режима и с вторым входом распределителя тактовых импульсов, третий вход которого соединен с вторым выходом шифратора кода режима, выход распределителя тактовых импульсов подключен к тактовым входам шифратора кода режима и формирователя синхронизирующих сигналов, причем формирователь синхронизирующих сигналов содержит триггеры, элементы ИЛИ и группы элементов И, первые входы которых подключены к тактовому входу формирователя синхронизирующих сигналов, вторые входы соединены с управляющим входом формирователя синхронизирующих сигналов, первый вход каждого элемента ИЛИ соединен с управляющим входом формирователя синхронизирующих сигналов, входы, начиная с второго, соединены с выходами элементов И соответствующей группы, выходы каждого пред1-1дущего и последующего элементов ИЛИ, кроме первого, соединены соответственно с первым и вторым входами соответствующего триггера, выход1л триггеров и первого элемента ИЛИ соединены с выходом формиротза.келя синхронизирующих сигналов, о т л и чающееся тем, что, с целью повЕлшения производительности, в него введены блок буферной памяти подготовительных команд, стек ссылок, регистр ссылок и коммутатор указателей стека дешифрированных адресов, первый вход и выход которого подключены соответственно к информационному выходу блока указателей стека дешифрированных адресов и к адресному входу стека дешифрированных адресов- информационный выход блока укйзагалей стека дешифрированных адресов с:;едйнен с первым входом реГис.лра ссылок, выход комментатора указателей стека де1иифрированных адресов поцключен к адресному входу стека ссылок,, первые вход и выход которого соединены соотватстиенно с первым: выходом и вторым входом регистра ссылок,, второй выход которого подключен к второму входу комм5,татора указателей стека дешифрированн11 ; адресов, управляющий вход которого сОединен с выходом формирователя синхронизирующих сигналов, с управляющим входом регистра ссылок и с вторым входом стека ссылок, второй выход которого, третий выход регистра ссылок и управляющий выход блока буферной памяти подготовительных команд соединены с группой входов шифратора кода режима, первый и второй входы блока буферной памяти подготовительных команд соединены соответственно с выходом формирователя кода операций и с выходом коммутатора адресов, третий выход подключен к пятому входу блока адресации и к второму адресному выходу устройства, а управляющий вход является пятым управляющим входом устройства .

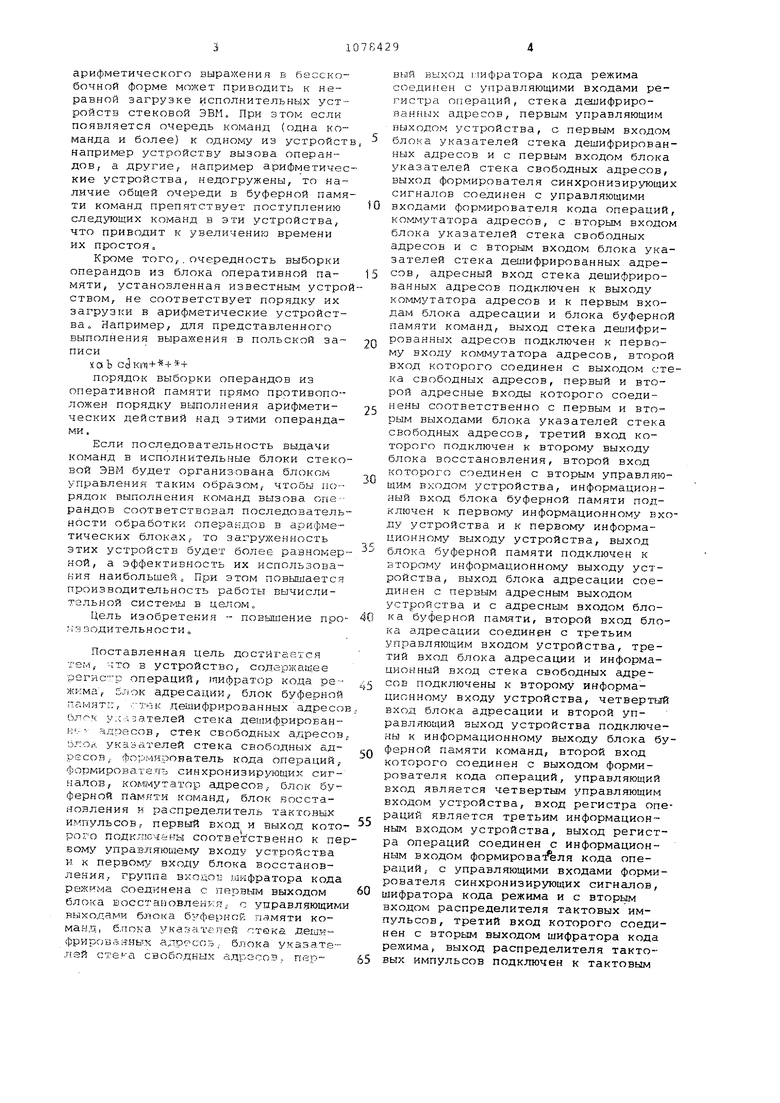

2,Устройство nort. 1, отличающееся тем, что формирователь кода операций содержит шифратор и коммутатор, первый вход которого является информационным входом формирователя, второй вход коммутатора

и вход шифратора соединены с управляющим входом формирователя, выход шифратора подключен к третьему входу коммутатора, выход которого является выходом формирователя.

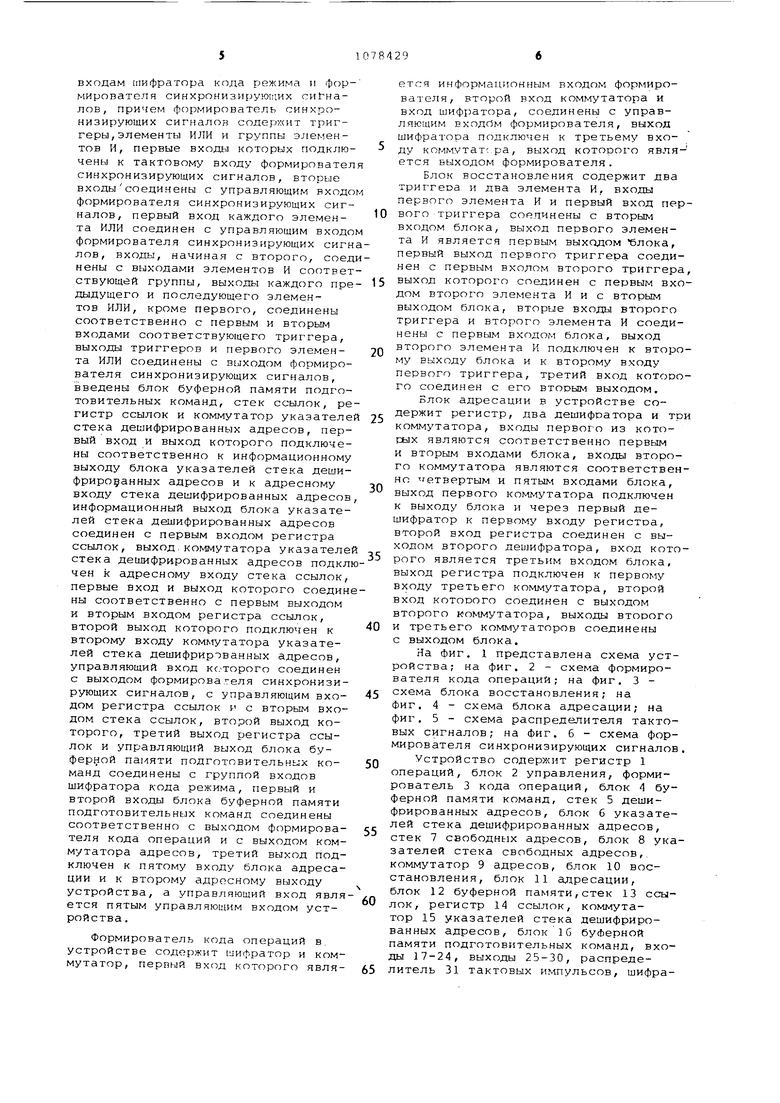

3,Устройство по п. 1, отличающееся тем, что блок восстановления содержит два триггера и два элемента И, входы первого элемента И и первый вход первого триггера соединены с вторым входом блока, выход первого элемента И является первым выходом блока, первый выход первого триггера соединен с первым входом второго триггера, выход которого соединен с первым входом второго элемента И и с вторым выходом блока, вторые входы второго триггера и второго элемента И соединены

с первым входом блока, выход второго элемента И подключен к второму выходу блока и второму входу первого триггера, третий вход которого соединен с его-вторым выходом.

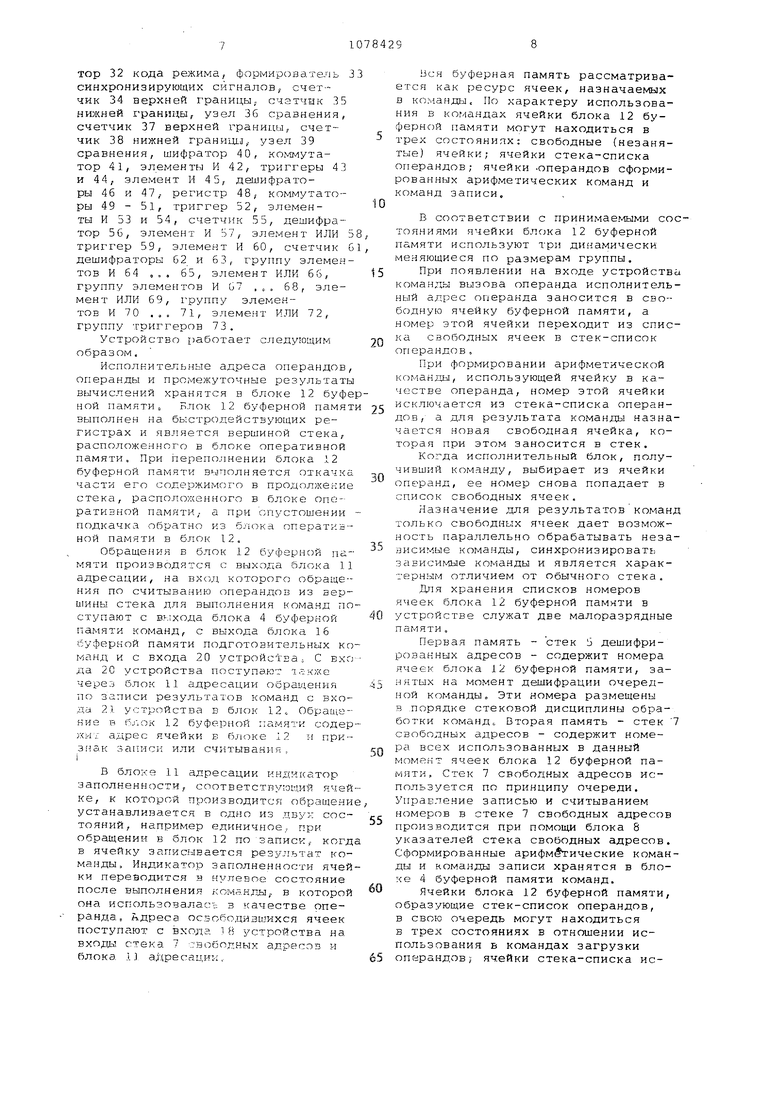

4,Устройство по п. 1, отличающееся тем, что блок адресации содержит регистр, два дешифратора и три коммутатора, входы первого из которых являются соответственно первым и вторым входами блока, входы второго коммутатора являются соответственно четвертым и пятым входами блока, выход первого коммутатора подключен к выходу блока и через первый дешифратор к первому входу регистра,второй вход регистра соединен с выходом второго дешифратора, вход которого двляется третьим входом блока, выход регистра подключен к первому входу третьего коммутатора, второй вход которого соединен с выходом второго коммутатора, выходы второго и третьего коммутаторов соединены с выходом блока.

Изобретение относится к вычислительной технике и может быть использовано в электронных вычислительных машинах (ЭВМ) с внутренним языком высокого уровня.

Известно устройство, которое управляет связью между блоками оперативной памяти и арифметическим блоком, осуществляемой через два быстродействующих регистра блока буферНой памяти, являющихся верхними ячейками стека, содержащее регистр операций, блок управления, блок адресации и блок буферной памяти, информационный вход и выход которого соединены соответственно с информационным входом и первым информационным выходом устройства, адресный вход - с выходом блока адресации, вход и выход регистра операций соединены соответственно с первым входом устройства и с первым управляющим входом блока управления, второй управляющий вход которого соединен с первым управляющим входом устройства

Устройство входит в состав высокопроизводительной вычислительной машины со стековой системой команд, обеспечивающей уменьшение длины программ и упрощение программирования по сравнению с адресной системой команд l .

Эффективность ЭВМ с поточной обработкой команд в большей мере зависит от распределения быстродействующих регистров, используемых для быстрого доступа к промежуточным результатам, так как планирование параллельного выполнения независимых команд происходит за счет резервирования различных быстродействующих регистров для операндов, вызываемых из блока оперативной памяти, а также под результаты параллельно выполняемых команд.

В известном устройстве только два быстродействующих регистра блока буферной памяти, являющихся верхними ячейками стека, связаны с арифметическим блоком. Поэтому известное устройство не в состоянии обеспечить параллельную обработку нескольких команд и, следовательно, не позволяет организовать параллельное выполнение команд по принципу поточной линии.

Наиболее близким к изобретению по технической сущности является устройство, содержащее регистр операций, блок адресации, блок буферной памяти, стек дешифрованных адресов, блок указателей стека дешифрованных адресов, стек свободных адресов, блок указателей стека свободных адресов, формирователь кода операции, коммутатор адресов, буферную

память команд, блок восстановления и блок управления,

В устройстве производится динамическое отображение стекового формата команды во внутренний адресный формат команды непосредственно пере выполнением команды, при этом вся работа по поддержанию стековой дисциплины использования ячеек буферной памяти производится не над самими ячейками, а над их адресами. Вся буферная память рассматривается как ресурс ячеек, назначаемый в стековую память под результаты очередных команд и возвращаемых обратно после использования в качестве операндов в последующих командах. Использование под результат операции только свободной ячейки буферной памяти, позволяет синхронизировать логически связанные команды, когда результат одной используется в последующей как операнд.

Применение этого устройства в стековой ЭВМ дает возможность организовать обработку информации по принципу поточной линии |2 .

Недостатками описанного устройства, не позволяющими полностью совместить в стековой ЭВМ выборку операндов с обработкой операндов в ариметико-логических исполнительных блоках, являются последовательный характер загрузки команд в исполнительные блоки в результате применения общего буфера для всех команд и несоответствие очередности выполнения сформированных устройством команд вызова операндов из оперативной памяти последовательности обработки операндов.

Последовательность команд стековой ЭВМ представляет собой строку бесскобочной польской записи, заданную в машинной форме. Одной из особенностей выражения, представленного в польской записи, является возможность образования групп из более чем двух операндов и знаков операций. Например, выражение

X а+ (к+гч)

в польской записи имеет вид хаЪ fcdKm+ -t- + .

В машинную форму эти группы транформируются в виде последовательностей соответственно команд вызова операндов из блока оперативной памяти и безадресных арифметических команд, поступающих на вход блока управления. В результате соответствия последовательностей команд на входе и выходе известного устройства команды одного вида, соответствующие группам в польской записи, поступаютк исполнительным устройствам ЭВМ. Таким образом, группирование операндов при задании арифметического выражения в бесскобочной форме может приводить к неравной загрузке исполнительных устройств стековой ЭВМ, При зтом если появляется очередь команд (одна команда и более) к одному из устройст например устройству вызова операндов, а другие, например арифметиче кие устройства, недогружены, то наличие общей очереди в буферной памя ти команд препятствует поступлению следующих команд в эти устройства, что приводит к увеличению времени их простоя. Кроме того,.очередность выборки операндов из блока оперативной памяти, установленная известным устро ством, не соответствует порядку их загрузки в арифметические устройства Например, для представленного выполнения выражения в польской записиха Ъ порядок выборки операндов из оперативной памяти прямо противоположен порядку выполнения арифметических действий над этими операндами . Если последовательность выдачи команд в исполнительные блоки стеко вой ЭВМ будет организована блоком управления таким образом, чтобы порядок выполнения команд вызова one рандов соответствовал последователь ности обработки операндов в арифметических блоках, то загруженность этих устройств будет более равномер ной, а эффективность их использования наибольшей, При этом повышаетс производительность работы вычислительной систе л в целом. Цель изобретения - повыизение про ;;3 зодительности „ Поставленная цель достигается тем, -iTo в устройство, содержащее регис р операций, шифратор кода ре жима, блок адресации, блок буферно памяти, дешифрированных адрес у..;лзателей стека дешифрирован )-;. адресов, стек свободных адресо 13лол указателей стека свободных ад ресов,- фог;.мирователь кода операций формирователъ синхронизирующих сиг налов, коммутатор адресов,, блок бу ферной памяти команд, блок восстановления и распределитель тактовых импульсов я первый вход и выход кот рого подключены соответственно к п вому управляющему входу устройства и к первом входу блока восстановления, группа Bxoaoi- шифратора код режг ма соединена с первым выходом блока восстановленкя, с управляющи выходами блока буферной памяти команд, блока указатепей стека дешиф р и ро в S ; н ьч X а л р р с с; ъ .- б л ока указате лей сте;.-а свободных адресов,, первый выход 1ми фра тора кода режима соединен с управляющими входами регистра операций, стека дешифрированных адресов, первым управляющим выходом устройства, с первым входом блока указателей стека дешифрированных адресов и с первым входом блока указателей стека свободных адресов, выход формирователя синхронизирующих сигналов соединен с управляющими входами формирователя кода операций, коммутатора адресов, с вторым входом блока указателей стека свободных адресов и с вторым входом блока указателей стека дешифрированных адресов, адресный вход стека дешифрированных адресов подключен к выходу коммутатора адресов и к первым входам блока адресации и блока буферной памяти команд, выход стека дешифрированных адресов подключен к первому входу коммутатора адресов, второй вход которого соединен с выходом стека свободных адресов, первый и второй адресные входы которого соединены соответственно с первым и вторым выходами блока указателей стека свободных адресов, третий вход которого подключен к второму выходу блока восстановления, второй вход которого соединен с вторым управляющим входом устройства, информационный вход блока буферной памяти подключен к первому информационному входу устройства и к первому информационному выходу устройства, выход блока буферной памяти подключен к второму информационному выходу устройства, выход блока адресации соединен с первЕлм адресным выходом устройства и с адресным входом блока буферной памяти, второй вход блока адресации соединен с третьим управляющим входом устройства, третий вход блока адресации и информационный вход стека свободных адресов подключены к второму информационному входу устройства, четвертый вход блока адресации и второй управляющий выход устройства подключены к информационному выходу блока буферной памяти команд, второй вход которого соединен с выходом формирователя кода операций, управляющий вход является четвертьлм управляющим входом устройства, вход регистра операций является третьим информационным входом устройства, выход регистра операций соединен с информационным входом формирователя кода операций, с управляющими входами формирователя синхронизирующих сигналов, шифратора кода режима и с вторым входом распределителя тактовых импульсов, третий вход которого соединен с вторьм выходом шифратора кода режима, выход распределителя тактовых импульсов подключен к тактовым входам шифратора кода режима и формирователя синхронизирующих си1 налов, причем формирователь синхронизирующих сигналов содержит триггеры, элементы ИЛИ и группы элементов И, первые входы которых подключены к тактовому входу формировател синхронизирующих сигналов, вторые входысоединены с управляющим входо формирователя синхронизирующих сигналов, первый вход каждого элемента ИЛИ соединен с управляющим входо формирователя синхронизирующих сигн лов, входы, начиная с второго, соед нены с выходами элементов И соответ ствующей группы, выходы каждого пре дыдущего и последующего элементов ИЛИ, кроме первого, соединены соответственно с первым и вторым входами соответствующего триггера, выходы триггеров и первого элемента ИЛИ соединены с выходом формирователя синхронизирующих сигналов, введены блок буферной памяти подготовительных команд, стек ссылок, ре гистр ссылок и коммутатор указателе стека дешифрированных адресов, первый вход и выход которого подключены соответственно к информационному выходу блока указателей стека дешифрирО9анных адресов и к адресному входу стека дешифрированных адресов информационный выход блока указателей стека дешифрированных адресов соединен с первым входом регистра ссылок, выход.коммутатора указателе стека дешифрированных адресов подкл чен k адресному входу стека ссылок, первые вход и выход которого соедин ны соответственно с первым выходом и вторым входом регистра ссылок, второй выход которого подклю ген к второму входу комьгутатора указателей стека дешифрированных адресов, управляющий вход которого соединен с выходом формирователя синхронизирующих сигналов, с управляющим входом регистра ссылок i с вторым входом стека ссылок, второй выход которого, третий выход регистра ссылок и управляющий выход блока буферуой памяти подготовительных команд соединены с группой входов шифратора кода режима, первый и второй входы блока буферной памяти подготовительных команд соединены соответственно с выходом формирователя кода операций и с выходом коммутатора адресов, третий выход подключен к пятому входу блока адресации и к второму адресному выходу устройства, а управляющий вход явля ется пятым управляющим входом устройства . Формирователь кода операций в, устройстве содержит шифратор и коммутатор, первый вхсзд которого является информационным входо.м формирователя, второй вход коммутатора и вход шифратора, соединены с управляющим входг1м формирователя, выход шифратора подключен к третьему входу коммутат; ра, выход которого явля- ется выходом формирователя. Блок восстановления содержит два триггера и два элемента И, входы первого элемента И и первый вход первого триггера соединены с вторым входом блока, выход первого элемента И является первым выходом блока, первый выход первого триггера соединен с первым входом второго триггера, выход которого соединен с первым входом второго элемента И и с вторым выходом блока, вторие входы второго триггера и второго элемента И соединены с первым входом блока, выход второго элемента И подключен к второму выходу блока и к второму входу первого триггера, третий вход КОТОРОГО соединен с его вторым выходом. Блок адресации в устройстве содержит регистр, два дешифратора и три коммутатора, входы первого из которых являются соответственно первым и вторым входами блока, входы второго коммутатора являются соответственно етвертым и пятым входами блока, выход первого коммутатора подключен к выходу блока и через первый дешифратор к первому входу регистра, второй вход регистра соединен с выходом второго деи ифратора, вход которого является третьим входом блока, выход регистра подключен к первому входу третьего коммутатора, второй вход КОТОРОГО соединен с выходом второго коммутатора, выходы ВТОРОГО и третьего ко 1мутаторов соединены с выходом блока. На фиг. 1 представлена схема устройства; на фиг. 2 - схема формирователя кода операций; на фиг. 3 схема блока восстановления; на фиг. 4 - схема блока адресации; на фиг. 5 - схема распределителя тактовых сигналов; на фиг. 6 - схема формирователя синхронизирующих сигналов. Устройство содержит регистр 1 операций, блок 2 управления, формирователь 3 кода операций, блок 4 буферной памяти команд, стек 5 дешифрированных адресов, блок 6 указателей стека дешифрированных адресов, стек 7 свободных адресов, блок 8 указателей стека свободных адресов,, коммутатор 9 адресов, блок 10 восстановления, блок 11 адресации, блок 12 буферной памяти,стек 13 ссылок, регистр 14 ссылок, коммутатор 15 указателей стека дешифрированных адресов, блок 1G буферной памяти подготовительных команд, входы 17-24, выходы 25-30, распределитель 31 тактовых импульсов, шифратор 32 кода режима, формирователь 3 синхронизирующих сигналов, счетчик 34 верхней границы; счатчнк 35 ншкней границы, узел 36 сравнения, счетчик 37 верхней границы, счетчик 38 нижней границы,, узел 39 сравнения, шифратор 40, коммута12, триггеры 43 тор 41, элементы И и 44, элемент И 45, дешифраторы 46 и регистр коммутато-52, элеменры 49 триггер55, дешифраи 54, счетчик ты И 53 элемент И S , элемент ИЛИ 5 тор 5G, триггер 59, элемент И 60, счетчик G дешифраторы 62 и 63, группу элементов И 64 ,,. 65, элемент ИЛИ 6G, группу элементов И G7 ,,. 68, элемент ИЛИ 69, группу элементов И 70 ... 71, элемент ИЛИ 72, группу триггеров 73. Устройство работает следующим образом. Исполнительные адреса операндов операнды и промежуточные результаты вычислений хранятся в блоке 12 буфе ной памяти. Блок 12 буферной памят выполнен на быстродействующих регистрах и является вершиной стека, расположенного в блоке оперативной памяти. При переполнении блока .12 буферной памяти выполняется откачка части его содержимого в продолжение стека, расположенного в блоке оперативной памяти,, а при опустошении подкачка обратно из блока оперативной памяти в блок 12. Обращения в блок 12 буферной па мяти производятся с выхода блока 1 адресации, на вход которого обращения по считыванию операндчов из вершины стека для выполнения команд по ступают с выхода блока 4 буферной памяти команд, с выхода блока 16 буферной памяти подготовительных ко манд и с входа 20 устройства о С вхо да 20 устройства поступают т.гкже через блок 11 адресации обраидения по записи результатов команд с вхо да 21 устройства в блок 12, Обраще ние в 6jiOK 12 буферной содер адрес ячейки в блоке 12 и при 3tiap; записи или считывания, В блоке 11 адресации индикатор заполненности, соответстпу;ок,ий яче ке, к которой производится обращен устанавливается в одно из двух сос тояний, например единичное, при обращении в блок 12 по записи, когд в ячейку записЕДвается результат ко манды. Индикатор заполненности яче ки переводится в нулевое состояние после выполнения команды,- в которо она использовалась в качестве рперан7да. Адреса осзобсдизшихся ячеек поступают с входа i8 устройства на входы стека 7 .свободных адресов и блока л адресаци:-:, Вся буферная память рассматривается как ресурс ячеек, назначаемых Б команды. По характеру использования в командах ячейки блока 12 буферной памяти могут находиться в трех состояниях: свободные (незанятые) ячейки; ячейки стека-списка операндов; ячейки -операндов сформированных арифметических команд и команд записи, В соответствии с принимаемыми состояниями ячейки блока 12 буферной памяти используют три диг амически меняющиеся по размерам группы. При появлении на входе устройства команды вызова операнда исполнительный адрес операнда заносится в свободную ячейку буферной памяти, а номер этой ячейки переходит из списка свободных ячеек в стек-список операндов, При формировании арифметической команды, использующей ячейку в качестве операнда, номер этой ячейки исключается из стека-списка операндов, а для результата команды назначается новая свободная ячейка, которая при этом заносится в стек, Когда исполнительный блок, получивший команду, выбирает из ячейки операнд, ее номер снова попадает в список свободных ячеек. Назначение для результатов команд только свободных ячеек дает возможность параллельно обрабатывать незанисимые команды, синхронизировать Зс1висимые команды и является характерным отличием от обычного стека. Для хранения списков номеров ячеек блока 12 буферной памяти в устройстве служат две малоразрядные памяти. Первая память - стек 5 дешифрированных адресов - содержит номера ячеек блока 12 буферной памяти, занятых на момент дешифрации очередной команды. Эти номера размещены в порядке стековой дисциплины обработки команд. Вторая память - стек 7 свободных адресов - содержит номера всех использованных в данный момент ячеек блока 12 буферной памяти. Стек 7 свободных адресов используется по принципу очереди, Управление записью и считыванием номеров в стеке 7 свободных адресов производится при помощи блока 8 указателей стека свободных адресов. Сформированные арифм ические команды и команды записи хранятся в блохе 4 буферной памяти команд. Ячейки блока 12 буферной памяти, образующие стек-список операндов, в свою очередь могут находиться в трех состояниях в отношении использования Б командах загрузки операндов; ячейки стека-списка исполнительных адресов; ячейки сформированных команд вызова операндов; ячейки операндов (ячейки с результатами команд загрузки).

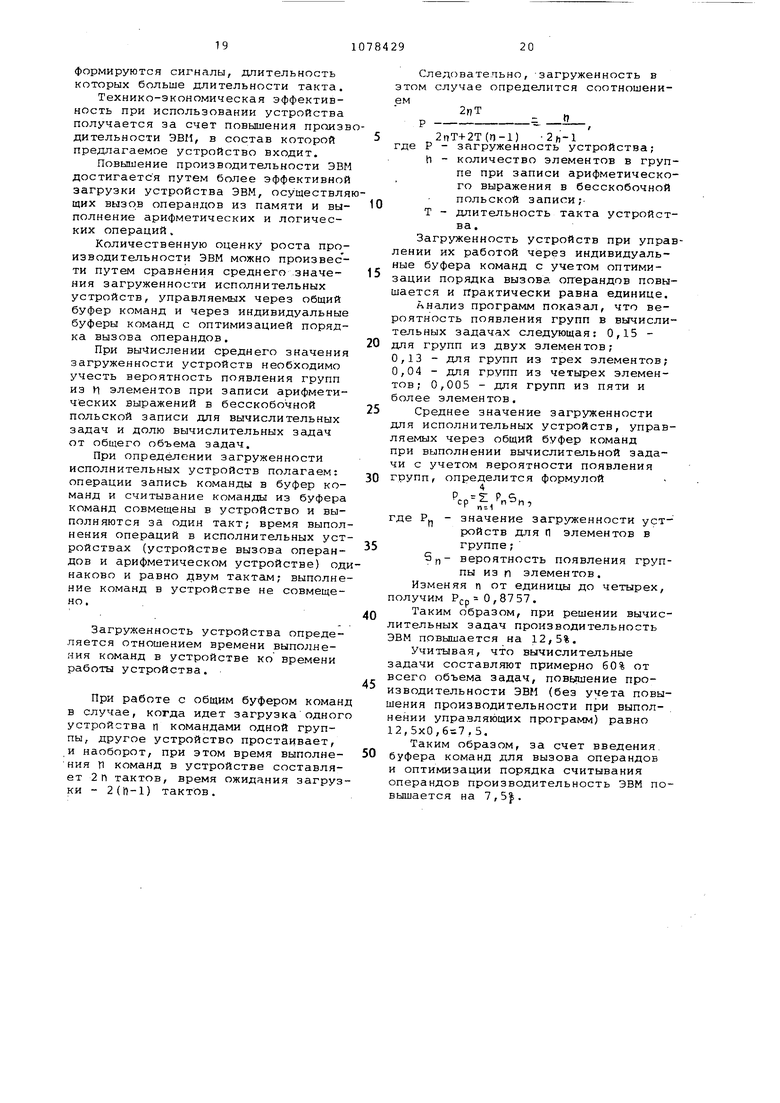

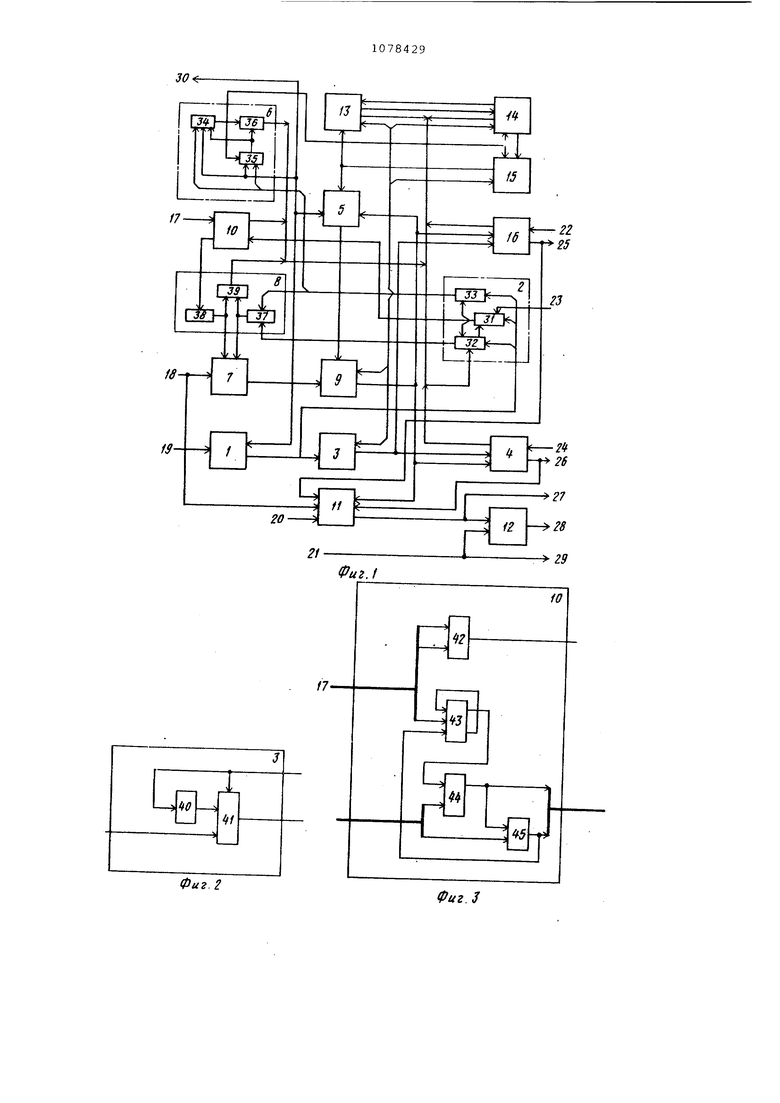

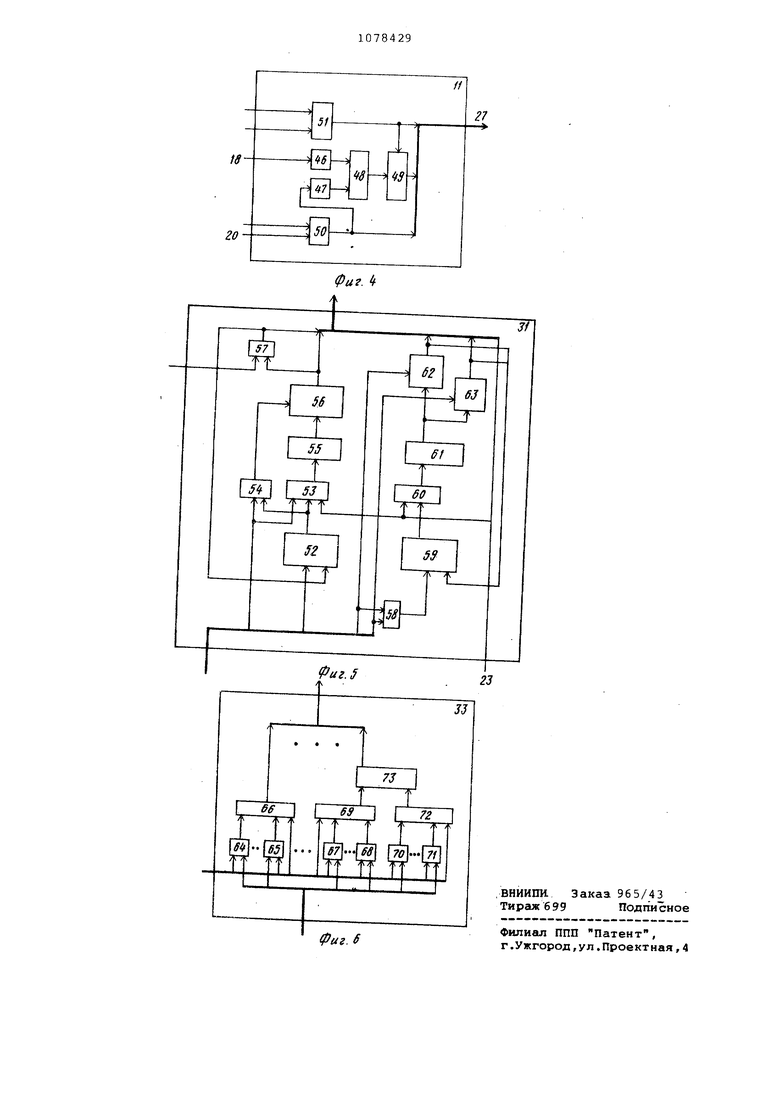

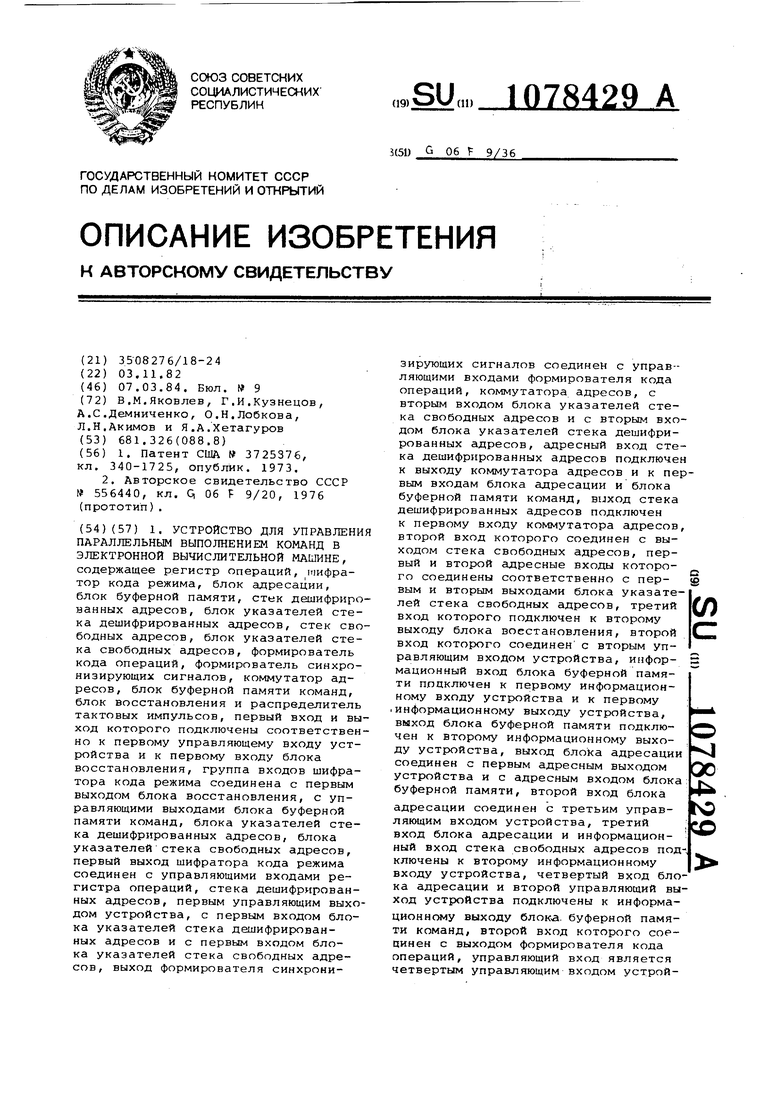

Номер ячейки блока 12 буферной памяти, назначенной под и.сполнительный адрес операнда, поступающий в стек-список операндов, заносится одновременно и в стек-список исполнительных адресов. При формировании арифметической команды, использующей ячейку стека-списка исполнительных адресов в качестве операнда, номер этой ячейки исключается из стек списка исполнительных адресов и назначается в команду вызова операнда поступающую в блок 1и буферной памяти подготовительных команд.

Если блок 1G освобождается прежде, чем будет сформирована очередна арифметическая команда, в него заносится, .дежурная команда вызова операнда с ячейкой, назначенной из вершины стека-списка исполнительных адресов. Таким образом, если в блоке 12 буферной памяти хранится по крайней мере один адрес операнда, то память блока 16 никогда не будет свободной. Поэтому перестановка адресов вызова операндов не приводи к простоям блока оперативной памяти

Результат команды вызова операнд заносится в ту хе ячейку блока 12 буферной памяти, в которой хранился исполнительный адрес операнда, при этом индикатор занятости этой ячейки устанавливается в единичное значение.

Для организации в устройстве стековой дисциплины использования исполнительных адресов операндов в командах вызова операндов служит стек 13 ссылок. В стеке 13 ссылок хранится список ячеек стека 5 дешифрированных адресов, занятых номерами адресов в блоке 12 буферной памяти. Между ячейками стека 13 ссылок и стека 5 дешифрированных адресов устанавливается следующее соответствие.

Ячейка стека 13 ссылок с тем же номером, что и ячейка стека 5 дешифрированных адресов, занятая номером адреса операнда блока 12 буферной памяти, содержит признак принадлежности ячейки стеку-списку исполнительных адресов, ссылку-номер следующего элемента списка, признак первого элемента списка. Биты признака принадлежности и признака первого элемента принимают единичное значение соответственно, когда номер адреса операнда в блоке 12 буферной памяти, записанный в ячейку стека 5 дешифрированных адресов, принадлежит стеку-списку исполнительных адресов и когда номер адреса операнда является первым элементом списка.

Адрес ячейки стека 5 дешифрированных адресов, в которой записан номер последнего на момент формирования команды элемента стека-списка исполнительных адресов, хранится в регистре 14 ссылок.

Управление записью и считыванием информации в стеке 5 дешифрированных адресов и в стеке 13 ссылок осуществляется по общему адресному входу через коммутатор 15 с региЬтра 14 ссылок или из блока 6 указателей стека дешифрированных адресов.

Для очередной команды, поступающе в стековом формате с входа 19 устройства на регистр 1 операций, по коду операции определяется принадлежность к одному из двух следующих классов команд: командам вызова операндов из памяти и командам арифметическим, логическим и записи в оперативную память .

Для команды вызова операнда назначается одна ячейка блока 12 буферной памяти для размещения сначала адреса операнда, а затем операнда после его выборки из оперативной памяти.

Номер назначенной в команду вызова операнда ячейки блока 12 буферной памяти поступает с выхода стека 7 свободных адресов через коммутатор 9 адресов, управляемый формирователем 33, на вход стека 5 дешифрированных адресов и через блок 11 адресации на адресный вход блока 12 буферной памяти, на информационный вхо которого подается исполнительный адрес операнда с входа 21 устройства. Ядрес, по которому производится запись в стек 5 дешифрированных адресов, поступает из блока 6 указателей стека дешифрированных адресов через коммутатор 15, управляемый формирователем 33. Одновременно с записью информации в ячейку стека 5 дешифрированных адресов в соответствующую ячейку стека 13 ссылок записываются адрес и бит признака первог элемента списка исполнительных адресов из регистра 14 ссылок, а также бит признака принадлежности списку из формирователя 33. ндрвс, по которому сделана запись в стек 5 и в стек 13 из блока 6, и бит признака первого элемента, соответствующий следующему еще не поступившему на вход устройства адресу операнда, из формирователя 33 записываются в регистр 14 ссылок.

Пустая буферная память блока 1б формирует сигнал на вход шифратора 32, В результате, если в устройстве в данный момент еще не формируется команда, устанавливается режим подготовки команды вызова операнда, цля которой ячейка блока 12 буферной памяти назначается из вершины стека-списка исполнительных адресов. Перед началом режима опрашивается бит признака первого элемента списка, записанный на регистре 14 ссылок. Единичное значение бита признака свидетельствует о наличии элементов в списке и является сигналом к началу режима. Адрес последнего элемента списка в стеке 5 дешифрированных адресов, записанный на регистре 14 ссылок, поступает с выхода регистра 14 через коммутатор 15 на адре.сный вход стека 5 дешифрированных адресов и стека 13 ссылок., /лдрес с выхода стека J дешифрированных адресов поступает на вход блока- 16 буферной памяти подготовительных команд через коммутатор 9 адресов, управляемый формирователем 33. Код операции вызова операнда поступает на вход блока 16 из фо мирователя 3 кода операций, управля мого формирователем 33. Адрес и бит признака первого элемента списка с первого выхода стека 13 ссылок запи сываются в регистр 14 ссылок, В результате из стека-списка исполнител ных адресов исключается последний элемент и заносится в очередь коман вызова операндов. Для арифметической, логической команд или команды записи, поступив шей на peiHCTp 1 операций, назначаю ся ячейки блока 12 буферной памяти, в которых находятся операнды, а для арифметической и логической команды кроме того, и ячейка, в которую будет помещен результат. Код операции передается с выхода регистра 1 чере формирователь 3 кода операций на вход блока 4 буферной памяти команд Номера назначенных в команду ячеек операндов блока 12 буферной памяти поступают на вход блока 4 буферной памяти команд из стека 5 дешифрированны): адресов через ком.мутатор 9 адресов, управляемый формирователем 33. Адрес, по которому в этот м мент осуществляется считывание из стека 5, поступает из блока G указа телей стека дешифрированных адресов через KOMj/iyTaTop 15, Адрес ячейки блока 12 буферной памяти, назначенной под результат арифметической ко манды, поступает на вход блока 4 бу ферной памяти кс:1манд через коммутатор 9 адресов из стека 7 свободных адресов. Использование под результат толь ко свободной ячейки блока 12 оказывается существенным при синхронизации логически связанных команд, ког да результат одной используется в последующей как операнд. Однов :)еменно с формированием ар-ифметической команды или команды замены осуществляется формирование команд вызова операндов для этой команды. Формирование команд вызова операндов осуществляется следующим образом. При считывании из стека 5 адресов, назначенных в команду ячеек, одновременно считывается также содержимое соответствующих ячеек стека 13 ссылок. Бит признака принадлежности номера ячейки блока 12 буферной памяти стеку-списку исполнительных адресов поступает с выхода стека 13 на вход шифратора 32. При единичном значении бита признака, когда номер ячейки принадлежит списку, формирователь 33 вырабатывает сигнал, по которому адрес и бит признака первого элемента с выхода стека 13 поступают на регистр 14 ссылок, а адрес с выхода стека 5 через коммутатор 9 адресов в блок 16. Арифметические команды и команды записи, представленные во внутреннем адресном формате, с выхода блока 4 буферной памяти команд поступают на выход 26 устройства для их выполнения в специализированных по своих функциям блоках при условии разрешения выдачи, поступающего на управляющий вход блока 4 буферной памяти команд с входа 24 устройства. Команды вызова операндов поступают на выход 25 устройства для их выполнения при условии разрешения выдачи, поступающего на управляющий вход блока 1G с входа 22 устройства, В момент выдачи команды с выхода блока 4 буферной памяти команд производится обращение по считыванию соответствующих ячеек операндов в блок 12 буферной памяти через блок 11 адресации, и если ячейки заполнены, то их содержимое с выхода блока 12 буферной памяти выдается на выход 28 устройства. ЕСЛИ нет, то команда все равно выдается в специализированный блок, где ожидает своих операндов. В момент выдачи команды с выхода блока 16 также производится обращение по считыванию в блок 12 буферной памяти через блок 11 адресации, причем содержимое ячейки вне зависимости от состояния индикатора занятости ячейки передается на выход 28 устройства . При обращении очередной команды по записи в блок 12 буферной памяти через блок 11 адресации с входа 20 устройства адрес ячейки под результат в блоке 12 передается также на выход 27 устройства, сопровождая, таким образом, результат очередной команды (и операнд апя последующей), который, поступая с входа 21 устройства на вход блока 12, одновременно передается на выход 29 устройства, С выходов 28 и 29 устройства операн ды и с выхода 27 соответствуюыие им адреса блока 12 буферной памяти поступают на входы всех исполнительны специализированных блоков. По этим адресам команды, хранящиеся в специализированных блоках, опознают своих операндов и начинают выполняться. Одновременно с записью исполнительного адреса в блок 12 буферной памяти и одновременно с формированием арифметической команды или команды записи происходит реорганизация вершины стека или, что то же са мое, стека 5 дешифрированных адресов. В счетчике 34 верхней границы блока б указателей стека дешифрированных адресов находится текущий адрес по стеку 5, который с выхода счетчика 34 подается на адресный вход стека 5. Выдаваемые из стека 5 по значению счетчика 34 через коммутатор 9 в блок 4 номера операндов по блоку 12 согласно стековой дисциплине обработки команд вычеркиваются из стека 5. На их место по зна чению счетчика 34 записывается номер ячейки под результат команды в блоке12, который выдается из стека 7 через коммутатор 9 на вход сте ка 5. Вычеркивание операндов из сте ка 5 достигается изменением значени счетчика 34, которым управляет форм рователь 33. Таким образом, стекова дисциплина использования адресов яч ек блока 12, а следовательно, и сами операндов в этих ячейках обеспечива ется соответствующими изменениями счетчика 34 верхней границы, а также записью в стек 5 и считыванием из стека 5 по значению счетчика 34. Выдача номеров свободных ячеек блока 12 из стека 7 происходит .анал гично по значению счетчика 37 верхней границы в блоке 8 указателей стека свободных адресов, выход которого соединен с адресным входом стека 7. Изменением значения счетчика также управляет формирователь 33. Запись в стек 7 по блоку 12 производится по значению счетчика 38 нижней границы, выход которого соеди нен с адресным входом стека 7 и кото рым управляет блок 10 восстановления Ячейка операнда блока 12 считается освободившейся после выполнения команды, в которой она использовалась Соответствующие сигналы о выполнении команд с входа 17 устройства поступают в блок 10 восстановления, а освободившиеся адреса ячеек операндов с входа 18 устройства - на вход стека 7 и на вход блока 11 адресации. При этом в блоке 11 обнуляются индикаторы заг:олненности соответствующих ячеек. С Еыхода регистра 1 операций очередная команда поступает в блок 2 управления. В формирователе 33 вырабатывается последовательность сигналов, поступающих на его выход и управляющих изменениями счетчиков 34, 35 и 37. того, управляющие сигналы поступают на управляющие входы коммутатора 9 адресов, формирователя 3 кода операций, коммутатора 15 указателей стека дешифрирова 1ных адресов, входы стека 13 ссылок и регистра 14 ссылок. В узле 36 сравнения происходит сравнение значений счетчика 34 верхней границы и счетчика 35 нижней границы. По результату сравнения определяется наличие достаточного количества операндов для выполнения очередной команды. Если количество операндов достаточно, то с выхода шифратора 32 выдаетсяразрешение на выполнение команды, которое поступает на вход распределителя 31. При этом поступающие с входа 23 устройства тактовые сигналы на вход распределителя 31 преобразуются в соответствующую команду. Прюисходят формирование внутреннего представления команды и реорганизации блоков б и 8, описанные выше. Если определяется, что количество операндов меньше, чем требуется очередной команде, то организуется режим подкачки. С выхода шифратора 32 вьщается блокировочный сигнал, запрещающий реорганизацию блоков б и 8, запись в стек 5 и в стек 13, прием в регистр 1 и дешифрацию последующих команд на выход 30 устройства. С выхода шифратора 32 в распределитель 31 вьщается сигнал, по которому приостанавливается вьадача тактовых сигналов для очередной команды, и с выхода распределителя начинают поступать тактовые сигналы по временной диаграмме команды подкачки. По этим сигналам в формирователе 33 вырабатываются сигналы для формирования команды подкачки в блок 16, куда поступает код операции, сфор шрованный в формирователе 3, и адрес ячейки в блок 12 из стека 7 через коммутатор 9, Для сохранения стековой дисциплины адрес для подкачиваемого операнда должен быть записан в стек 5 дешифрированных адресов по значению счетчика 35 нижней границы. Для этого в формирователе 33 вырабатывается сигнал обмена, по которому обменивается содержимое с четчиков 34 и 35. Сформированная в блоке 16 ко манда подкачки поступает на выход 25 устройства для выполнения. Формирование команд подкачки про должается до тех пор, пока количест во адресов в стеке 5 не будет соответствовать количеству тpeбye 1ыx дл очередной команды операндов. Выраба тывается сигнал о прекращении подка ки, поступающей на вход распределителя 31. По окончании режима подкач ки производится обратный обмен соде жимого счетчиков 34 и 35, причем зн чение счетчика 35 нижней границы бу дет новым по сравнению с его значением до начала подкачки. Распределитель 31 переключается на выработку тактовых си.гналов по временной диаграмме очередной команды. Режим откачки устанавливается аналогично режиму подкачки. Отличие в том, что при отсутствии свободных адресов в стеке 7 и соответствующем сигнале из узла 39 сравнения в блоке 8 указателей стека свободных адресов режим откачки устанавливает ся лишь после того, как произойдет выполнение всех предыдущих команд. Сообщение об этом происходит с входа 17 устройства в блок 10 восстановления, откуда поступает в шифратор 32 . Это обусловлено тем, что после выполнения команды могут освободить ся ячейки блока 12, использованные в качестве операндов, и их адреса zvioryT быть записаны в стек 7 свобсад ных адресов с входа 18 устройства. Пока стек 7 пуст и не выполнены все предьщугдие команды, в устройстве поддерживается состояние ожидания, останавливая выработку тактовы сигналов в распределителе 31 и выдавая блокировку на выход. После записи адреса в стек 7 с входа 18 устройства шифратор 32 вьщает разре шение на обработку очередной команды, в противном случае усганавливается режим откачки. Другим отличием режима откачки является то, что адрес ячейки блока I2 выдается из стека 5 4ерез ком мутатор 9 в блок 4 буферной памяти ко1-/ а.чд. в сформированной команде откачка; содержится адрес ячейки бло ка , содержимое которой необходим отослать в блок оперативной памяти, так как на этот адрес указыпает сче чик 35 нижней границы в блоке 6 ука зателей стека дегиифрированных адресов . Полностьк заполненные блок 4 буферной памяти команд и блок 1G буфер ,ной памяти подготовительных команд формируют блокировочные сигналы. В результате при полной загрузке блока 4 блокируется формирование ко манд в блок 4, а при полной загрузке блока 1ь - формирование команд в блоки 4 и 16 до тех пор, пока соответствующие блоки памяти не смогут принять очередную команду. Формирователь 3 кода операций обеспечивает формирование кодов операций подкачки и отка.чки, а также трансляцию кода операции с входа на выход. Выбор режима работы формирователя 3 кода операций определяется сигналами, поступающими на его управляющий вход. Работа блока 10 восстановления определяется сигналами ОсвобождеВыполнение команние ячейки поступающими с входа 17 устройства (из специализированных устройств) на вход блока. При поступлении со всех специализированных устройств сигнала Выполнение команды на выходе элемента И 42 формируется сигнал о выполнении предыдущих команд, который передается в шифратор 32 для организации режима откачки в случае отсутствия свободных номеров в стеке 7 свободных адресов. По сигналу Освобождение ячейки , поступающему с входа 17 устройства на вход триггера 43, он устанавливается в единичное состояние. При установке триггера 43 в единичное состояние синхроимпульсом, поступающим с входа блока на управляющий вход триггера 44, информационный вход которого соединен с единичным выходом триггера 43, триггер 44 устанавливается в единичное состояние. При этом открывается элемент И 45, на вход которого поступают синхроимпульсы и на выходе блока появляются сигналы управления записью в стек 7 свободных адресов номера освобождаемой ячейки через блок 8 указателей свободных адресов , После выдачи сигналов блок приходит в исходное состояние следую щим образом: сначала с выхода элемента И 45 устанавливается в нулевое состояние триггер 43, затем синхроимпульсом - триггер 44. Блок 11 адресации работает следующим образом. При поступлении адреса освобожденной ячейки с входа 18 устройства через дешифратор 46 осуществляется установка в нулевое состояние соответствующего индикатора занятости (разряда) в регистре 48. При обращении очередной команды по записи результата выполнения команды или при записи исполнительного адреса операнда при формировании команды вызова операнда номер назначенной ячейки блока 12 буферной памяти соответственно поступает с входа 20 устройства на вход кo - мyтaтo-. pa 50, а с выхода коммутатора 9 - н щругой вход коммутатора 50, С выхода коммутатора 50 номер ячейки с признаком результата (операнда) передается на выход 27 устройства и на вход дешифратора 47, через который соответствующий индикатор занятости ячейки в регистре 4 устанавливается в единичное состояние. При выдаче- команд из блоков 4 и 16 буферной памяти производится обращение по считыванию в блок 12 буферной памяти, при этом адреса яч ек поступают соответственно с выхода блока 4 на вход коммутатора 51 и с выхода блока 16 на вход коммута тора 51. С выхода коммутатора 51 но мер ячейки передается на выход 27 устройства и на управляющий вход коммутатора 49 (индикаторов занятос ти ячеек), представляющего собой коммутатор К входов - один выход (где К - число ячеек блока 12 буфер ной памяти) и подключенного к выходу регистра 48. Сигнал с выхода ком мутатора 49 передается на выход 27 устройства, сигнализируя о заполнен ности ячейки (готовности операнда), к которой произведено обращение по считыванию. Режим работы распределителя 31 Выполнение определяется сигналами Блокировка выполнения команды ОткачПодкачкакоманды ка , поступающими с выхода шифрато ра 32 на его управляющий вход. По сигналу Выполнение команды поступающему на вход триггера 52, он устанавливается в единичное состояние, при этом с входа 23 устройства через элемент И 53, управляе1 4)1й с единичного плеча этого триггера, на счетный вход счетчика 55 начинают поступать тактовые импульсы, а через элемент И 54 на управляющий вход дешифратора 56 вырабатывается сигнал, по которому осуществляется дешифрация кода, поступающего на информационный вход дешифратора 56 со счетчика 55. I . Последовательность вырабатываемы сигналов зависит от типа выполняемо команды (команда вызова операнда, команда записи или команда арифмети ческая) , Изменение последовательнос ти вырабатываемых сигналов осуществ ляется с помощью элемента И 57, на первые входы которого поступают сиг налы с дешифратора 56, на вторые вх ды поступают сигналы о типе выполня мой команды с выхода регистра опера ций, а выходы подключены к второму входу триггера 52 (вход установки в нуль) и выходу блока. Сигнал с вы хода элемента И 57 сигнализирует о конце выполнения команды, а также устанавливает триггер 52 в нулевое состояние, прекращая тем самым выработку последовательности сигналов. Сигнал Блокировка выполнения команды, поступающий на первые входы элементов И 53 и 54, блокирует формирование сигналов на управляющий вход дешифратора 56 и счетный Bxofi Jcчeтчикa 55 и, следовательно, выработка последовательности сигналов прекращается. Сигнал Подкачка (Откачка) поступает на управляющий вход дешифратора G2 (63) , а через элемент ИЛИ 58 на вход триггера 59, устанавливая его в единичное состояние. При установке триггера 59 в единичное состояние через элемент И 60, управляемый с единичного плеча этого триггера, на счетный вход счетчика 61 с входа 23 усТ|ройства начинают поступать тактовые сигналы. Дешифрация кода счетчика 61 осуществляется с помощью дешифратора 62 (63). Вырабатываемая последовательность сигналов с вухода дешифратора 62 (63) поступает на выход блока, при этом последний сигнал последовательности сигнализирует о конце выполнения команды Подкачка (Откачка) и устанавливает триггер 59 в нулевое состояние. Работа формирователя 33 определяется управляющими сигналами с регистра операций, определяющими тип выполняемой команды (команда записи, команда вызова операнда или арифметическая команда) и поступающими на его управляющий вход, а также последовательностью сигналов, поступающих на его тактовый вход с распределителя 31. Управляющие сигналы с тактового входа формирователя поступают на входы групп элементов И 64, 65, 67, 68, 70 и 71. Последовательность сигналов с управляющего входа в зависимости от режима работы устройства (режим выполнения команды или режим Подкачка - Откачка) поступает соответственно на входы элементов И G4, 65, 67, 68, 70 и 71 или на входы элементов ИЛИ 66, 69 и 72. При совпадении сигналов на входах любого из элементов И 64, 65, 67, 68, 70 и 71 на их выходах появляется сигнал, который через элемент ИЛИ 66 или через элемент ИЛИ 69 (72), либо через триггер 73 выдается (снимается) на выход формирователя. С помощью группы элементов И 64 ... 65 и элементов ИЛИ 6ь формируются импульсные сигналы (т.е. сигналы, длительность которых равна длительности тактаi. С помощью группы элементов И 67 ... 68, 70 ... 71, элементов ИЛИ 69 и 72 и триггера 73 формируются сигналы, длительность которых больше длительности такта. Технико-экономическая эффективность при использовании устройства получается за счет повышения произв дительности ЭВМ, в состав которой предлагаемое устройство входит. Повышение производительности ЭВМ достигается путем более эффективной загрузки устройства ЭВМ, осуществля щих вызов операндов из памяти и выполнение арифметических и логических операций. Количественную оценку роста производительности ЭВМ можно произвести путем сравнения среднего значения загруженности исполнительных устройств, управляемых через общий буфер команд и через индивидуальные буферы команд с оптимизацией порядка вызова операндов. При вычислении среднего значения загруженности устройств необходимо учесть вероятность появления групп из И элементов при записи арифметических выражений в бесскобочной польской записи для вычислительных задач и долю вычислительных задач от общего объема задач. При определении загруженности исполнительных устройств полагаем: операции запись команды в буфер команд и считывание команды из буфера команд совмещены в устройство и выполняются за один такт; время выпол нения операций в исполнительных уст ройствах (устройстве вызова операндов и арифметическом устройстве) од наково и равно двум тактам; выполне ние команд в устройстве не совмещено , Загруженность устройства определяется отношением времени выполнения команд в устройстве ко времени работы устройства. При работе с общим буфером коман в случае, когда идет загрузкаодног устройства п командами одной группы, другое устройство простаивает, и наоборот, при этом время выполне ния fi команд в устройстве составляет 2П тактов, время ожидания загруз ки - 2(П-1) тактов. Следовательно, -загруженность в этом случае определится соотношением2пТ+2Т(П-1) 2h-l Р - загруженность устройства; h - количество элементов в группе при записи арифметического выражения в бесскобочной польской записи;Т - длительность такта устройства . Загруженность устройств при управлении их работой через индивидуальные буфера команд с учетом оптимизации порядка вызова операндов повышается и практически равна единице. Анализ программ показал, что вероятность появления групп в вычислительных задачах следующая: 0,15 для групп из двух элементов; 0,13 - для групп из трех элементов; 0,04 - для групп из четырех элементов; 0,005 - для групп из пяти и более элементов. Среднее значение загруженности для исполнительных устройств, управляемых через общий буфер команд при выполнении вычислительной задачи с учетом вероятности появления групп, определится формулой р,,б, где Р. - значение загруженности устройств для Л элементов в группе; S f, - вероятность появления группы из п элементов. Изменяя п от единицы до четырех, получим Pj.,8757. Таким образом, при решении вычислительных задач производительность ЭВМ повышается на 12,5%. Учитывая, что вычислительные задачи составляют примерно 60% от всего объема задач, повьпиение производительности ЭВМ (без учета повышения производительности при выполнении управляющих программ) равно 12,5x0,,5. Таким образом, за счет введения, буфера команд для вызова операндов и оптимизации порядка считывания операндов производительность ЭВМ повьшается на 7,5.

ЧЖ)

-

/;-2225

r5J} X- - -ф

1819f 7

-/

/.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство управления конвейерным вычислительным устройством | 1991 |

|

SU1751757A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

| Процессор микропрограмируемой ЭВМ | 1989 |

|

SU1697082A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПАРАЛЛЕЛЬНЫМ ВЫПОЛНЕНИЕМ КОМАНД В ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЕ, содержащее регистр операций, щифратор кода режима, блок адресации, блок буферной памяти, стек дешифрированных адресов, блок указателей стека дешифрированных адресов, стек свободных адресов, блок указателей стека свободных адресов, формирователь кода операций, формирователь синхронизирующих сигналов, коммутатор адресов, блок буферной памяти команд, блок восстановления и распределитель тактовых импульсов, первый вход и выход которого подключены соответственно к первому управляющему входу устройства и к первому входу блока восстановления, группа входов шифратора кода режима соединена с первым выходом блока восстановления, с управляющими выходами блока буферной памяти команд, блока указателей стека дешифрированных адресов, блока указателей стека свободных адресов, первый выход шифратора кода режима соединен с управляющими входами регистра операций, стека дешифрированных адресов, первым управляющим выходом устройства, с первым входом блока указателей стека дешифрированных адресов и с первым входом блока указателей стека свободных адресов, выход формирователя синхронизирующих сигналов соединен с управляющими входами формирователя кода операций, коммутатора адресов, с вторым входом блока указателей стека свободных адресов и с вторым входом блока указателей стека дешифрированных адресов, адресный вход стека дешифрированных адресов подключен к выходу коммутатора адресов и к первым входам блока адресации и блока буферной памяти команд, выход стека дешифрированных адресов подключен к первому входу коммутатора адресов, второй вход которого соединен с выходом стека свободных адресов, первый и второй адресные входы котороС го соединены соответственно с пер- g вым и вторым выходами блока указате(Л лей стека свободных адресов, третий вход которого подключен к второму выходу блока восстановления, второй вход которого соединен с вторым управляющим входом устройства, информационный вход блока буферной памяти подключен к первому информационному входу устройства и к первому .информационному выходу устройства, выход блока буферной памяти подключен к второму информационному выходу устройства, выход блока адресации соединен с первым адресным выходом устрюйства и с адресным входом блока буферной памяти, второй вход блока адресации соединен с третьим управляющим входом устройства, третий вход блока адресации и информационный вход стека свободных адресов подключены к второму информационному входу устройства, четвертый вход блока адресации и второй управляющий выход устрюйства подключены к информационнгаиу выходу блок. буферной памяти команд, второй вход которого соединен с выходом формирователя кода операций, управляющий вход является четвертым управляющим входом устрой

/7«/

Фиг. 2

С

«5

Фиг.

51

fS

/(

27

-

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3725376, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-07—Публикация

1982-11-03—Подача