Изобретение относится к контрольно-иэмерительной технике в микроэлектронике и предназначеио для отбраковки дефектных ТТЛ интегральных схем (ИС) с номинальным напряжением питания 5 В.

Известен способ контроля ИС по цепи питания, при котором подают номинальное напряжение питания одновременно ни контролируемую и опорну HCfHa их входы подают испытательный сигнал, а о годности контролируемой ИС судят по отличию потребляемых по цепи питания токов контролируемой и опорной ИС ) .

Недостатком этого способа является невозможность выявления ИС со скрытыми дефектами.

Наиболее близким по технической сущности к изобретению является способ контроля полупроводниковых приборов/ включающий помещение контролируемых ИС в термокамеры, задание повыцГенной и пониясенной температур, выдержку в течение 30 мин/ измерение при каждой температуре статических параметров при номинальном напряжении питания, вынесение решения о годности ИС на основании соответствия измеренных параметров, техническим условиям PJ .

Недостатком известного способа является его сложность, связанная с необходимостью создания темпера- , тхфных режимов путем выдерживания контролируемых ИС в термокамере.

Целью изобретения является упро.Щение контроля ТТЛ ИС,

Поставленная цель достигается тем, что согласно способу контроля , ТТЛ ИС, включающему измерение их статических параметров при номинальном напряжении питания, производят измерение статических параметров ИС прц пониженном напряжении питания в диапазоне 3,1 - 3,2 В, определяют разность значений статичес ких параметров, измеренных при номинальном и пониженном напряжениях питания и сравнивают эту разность с эталонным значением.

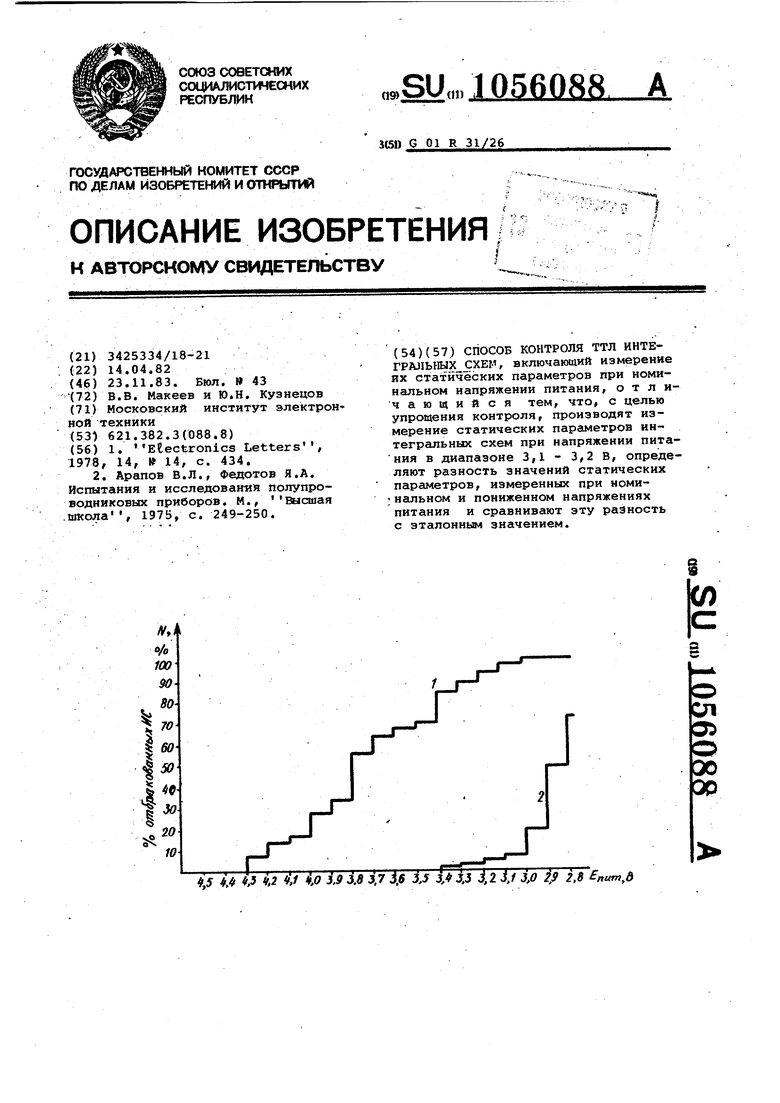

На чертеже приведены зависимости числа отбракованных ИС от величины пониженного напряжения питания (1 группа ИС годных при нормальной температуре, но из-за различных дефектов не удовлетворяющих требованиям ТУ при крайних значениях рабочих температур (-60 и +125 с); 2 - группа ИС годных во всем диапазоне рабочих температур).

В результате анализа отказов ИС при испытаниях и эксплуатации, а также анализа брака с различных контрольно-измерительных операций в производстве ИС выявлены основные виды дефектов, снижающих качество и надежность ИС. Для ТТЛ ИС наиболе

часто встречающимися являются л фвкты, приводящие к утечкам между различными узлами схемы. Так при контроле ТТЛ ИС с сопротивлением утечки на подложку базы входного транзистора,равной 5 кОм, ее можно выявить путем измерения напряжения логического нуля только при . При более высоких температурах эта утечка не выявляется. При длительной зксп0луатации вследствие протекания различных физико-химических процессов величина утечки по дефекту может меняться, что приводит к катастрофическому отказу. Поэтому такие утечки опасны с точки зрения надежности.

При уменьшении напряжения источника питания резко повышается чувствительность выходных статических параметров ИС к внутрисхемным утечкам. С 5меньшением напряжения питания

0 увеличиваются критические величины сопротивлений утечек, приводящих к аномальным изменениям выходных параметров. При этом появляется возможность при нормальной температуре

5 отбраковывать ИС с дефектами, которые известными способами выявлялись лишь при изменениях температуры.

Теоретически минимальная величина напряжения питания, при которой

0 ТТЛ ИС еще функционирует, составляет 2,8 В. Однако на практике, в силу разброса электрофизических параметров компонентов в пределах допусков, данная величина напряжения приводит к отбраковке большого количества годных ИС. Выбор величины пониженного напряжения питания произведен эмпирически. На чертеже показаны эмпирические распределения числаотбракованных ИС для двух групп заведомо годных ИС и ИС со Скрытыми дефектами. При снижении напряжения питания увеличивается процент отбраковываемых дефектньлх схем. Однако при напряжении питания ниже 3,1 В начинают в значительном количестве i браковаться и годные ИС. Оптимальным с точки зрения эффективности контроля и экономичности произво/тства является диапазон 3,1 - 3,2 %. Конк0ретное значение пониженного напряжения питания внутри данного диапазона зависит от требований ТУ,,.,которые колеблются в з ависимости от.Типа ИС, от допустимых значений рибка

5 поставщика и заказчика, от условий и целей производства.

При анализе значений выходных статических параметров годных и дефектных схем установлено, что оценку

0 годности ИС целесообразно проводить по величине изменения параметра при изменении напряжения питания. Это дает возможность не браковать те ИС, у которых завышенные или заниженные

5 абсолютные значения параметров,обусловленные не каким-либо дефектом, а получившимся соотношением электрофизических параметров компонентов. Такие KCf не удовлетворяя по абаоч лютной величине выходных статических параметров жестким требованиям метоперационного контроля, тем не менее могут отличаться хорошей стабильностью и нормально функционируют при различных режимах эксплуатации.

Данный способ опробируют в производстве биполярных ИС транзисторнотранзисторной логики при измерении выходных напряжений логического ноля и логической единицы. При измерении статических параметров схем при комнатной температуре до разделения пластин на кристаллы измерение статических параметров проводят при двух величинах напряжения питания Сначала - при напряжении, равном 4,5 В, затем - при напряжении, равном 3,2 В. При этом годными считают схемы, у которых разница выходных напряжений логического нуля измеренных при двух величинах напряжения питания не превышает 60 мВ, а разница выходных напряжений логической единицы не более 1,5 В.Например, если при питании 4,5 В выходное напряжение логического ноля равно 300 мВ, а при питании 3,2 В оно увеличивается, до 340 мВ, то такая ИС считается годной. Если увеличение составляет олее 60 мВ и значение параметра

равно, , 380 мВ, то такая схема считается негодной. Аналогично ДЛЯ выходного напряжения логической единицы.

После разделения данных пластин на кристаллы, сборки кристаллов в корпусы к контроля Статических параметров полученных схем при повышен.ной и пониженной температурах, т.е. при Тг-бО С и при Т.4-125с, выход

o годных при повшленной и пониженной температурах увеличивается по сравнению с текущей продукцией, контро .тируемой по известному способу, в среднем на 7,2%, Таким образом, предлагаемый способ контроля позволяет при комнатной температуре до разделения пластин на кристаллы отбраковывать ИС с низкой температурной стабильностью статических параметров .

0

Предлагаемый способ контроля ТТЛ ИС проводят при комнатной температуре и может быть применён при контроле параметров схем до разделения пластин на кристаллы. Это позвол1-1т

5 за счет отбраковки негодных схем на более раннем этапе технологического процесса избежать затрат,, связанных со сборкой этих схем в корпусн, а также с операциями нагрева

0 и охлаждения ИС. Проведение контроля схем при двух напряжениях питания ПОЗВОЛИТ также повысить качество выпускаемых ИС.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля ТТЛ итегральных схем | 1989 |

|

SU1675804A1 |

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 2004 |

|

RU2257591C1 |

| СПОСОБ ОТБРАКОВКИ ИНТЕГРАЛЬНЫХ СХЕМ | 2001 |

|

RU2217843C2 |

| Способ контроля микросхем со скрытыми дефектами | 1987 |

|

SU1511721A1 |

| Способ отбраковки потенциально ненадёжных цифровых интегральных схем по времени задержки распространения сигнала | 2024 |

|

RU2836117C1 |

| Способ неразрушающей диагностики интегральных схем | 2020 |

|

RU2743708C1 |

| СПОСОБ СТАБИЛИЗАЦИИ НАНО- И МИКРОЭЛЕКТРОМЕХАНИЧЕСКОЙ СИСТЕМЫ ТОНКОПЛЕНОЧНОГО ТЕНЗОРЕЗИСТОРНОГО ДАТЧИКА ДАВЛЕНИЯ | 2010 |

|

RU2434210C1 |

| СПОСОБ СТАБИЛИЗАЦИИ ТОНКОПЛЕНОЧНОЙ НАНО- И МИКРОЭЛЕКТРОМЕХАНИЧЕСКОЙ СИСТЕМЫ ТЕНЗОРЕЗИСТОРНОГО ДАТЧИКА ДАВЛЕНИЯ | 2011 |

|

RU2472127C1 |

| Способ отбраковки ненадежных КМОП ИС | 1984 |

|

SU1239658A1 |

СПОСОБ КОНТРОЛЯ ТТЛ ИНТЕГР7и1ЬШХ ХЕМ, включающий измерение их статических параметров при номинальном напряжении питания, отличающийся тем, что, с целью упрощения контроля, производят измерение статических параилетров интегральных схем при напряжении питания в диапазоне 3,1 - 3,2 В, определяют разность значений статических параметров, измеренных при номи;нальном и пониженном напряжениях питания и сравнивают эту разность с зталонным значением. а с СП ОГ) о 00 СХЭ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Etectronics Letters, 1978, 14, № 14, с | |||

| Станционный указатель направления времени отхода поездов и т.п. | 1925 |

|

SU434A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арапов В.Л., Федотов Я.А | |||

| Испытания и исследования полупроводниковых приборов | |||

| М., Высшая .школа, 1975, с | |||

| Трансляция, предназначенная для телефонирования быстропеременными токами | 1921 |

|

SU249A1 |

Авторы

Даты

1983-11-23—Публикация

1982-04-14—Подача