Изобретение относится к микроэлектронике, а именно к обеспечению надежности цифровых интегральных схем (ЦИС) за счет определения потенциально ненадежных. Изобретение может быть использовано на этапе серийного производства ЦИС, а также на входном контроле при производстве радиоаппаратуры.

Так как временные параметры ЦИС увеличиваются при снижении напряжения питания, что эквивалентно увеличению длительности переходного процесса при эксплуатации, то на этом принципе предложен способ для прогнозирования работоспособности ЦИС.

Известен способ диагностирования ЦИС [1] по зависимости величины изменения времени задержки сигнала Δ tз 01 (при различных напряжениях питания) от tз 01 при номинальном напряжении питания. Годной считается ЦИС, у которой Δ tз 01≤0,75 Δ tз 01 мax (Δ tз 01 мах - максимальное значение времени задержки входного сигнала ЦИС при снижения напряжения питания до величины Uн - пониженного напряжения питания).

Недостатки известного способа таковы, что в цифровых интегральных схемах не учитывается различие временных параметров по имеющимся в ЦИС нескольким однотипным входам.

Известен способ отбраковки комплиментарных МОП (металл, окисел, полупроводник) (КМОП) интегральных схем по уровням надежности [2], принятый за прототип.

Способ-прототип заключается в том, что в качестве информационного параметра для отбраковки интегральных схем (ИС) выбрано время задержки распространения сигнала при включении и выключении. Этот параметр позволяет в большей мере учесть дефекты ИС, чем измерение статических параметров и в то же время обладает более ранним этапом обнаружения дефектов, чем нестабильная сигнатура. Проводят отбраковку ЦИС путем сравнения разности значений между средним значением времени задержки распространения сигнала при включении (выключении) для выборки и времени задержки распространения для конкретной ЦИС при пониженном напряжении питания, с интервалом значений, устанавливаемых эмпирически в зависимости от типа ЦИС и предъявляемых требований по надежности.

Недостатками способа-прототипа являются недостаточные функциональные возможности и достоверность диагностики.

По схемотехнике и технологии изготовления временные параметры по однотипным входам в идеальном случае должны быть одинаковыми, но фактически они разнятся. Величина разности временных параметров по однотипным входам несет информацию о несовершенстве поверхностной и объемной структуры p-n-переходов. Поэтому, замеряя временные параметры по однотипным входам, по их отличию можно судить о потенциальной надежности этих переходов, а следовательно, и по надежности ЦИС в целом.

Изобретение направлено на расширение функциональных возможностей и повышение достоверности результатов диагностики.

Для устранения указанных недостатков в способе, заключающемся в том, что измеряют временные (динамические) параметры по всем входам ЦИС при пониженном напряжении питания, сравнивают их с интервалом допустимых значений, устанавливаемых эмпирически, получают результат сравнения, являющийся первым критерием отбраковки цифровых интегральных схем, согласно изобретению измеряют временные параметры при номинальном напряжении питания по всем входам раздельно, определяют отношение величины временного параметра каждого входа к минимальной величине временного параметра одного из входов данной ЦИС, сравнивают его с интервалом допустимых значений, устанавливаемых эмпирически, получают результат сравнения, являющийся вторым критерием, при совпадении двух критериев ЦИС отбраковывают как потенциально ненадежную.

Предлагаемый способ заключается в том, что на партии ЦИС, в которой необходимо определить, а затем отделить потенциально ненадежные схемы, проводят измерение динамических параметров, например, времени задержки распространения сигнала при включении (выключении), по всем входам раздельно при напряжении питания близкого к критическому напряжению питания, одинакового для всех ЦИС. Устанавливают первый критерий для отбраковки потенциально ненадежных интегральных схем по абсолютной величине значения временного (динамического) параметра, например, tздp 0,1≥150 нс.

Затем на этих же схемах по всем входам измеряют такой же временной параметр при номинальном напряжении питания. Строят таблицу, где для каждой ЦИС минимальное значение времени задержки распространения сигнала при включении (выключении) по входу принимается за единицу, а по остальным входам записывают полученный коэффициент К, определяющий интервал допустимых значений, устанавливаемых эмпирически, равный отношению величины времени задержки распространения сигнала при включении (выключении) по данному входу к значению минимальной величины времени задержки, принятой за единицу. Выбирается критерий оценки, например значение К≥ 1,75, устанавливающийся для потенциально ненадежных ЦИС. Это второй критерий для отбраковки ЦИС.

Те ЦИС, у которых совпали два критерия, считаются потенциально ненадежными.

Конкретные значения критериев определяются для каждого типа ЦИС в зависимости от жесткости требований по надежности.

Пример осуществления способа.

На произвольно выбранных 10 ЦИС типа К155ЛР1 (два элемента 2И-2ИЛИ-НЕ, один с расширением по ИЛИ) измерили время задержки распространения сигнала при выключении tздр 0,1 при напряжении питания Uн=2 В, частоте импульсов 10 МГц (табл. 1). Данное напряжение определено снижением напряжения питания у каждой схемы до тех пор, пока ЦИС еще работает в соответствии с назначением.

Если по полученным данным таблицы 1 выбрать первый критерий tзp≥150 нc, то потенциально ненадежными будут ЦИС №5, 6, 8.

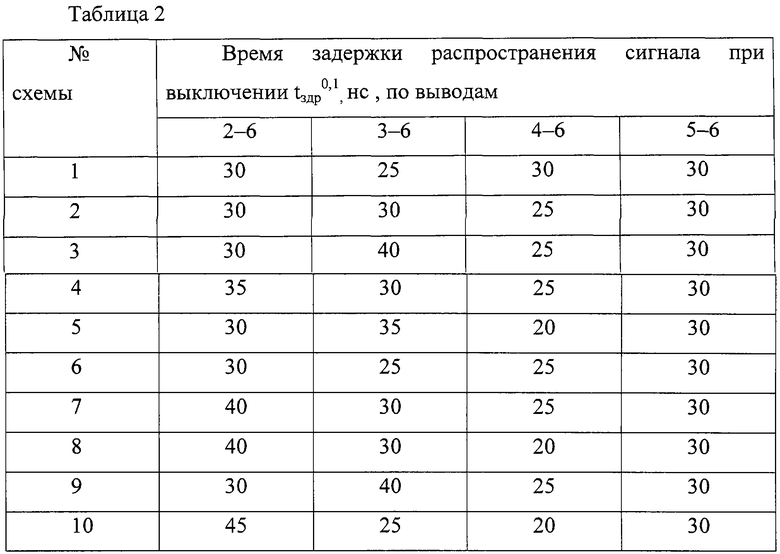

Замерили tздр 0,1 в режиме Uп (при номинальном напряжении питания) (табл.2)

По полученным данным составим таблицу 3 коэффициентов увеличения tздр 0,1 по всем выводам относительно минимального значения.

По таблице 3 при втором критерии Kj≥1,75 потенциально ненадежными будут схемы № 5, 8, 10.

Окончательное значение по двум критериям одновременно: потенциально ненадежными будут схемы № 5, 8.

Проведенные испытания в течение 500 ч при максимальной нагрузке и повышенной температуре 70° С подтвердили полученные результаты.

По сравнению с прототипом предлагаемый способ позволяет расширить функциональные возможности и повысить достоверность результатов диагностики.

Источники информации

1. Кураченко С.С., Прохоренко В.А., Воинов В.В. Новый метод диагностирования ИС // Электронная промышленность. 1990. № 6. С.71-72.

2. Патент RU 2046365 C1, G 01 R 31/26. Опубл. 20.10.95. Бюл. № 29.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ отбраковки потенциально ненадёжных цифровых интегральных схем по времени задержки распространения сигнала | 2024 |

|

RU2836117C1 |

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| Способ отбраковки КМОП интегральных схем по уровням надежности | 1985 |

|

SU1269061A1 |

| СПОСОБ ОТБРАКОВКИ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 2005 |

|

RU2284538C1 |

| СПОСОБ ОТБРАКОВКИ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 2004 |

|

RU2276378C1 |

| Способ разделения КМОП интегральных схем по надежности | 2023 |

|

RU2829710C1 |

| СПОСОБ КОНТРОЛЯ ПОЛУПРОВОДНИКОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 1990 |

|

RU2018148C1 |

| Способ неразрушающего контроля качества сверхбольших интегральных схем по значению критического напряжения питания | 2018 |

|

RU2696360C1 |

| СПОСОБ ИЗМЕРЕНИЯ ПЕРЕХОДНОЙ ТЕПЛОВОЙ ХАРАКТЕРИСТИКИ ЦИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ | 2015 |

|

RU2613481C1 |

| СПОСОБ ОТБРАКОВКИ ПОТЕНЦИАЛЬНО НЕНАДЕЖНЫХ ТОНКОПЛЕНОЧНЫХ РЕЗИСТОРОВ | 2023 |

|

RU2825537C1 |

Изобретение относится к измерительной технике, а именно к автоматическому контролю цифровых интегральных схем. Технический результат - повышение достоверности процесса диагностики цифровых интегральных схем. Для достижения данного результата измеряют основные динамические характеристики и параметры цифровых интегральных схем при пониженном и номинальном напряжении питания. На основе полученных результатов формируют критерии для отбраковки цифровых интегральных схем. При этом по всем входам цифровых интегральных схем раздельно определяют отношение величины временного параметра каждого входа к минимальной величине временного параметра одного из входов данной цифровой интегральной схемы. 3 табл.

Способ определения потенциально ненадежных цифровых интегральных схем, имеющих несколько однотипных входов, заключающийся в том, что измеряют временные (динамические) параметры при пониженном напряжении питания, сравнивают их с интервалом допустимых значений, устанавливаемых эмпирически, получают результат сравнения, являющийся первым критерием отбраковки цифровых интегральных схем, отличающийся тем, что измеряют временные параметры при номинальном напряжении питания по всем входам раздельно, определяют отношение величины временного параметра каждого входа к минимальной величине временного параметра одного из входов данной цифровой интегральной схемы, сравнивают его с интервалом допустимых значений, устанавливаемых эмпирически, получают результат сравнения, являющийся вторым критерием, при совпадении двух критериев цифровую интегральную схему отбраковывают как потенциально ненадежную.

| СПОСОБ ОТБРАКОВКИ КМОП ИНТЕГРАЛЬНЫХ СХЕМ ПО УРОВНЯМ НАДЕЖНОСТИ | 1992 |

|

RU2046365C1 |

| Кураченко С.С., Прохоренко В.А., Воинов В.В | |||

| Новый метод диагностирования ИС | |||

| Электронная промышленность | |||

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕПЛОВОГО СОПРОТИВЛЕНИЯ ПЕРЕХОД-КОРПУС ПОЛУПРОВОДНИКОВЫХ ДИОДОВ | 2001 |

|

RU2178893C1 |

| Siemens "Силовые IGBT модули" | |||

| Материалы по применению | |||

| - М.: ДОДЭКА, 1997, с.101-107 | |||

| DE 1231815 А, 01.05.1967. | |||

Авторы

Даты

2005-07-27—Публикация

2004-04-19—Подача