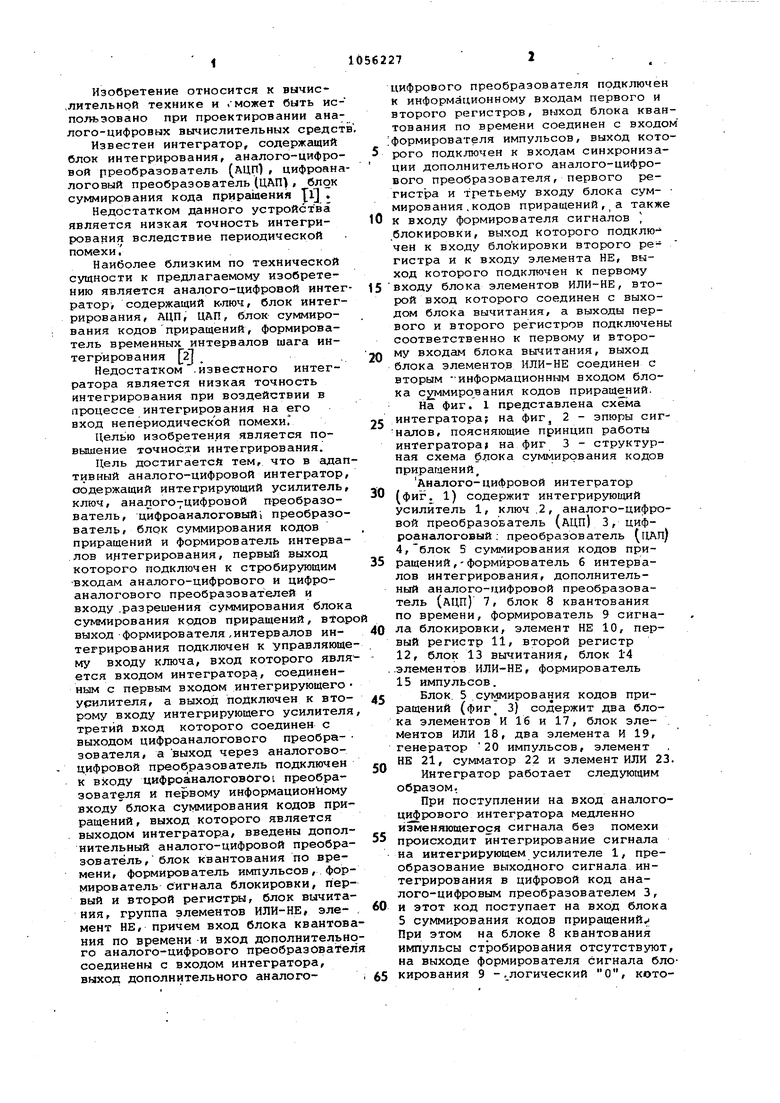

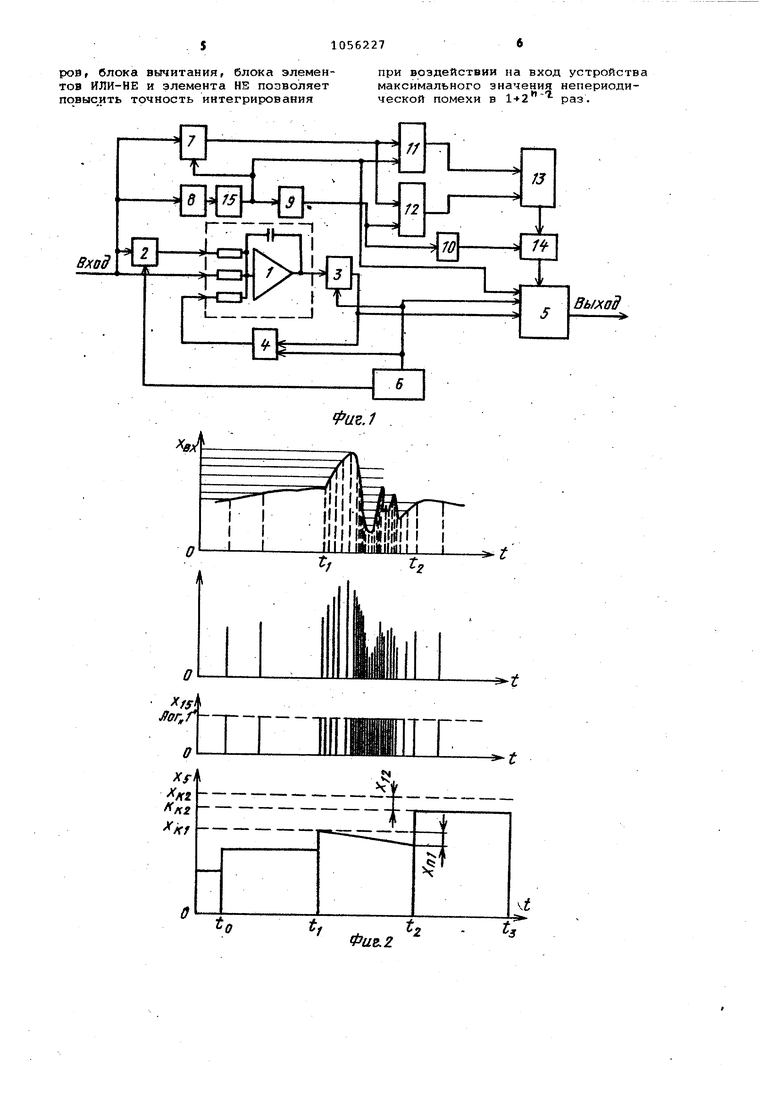

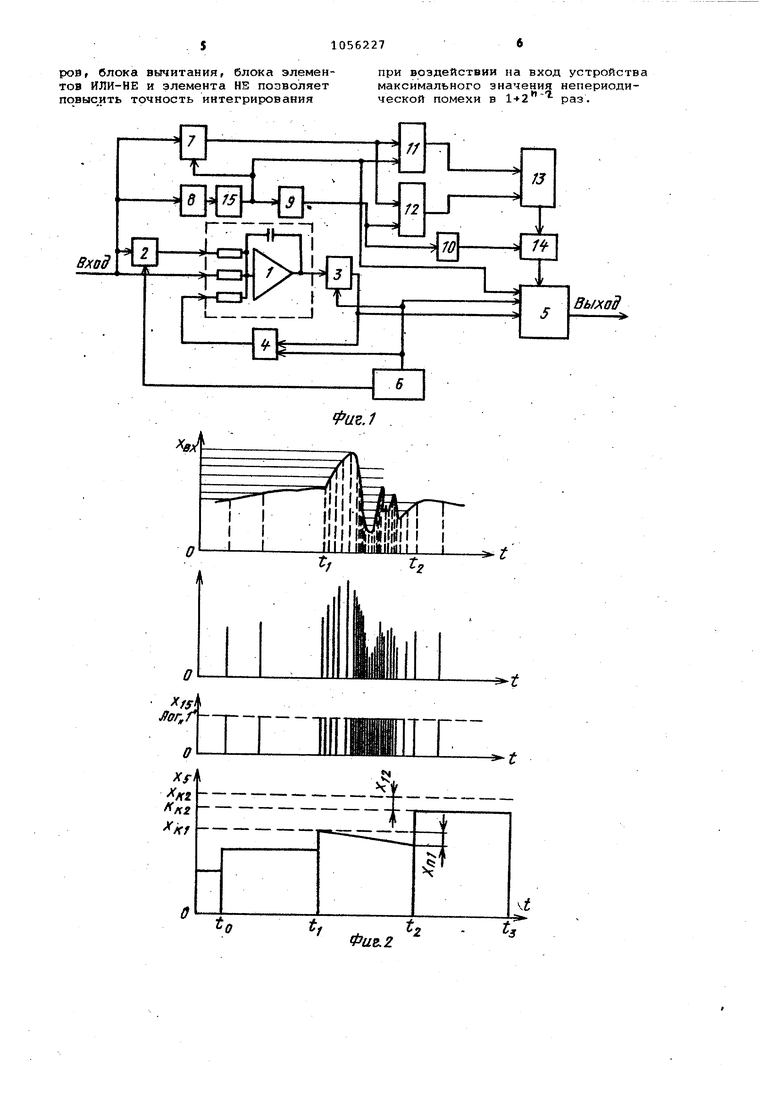

Изобретение относится к вычис.лительной технике и .может быть испотозэовако при проектировании аналого-цифровых вычислительных средст Известен интегратор, содержащий блок интегрирования, аналого-цифровой преобразователь (АЦП), цифроана логовый преобразователь(ЦАП), блок суммирования кода прираидения Недостатком данного устройства является низкая точность интегрирования вследствие периодической помехи, Наиболее близким по технической сущности к предлагаемому изобретению является аналого-цифровой интег ратор, содержащий ключ, блок интегрирования, АЦП, ЦАП, блок суммирования кодов приращений, формирователь временных интервалов шага интегрирования {2J Недостатком .известного интегратора является низкая точность интегрирования при воздействии в процессе интегрирования на его вход непериодической помехи. Целью изобретения является повышение точности интегрирования. Цель достигаетсй тем, что в адап тивный аналого-цифровой интегратор содержащий интегрирующий усилитель ключ, аналого7Цифровой преобразователь, цифроаналоговый преобразователь/блок суммирования кодов приращений и формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и цифроаналогового преобразователей и входу .разрешения суммирования блока суммирования кодов приращений, втор выход формирователя,интервалов интегрирования подключен к управляюще му входу ключа, вход которого явля ется входом интегратора, соединенным с первым входом интегрирующего усилителя, а выход подключен к второму входу интегрирующего усилителя третий вход которого соединен с выходом цифроаналогового преобразователя, а выход через аналоговоцифровой преобразователь подключен к входу цифроаналогового. преобразователя и первому информацион ому входу блока суммирования кодов приращений , выход которого является выходом интегратора, введены допол нительный аналого-цифровой преобра зователь, блок квантования по времени, формирователь импульсов,.фор мирователь сигнала блокировки, пер вый и второй регистры, блок вычита ния, группа элементов ИЛИ-НЕ, элемент НЕ, причем вход блока квантов ния по времени и вход дополнительн го аналого-цифрового преобразовагел соединены с входом интегратора, выход дополнительного аналого цифрового преобразователя подключен к информационному входам первого и второго регистров, выход блока квантования по времени соединен с входом ;формирователя импульсов, выход которого подключен к входам синхронизации дополнительного аналого-цифрового преобразователя, первого регист1ра и третьему входу блока сум- мирования.кодов приращений,а также к входу формирователя сигналов блокировки, выход которого подклю- чен к входу блокировки второго регистра и к входу элемента НЕ, выход которого подключен к первому входу блока элементов ИЛИ-НЕ, вторюй вход которого соединен с выходом блока вычитания, а выходы первого и второго регистров подключены соответственно к первому и второму входам блока вычитания, выход блока элементов ИЛИ-НЕ соединен с вторым -информационным входом блока с пимиро вания кодов приращений. На фиг, 1 представлена схема интегратора; на фиг, 2 - эпюры сигналов, поясняющие принцип работы интегратора на фиг 3 - структурная схема блока суммирования кодов приращений, Аналого-цифровой интегратор (фиг. 1) содержит интегрируюищй усилитель 1, ключ .2, аналого-цифрювой преобразователь (АЦП) 3, цифроаналоговый ; преобразователь (ЦАП) 4, блок 5 суммирования кодов приращений,- формирователь 6 интервалов интегрирования, дополнительный аналого-цифровой преобразователь (АЦП) 7, блок 8 квантования по времени, формирователь 9 сигнала блокировки, элемент НЕ 10, первый регистр 11, второй регистр 12, блок 13 вычитания, блок 14 .элементов ИЛИ-НЕ, формирователь 15 импульсов. Блок. 5 суммирования кодов приращений (фиг 3) содержит два блока элементов И 16 и 17, блок элементов ИЛИ 18, два элемента И 19, генератор 20 импульсов, элемент НЕ 21, сумматор 22 и элемент ИЛИ 23. Интегратор работает следующим образом. При поступлении на вход аналогоцифрового интегратора медленно изменяющегося сигнала без помехи происходит интегрирование сигнала на интегрирующем усилителе 1, преобразование выходного сигнала интегрирования в цифровой код аналого-цифровым преобразователем 3, и этот код поступает на вход блока 5 суммирования кодов приращений,При этом на блоке 8 квантования импульсы стробирования отсутствуют, на выходе формирователя сигнала блокирования 9 -.логический О, который поступает нг входы блока эЛем тов ИЛИ-НЕ 14 и тем самым блокиру значение, снимаемое с выхода блок 13 вычитания. Далее при рассмотрении работы интегратора будем пользоваться графиками (фиг. 2). При поступлении в моментД,: помехи любой .ды. длительностью .Си 2 V, где Ни длительность помехи; Tjj - период импульсов шага i интегрирования. На выходе блока 8 квантования появляются импульсы, частота кото рых прямо пропорциональна скорост изменения входного сигнала. Вид импульсов показан на графике Xg 5Cg (t) , фиг. 2. Эти импульсы преобразуются формирователем 15 импульсов и на его выходе имеют вид, показанный на.графике Х (i) фиг. 2. Эти импульсы синхронизируют АЦП 7, регистр 11 блок 5 суммирования кодов приращений. Они же поступают на вход формирователя 9 сигнала блокировки, на выходе которого логическая 1 блокТГрхет на регистре 12 последнее значение входного сигнала, поступившего непосредственн перед началом действия помехи Эта же логическая 1 преобразует ся в логический 0 который поступает на блок элементов ИЛИ-НЕ открывая доступ сигнала с выхода блока 13 вычитания на блок 5 суммирования КОДОВ приращений. При этом на регистре 11 фиксируются коды, соответствующие величине смеси сигнал/помеха. Эти коды вычитаются на блоке 13 вычитания, на выходе которого имеем текущие значения помехи, фиксированные с частотой квантования блока 8 квантования. Значения кодов инвертируются и складываются с ко дом записанным в блоке 5 суммирования кодов приращений в момент времени- t( .. Поясним работу этого блокаГ На фиг, 3 представлена его структурная , схема. При поступлении сигнала с формирователя.6 на вход элемента НЕ 21, являющийся входом разрешения суммирования блока 5 суммирования кодов приращений, импульс формирователя 6 блокирует вход синхронизации и второй информационный вход блока генератор 20 импульсов и поступае на .вход блока элементов И 17, вто рой вход которого является первым информационным входом блока 5.Од новременно происходит считывание и суммирование сумматором 22 значения интегрсша с АЦП 3. Во время действия помехи при отсутствии сигнала на входе разрешения суммирования блока 5 суммирования кодов, на eip вход синхронизации поступают импульсы с формирователя 15 импульс сов. Они поступгиот на вход блока элементов И 16, на второй вход которого поступают текущие инвертированные значения помехи. Сложение этих значений с находящейся в сумматоре 22 величиной происходит в моменты формирювания сигналор генеjpaTopa 20 импульсов, частота импульсов которого определена временем быстродействия логических элементов. Таким образом, за время от момента tf до1у из сум.матора 22 вычитается интеграл поме-. хи (на графике Ху Xy(i) фиг 2 {значение Хц,) . В момент t на сумматор, поступает величина интегрирования с АЦП 3, но так как в предыдущем такте величина интеграла помехи вычлась заранее, то на выходе блока 5 суммирования кодрв приращений формируется сигнал Х., В случае отсутствия процесса вычитания интеграла помехи, на выходе блока 5 была бы величина X)J ( (ц Хп) В результате работы аналого-цифрового интегратора на результат интегрирования не влияет помеха. Таким образом, влияние помехи любой амплитуды с длительностью б 2Тц, , полностью устраняется, При этом Ту выбирается так, что при максимальной скорости изменения входной функции последующее значение АЦП 3, фиксированное сигналом формирователя б, будет отличаться от предыдущего на единицу младшего разряда АЦП. I Преимуществом изобретения по . сравнению с базовым объектом,яв- . ляется повышение точности интегрирования при наличии на входе устройства непериодической помехи любой амплитуды с длительностью менее двух периодов интегрирования. 1 : . . При этом выигрыш в точности интегрирования определяется выражением 1Х с г - - 1 4. «п к - 1 + -Jг Oartban где OQ(, - ошибка, обусловленная разрядностью аналогоцифрового преобразователя;ЦП ошибка, вносимая непериодической помехой. Таким образом, введение в аналого-цифровой интегратор дополнительного АЦП, блока квантования по времени, формирователя импульсов, формирователя сигнала блокировки -.первого и второго регистpoBf блока вычитания, блока элементов ИЛИ-НЕ и элемента HS позволяет повысить точность интегрирования

при воздействии на вход устройства максимального значения непериодической помехи в раз.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор синусоидальных сигналов | 1984 |

|

SU1193674A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842867A1 |

| УСТРОЙСТВО МОНИТОРИНГА ВЫСОКОВОЛЬТНЫХ ВВОДОВ И СИГНАЛИЗАЦИИ О СОСТОЯНИИ ИХ ИЗОЛЯЦИИ | 2006 |

|

RU2328009C1 |

| Цифровой феррозондовый магнитометр | 1982 |

|

SU1114997A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| АЦП С ПЕРИОДИЧЕСКОЙ ПОДСТРОЙКОЙ ПОСТОЯННОЙ СОСТАВЛЯЮЩЕЙ | 2001 |

|

RU2198463C1 |

| Измеритель характеристик аналого- цифРОВыХ пРЕОбРАзОВАТЕлЕй | 1978 |

|

SU819950A1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| РЕВЕРСИВНЫЙ ЧИСЛО-ИМПУЛЬСНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2429563C1 |

АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР, содержащий интегрирующий усилитель, ключ, аналого-цифровой преобразователь, ..«цифроаналоговый преобразователь/ блок суммирования кодов приращений и формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и -.Цифроаналогового преобразователей и входу разрешения суммирования блока суммирования кодов приращений, второй вы- . ход формирователя интегралов интегрирования подключен к управляквдем . входу ключа, вход которого является входом интегратора, соединенным с первым входом интегрирующего усилителя, а выход подключен к второму входу интегрирующего усилителя третий вход которого соединен с выходом цифроангалогового . преобразователя, а выход через анашого-цифровой преобразователь подключен.к входу цифроаналогового преобразователя.и первому информационному входу блока суммирования кодов приращений , выход которого является Iвыходом интегратора, отличающийся тем, что,с целью повышения точности интегрирования, в него введены дополнительный аналого-цифровой преобразователь, блок квантования по времени, формирователь импульсов, формирователь сигнала блокировки, первый и второй регистры, блок вычитания, блок элементов ИЛИ-НЕ, элемент НЕ, причем вход блока квантования по времени и вход дополнительного аналого-цифрового преобразователя соединены с входом интегратора, выход дополнительного аналого-цифрового преобразователя подключен к информационным входам первого и второго регист(Л ров, выход блока квантования по времени соединен с входом формирователя импульсрв, выход которого подключен к входам синхронизации дополнительного аналого-цифрового преоб- разователя, первого регистра и блока суммирования кодов приращений, а также к входу формирователя сигнала блокировки, выход которрго подо ел а 1ключен к входу блокировки второго регистра и к входу элемента НЕ, выход которого подключен к первому входу .блока элементов ИЛИ-НЕ, вторрй ND вход которого соединен с выходом л блока вычитания, а выходы первого и второго регистров подключенысоответственно к первому и вторюму ,входам блока вычитания, выход блока .элементов ИЛИ-НЕ соединен с вторым инфррмацирнным входом блока суммирования кодов приращений.

Xff

Jfor.n

Фие.2

13

Вход 1

еход2

16

18

Выход

22

23

J1

19

,ФиВ.5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аналого-цифровой интегратор | 1976 |

|

SU578645A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР ,№ 842867, кл, G 06 j 1/00, 1979 (прототип). | |||

Авторы

Даты

1983-11-23—Публикация

1982-08-05—Подача