Изобретение относится к вычислительной технике и может быть использовано при проектировании аналого-цировых вычислительных средств.

Цель изобретения - повышение точ- ности интегрирования синусоидальных сигналов.

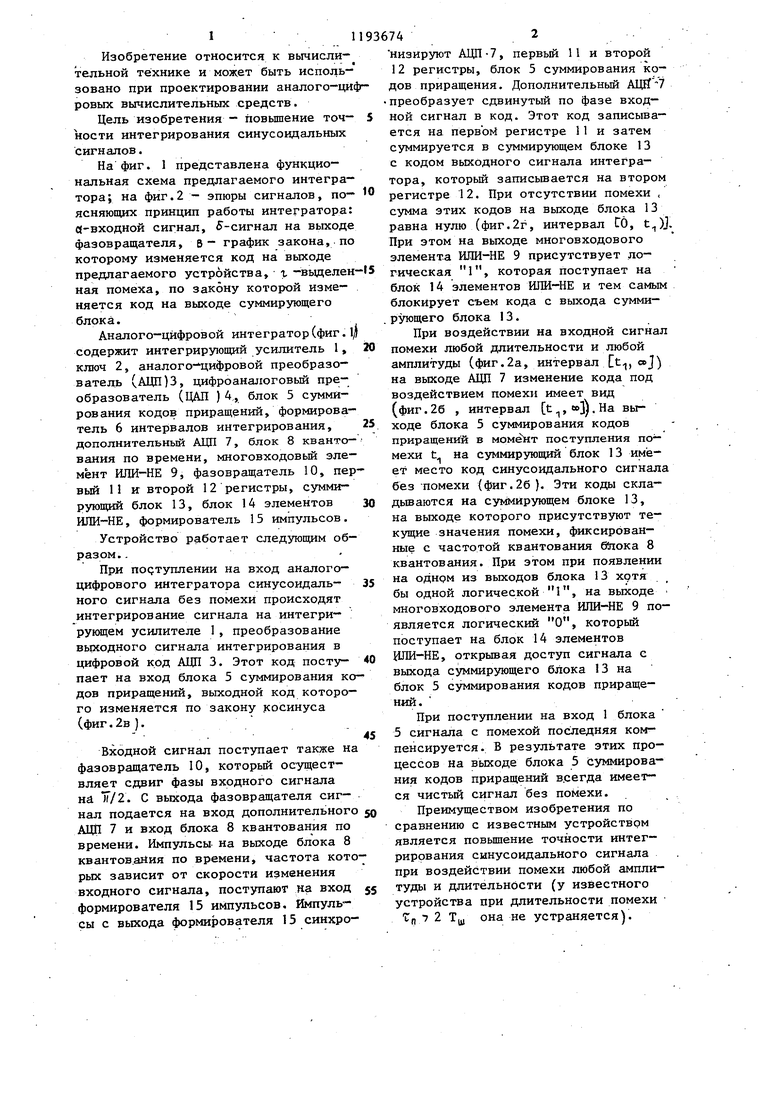

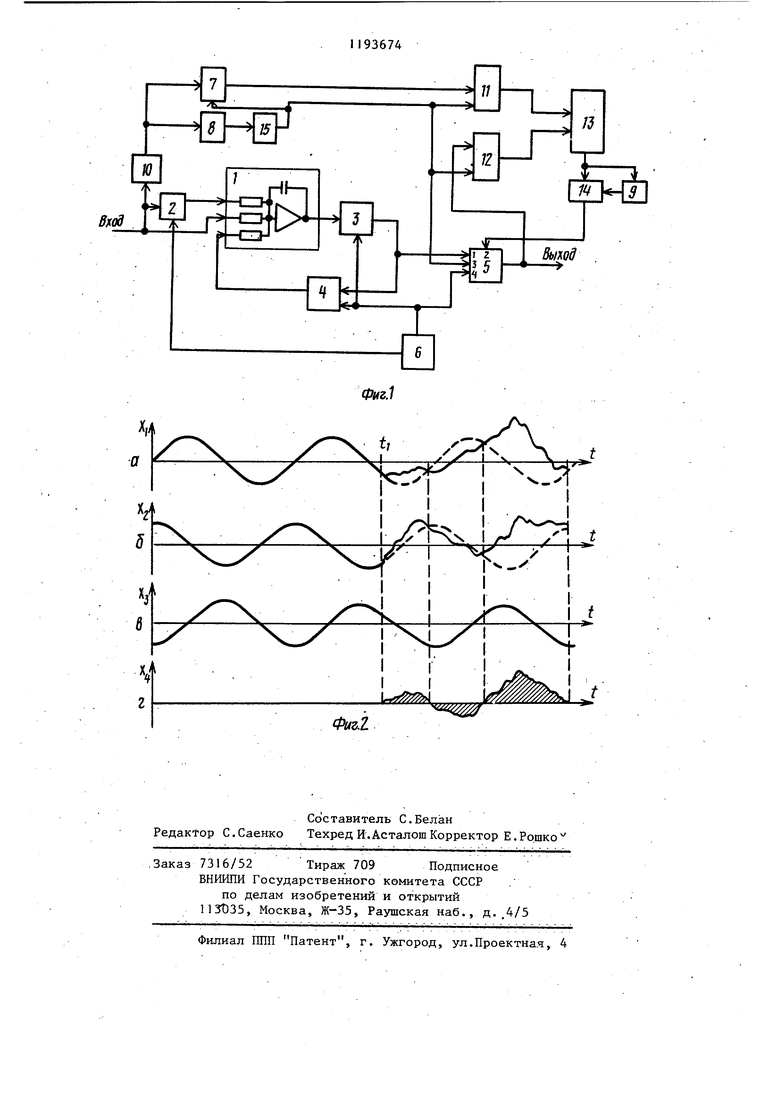

На фиг. 1 представлена функциональная схема предлагаемого интегратора; на фиг.2 - эпюры сигналов, по- ясняюпщх принцип работы интегратора: «-входной сигнал, 5-сигнал на выходе фазовращателя, в- график закона, по которому изменяется код на выходе предлагаемого устройства, г -выделен ная помеха, по закону которой изменяется код на выходе суммирующего блока.

Аналого-цифровой интегратор (фиг. 1 содержит интегрирующий усилитель 1 ключ 2, аналого-цифровой преобразователь (АЦП)З, цифроаналоговый преобразователь (ЦАП ) 4,, блок 5 суммирования кодов приращений, формирователь 6 интервалов интегрирования, дополнительный АЦП 7, блок 8 кванто- вания по времени, многовходовьй элемент Ш1И-НЕ 9, фазовращатель 10, первый П и второй 12 регистры, суммирующий блок 13, блок 14 элементов ИЛИ-НЕ, формирователь 15 импульсов.

Устройство работает следующим образом ..

При подтуплении на вход аналогоцифрового интегратора синусоидального сигнала без помехи происходят интегрирование сигнала на интегри- ; рукяцем усилителе I , преобразование вьрсодного сигнала интегрирования в цифровой код АЦП 3. Этот код посту- пает на вход блока 5 суммирования кодов приращений, выходной код которого изменяется по закону косинуса СФИГ.2В ).

.

Входной сигнал поступает также на

фазовращатель 10, которьш осуществляет сдвиг фазы входного сигнала на /2. С выхода фазовращателя сигнал подается на вход дополнительного АЦП 7 и вход блока 8 квантования по времени. Импульсы на выходе блока 8 квантов.аЯия по времени, частота которых зависит от скорости изменения входного сигнала, поступают на вход формирователя 15 импульсов. Ш пуль- сы с выхода формирователя 15 синхронизируют АЦП-7, первый П и второй 12 регистры, блок 5 суммирования кодов приращения. Дополнительный АЦ1Г 7 преобразует сдвинутый по фазе входной сигнал в код. Этот код записывается на первом регистре 11 и затем суммируется в суммирующем блоке 13 с кодом выходного сигнала интегратора, который записьшается на втором регистре 12. При отсутствии помехи , сумма этих кодов на выходе блока 13 равна нулю (фиг.2г, интервал ГО, t) При этом на выходе многовходового элемента ШШ-НЕ 9 присутствует логическая 1, которая поступает на блок 14 элементов ИЛИ-НЕ и тем самьм блокирует съем кода с выхода сумми- .рующего блока 13.

При воздействии на входной сигнал помехи любой длительности и любой амплитуды (фиг.2а, интервал t, ееJ) на выходе АЦП 7 изменение кода под воздействием помехи имеет вид (фиг. 26 , интервал t,to,Ha выходе блока 5 суммирования кодов приращений в момент поступления помехи Ц на суммирующий блок 13 имеет место код синусоидального сигнала без -помехи (фиг. 26 ). Эти коды складьшаются на суммирующем блоке 13, на выходе которого присутствуют текущие значения помехи, фиксированные с частотой квантования бйока 8 квантования. При этом при появлении на однрм из выходов блока 13 хотя бы одной логической 1, на выходе многовходового элемента ИЛИ-НЕ 9 появляется логический О, который поступает на блок 14 элементов ЩМ-НЕ, открывая доступ сигнала с выхода суммирующего блока 13 на блок 5 суммирования кодов приращений.

При поступлении на вход 1 блока 5 сигнала с помехой последняя компенсируется. В результате этих процессов на выходе блока 5 суммирования кодов приращений всегда имеется чистый сигнал без помехи.

Преимуществом изобретения по сравнению с известным устройством является повьшение точности интегрирования синусоидального сигнала при воздействии помехи любой амплитуды и длительности (у известного устройства при длительности помехи tf, 7 2 Тщ она не устраняется).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842867A1 |

| СПОСОБ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИЗМЕРИТЕЛЬНЫХ СИГНАЛОВ | 2009 |

|

RU2444125C2 |

| Способ аналого-цифрового преоб-РАзОВАНия и уСТРОйСТВО для ЕгООСущЕСТВлЕНия | 1979 |

|

SU839050A1 |

| УСТРОЙСТВО МОНИТОРИНГА ВЫСОКОВОЛЬТНЫХ ВВОДОВ И СИГНАЛИЗАЦИИ О СОСТОЯНИИ ИХ ИЗОЛЯЦИИ | 2006 |

|

RU2328009C1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 2018 |

|

RU2670389C1 |

| Цифровой измеритель @ -параметров | 1983 |

|

SU1120254A1 |

| ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ-КОД С ИНДУКТИВНЫМ ДАТЧИКОМ | 1992 |

|

RU2065665C1 |

АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР СИНУСОИДАЛЬНЫХ СИГНАЛОВ, содержащий интегрирующий усилитель, первый вход которого является входом интегратора и через ключ соединен с вторым входом интегрирующего усилителя, третьим входом связанного через цифроаналоговый преобразователь с выходом первого аналого-цифрового преобразователя, подключенного входом к выходу интегрирующего усилителя, а выходом - к первому входу блока суммирования кодов приращений, выход которого является выходом интегратора, а второй вход через блок элементов ИЛИ-НЕ соединен с выходом суммирующего блока, -входы которого подключены к выходам первого и второго регистров. формирователь интервалов интегрирования, первый выход которого подключен к стробирующим входам аналого-цифрового и цифроаналогового преобразователей и входу разрешения блока суммирования кодов приращений, а второй выход соединен с управляющим входом ключа, второй аналого-цифровой преобразователь, выход которого подключен к информационному входу первого регистра, информационный вход второго регистра соединен с выходом блока суммирования кодов приращений, выход блока квантования по времени через формирователь имI пульсов подключен к входу синхрони(Л зации второго аналого-цифрового преобразователя, первого и второго регистров и блока суммирования кодов приращений, отличающийся тем, что, с целью повьшения точности интегрирования, он содержит фазовращатель и многовходовый элемент ИЛИ-НЕ, включенный между выходом сумсо мирующего блока и вторым входом бло00 ка элементов ИЛИ-НЕ, вход фазовращаа теля подключен к входу интегратора, а выход соединен с входами второго 4;: аналого-цифрового преобразователя и входом блока 1 вантования по времени.

| Аналого-цифровой интегратор | 1979 |

|

SU842867A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-18—Подача