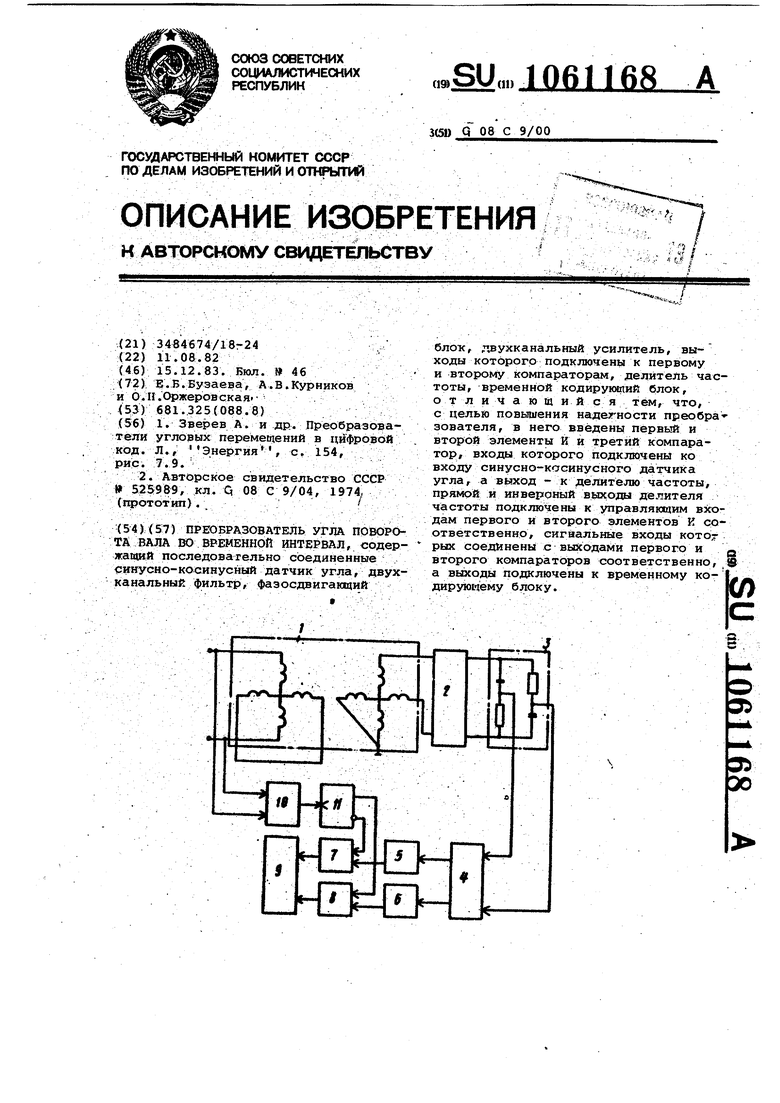

Изобретение относится к автоматике и вычислительной технике и может быть использовано л автоматических системах управления в качестве составной части преобразователя угол-ко или как самостоятельный преобразователь. Извейтен преобразователь угла поворота вала во временной интервал, состоякий из синусно-косинусного датчика угла (СКДУ) , фазодвиганжчего блока, суммирукл-дего и вычитакжего блоков, двух нуль-органов и -три ;;гераНедостатком известного преобразователя является неоднозначность соответствия временного интервала углу в пределах полного оборота ротора . СКДУ, что требует включения в состав преобразователя специального логичес кого блока формирования староего раз ряда, с помсФ1ью которого и устраняется иеоднозначность преобразования в пределах оборота вала. А это услож няет пре образователь угол-код, в котором используется указанный преобра зователь. Наиболее близким к изобретению является преобразователь угла поворота вала во временной интервал, содержа1«ий последовательно соединенные синусно-косинусный датчик угла, двухканальннА фильтр, фазосдвигающий блок, двухканадьный усилитель, высходы которого подключены к первому и второму компараторам, делитель Частоты, временной кодирукюий блок Яругой делитель частоты, выходы первого и второго компараторов через один и другой делитель частоты соответственно подключены к временному кодирукЛчему блоку 2 . Однако равновероятная возможность вьщачи результатов измерения одного и того же значения угла снижает надежность работы данного преобразователя. Цель изобретения - повые ние надежности преобразователя. Поставленная цель достигается тем, что в преобразователь угла поворота вала во временное интервал, содержащий последоватвльнр соединен ные синусно-косинусный датчик угла, двyxкiaнaльнt)й фильтр, фазосдвигающив блок, двухканалышй усилитель, выходы которого подключены к первому и вторсму компараторсШ, делитель частоты, временной кодирующий блок, введены первый и второй элементы И .и третий ксмпараторг.входы которого подключенн к входу синусно-косинусного датчика угла, а выход - к делителю частоты, прямой и инверсный выходы делителя частоты подключены к управляк1:;йм входам первого и второго элементов И соответственно, сигнальные входи которых соединены с выходами первого и второго компараторов .соответственно, а вьисоды подключены к временному кодирукячему блoкv. На чертеже представлена структурная схема преобразователя угла во временной интервал. Схема включает синусно-косинусный датчик 1 угла, двухканальный фильтр 2, Фазосдвигак.ий блок 1, двухканальный усилите ль 4, первый 5 и второй 6 компараторы, первый 7 и второй 8 элементы И, временной кодируклчий блок 9, третий кс таратор 10, делитель 11 частоты. Преобразователь работает следующим образом. На вход обмотки возбуждения .СКДУ 1 и компаратора 10 поступает синусоидальный сигнал переменного тока U,-Uj slncjt, . где СО - круговая частота напряхсения питания СКЧУ 1. Компаратор 10 формирует короткие импульсы в моменты перехода через нуль при поло)ительном градиенте сигнала U . Выходные сигналы СКДУ 1 через двухканальныС фильтр 2 поступают на входы блока 3, представляющего собой двойную RC -цепь и вырабатывающую сигналы и и Uj в соответствии с равенствами U2 (wl+j+)i .(), где х - угол поворота ротора СКЦУ 1,. Сигналы через двухканаль шй усилитель 4 подаются на входы компараторов 5 и б, формирующих короткие импульсы в моменты перехода через нуль при положительном градиенте входного сигнала. Шпульсы с выхода компаратора 10 поступают на ; вход делителя 11, имеющего коэффициент деления, равный 2. В качестве делителя 11 мокет быть нспользо.ван, например, триггер со счетным входе. Выходные напряжения делителя 11 имеют вид перепадов напряжения, которых совпадают во времени с выходными импульсами компаратора 10И-.имеют период следования, равнь 2Т (где Т - период напряжения возбуждения СКДУ 1), а скважность, равную 2. Выходные напряжения делителя 11всегда находятся в противофазе по.ютноиению друг к другу. Инверсный выход делителя 11 подключен к управляющему входу элемента 7, а прямой выход - к управляющему входу элемента 8. В результате выходу ные импульсы компараторов 5 и 6 роходят на входы кодирующего блока

3 , 10611684

9 всегда в разные периоды возбужде-ротора СКДУ не зависит от состояния

ния СКЛУ 1.делителя 11 в момент включения преКодируюиий блок 9 устанавливает-образователя. В результате увеличися в состояние .по импульсам свается надежность работы преобразоваэлемента 7 и возвращается в нуле потеля.

и шyльcaм. с элемента 8. При этом Экономическ1й эффект от испольэодпитёльность временного интервала навания предлагаемого преобразователя

выходе блока 9 изменяется в пределахопределяется его 7ехническ|)М преиму0-2 Т в зависимости от угла поворота.теством,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1985 |

|

SU1267620A1 |

| Преобразователь угла поворота вала во временной интервал | 1977 |

|

SU655890A1 |

| Преобразователь угла поворота вала в код | 1981 |

|

SU980112A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 1991 |

|

RU2020752C1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1152090A1 |

| Преобразователь угла поворота вала во временной интервал | 1975 |

|

SU525989A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Преобразователь угла поворота вала в длительность импульсов | 1980 |

|

SU907568A1 |

ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОР ТА ВАЛА ВО ВРЕМЕННОЙ ИНТЕРВАЛ, соде жащий последовательно соединенные синусно-косинусный датчик угла, дву канальный фильтр, фаэосдвигакадий блок, лвухканальный усилитель, выходы которого подключены к первому и второму компараторам, делитель частоты, временной кодирующий блок, о т л и ч а ю щ и и с я тем, что, с целью повышения надежности преобразователя, в него введены первый и второй элементы И и третий компаратор, входы которого подключены ко входу синусно-косинусного датчика угла, а выход - к .делителю частоты, прямой и инвероный выходы делителя ча стоты подключе ны к управляющим входам первого и второго элементов И соответственно, сигнальные входы котог рых соединены с выходами первого и Q второго компараторов соответственно,8 а вьосоды подключены к временному кодирующему блоку. а 00

Авторы

Даты

1983-12-15—Публикация

1982-08-11—Подача