(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сортировки чисел | 1984 |

|

SU1254467A1 |

| Устройство для моделирования узлов коммутации сообщений | 1986 |

|

SU1354203A1 |

| Устройство для моделирования узлов коммутации сообщений | 1985 |

|

SU1278879A1 |

| Устройство для автоматического контроля веса материала в бункерах | 1980 |

|

SU964475A2 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для автоматического поиска неисправностей | 1972 |

|

SU467331A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Устройство для сортировки чисел | 1987 |

|

SU1444749A1 |

| Устройство для поиска неисправностей | 1982 |

|

SU1059550A1 |

| Устройство контроля веса материала в бункерах | 1980 |

|

SU972243A1 |

Изобретение относится к автоматике и вычислительной технике и предназначен но для использования в устройствах передачи и обработки информации. Известно устройство для сравнения чисел, содержащее блок уставок, блок фор мирования знака, коммутатор, счетчик, схему сравнения, триггер, элементы И, ИЛИ, и элемент задержки . Недостатком этого устройства является то, что оно обеспечивает последовательное сравнение N. чисел и выбор по результатам сравнения большего из них. Наиболее, близким к предлагаемому по технической сущности и достигаемому ре- зультату является устройство для поразрядного сравнения двоичных чисел, содержащее регистры сдвига, группа выходов которых соединена с группой входов блока для поразрядного сравнения двоичных чисел пе{тый выход которого соединен с выходным регистром, второй в третий выходысоответо.теенно;с первым и вторым входами блока управления, первый выход которого соединен с первыми входами регистров сдвига, причем входящая в состав блока для поразрядного сравнения двоичных чисел группа элементов И первыми входами соединена с соответствующими входами блока для поразрядного сравнения двоичньк чисел, а выходами - с входами элемента ИЛИ, выход которого соединен с пертым выходом блока для п6разр1щного сравнения двоичных чисел и с управляющими входами группы элементов запрета НЕ-И, сигнальные входы которых соединены с соответствующими входами блока для поразрядного сравнения двоичных чисел, выходы группы элементов запрета НЕ-И соединены с первыми входами триггеров, вторые и третьи входы которых соединены соответственно с вторым и третьим выходами блока для поразрядного сравнения двоичных чисел, выходы группы триггеров соединены cooiw ветственно с вторыми входами группы

элементов И и с первой группой вых-одов блока для.поразрядного сравнения двоичных чисел 21 .

Недостатком известного устройства является то, что в нем не обеспечивается $ указание номера входного регистра с максимальным числом.

Целью изобретения является расшире ние функциональных возможностей за формирования адреса максимального чис- 10 ла.- Поставленная цель достигается тем, что в устройство для сравнения чисел, содержащее входные регистры сдвига, блок (5 поразрядного сравнения, выходной регистр, элементы задержки, причем выходы каж- . дого -( -го входного регистра сдвига со- , единены с входами i -го блока поразряд- ного сравнения, где | Г, 2,..,, П , д блок поразрядного сравнения содержит п элементов И, Я элементов запрета, Ц триггеров, элемент ИЛИ, -и вход каждого

блока поразрядного .сравнения поуоключан к инф ормационному входу каждого ( нго

элемента И блока, выхоц каждого i -го элемента И соеаинен с -м входом элемента ИЛИ, выход которого подключен к управляющим входам элементов запрета, выход каждого ( -го элемента запрета соединен с входом установки в единичное состояний триггера, входы синхронизадии которых подключены к входу запуска уст- ройства, который через первый элемент задермжи соединен с входами установки . в нулевое состояние триггеров, выход .

элемента ИЛИ блока поразрядного сравнения подключен к информационному входу выходного регистра, введены блок выбора канала, шифратор адреса, регистр, при 8ТОМ I -и выход блока поразрядного сравнения соединен с f -w входом блока выбора канала, управляющий вход которого через второй элемент задержки подключен к выходу первого элемента задержки, выход блока выбора, канала соединен с входом шифратора адреса, выходы которого подключены к входам регистра, блок выбора канала состоит из П входных элементов И, эл «гента НЕ, {П-2) элементов запрета, (П - 1) выходных элементов 50 И, -и вход блока соединен с первым входом -го входного элемента И, выход каждого j входного элемента И, где J 1, 2, ..., П , соединен с первым входом ( - 1) выходного элемента И и с управляющим входом ( j - 1)-го элбмента запрета, выход - j -го элемента запрета подключен к информационному

входу ( ,.| +1)-го элемента запрета и к второму входу -го выходного элемента И, выход первого входного элемента И соединен с .первыь) выходом узла и через элемент НЕ -подключен к первому входу перв1эго выходного элемента И и к инфор- . маиионнрму входу первого элемента запрета, выход каждого i.-го выходного элемента И соединен с (t +1)-ым выходом удла. . .

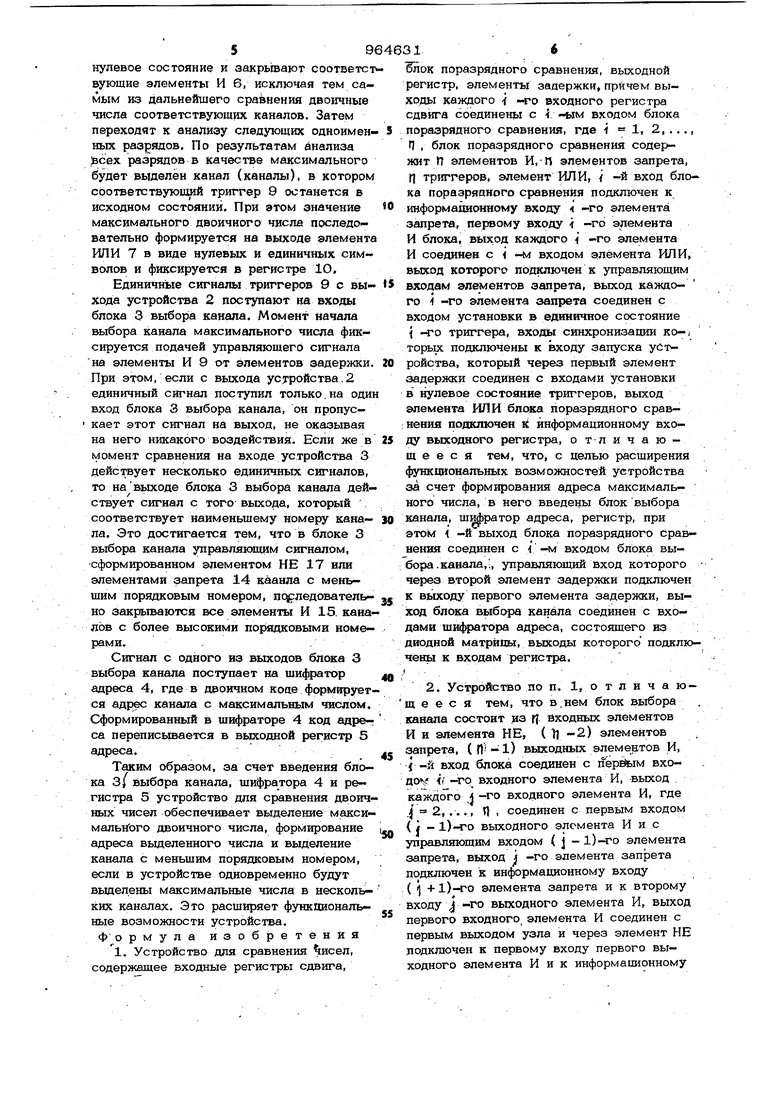

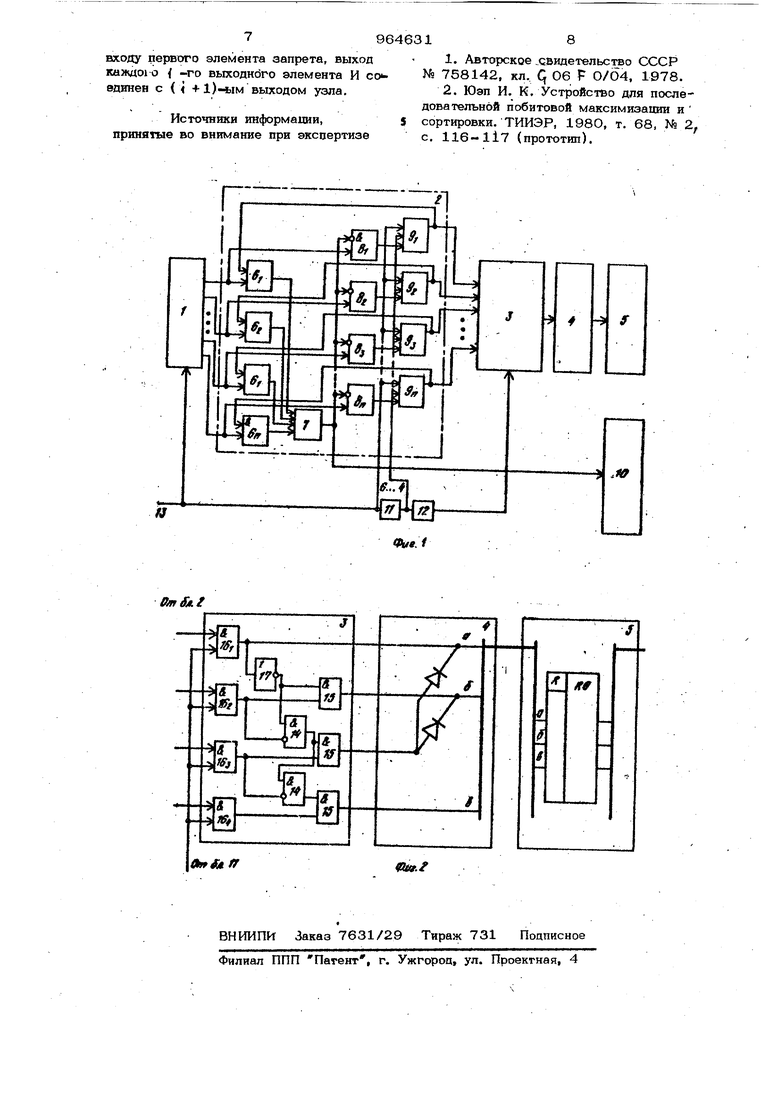

На фиг, 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока выбора канала, шифратора и выходного регистра (вариант выполнения для N 4).

Устройство для сравнения двоичных . чисел содержит (фиг. 2) входные регистры 1 сдвига, блок 2 поразрядного сравнения, блок 3 выбора канала, шифратор 4 адреса, регистр 5, группу элементов И 6, б2, .,., 6tj, элементы ИЛИ 7, элем енты запрета 8,, впр . ., 8ц. триггеры 9, 92,..., 9fj, выходной регистр 10 элемента задержки 11 и 12, вход 13.запрета устройства.

Блок 3 выбора канала {фиг. 2) содер- , жит элементы запрета 14 и элементы И 15 и 16, элемент НЕ 17.

Шифратор 4 адреса (фиг. 2) может быть выполнен в виде диодной матрицы.

Устройство для сравнения двоичных чисел работает следующим образом.

Сравниваемые двоичные числа всех JY каналов хранятся BQ входных регистрах. По сигналу с элементов задержки И 12 производитса последовательный анализ всех одноименных разрядов двоичных чисел, начиная со старшего (младшего) разрада Если все одноименные старшие (младшие) разряды двоичных чисел в регистрах 1 единицы (нули), то на выходах элементов И формируется сигнал 1 (сигнал О) и на выходе элемента ИЛИ соответственно сигнал 1 (сигнал О). Этот сигнат;-вместе с сигналами с регистров 1 поступает на элементь запрета 8. При этом на ьыходе всех элементов запрета 8 действует сигнал О, {который не изменяет состояние триггеров 9. Если в регистрах 1 фиксируются коды с разными значениями одноименных разрядов, то в процессе анализа на выходе элементов И 6 формируются сигналы 1 и О, соответственно, а на выходе элемента ИЛИ 7 только. сигнал 1. В этом спуше элементы запрета НЕ-И 8 для единичных разрядов, формируют сигнал О, а для нулевых разрядов - сигнал 1, соотетствующие триггеры 9 переводятся в нулевое состояние и аакрьгоаюг соответст вующие элементы И 6, исключая тем самым из дальнейшего сравнения двоичные числа соответствующих каналов. Затем переходят к анализу следующих одноименных разрядов. По результатам анализа ;всех разрядов в качестве максимального будет вьшелён канал (каналы), в котором соответствующий триггер 9 останется в исходном состоянии. При этом значение максимального двоичного числа последовательно формируется на выходе элемента ИДИ 7 в виде нулевых и единичных символов и фиксируется в регистре 1О. Единичнь1е сигналы триггеров 9 с выхода устройства 2 поступают на входы блока 3 выбора канала. Момент начала выбора канала максимального числа фиксируется подачей управляющегс сигнала на элементы И 9 от элементов задержки. При этом, если с выхода ус гройства, 2 единичный сигнал поступил только.на оди вход блока 3 выбора канала, он пропускает этот сигнал на выход, не оказывая на него никакого воздействия. Если же в момент сравнения на входе устройства 3 действует несколько единичных сигналов, то навьссоде блока 3 выбора канала действует сигнал с того выхода, который соответствует наименьшему номеру кана- ла. Это достигается тем, что в блоке 3 выбора канала управляющим сигналом, сформированном элементом НЕ 17 или элементами запрета 14 каанла с меньшим порядковым номером, пррледовательно закрьтаются все элементы И 15. кана лов с более высокими порядковыми номерами... Сигнал с одного из выходов блока 3 выбора канала поступает на ши( адреса 4, где в двоичном коае формирует ся адрес канала с максимальным числом. Сформированный в шифраторе 4 код адреса переписывается в выходной регистр 5 адреса.. Таким образом, за счет введения блока 3} выбора канала, шифратора 4 и регистра 5 устройство для сравнения двоич- нь1х чисел обеспечивает выделение макси- мальНЬго двоичного числа, формирование адреса вьзделенного числа и выделение канала с меньшим порядковым номером, если в устройстве одновременно будут вьщел.ены максимальные числа в нескольких каналах. Это расширяет функциональные возможности устройства. Формула изобретения 1. Устройство для сравнения исел, содержащее входные регистры сдвига. ок поразрядного сравнения, выходной регистр, элементы задержки, причем выходы каждого i -го входного регистра сдвига соединены с I, ым входом блока поразрядного сравнения, где i 1, 2, ..., П , блок поразрядного сравнения содержит П элементов И, П элементов запрета, П триггеров, элемент ИЛИ, f -и вход блока поразрядного сравнения подключен к информашонному входу -го элемента запрета, первому входу i -го элемента И блока, выход каждого -i -го элемента И соединен с i -м входом элемента ИЛИ, выход которого подключен к управляющим входам элементов запрета, выход каждого i -го элемента запрета соединен с входом установки в единичное состояние -го триггера, входы синхронизации ко- j Topbix подключены к входу запуска устройства, который через первый элемент задержки соединен с входами установки в нулевое состояние триггеров, выход элемента ИЛИ блока поразрядного сравнения подключен и информационному входу выходного регистра, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет формирования адреса максимального числа, в него введены блок выбора канала, шю)ратор адреса, регистр, при этом i -и выход блока поразрядного сравнения соединен с f -м входом блока выбора.канала,;, управляющий вход которого через второй элемент задержки подключен к выходу первого элемента задержки, выход блока выбора канала соединен с входами шифратора адреса, состоящего из : диодной матрицы, выходы которого подключены к входам регистра. 2. Устройство по п. 1, о т л и ч а ющ е е с я тем, что в.нем блок выбора , канала состоит .из fj входных элементов И и элемента НЕ, ( Ц -2) элементов запрета, (f}-) выходных элементов И, f-и вход блока соединен с перйым входов / -го входного элемента и, выход каждого 4 -го входного элемента И, где / 2, ..., П , соединен с первым входом ( i - 1)-го выходного элемента И и с управляющим входом ( -1)-го элемента запрета, выход i -го элемента подключен к информационному входу ( + 1)-го элемента запрета и к второму входу J -го выходного элемента И, выход первого входного, элемента И соединен с первым выходом узла и через элемент НЕ .подключен к первому входу первого выходного элемента И и к информационному

7 9646318

входу первого элемента запрета, выход 1. Авторское свидетельство СССР

казадо1ч { -го выходного элемента И 758142, кл. Q 06 F 0/О4, 1978.

единен с (ч -И)-ым выходом узла.2. Юэп И. К. Устройство для последовательной побитовой максимизашш и

Источники информации,5 сортировки. ТИИЭР, 1980, т. 68, № 2,

принятые во внимание при экспертизес, 116-117 (прототип).

Авторы

Даты

1982-10-07—Публикация

1981-01-19—Подача