Изобретение относится к вычислительной и измерительной технике и может быть использовано для анализа случайных процессов. .

Целью изобретения является повы-f шение точности вычисления оценок корреля ционных функций и увеличение функциональных возможностей анализатора.

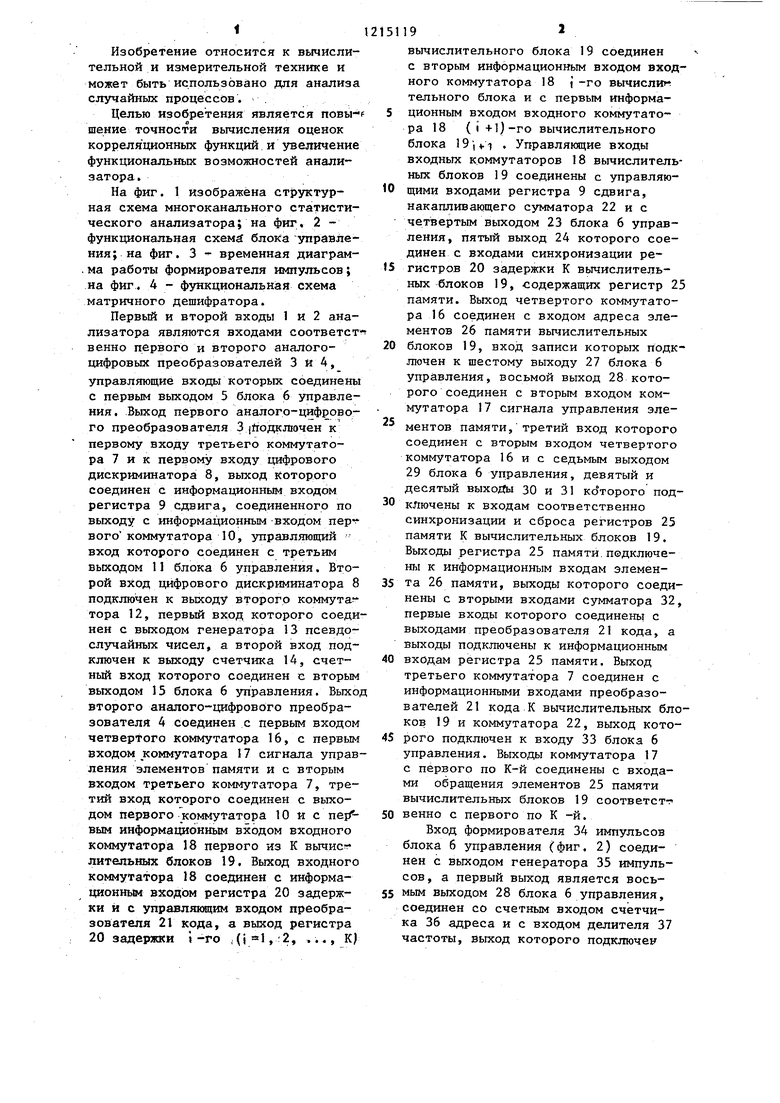

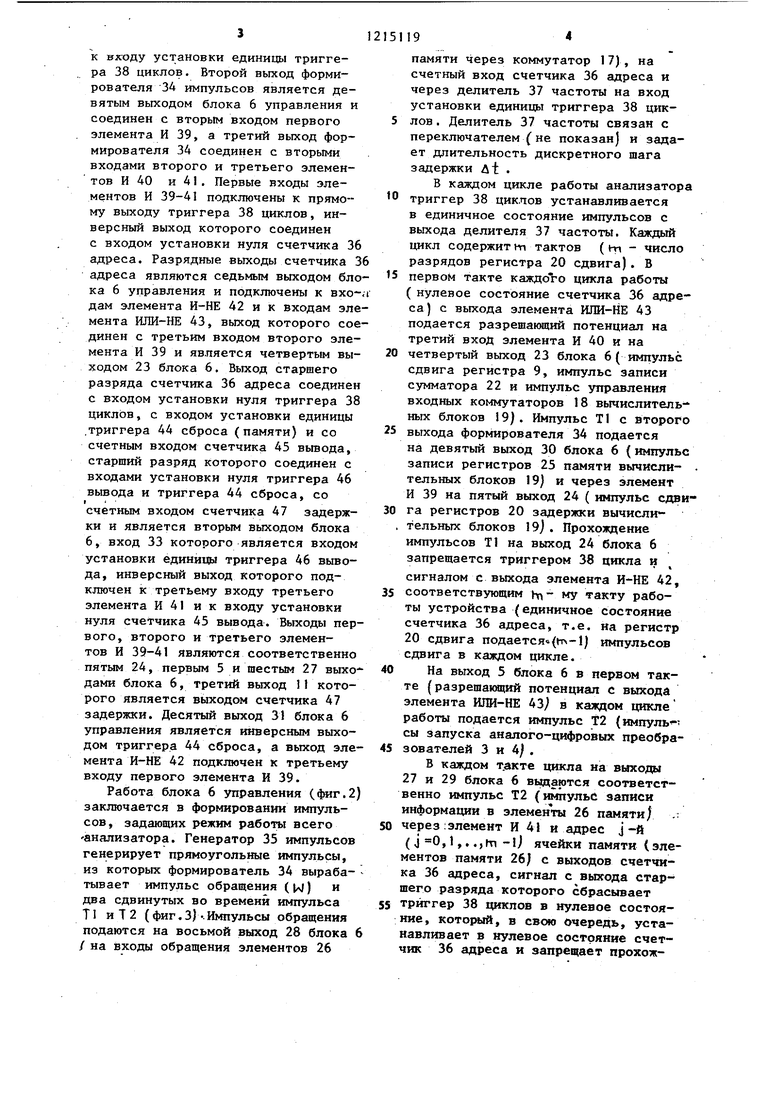

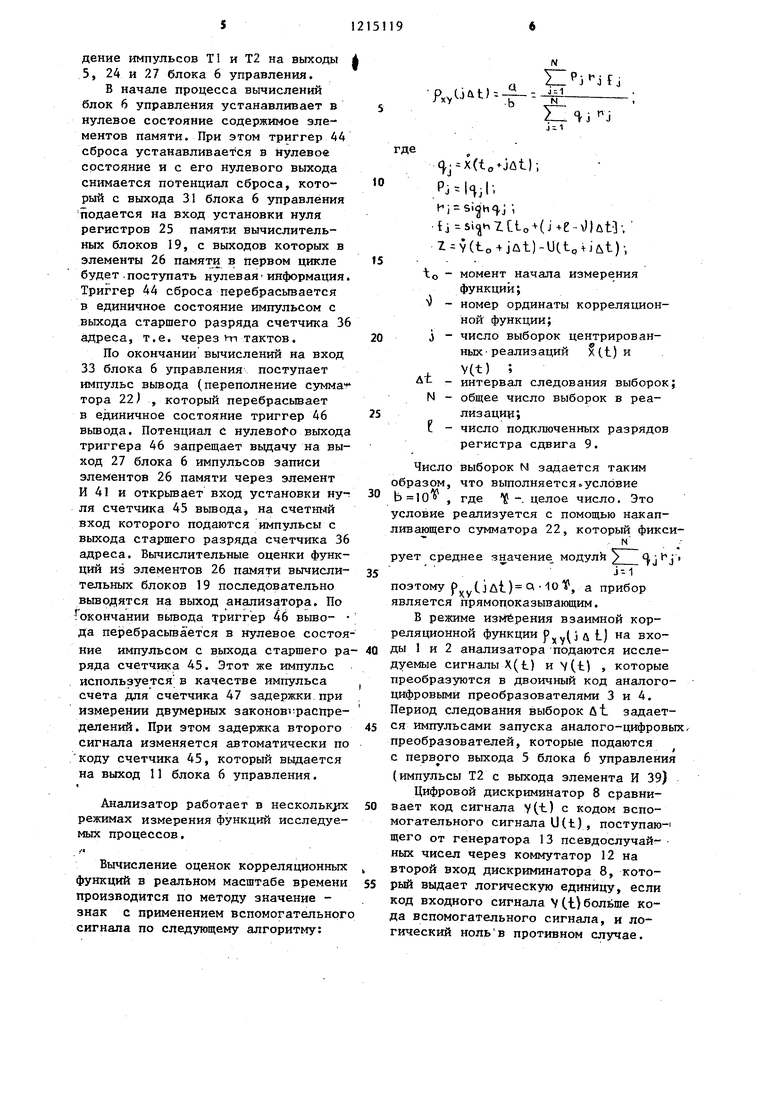

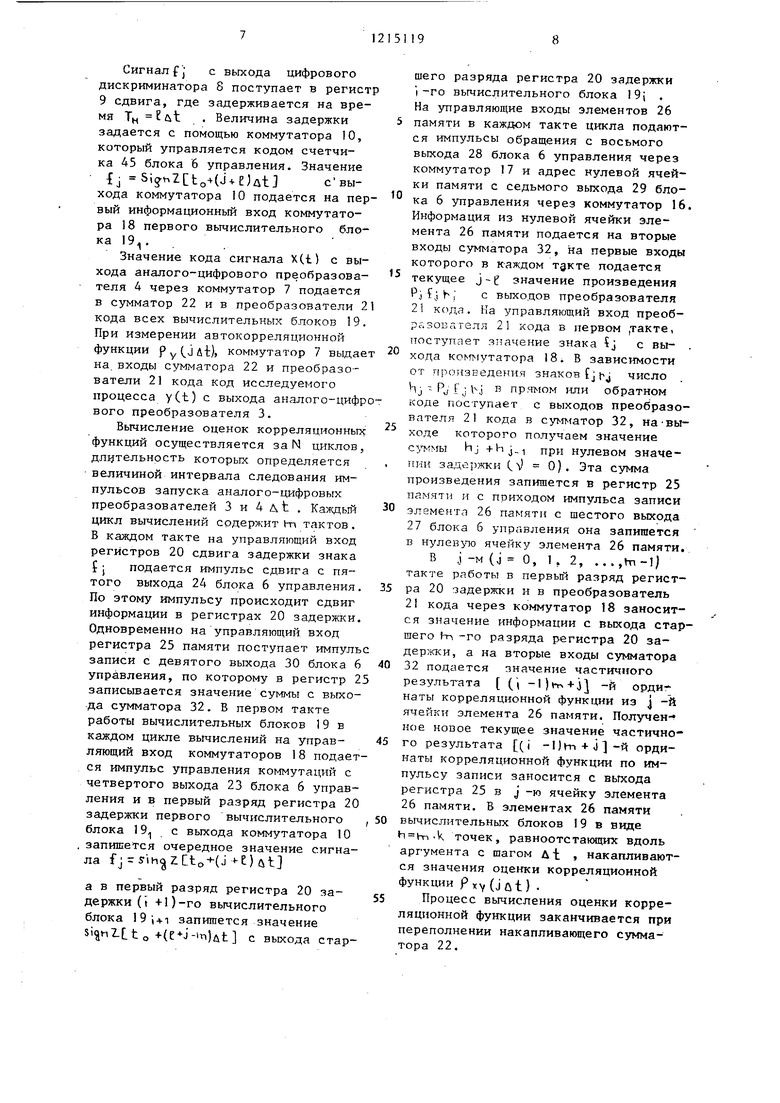

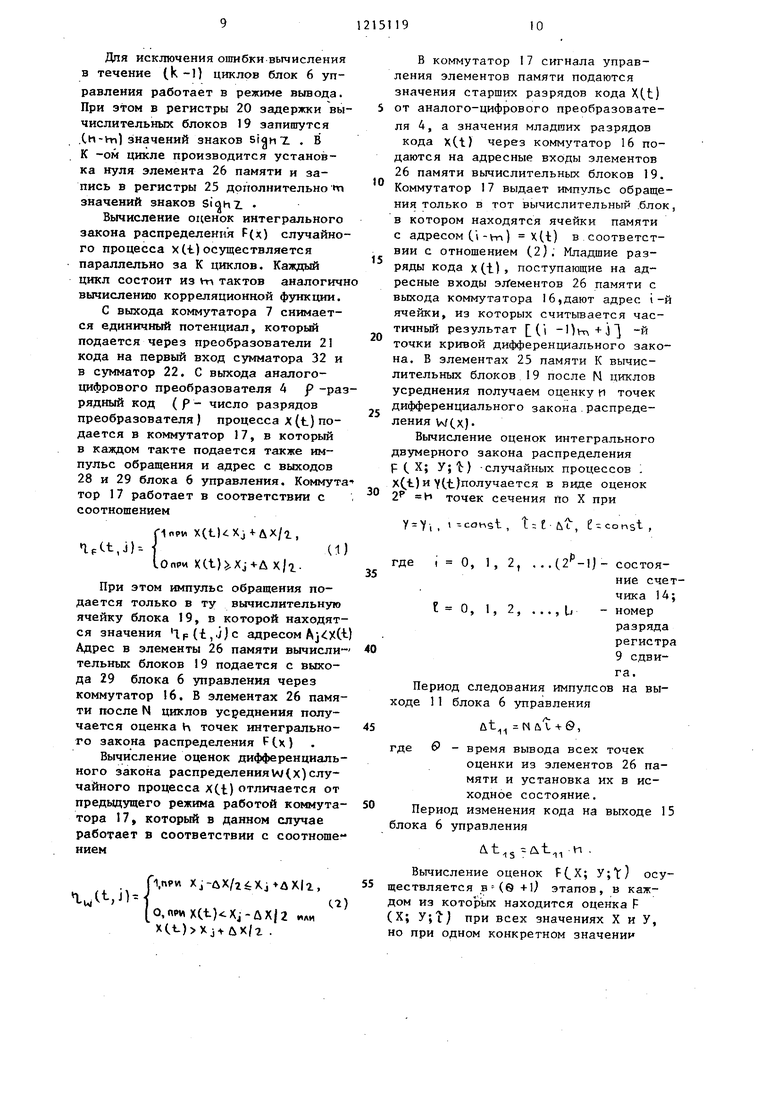

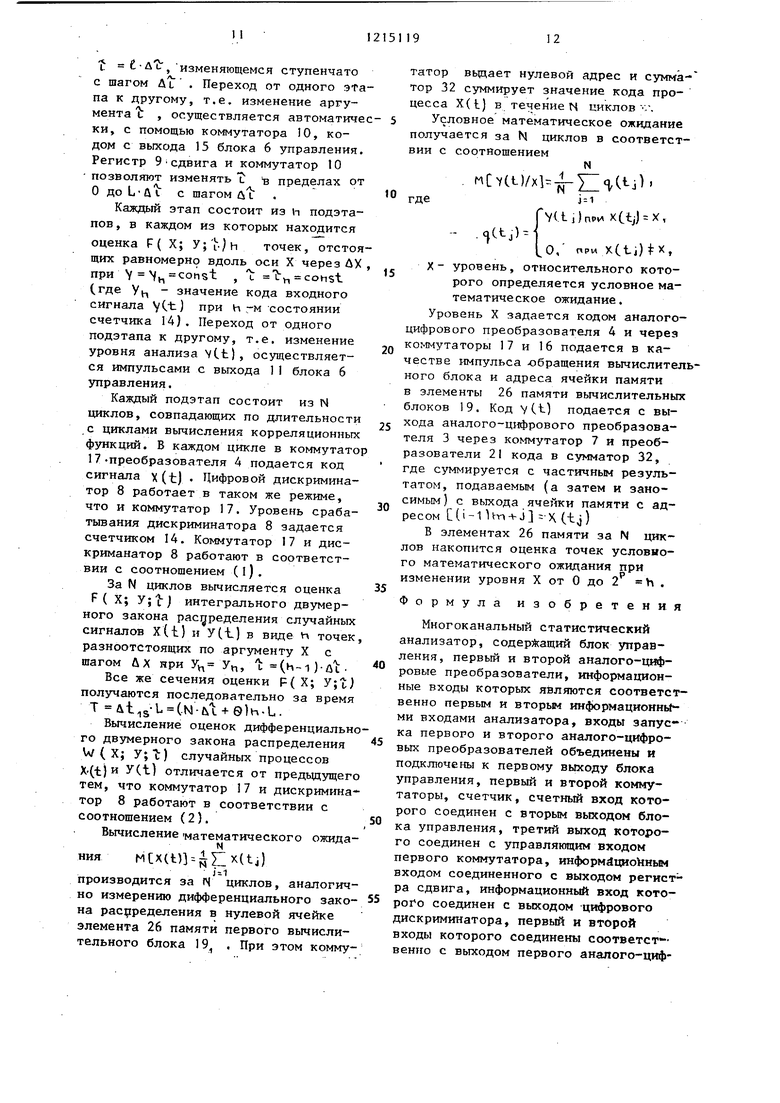

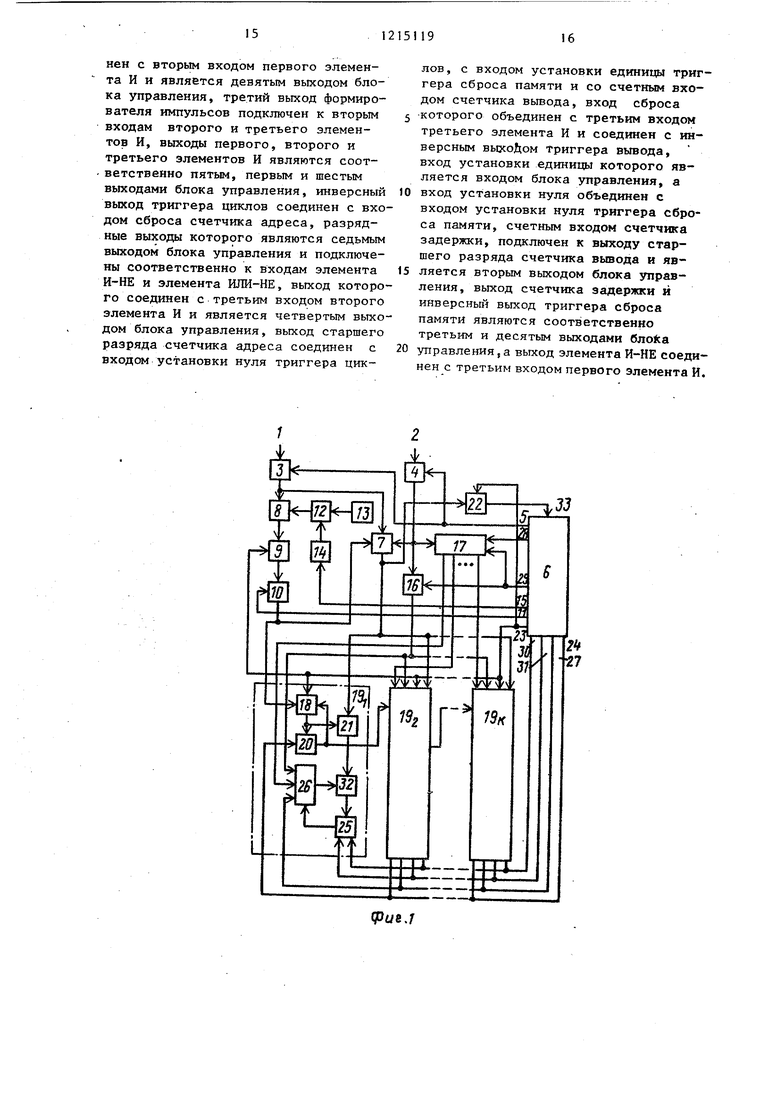

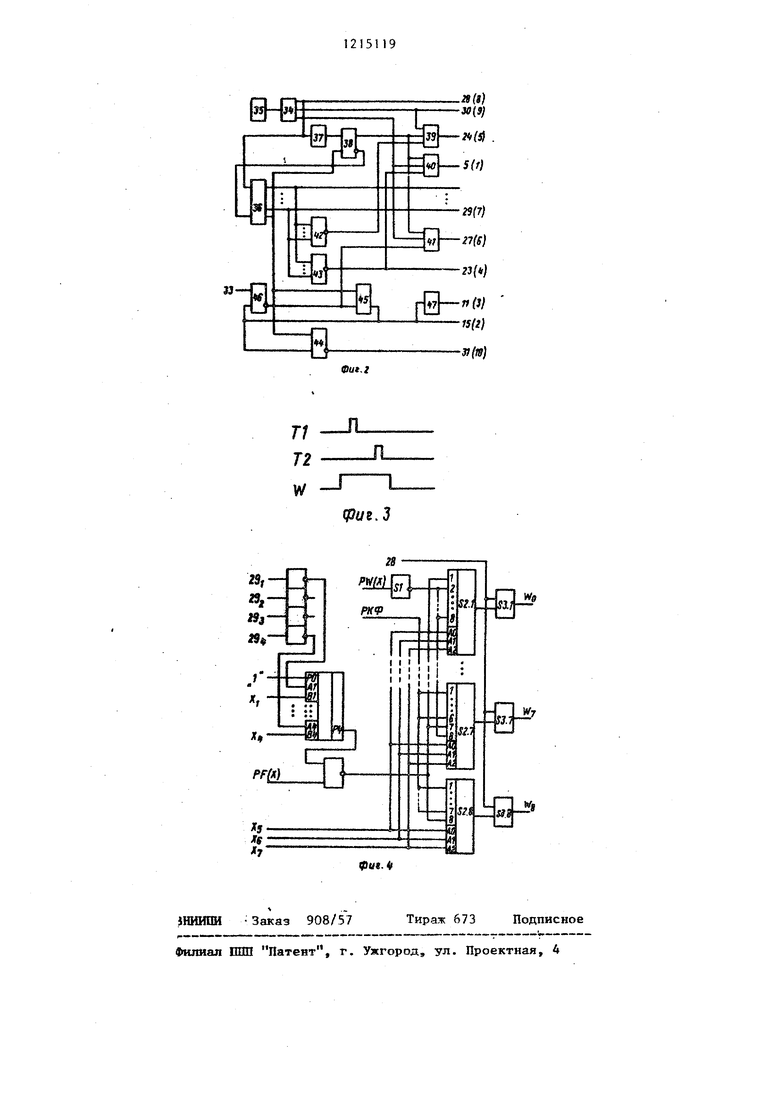

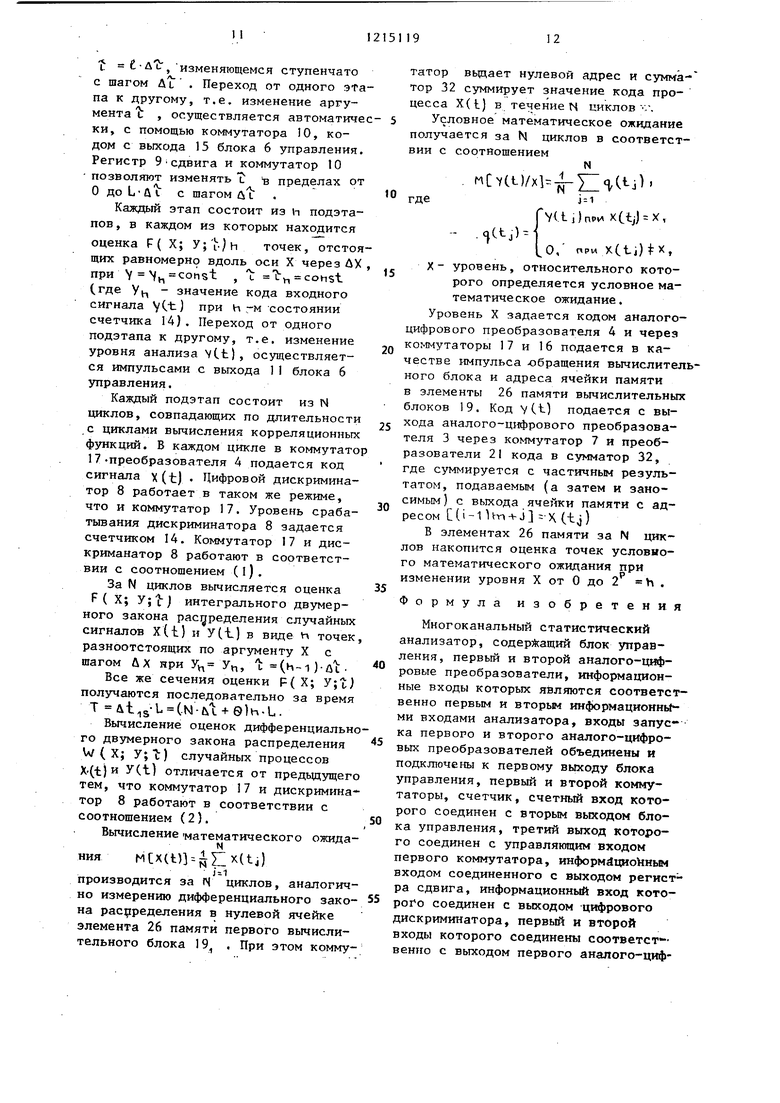

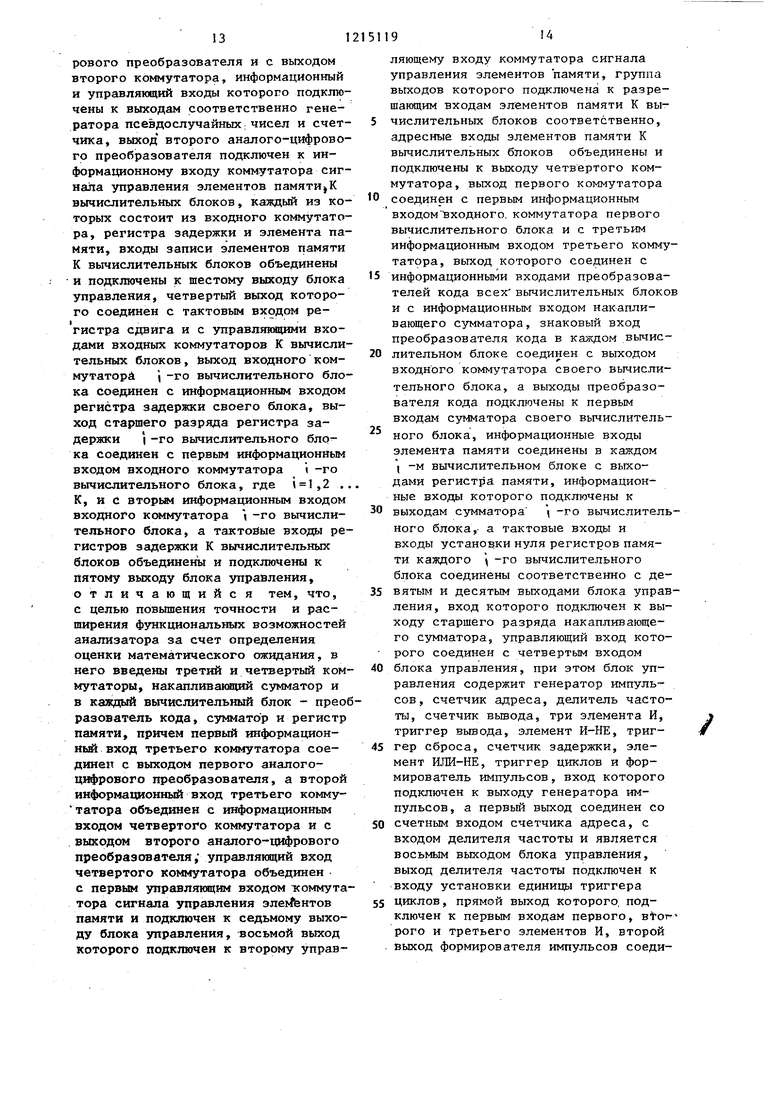

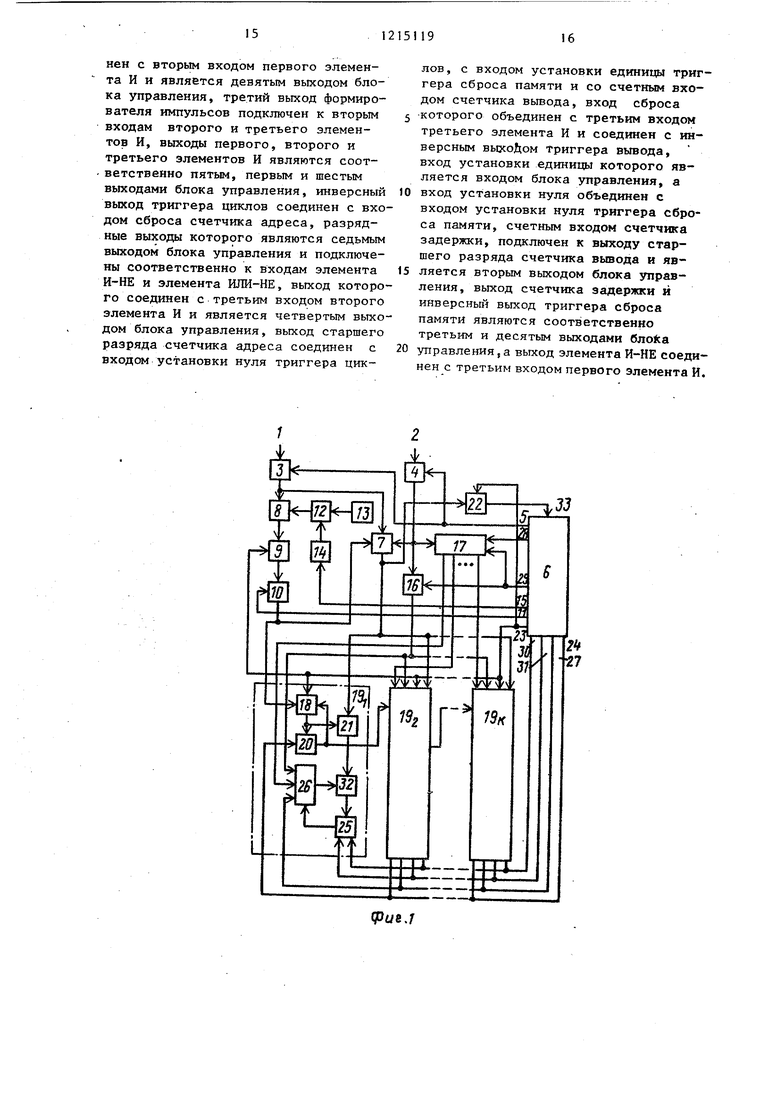

На фиг. 1 изображена структурная схема многоканального статистического анализатора; на фиг. 2 - функциональная схемй блока управления ; на фиг. 3 - временная диаграм- . на работы формирователя импульсов; на фиг. 4 - Фзгнкциональная схема матричного дешифратора.

Первый и второй входы 1 и 2 анализатора являются входами соответст венно первого и второго аналого- цифровых преобразователей 3 и 4, управляющие входы которых соединены с первым выходом 5 блока 6 управления. Выход первого аналого-цифрового преобразователя 3 (подключен к первому входу третьего коммутатора 7 и к первому входу цифрового дискриминатора 8, выход которого соединен с информационным входом регистра 9 сдвига, соединенного по выходу с информационным -входом пер- вого коммутатора 10, згаравляющий вход которого соединен с третьим выходом 11 блока 6 управления. Второй вход цифрового дискриминатора 8 подключен к выходу второго коммута - тора 12, первый вход которого соединен с выходом генератора 13 псевдослучайных чисел, а второй вход подключен к выходу счетчика 14, счетный вход которого соединен G вторым выходом 15 блока 6 управления. Выхо второго аналого-цифрового преобразователя 4 соединен с первым входом четвертого коммутатора 16, с первым входом коммутатора 17 сигнала управления элементов памяти и с вторым входом третьего коммутатора 7, третий вход которого соединен с выходом первого коммутатора 10 и с вым информационным входом входного коммутатора 18 первого из К вычис - лительиых блоков 19. Выход входного коммутатора 18 соединен с информа- ционнь«м входом регистра 20 задержки и с управляняцим входом преобразователя 21 кода, а выход регистра 20 задержки «-го ,((1,:2, ..., К)

25

2151192

вычислительного блока 19 соединен с вторым информационным входом входного коммутатора 18 J-го вычисли тельного блока и с первым информа5 ционным входом входного коммутатора 18 (i +1)-го вычислительного блока 19 | V1 . Управлякяцие входы входных коммутаторов 18 вычислительных блоков 19 соединены с управляю 0 щими входами регистра 9 сдвига, накапливающего сумматора 22 и с четвертым выходом 23 блока 6 управления, пятый выход 24 которого соединен с входами синхронизации ре15 гистров 20 задержки К вычислительных блоков 19, содержащих регистр 25 памяти. Выход четвертого коммутатора 16 соединен с входом адреса элементов 26 памяти вычислительных

20 блоков 19, вход записи которых подключен к шестому выходу 27 блока 6 управления, восьмой выход 28 которого соединен с вторым входом коммутатора 17 сигнала управления элементов памяти, третий вход которого соединен с вторым входом четвертого коммутатора 16 и с седьмым выходом 29 блока 6 управления, девятый и десятый выходы 30 и 31 которого подключены к входам соответственно синхронизации и сброса регистров 25 памяти К вычислительных блоков 19. Выходы регистра 25 памяти.подключены к информационным входам элемен35 та 26 памяти, выходы которого соединены с вторыми входами сумматора 32, первые входы которого соединены с выходами преобразователя 21 кода, а выходы подключены к информационным

40 входам регистра 25 памяти. Выход третьего коммутатора 7 соединен с информационными входами преобразователей 21 кода К вьгаислительных блоков 19 и коммутатора 22, выход кото45 рого подключен к входу 33 блока 6 управления. Выходы коммутатора 17 с первого по К-й соединены с входами обращения элементов 25 памяти вычислительных блоков 19 соответстгг

50 венно с первого по К-й.

Вход формирователя 34 импульсов блока 6 управления (фиг. 2) соединен с выходом генератора 35 импульсов, а первый выход является вось55 мым выходом 28 блока 6 управления, соединен со счетньм входом счетчика 36 адреса и с входом делителя 37 частоты, выход которого подключен

30

входу установки единицы триггера 38 циклов. Второй выход формирователя ЗА импульсов является деятым выходом блока 6 управления и соединен с вторым входом первого 5 элемента И 39, а третий выход формирователя 34 соединен с вторыми входами второго и третьего элемен- тов И 40 и 41. Первые входы элементов И 39-41 подключены к прямо- му выходу триггера 38 циклов, инверсный выход которого соединен с входом установки нуля счетчика 36 адреса. Разрядные выходы счетчика 36 адреса являются седьмым выходом бло- ка 6 управления и подключены к дам элемента И-НЕ 42 и к входам элемента ИЛИ-НЕ 43, выход которого соединен с третьим входом второго элемента И 39 и является четвертым вы- 20 ходом 23 блока 6. Выход старшего разряда счетчика 36 адреса соединен с входом установки нуля триггера 38 циклов, с входом установки единицы триггера 44 сброса (памяти) и со 5 счетным входом счетчика 45 вывода, старший разряд которого соединен с входами установки нуля триггера 46 вывода и триггера 44 сброса, со счетным входом счетчика 47 задерж- 0 ки и является вторым выходом блока 6, вход 33 которого является входом установки единицы триггера 46 вывоа, инверсный выход которого подключен к третьему входу третьего 35 элемента И 41 и к входу установки нуля счетчика 45 вывода. Выходы первого, второго и третьего элементов И 39-41 являются соответственно пятым 24, первым 5 и шестым 27 выхо 40 дами блока 6, третий выход 1I которого является выходом счетчика 47 задержки. Десятый выход 31 блока 6 управления является инверсным выходом триггера 44 сброса, а выход эле- 45 мента И-НЕ 42 подключен к третьему входу первого элемента И 39.

Работа блока 6 управления (фиг.2) заключается в формировании импульсов, задающих режим работа всего 50 анализатора. Генератор 35 импульсов генерирует прямоугольные импульсы, из которых формирователь 34 выраба- - тывает импульс обращения () и два сдвинутых во времени импульса 55 TI иТ2 (фиг, 3).Импульсы обращения подаются на восьмой выход 28 блока 6 на входы обращения элементов 26

памяти через коммутатор 17), на счетный вход счетчика 36 адреса и через делитель 37 частоты на вход установки единицы триггера 38 циклов . Делитель 37 частоты связан с переключателем (не показан) и задает длительность дискретного шага задержки Д1 .

В каждом цикле работы анализатор триггер 38 циклов устанавливается в единичное состояние импульсов с выхода делителя 37 частоты. Каждый цикл содержит нп тактов ( ип - число разрядов регистра 20 сдвига). В первом такте каждо го цикла работы ( нулевое состояние счетчика 36 адреса) с выхода элемента ИЛИ-НЕ 43 подается разрешающий потенциал на третий вход элемента И 40 и на четвертый выход 23 блока 6 ( импульс сдвига регистра 9, импульс записи сумматора 22 и импульс управления входных коммутаторов 18 вычислитель ных блоков 19). Импульс Т1 с второг выхода формирователя 34 подается на девятый выход 30 блока 6 (импуль записи регистров 25 памяти вычислительных блоков 19) и через элемент И 39 на пятый выход 24 ( импульс сдвга регистров 20 задержки вычислительных блоков 19J. Прохождение импульсов Т1 на выход 24 блока 6 запрещается триггером 38 цикла и

сигналом с выхода элемента И-НЕ 42, соответствующим hi - му такту работы устройства (единичное состояние счетчика 36 адреса, т.е. на регистр 20 сдвига подается((тч-1) импульсов сдвига в каждом цикле.

На выход 5 блока 6 в первом такте (разрешакиций потенциал с выхода элемента ИЛИ-НЕ 43 в каждом цикле работы подается импульс Т2 (импуль - сы запуска аналого-цифровых преобразователей 3 и 4) .

В каждом т.акте цикла иа выхода 27 и 29 блока 6 выдаются соответственно импульс Т2 (импульс записи информации в элементы 26 памяти/ . через :элемент И 41 н адрес j-и (,l,..,hn -l) ячейки памяти (элементов памяти 26) с выходов счетчика 36 адреса, сигнал с выхода старшего разряда которого сбрасывает триггер 38 цикпов в нулевое состояние, который, в свою очередь, устанавливает в нулевое состояние счетчик 36 адреса и запрещает прохождение импульсов Т1 и Т2 на выходы А 5, 24 и 27 блока 6 управления.

В начале процесса вычислений блок 6 управления устанавливает в нулевое состояние содержимое элементов памяти. При этом триггер 4А сброса устанавливается в нулевое состояние и с его нулевого выхода снимается потенциал сброса, кото- рый с выхода 31 блока 6 управления подается на вход установки нуля регистров 25 памяти вычислительных блоков 19, с выходов которых в элементы 26 памяти в первом цикле будет .поступать нулевая информация. Триггер 44 сброса перебрасывается в единичное состояние импульсом с выхода старшего разряда счетчика 36 адреса, т.е. через t-n тактов.

По окончании вычислений на вход 33 блока 6 управления поступает импульс вывода (переполнение суммам тора 22) , который перебрасывает в единичное состояние триггер 46 вьшода. Потенциал с нулевою выхода триггера 46 запрещает вьщачу на выход 27 блока 6 импульсов записи элементов 26 памяти через элемент И 41 и открывает вход установки ну- ля счетчика 45 вьтода, на счетный вход которого подаются импульсы с выхода старшего разряда счетчика 36 адреса. Вычислительные оценки функций из элементов 26 памяти вычисли- тельных блоков 19 последовательно выводятся на выход анализатора. По окончании вьгеода триггер 46 вьюо- да перебрасьгаается в нулевое состояние импульсом с выхода старшего ра ряда счетчика 45. Этот же импульс используется в качестве импульса счета для счетчика 47 задержки, при измерении двзгмерных законовтфаспре- делений. При этом задержка второго сигнала изменяется автоматически по коду счетчика 45, который выдается на выход 11 блока 6 управления.

1

Анализатор работает в нескольк гх режимах измерения функций исследуемых процессов.

,ч

Вычисление оценок корреляционных функций в реальном масштабе времени производится по методу значение - знак с применением вспомогательног сигнала по следующему алгоритму:

- .b N

j-1

J

де

();

..i .

,

fj Si лZetoЧЬE-).

l-Y(to4Jat)-UCtptJut)to - момент начала измерения функций;

- номер ординаты корреляционной функции;

j - число выборок центрированных реализаций X(t) и

vet) ;

интервал следования выборок; общее число выборок в реализации;

число подключенных разрядов регистра сдвига 9.

At N

е Число выборок N задается таким образом, что выполняется условие , где -. целое число. Это условие регшизуется с помощью накапливающего сумматора 22, который фикси. N

рует среднее значение модул У .t

. J-1 поэтому р УСJAt) 0-10 Y, а прибор является прямопоказывающим.

В режиме измерения взаимной корреляционной функции Pxy(j л i) на входы 1 и 2 анализатора подаются исследуемые сигналы X(t) и v(t) , которые преобразуются в двоичный код аналого- цифровыми преобразователями 3 и 4. Период следования выборок ut. задается импульсами запуска аналого-цифровы преобразователей, которые подаются с первого выхода 5 блока 6 управления (импульсы 12 с выхода элемента И 39)

Цифровой дискриминатор 8 сравнивает код сигнала V(t) с кодом вспомогательного сигнала U(t) , поступаю- щего от генератора 13 псевдослучай ных чисел через коммутатор 12 на второй вход дискриминатора 8, который выдает логическую единицу, если код входного сигнала V(t)болбше кода вспомогательного сигнала, и логический ноль в противном случае.

Сигнал fj с выхода цифрового дискриминатора 8 поступает в регист 9 сдвига, где задерживается на время Т ut . Величина задержки задается с помощью коммутатора 10, который управляется кодом счетчика 45 блока 6 управления. Значение fj SijviZ to-(J+E)AtJ с вы- хода коммутатора 10 подается на пер вый информационный вход коммутатора 18 первого вычислительного блока 19,

Значение кода сигнала X(t) с выхода аналого-цифрового преобразова- теля 4 через коммутатор 7 подается в сумматор 22 и в преобразователи 2 кода всех вычислительных блоков 19. При измерении автокорреляционной функции py(JAi:), коммутатор 7 вьщае на. входы сумматора 22 и преобразователи 21 кода код исследуемого процесса yCt) с выхода аналого-цифрвого преобразователя 3.

Вычисление оценок корреляционных функций осуществляется за N циклов, длительность которых определяется величиной интервала следования импульсов запуска аналого-цифровых преобразователей 3 и 4 At , Каходьй цикл вычислений содержит hn тактов. В каждом такте на управляющий вход регистров 20 сдвига задержки знака f j подается импульс сдвига с пятого выхода 24 блока 6 управления. По этому импульсу происходит сдвиг информации в регистрах 20 задерж1 и. Одновременно на управляющий вход регистра 25 памяти поступает импуль записи с девятого выхода 30 блока 6 управления, по которому в регистр 2 записывается значение суммы с выхода сумматора 32. В первом такте работы вычислительных блоков 19 в каждом цикле вычислений на управ- ляющий вход коммутаторов 18 подается импульс управления коммутаций с четвертого выхода 23 блока 6 управления и в первый разряд регистра 20 задержки первого вычислительного блока 19 с выхода коммутатора 10 , запишется очередное значение сигнала fj s: ih Z :to+(j E)ut

а в первый разряд регистра 20 задержки (t +1)-го вычислительного блока 19, + 1 запишется значение +(,)ut с выхода стар

5

5

5 0 5

0

5

шего разряда регистра 20 задержки 1-го вычислительного блока 9| . На управляющие входы элементов 26 памяти в каждом такте цикла подаются импульсы обращения с восьмого выхода 28 блока 6 управления через коммутатор 17 и адрес нулевой ячейки памяти с седьмого выхода 29 блока 6 управления через коммутатор 16. Информация из нулевой ячейки элемента 26 памяти подается на вторые входы сумматора 32, на первые входы которого в каждом тдкте подается текущее значение произведения Pjfjh; с вьпсодов преобразователя 21 кода. На управляющий вход преоб- разовсягеля 21 кода в первом ,такте, поступает значение знака ij с вы- . хода коммутатора 18 В зависимости от проязведеиия знаков fj число hj-Pjfj J в пр.чмом или обратном коде поступает с выходов преобраэо- вателя 21 кода в сум {атор 32, на-выходе которого полз чаем значение с:,тшы hj при нулевом значении заде1)жки (,V 0). Эта сумма произведения запишется в регистр 25 памяти и с приходом импульса записи элемента 26 памяти с шестого выхода 27 блока б управления она запишется в нулев по ячейку элемента 26 памяти,

В j -м (J 0, 1 , 2, ...,hn-l| такте работы в первый разряд регистра 20 задержки и в преобразователь 21 кода через коммутатор 18 заносится значение информации с выхода старшего -п -го разряда регистра 20 задержки, а на вторые входы сумматора 32 подается значение частичного результата ( -и ординаты корреляционной функции из j -и ячейки элемента 26 памяти. Получен- ное новое текущее значение частичного результата (i -I)и +j -и ординаты корреляционной функции по импульсу записи заносится с выхода регистра 25 в j -ю ячейку элемента 26 памяти. В элементах 26 памяти вычислительных блоков 19 в виде точек, равноотстающих вдоль аргумента с шагом Д t , накапливаются значения оценки корреляционной функции Pxv(Jut) .

Процесс вычисления оценки корреляционной функции заканчивается при переполнении накапливающего сумматора 22.

Для исключения ошибки вычисления в течение (К -1) циклов блок 6 управления работает в режиме вывода. При этом в регистры 20 задержки вычислительных блоков 19 запишутся .Си-Vn) значений знаков . . В К -ом цикле производится установка нуля элемента 26 памяти и запись в регистры 25 дополнительно ип значений знаков SiahT.

Вычисление оценок интегрального закона распределения F(x) случайного процесса x(-t) осуществляется параллельно за К циклов. Каждый цикл состоит из vr тактов аналогичн вычислению корреляционной функции.

С выхода коммутатора 7 снимается единичный потенциал, который подается через преобразователи 21 кода на первый вход сумматора 32 и в сумматор 22. С выхода аналого- цифрового преобразователя 4 р -разрядный код (р- число разрядов преобразователя) процесса Л (t)подается в коммутатор 17, в который в каждом такте подается также импульс обращения и адрес с выходов 28 и 29 блока 6 управления. Коммута тор 17 работает в соответствии с соотношением

ПОРИ XCt)iXj -&X/l,

IpCtj)-- j(1

lOnPM XCt) x/lПри этом импульс обращения подается только в ту вычислительную ячейку блока 19, в которой находятся значения lF(t,j)c адресом Адрес в элементы 26 памяти вычисли™ тельных блоков 19 подается с выхода 29 блока 6 управления через коммутатор 16. В элементах 26 памяти после N циклов усреднения получается оценка h точек интегрального закона распределения F Сх )

Вычисление оценок дифференциального закона распределенияW(x)случайного процесса XCt) отличается от предыдущего режима работой коммутатора 17, который в данном случае работает в соответствии с соотношением

fl.npva Xj-uX/2 Xi dX|i, U 0,nPMXCt)Xj-UX|2 лм XCi-)Xj- -uX/z .

o

5

В коммутатор 17 сигнала управления элементов памяти подаются значения старших разрядов кода X(.t) 5 от аналого-цифрового преобразователя 4, а значения младших разрядов

кода x(t) через коммутатор 16 подаются на адресные входы элементов 26 памяти вычислительных блоков 19. Коммутатор 17 выдает импульс обращения только в тот вычислительный .блок, в котором находятся ячейки памяти с адресом (.1-vn) X( t) в соответствии с отношением (2). Младшие разряды кода x(t) поступающие на адресные входы эл ементов 26 памяти с выхода коммутатора 16,дают адрес i-и ячейки, из которых считьшается частичный результат (i -l i-n+J й точки кривой дифференциального закона. В элементах 25 памяти К вычислительных блоков 19 после N циклов усреднения получаем оценку и точек дифференциального закона распределения W(,X)

Вычисление оценок интегрального двумерного закона распределения р ( X; y;t-) -случайных процессов . X{,t.) и у()получается в виде оценок 0 2Р и точек сечения по X при

У:,, 1--const, t;t Л, е const,

5

где t О, 1, 2, ..,(2-1)- состояние счетчика 14; , 1, 2, ...,Ь - номер

разряда регистра 9 сдвига.

Период следования импулсов на выходе 11 блока 6 управления

ut Nut-v6 ,

где & - время вывода всех точек

оценки из элементов 26 памяти и установка их в исходное состояние, Период изменения кода на выходе 15

блока 6 управления

Д1,з-л1,,.н.

Вычисление оценок У;Т/ осу- ществляется в (0 +1J этапов, в каждом из которых находится оценка F (X; y;tj при всех значениях X и У, но при одном конкретном значении

г

e-At

, изменяющемся ступенчато

с шагом AL . Переход от одного этапа к другому, т.е. изменение аргумента t , осуществляется автоматичес ки, с помощью коммутатора 10, кодом с выхода 15 блока 6 управления. Регистр 9сдвига и коммутатор 10 позволяют изменять t в пределах от О до L а I с шагом u t .

Каждый этап состоит из h подэта- пов, в каждом из которых находится

оценка F( X; У; Ь)н точек, отстоящих равномерно вдоль оси X через ЛХ при V V, , tYi const (где У( - значение кода входного сигнала ) при и-м состоянии счетчика 14). Переход от одного подэтапа к другому, т.е. изменение уровня анализа vCt), осуществляется импульсами с выхода 11 блока 6 управления.

Каждый подэтап состоит из N циклов, совпадающих по длительности с циклами вычисления корреляционных Фзшкций. В каждом цикле в коммутатор 17-преобразователя 4 подается код сигнала y(t) Цифровой дискриминатор 8 работает в таком же режиме, что и коммутатор 17. Уровень сраба- тьгоания дискриминатора 8 задается счетчиком 14. Коммутатор 17 и дис- криманатор 8 работают в соответствии с соотношением (l).

За N циклов вычисляется оценка F ( X; yjt) интегрального двумерного закона распределения случайных сигналов X(t) и У(1) в виде н точек равноотстоящих по аргументу X с шагом ЛХ нри У, УН, L()-UL.

Все же сечения оценки F( X; У,1) получаются последовательно за время

Т л1,з-ь (м-л1 + 0)ь.и.

Вычисление оценок дифференциального двумерного закона распределения W { X; y;t) случайных процессов X.(t) и y(t) отличается от предьщзоцего тем, что коммутатор 17 и дискримина тор 8 работают в соответствии с соотношением (2).

Вьгчгисление математического ожида- N

НИН Mcx((tj)

производится за N циклов, аналогично измерению дифференциального зако- на распределения в нулевой ячейке элемента 26 памяти первого вычислительного блока 19, . При этом коммутатор выдает нулевой адрес и сумматор 32 суммирует значение кода процесса X(t) в течение ГЧ циклов :.Условное математическое ожидание получается за N циклов в соответствии с соотношением

0

°

0

5

1

N

где

MCva),ctjb

.Ctj) V(t j)npn xCtjj X,

0, rtPH xCti)X,

X- уровень, относительного которого определяется условное математическое ожидание. Уровень X задается кодом аналого- цифрового преобразователя 4 и через коммутаторы 17 и 16 подается в качестве импульса обращения вычислительного блока и адреса ячейки памяти в элементы 26 памяти вычислительных блоков 19. Код V(t) подается с выхода аналого-цифрового преобразователя 3 через коммутатор 7 и преобразователи 21 кода в сумматор 32, где суммируется с частичным результатом, подаваемым (а затем и заносимым ) с вькода ячейки памяти с ап- ресом C(i-lUn4-J ::-X(tj)

В элементах 26 памяти за N циклов накопится оценка точек условного математического ожидания при изменении уровня X от О до 2 h .

Формула изобретения

Многоканальный статистический анализатор, содержащий блок ления, первый и второй аналого-цифровые преобразователи, информационные входы которых являются соответственно первым и вторым информационнь - ми входами анализатора, входы запуска первого и второго аналого-цифровых преобразователей объединены и подключены к первому выходу блока управления, первый и второй коммутаторы, счетчик, счетный вход которого соединен с вторым выходом блока управления, третий выход которого соединен с управляющим входом первого коммутатора, информйциойным входом соединенного с выходом регистра сдвига, информационный вход которого соединен с выходом цифрового дискриминатора, первый и второй входы которого соединены соответст -- венно с выходом первого аналого-цифрового преобразователя и с выходом второго коммутатора, информационный и управляющий входы которого подключены к выходам соответственно генератора псевдослучайных; чисел и счетчика, выход второго аналого-цифрового преобразователя подключен к информационному входу коммутатора сигнала управления элементов памяти К вычислительных блоков, каждый из которых состоит из входного коммутатора, регистра задержки и элемента памяти, входы записи элементов памяти К вычислительных блоков объединены и подключены к шестому выходу блока управления, четвертый выход которого соединен с тактовым входом регистра сдвига и с управляющими входами входных коммутаторов К вычислительных блоков, йыход входного коммутатора I -го вычислительного блока соединен с информационным входом регистра задержки своего блока, выход старшего разряда регистра задержки I -го вычислительного блока соединен с первым информационным входом входного коммутатора i -го вычислительного блока, где ,2 . К, и с вторьм информационным входом входного кся мутатора -го вычислительного блока, а тактовые входы регистров задержки К вычислительных блоков объединены и подключены к пятому выходу блока управления, отличающийся тем, что, с целью повышения точности и расширения функциональных возможностей анализатора за счет определения оценки математического ожидания, в него введены третий и четвертый коммутаторы, накапливаиящй сумматор и в каждый вычислительный блок - преобразователь кода, сумматор и регистр памяти, причем первый информацион- ньй вход третьего коммутатора сое- дине1т с выходом первого аналого- цифрового преобразователя, а второй информационный вход третьего комму- Тагора объединен с информационньм входом четвертого коммутатора и с выходом второго аналого-цифрового преобразователя; управляияций вход четвертого коммутатора объединен с первым управляющим входом коммутатора сигнала управления памяти и подключен к седьмому выходу блока управления, восьмой выход которого подключен к второму управляющему входу коммутатора сигнала управления элементов памяти, группа выходов которого подключена к разрешающим входам элементов памяти К вычислительных блоков соответственно, адресные входы элементов памяти К вычислительных блоков объединены и подключены к выходу четвертого коммутатора, выход первого коммутатора

соединен с первым информационным входом входного, коммутатора первого вычислительного блока и с третьим информационным входом третьего коммутатора, выход которого соединен с

информационными входами преобразователей кода всех вычислительных блоков и с информационным входом накапливающего сумматора, знаковый вход преобразователя кода в каждом вычислительном блоке соединен с выходом входного коммутатора своего вычислительного блока, а выходы преобразователя кода подключены к первым входам сумматора своего вычислительного блока, информационные входы элемента памяти соединены в каждом ( -м вычислительном блоке с выходами регистра памяти, информационные входы которого подключены к

выходам сумматора -го вычислительного блока,- а тактовые входы и входы установки нуля регистров памяти каждого -го вычислительного блока соединены соответственно с девятым и десятым выходами блока управления, вход которого подключен к выходу старшего разряда накапливающего сумматора, управляющий вход кото- рого соединен с четвертым входом

блока управления, при этом блок управления содержит генератор импульсов, счетчик адреса, делитель частоты, счетчик вьшода, три элемента И, триггер вьшода, элемент И-НЕ, триггер сброса, счетчик задержки, элемент ИЛИ-НЕ, триггер циклов и формирователь импульсов, вход которого подключен к выходу генератора импульсов, а первьй выход соединен со

счетным входом счетчика адреса, с входом делителя частоты и является восьмым выходом блока управления, выход делителя частоты подключен к входу установки единицы триггера

циклов, прямой выход которого, подключен к первьм входам первого, Btor рого и третьего элементов И, второй выход формирователя импульсов соединен с вторым входом первого элемента И и является девятым выходом блока управления, третий выход формирователя импульсов подключен к вторым входам второго и третьего элементов И, выходы первого, второго и третьего элементов И являются соответственно пятым, первым и шестым выходами блока управления, инверсный выход триггера циклов соединен с входом сброса счетчика адреса, разрядные выходы которого являются седьмым выходом блока управления и подключены соответственно к входам элемента И-НЕ и элемента ИЛИ-НЕ, выход которого соединен с третьим входом второго элемента И и является четвертым выходом блока управления, выход старшего разряда счетчика адреса соединен с входом установки нуля триггера циклов , с входом установки единицы триггера сброса памяти и со счетным входом счетчика вьгоода, вход сброса

которого объединен с третьим входом третьего элемента И и соединен с инверсным выходом триггера вывода, вход установки единицы которого является входом блока управления, а

вход установки нуля объединен с

входом установки нуля триггера сброса памяти, счетным входом счетчика задержки, подключен к выходу старшего разряда счетчика вывода и является вторым выходом блока ления, выход счетчика задержки и инверсньй выход триггера сброса памяти являются соответственно третьим и десятым выходами

управления,а выход элемента И-НЕ соединен с третьим входом первого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Устройство для определения корреляционной функции | 1987 |

|

SU1501086A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Автокоррелятор | 1990 |

|

SU1833894A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Адаптивный кодирующий преобразователь стационарных случайных процессов | 1980 |

|

SU960846A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

Изобретение относится к вычислительной и измерительной технике и может быть использовано для анализа случайных процессов. Целью изобретения является повышение точности вычисления;оценок корреляционной функции и расширение функциональных возможностей за счет определения оценки математического и условного математического ожиданий. В анализатор введены третий и четвертый коммутаторы, блок фиксации среднего значения модуля и в каждый вычислительный блок - преобразователь кода, сумматор- .и регистр памяти. Анализатор позволяет измерять, кроме одномерных, и двумерные законы распределения, а также математическое и условное математичес кое ожидания, кроме того, определение корреляционных функций производится по методу значение - знак, что дает более высокую точность вычисления. 4 ил.

9JU87

.3

JHHHDH -Заказ 908/57

в илиал ШШ Патент, г. Ужгород, ул. Проектная, 4

Тираж 673

Подписное

| АНАЛИЗАТОР СЛУЧАЙНЫХ ПРОЦЕССОВ | 0 |

|

SU364944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-02-28—Публикация

1983-12-28—Подача