2. Коррелометр по п. 1, о т л ичающийся тем, что блок вычисления промежуточных сумм содержит сумматор, элемент памятиf дешифратор и счетчик, содержащий () разрядов, разрядные выходы которого соединены с соответствующими входами дешифратора, а выходы М младших разрядов и выход старшего разряда счетчика подключены к соответствующим входс1м адреса записи элемента памяти, вход синхронизации которого объединен с входом синхронизации счетчика и является входом синхронизации блока, выход старшего разряда счетчика подключен к соответствующему входу адреса чтения элемента памяти, остальные входы адреса чтения которого являются соответствующими входами адреса чтения блока, входы первой -группы выходов элемента пагляти подключены к соответствующим входам первой группы информационных, входов сумматора, выходы которого подключены, к соответствующим информационным входам . элемента памяти,. выходы второй группы выходов которого являются соответствующими выходами блока, вход управления режимом работы сумматора подключен к выходу дешифрато ра, а входы второй группы информационных входов являются соответствующими информационными входами блока;

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1982 |

|

SU1026144A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Многоканальный многомерныйцифРОВОй КОРРЕлОМЕТР | 1978 |

|

SU809199A1 |

| Многоканальный многомерный цифровой коррелометр | 1984 |

|

SU1187177A1 |

| Коррелятор | 1984 |

|

SU1180927A1 |

| Вероятностный коррелометр | 1978 |

|

SU942037A1 |

| Коррелометр | 1984 |

|

SU1171806A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для разделения коррелограмм | 1987 |

|

SU1432558A1 |

1МНОГОКАНАЛЬНЫЙ РЕЛЕЙНЫЙ КОРРЕЛСМЕТР, содержащий аналого-цифровой преобразователь, информационный вход которого является первым входом коррелоидатра, а вход синхронизации объединен с входе синхронизации первого регистра сдвига и подключен к выходу М-гр разряда счетчика, содержащего Iw+rn) разрядов (где т 1 f М - число отсчетов в i-м блоке, i 1,N), выход старшего разряда которого соединен с первым BXOJJOM синхронизации второгр .Р гистра сдвига, содержащего D ячеек, (где Ф - число ординат корреляционной функции), вход счетчика объединен с вторым входом синхронизации второго регистра сдвига и входом синхронизации сумматора и подключен к йыходу генератора импульсов , разрядные выходы старшей ячейки второго регистра сдвига подю1ючены к соответствующим входам первой группы входов первой ячейки, входы второй группы входов первой ячейки которого подключены к соответствующим разрядным выходам первого регистра сдвига, информационный вход которого подключен к выходу компаратора, вход которого является вторым входом коррелометра, о т л. и ч а ю щ и и с я тем, что, с целью повькиения быстродействия, в него введен блок вычисле(Л ния промежуточных сумм, инфop лaциoнные входы которого подключены к соответствующим разрядным выходам ангшого-цифрового преобразователя, а входы адреса чтения подключены к соответствующим разрядным выходам старшей ячейки второго регистра сдвига, вход синхронизации блока вычисления промежуточных сумм подключен к выходу генератора импульсов, а выходы подключены к соот,ветствующим информационным входам сумматора.

1

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для -построения многоканальных релейных коррелометров случайных стационарных эргодических сигналов.

Известен коррелометр, регшизующий релейный алгоритм.вычисления оценки взаимной корреляционной функции, содержащий линейно-частотный преобразователь, блок задержки, усилители-ограничители, элементы неоднозначности и накопители 13.

Однако сравнительно невысокое быстродействие этого коррелометра не позволяет исследовать высокочастотные сигналы.

Наиболее близким к предлагаемому по технической сущности и предлагаемому результату является устройство, содержащее аналого-цифровой преобразователь, информационный вход которого является первым входом коррелометра, управляющий вход аналого-цифрового преобразователя подключен к первому выходу блока управления, содержащего генератор импульсов и счетчик, а выход к первому входу дешифратора содержащего элементы И или ИЛИг второй вход которого подключен к выходу компаратора, первый - к входу блока фиксации среднеквадратического отклонения, а второй выход к входу сумматора, вход управления которого соединен с вторым выходом счетчяка, вход которого подключен к выходублока фиксации среднеквадратического отклонения, а третий выход - к первому входу компаратора второй вход которого является вторы входсял коррелс 4( 12.

Недостатком известного устройства является относительно низкое быстродействие, обусловленное последовательнУм порядком обработки данных. Цель изобретения - повышение быстродействия коррелометра, т.е. расширение частотного диапазона исследуBf.ttjx сигналов.

Указанная цель достигается тем,

iTO в многоканальный репейный коррелометр, содержшаий аналого-цифровой преобразователь, информационный вход которого является первъвл входом коррелометра, а вход синхронизации объединен с входом синхооннзации первого регистра сдвига и подключен к выходу М -го разряда с етчика, содержащего ) раэрядов (где М - число отсчетов в i-м блоке, i 1,,

выход старшего разряда, которого соединен с первым входом синхрони гацш второго регистра сдвига, содержащего D ячеек Ч где D -число Ординат корреляционной функции),

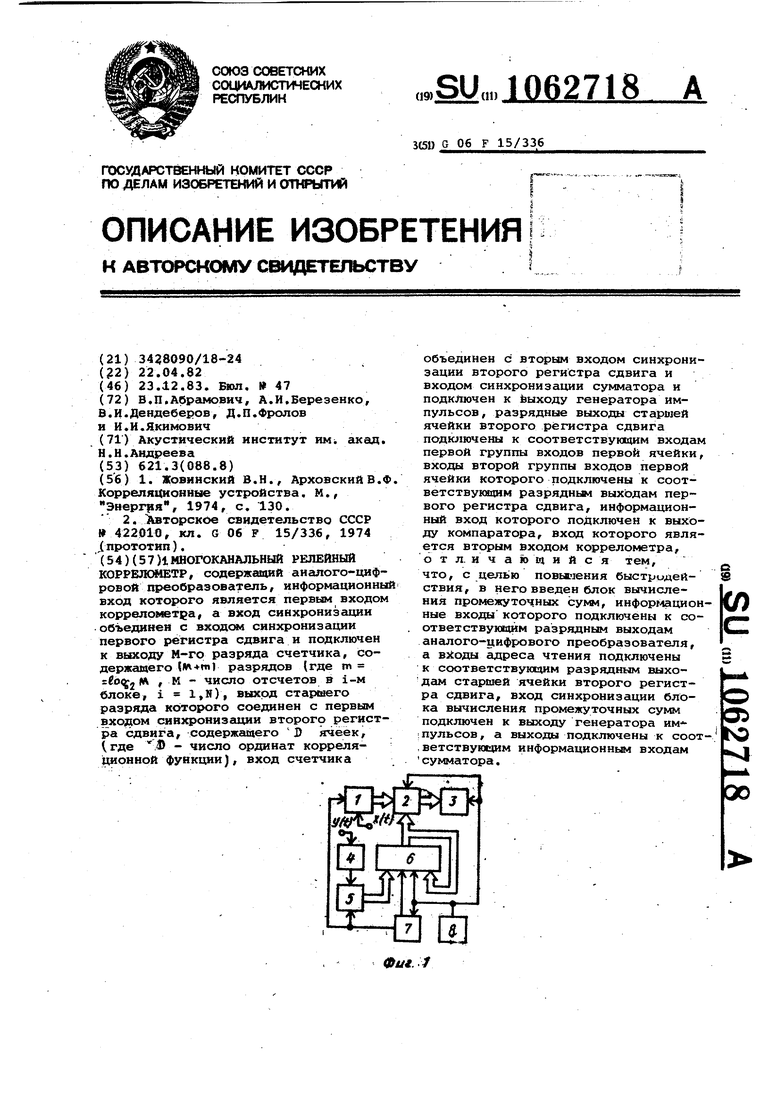

вход счетчика объединен с вторым входом синхронизации второго регистра сдвига и входом синхронизации сумматора и подключен к выходу генератора импульсов, разрядные выходы старшей ячейки второго регистра сдвига подключены к соответствую-щим входам первой группы входов первой ячейки, входы второй группы входов первой ячейки которого подключены к соответствукяцим разрядным выходам первого регистра сдвига, информационный вход которого подключен к выходу компаратора, вход которого явля«тся вторым входом коррёлометра, введен блок вычисления промежуточных сумм, инфс мационные входы которого подключены к соответ ствующим разрядным выходам аналогоцифрового преобразователя, а входы адцреса чтения подключены к соответствующим разрядным выходам старшей ячейки второго регистра сдвига, вхо синхронизации блока вычисления промежуточных сумм подключен к выходу генератора импульсов, а выходы подключены к соответствующим информа.ционным входам сумматора. Причем, блок вычисления промежуточных сумм содержит сумматор, элемент памяти и счетчик, содержащий ( + 1) разрядов, разрядные выходы которого соединены с соответ ствующими входами дешифратора, а выходы W младших разрядов и выход старшего разряда счетчика подключен к соответствугацим входам адреса записи элемента памяти, вход синхрони зации которого объединен с входом синхронизации счетчика и является входом синхронизации блока, выход старшего разряда счетчика подключен к соответствующему входу адреса чтения элемента памяти, осталд ные входы адреса чтения которого являют ся соответствукнцими входами адреса чтения блока, выходы первой груп пы выходов элемента памяти подключе ны к соответствующим входам первой группы информационных входов сумматора, выходы которого подключены к соответствующим информационным входам элемента памяти/ выходы второй груптш вых,одов которого являются соответствующими выходами блока вход управления режимом работы сумматора подю1ючен к выходу дешифратора, а входы второй группы инфор мационных входов являются соответст вующими информационными входами бло ка. На фиг. 1 изображена структурная схема многоканального релейного коррелометра; на фиг 2 - структурная схема блока вычисления промежуточных сумм. Коррелометр содержит аналого-циф ровой преобразователь (дцп 1, блок 2 вычисления промежуточных сум Ьумматсф 3, компаратор 4, первый 5 и второй 6 регистры сдвига, счет чик 7, генератор 8 импульсов,Блок 2 вычисления промежуточных сумм содер жит сумматор 9, дешифратор 10, элемент 11 памяти и счетчик 12. Коррелометр работает следующим образом... Входной случайный сигнал преобраэуется в АЦП 1 в двоичные многоразрядные числа с частотой f, равной частоте следования импульсов ТИ 1 выхода -Г9 разряда счетчика 7, содержащего ХЛ + fpi разряДОН, последовательность отсчетов входного сигнала разбиваетсяна блоки по М 2 чисел , где i ь 0,1,.,., (N-1) - номер блока, j О, 1,..., (М- 1) - номерЧисла в блоке. Из чисел каждого блока с номером i, поступающих с разрядных , выходов АЦП 1 на соответствующие входы одной из групп информационных входов су1л 1атора 9, за время прохождения М импульсов ТИ 1 в блоке 2 формируется 2 сумм №-1 я. ,Ч,-Пи,х,, где aj - зна,чения разрядов двоичного числа номера суммы А (а. ,а ,.., а г...« а4д L, А о, 1, ...«, ч , . . . , а |U i (- 1). , Частота f f2/2, где f2 частота выходных импульсов ТИ 2 генератора 8 импульсов. Импульсы ТИ 2 поступают на вход синхронизации элемента 11 памяти блока 2 вычисления промежуточных сумм и вход, счетчика 12, в котором формируется (М +П1+ 1)-разрядный двоичный код (0 I а,..., aj состоящий из трех частей: н младших разрядов равны, Л-номеру суммы 8д,;, разрящы , адц+,..., а;ц) j-номеру бтсче- та блока с i старший разРЯД3| Л О Ри i четном, ад, 1 при 1 нечетном. Для каждого значения Xjj число л поочередно принимает значения от О до ( 1) . В дешифраторе 10 формируется число а а а a,j. .. а,,.. .а которое поступает на вход упраВления режимом работы сумматора 9, работающего в режиме сложения, при aj 0, и в режиме вычитания при а 1. Число а- равно значению разряда с номером числа А . Элемент 11 памяти содержит ячеек памяти, разрядность которых соответствует максимальному значению сумл . На входы адреса з.аписи элемента 11 памяти поступает с выходов М млсщпжх разрядов и старшего разряда счетчика 12 («+ 1 -разрядный код (ао a,..., а.а.}, а на входы адреса чтени а (Ж f 1) -разряд||ый код, младшие М разрядов KOTjopo- . го равны выходному коду регистра 6 сдвига а старший разряд равен 9 -инверсному значению выходной величины старшего разртша счетчика 12. Элемент 11 памяти можно разбить на две половины по 2 ячеек, в правую иэ которых входят ячейки р номерами 0,1,.,, М-1, а во вторую - ячейки с номерами Л , (M-fir ,.., (2M-i) . В ячейках с номерами Л одной половины элемента 11 памяти находятся сформированные суммы Зд4, в ячейках памяти -другой половины накапливаются сумма Sy.. При четных i( о) ячейки йервой (второй) элемента 11 памяти подключаются к 9(3) сумматору/ при нечетных с сумматором 9(з; соединены ячейки второй (первой половины элемента 11. Промежуточное значение суммы S« ;. ,.из ячейки памяти с номером А одной из половины элемента 11 памяти поступает на соответствующие входы другой группы информационных входов сумматора ,9 при высоком потенциале на входе синхроВходной случайный сигнал у(1;) преобразуется в коМпаратс« е 4 сиг I Го, если у 70, и, если у i О, который в М-м регистре 5 сдвига, содержащем М разрядов, квантуется импульсами ТИ 1 по времени с частотой f и преобразуется в М-раэрядный двоичный код В ( ,..., ц,ц:)д, где B,,-j Bt(Mi+j)/ гЛ. i- номер блока j 0,1,.,, (М-1)номер числа в блоке, . , ..((-1J J. ; Второй регистр 6 сдвига содержит D м-2 ячеек разрядности М, где D - количество oпpeдeляe в«t ординат оценки корреляционной функции. Импульсы ТИ 1, поступая с выхода генератсч а 8 импульсов на соот вествукидий вход синхронизации регистра 6 сдвига, сдвигают информацию в нем на одну М-раррядяую ячейку. Разрядные выходы старшей ячейки регистра 6 сдвига подключены к соот ветствукхцим входам первой группы {ВХОДОВ первой (младыей ячейки. Импульсы ТИ 3, частота следования копоступаяторых f с выхода cxaiMuero разряда счетчика 7 на ДфугоЯ вход синхронизации регистра 6 сдэнга, записывают в его первую ячейку ереэ соответствуицяе входы второй группы входов первой

низации элемента 11 памяти (ТИ ) . В cyivwaTope 9 к промежуточной сумме добавляется одно слагаемое

а5Аи- Ч,,и.Н(- i

результат, при ТИ , записывается в ту же ячейку памяти с А. После окончания формирования сумм SA:+I (через время t,, M/Ji ) половины элемента 11 памяти переключаются.

Пример формировения сумм Зд

:при щ 1, М 2, А .(афа).. ячейки код Bj .сформированный в регистрё 5 сдвиги Разрядные выходы старшей ячейки регистра 6 сдвига подключены к соответствующим входам (к М младшим разрядам; адреса чтения элемента 11 памяти блока 2. На разрядных выходах старшей ячейки регистра 6 сдвига с частотой fi поочередно формируются коды B|:j)i, . j которые выбирают из элемента 11 памяти суммы ЛИ Ь, « 1C г- , rfc j где к 0,1,... ,(С-1), Время выборки сумм при изменении от о др (г-1) равноt2 Bjfl ; -2 т.е. за время цикла работы регистра б сдвига в блоке 2 вычисления промежуточных сумм сформируются все су№вл ёд,,4 . В сумматоре 3 формируются суюлл МН , И йлн к MN VK «Г MN Ц .J которые равны оценкам ординат релей.ной корреляционной функвд1и, вычисляемых известных устройством по ,MN отсчетам входных сигналов при D М2. Для .получения к-й орднна оценки взшмНой корреляционной функции сигналов X(t) и Y{t) достаточно, как и в известном устройстве, значения Н умножить на по тоянный коэффициент J, заёйЧ:;я1ций от закона распрделения входных сигналов . Й„(МК/€.-ун. Введение блока вычисления промежуточных сумм позволяет в М раз повысить быстродействие коррелотлетра. Действительно, если в известном уст ройстве для блоков X|f и формирования суммы S производится за М тактов, то в предлагаемом устройстве для каждого блока Ху заранее, независимо от значений сигналу Y{t7, подготавливаются сукйы s при всех возможных значениях В и для конкретного В. в сумматор 3 из блока 2 однотактноЯ операцией вызывается соответствующая сумма. Если, например, М 5, D 5-2 160, f. частота квантования входных сигналов, то f2 32f для предлагаемого коррелометра и. f2 l60f для известного, что позволяет использовать злементы с меньшим быстродействием. При одинаковой частоте следования импульсов ТИ 2 высшая частота исследуемых сигналов в М раз выше в предлагаемом устройстве.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Жовинский В.Н., Арховский В.Ф | |||

| Корреляционные устройства | |||

| М., энергия, 1974, с | |||

| Реверсивный дисковый культиватор для тросовой тяги | 1923 |

|

SU130A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1972 |

|

SU422010A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-23—Публикация

1982-04-22—Подача