27, элемент ИСКЛЮЧАЮЩЕЕ ИЖ 28. Устройство позволяет вычислять результи- ругоище коррелограммы по массиву, состоящему из частньЕх коррелограмм,

используя для хранения массивов отсчетов частных и результирующих коррелограмм один и тот же массив ячеек памяти. 2 з.п. ф-лы,. 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для разделения коррелограмм | 1987 |

|

SU1439619A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Устройство для отображения информации | 1984 |

|

SU1236541A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано .для измерения функции взаимной корреляции каждо Гз го из суммы случайных процессов, подвергнутых разным масштабно-временным искажениям. Цель изобретения - повышение быстродействия. Устройство со-- держит элементы НЕ 1, 2, коррелятор 3,, группы элементов И 4, 5, 29-37, элементы И 6-8, 38-40, группы элементов ИЛИ 9, 41-43, элементы ИЛИ 10, 44-46, блоки памяти 11, 26, триггеры 12, 13, счетчики 14-16, дешифратор 17, блок синхронизации 18, вычисли- тельньш блок 19 вычисления сумм частных коррелограмм, блоки форсирования младших 20 и старших 21 адресов, коммутаторы младших 22, 23 и старших 24, 25 адресов, блок контроля четности р Ьд ю ел сд 00 -f

1

Изобретение относится к измерительной и вычислительной технике и может быть использовано для измерения функции взаимной корреляции каждого из суммы случайных процессов, подвергнутых разным масштабно-временным искажениям.

Цель изобретения - повышение быстродействия.

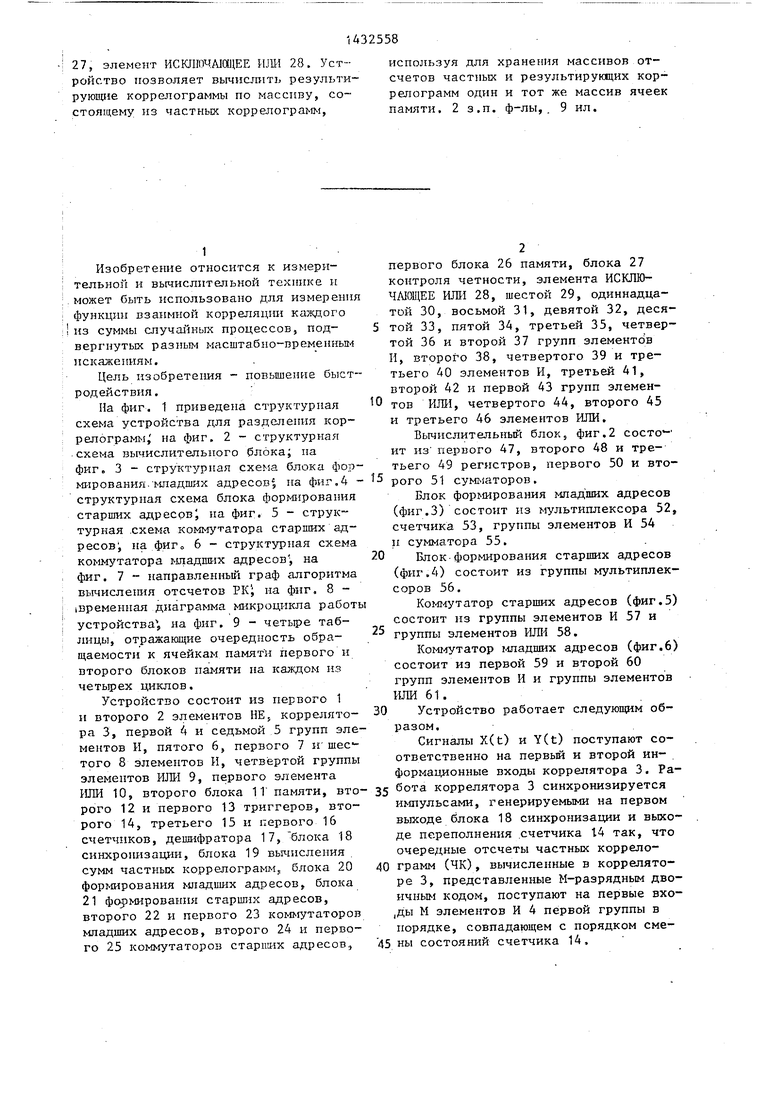

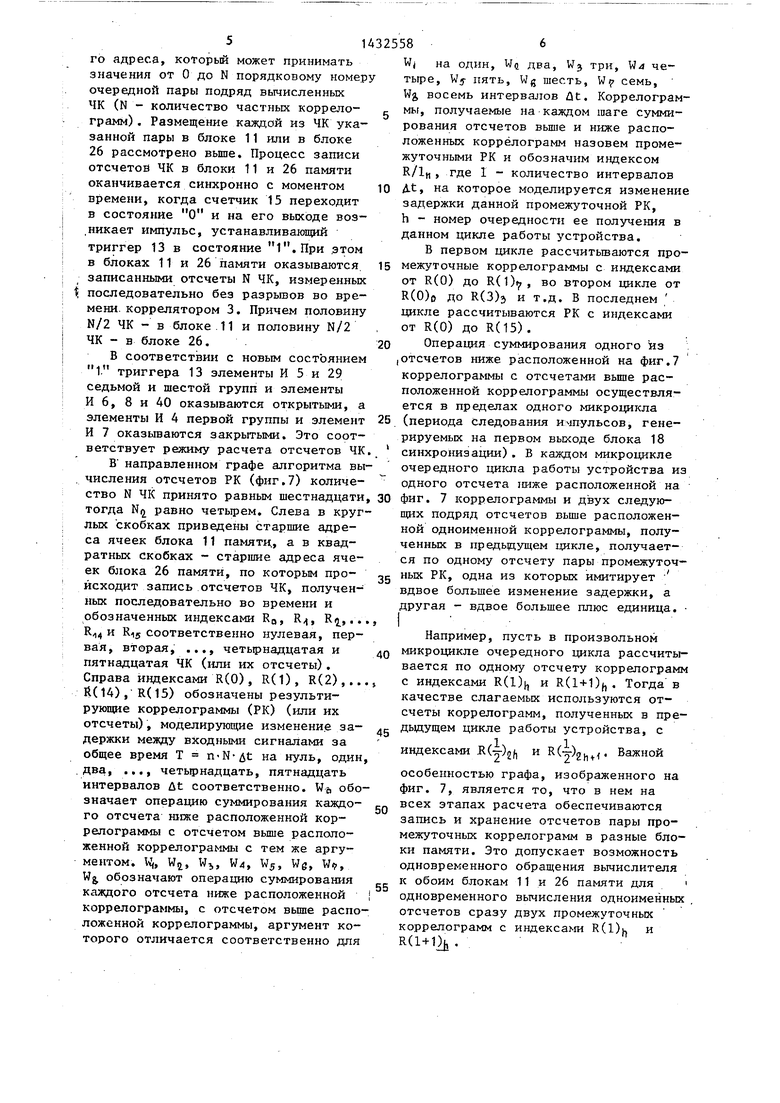

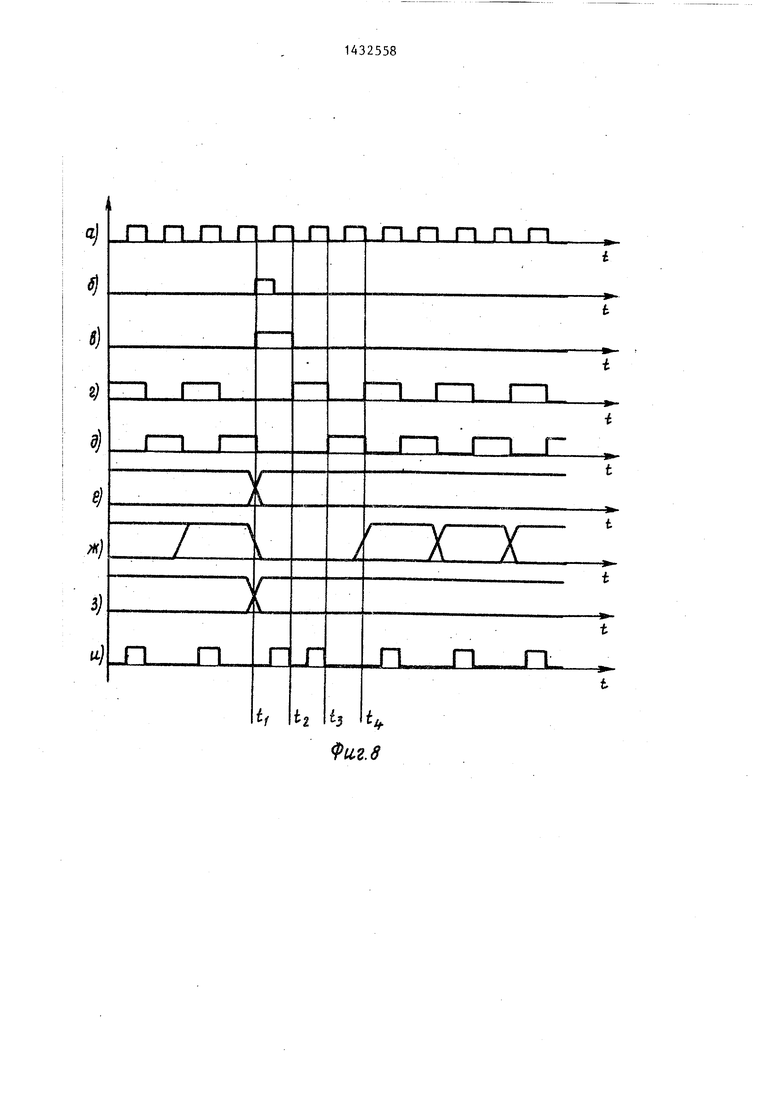

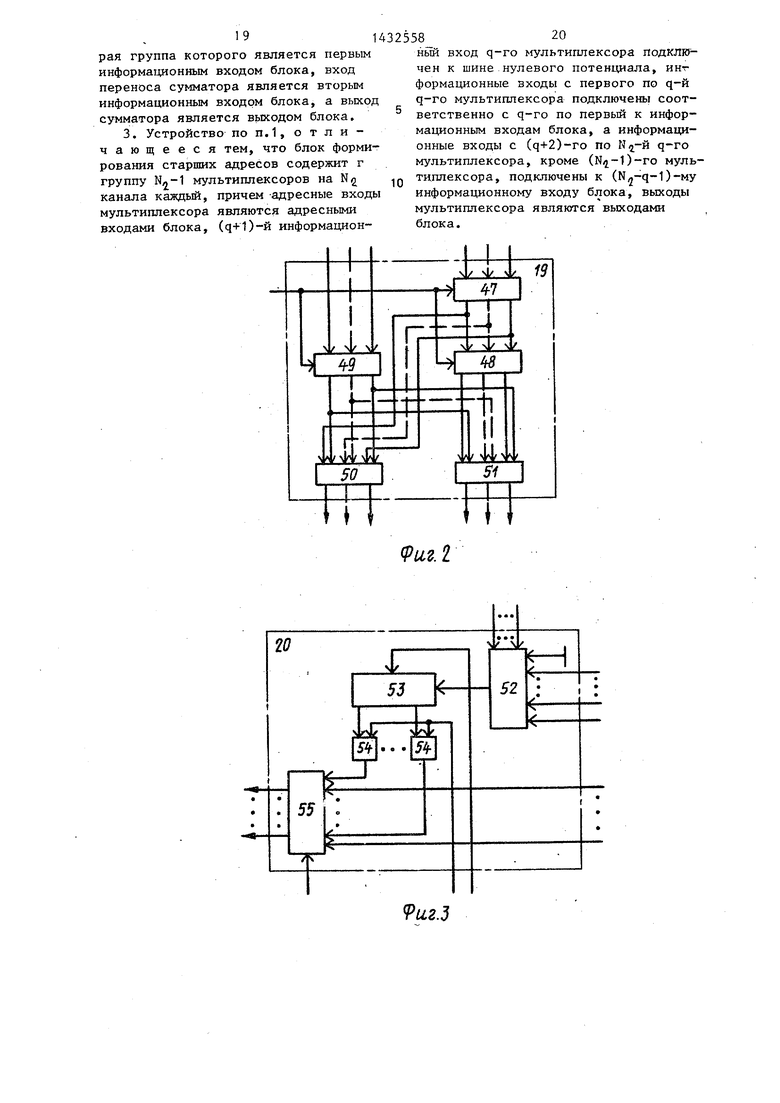

Па фиг. 1 приведена структурная схема устройства для разделения коррелограмм, на фиг. 2 - структурная схема вычислительного блока; па фиг, 3 - структурная схема блока фор- ьшрования. младших адресов, па фиг,4 структурная схема блока формирования старших адресовi па фиг, 5 - струк турная .схема комментатора старпгих ад- ресов на.фиго 6 - структурная схема коммутатора младших адресов , на фиг. 7 - направленньв граф алгоритма вьиислепия отсчетов РК ; па фиг, 8 - Времепная диаграмма микроцикла работы устройства, на фиг. 9 - четыре таблицы, отражающие очередность обращаемости к ячейкам памяти первого и второго блоков памяти на казкдом из четырех циклов.

Устройство состоит из первого 1 и второго 2 элементов НЕ; коррелятора 3, первой 4 и седьмой 5 групп элементов И, пятого 6j первого 7 и шес-- того 8 элемептов И, четвертой группы элементов РШИ 9, первого элемента 1-ШИ 10, второго блока 11 памяти, второго 12 и первого 13 триггеров, второго 14, третьего 15 и первого 16 счетчиков, дешифратора 17, блока 18 синхронизации, блока 19 вычисления, сумм частных коррелограмм, блока 20 формирования младших адресов, блока 21 формировапия старших адресов, второго 22 и первого 23 кoм ryтaтopoв младших адресов, второго 24 и первого 25 ко1гсмутаторов старпих гщресов.,

первого блока 26 памяти, блока 27 контроля четности, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 28, шестой 29, одиннадцатой 30, восьмой 31, девятой 32, десятой 33, пятой 34, третьей 35, четвертой 36 и второй 37 групп элементов И, второго 38, четвертого 39 и третьего 40 элементов И, третьей 41, второй 42 и первой 43 групп элеменгров ИЛИ, четвертого 44, второго 45 и третьего 46 элементов ИЛИ,

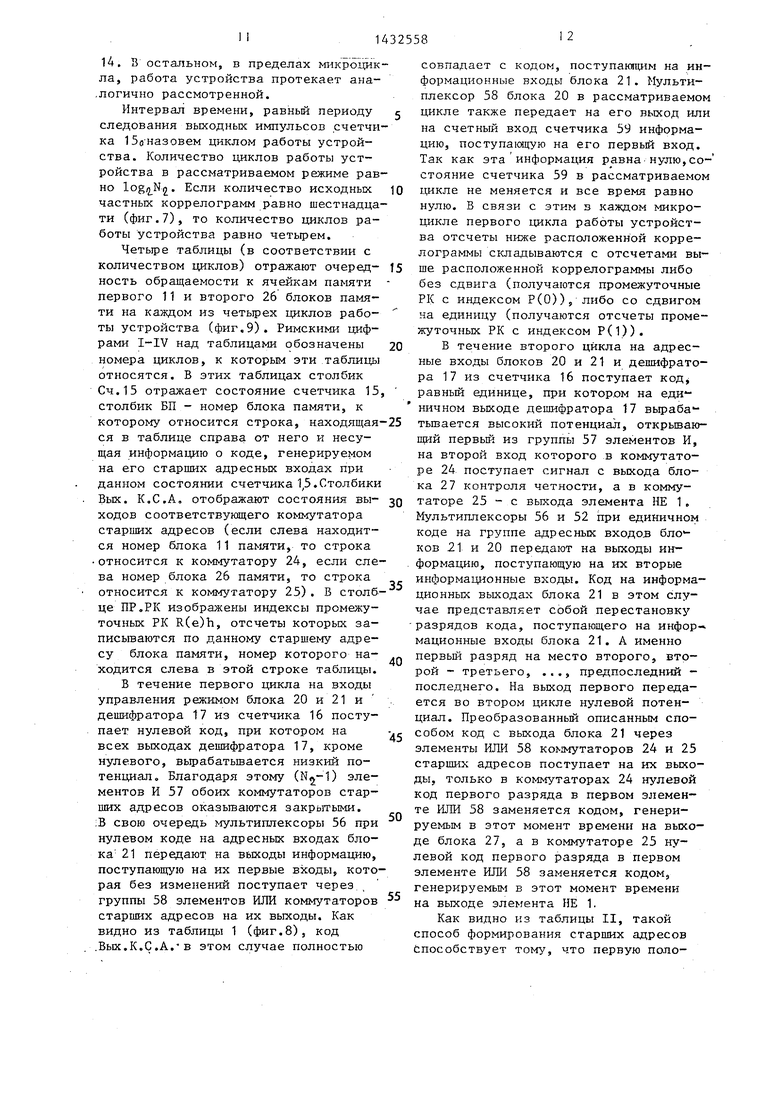

Вычислительный блок, фиг,2 состо - ит из первого 47, второго 48 и третьего 49 регистров, первого 50 и второго 51 cyMJsaTopoB.

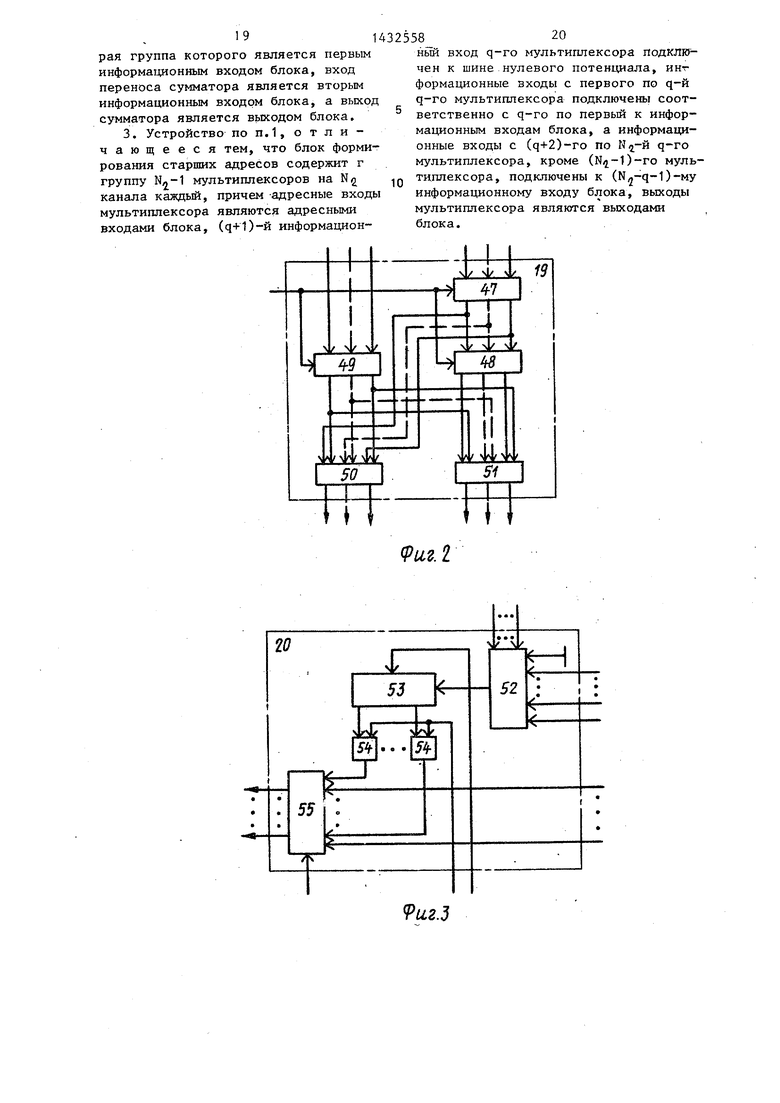

Блок формирования мпад шнх адресов (фиг.3) состоит из мультиплексора 52, счетчика 53, группы элементов И 54 и сумматора 55,

Блок-формирования старших адресов (фиг.4) состоит из группы мультиплексоров 56.

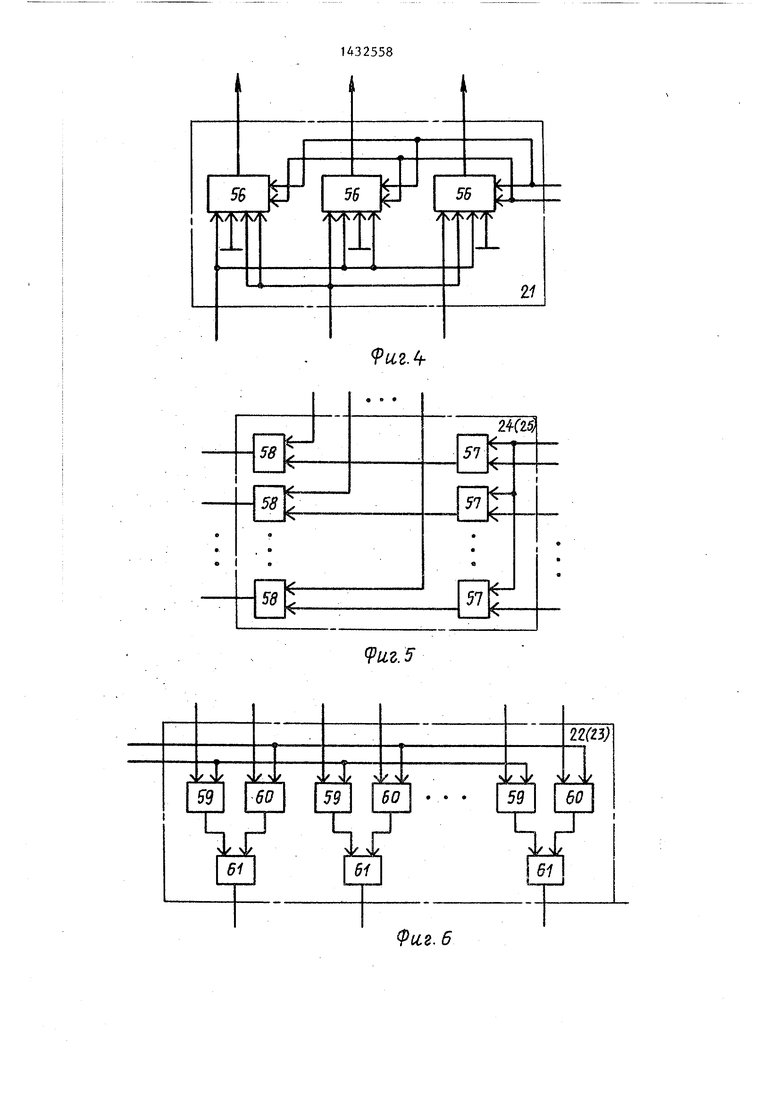

Ком1-1утатор старших адресов (фиг.5) состоит из группы элементов И 57 и

группы элементов Ш111 58,

Коммутатор младших адресов (фиг,6) состоит из первой 59 и второй 60 групп элементов И и группы элементов ИЛИ 61,

Устройство работает следующим образом.

Сигналы X(t) и Y(t) поступают соответственно на первый и второй информационные входы коррелятора 3, Работа коррелятора 3 синхронизируется и fflyльcaми, генерируемыми на первом выходе блока 18 синхронизации и выходе переполнения счетчика 14 так, что очередные отсчеты частных коррелограмм (ЧК), вычисленные в корреляторе 3, представленные М-разрядным двоичным кодом, поступают на первые вхо- ды М элемептов И 4 первой группы в порядке, совпадающем с порядком смены состояний счетчика 14.

Начало работы устройства совпадает с моментом времени, когда счетчик 16 переходит в состояние О и на его выходе возникает импульс, устанав-5 ливающий триггер 13 в состояние О. В соответствии с этим элементы И 4 первой группы и элемент И 7 оказьшаются открытыми, а элементы И 5 и 29 седьмой и шестой групп и элементы И 6, 8 и 40 оказываются закрытыми. Это соответствует режиму задней отсчетов ЧК, вычисляемых коррелятором 3, в блоки 11 и 26 памяти. Появление каждого нового отсчета ЧК совпадает с передним фронтом импульса, генерируемого на первом выходе блока 18 синхронизации. М-разрядньй код очередного отсчета ЧК через группу 4 открытых элементов И поступает на информационные входы блоков 11 и 26 памяти, причем, на вход блока 11 памяти через группу 9 элементов ИЛИ, а на вход блока 26 памяти - через группу 41 элементов ИЛИ. Запись этих отсчетов осуществляется либо в блок 11, либо в блок 26 в зависимости от того, какой из элементов И 38 или 39 в момент генерации указанного импульса открыт. Если открыт элемент И 39, импульс генерируемьй на первом выходе блока.18 синхронизации, поступает через элемент И 39 и элемент ИЛИ 45 на вход записи блока 11 памяти. Если открыт элемент И 38, импульс поступает через элемент И 38 и элемент ИЛИ 46 на вход записи блока 26 памяти. Указанным импульсом и осуществляется запись очередного отсчета ЧК в соответст- вуннций блок памяти. Этим обеспечивается попеременная запись отсчетов ЧК в блоки 11 и 26 памяти по адресу, генерируемому на группах выходов коммутаторов младших и старших адресов.

В рассматриваемом режиме на адресные входы блоков формирования младших 20 и старших 21 адресов, а также входы дешифратора 17с информационных выходов счетчика 16 поступает ну- левой код, в соответствии с которым коды, генерируемые счетчиком 14 в качестве младшего адреса, а коды, генеВ моменты времени, когда в корреляторе 3 идет процесс вычисления отсчетов второй, третьей, пятой, восьмой и т.д. ЧК, которым соответствует нечетная сумма указанных единиц, оказьшается открытым элемент И 38 и отсчеты ЧК записьшаются в блок 26 памяти по адресам с нулевого по ()-й второй ЧК, с по

рируемые счетчиком 15 в качестве

старшего адреса, поступают через блО- gg(2N -1)-й третьей ЧК и т.д. При этом

ки 20, 22 и 23 и блоки 21, 24 и 2 обеспечивается соответствие младсоответственно на адресные входышего адреса, которьй может принимать

младших и старших адресов блоков 11значения от О до () порядковому

и 26 памяти без изменения. Таким об-номеру отсчета очередной ЧК, старше

0

5

0

g

разом, смена старшего адреса на адресных входах обоих блоков памяти fe режиме записи отсчетов ЧК происходит после вычисления каждой второй от начала работы устройства ЧК. Вопрос в какой из блоков 11 или 26 записьгоа- готся отсчеты очередной из пары подряд следующих ЧК решается посредством управления состоянием элементов И 38 и 39, осуществляемым с помощью элемента НЕ 2 и элемента ИСКПЮЧАЩЕЕ ИЛИ 28, входы которого подключены к выходу триггера 12 и выходу блока 27 контроля четности.

Схема контроля четности вырабатывает низкий потенциал, если сумма единиц на информационных выходах счетчика 15 четная, и высокий потенциал, если сумма упомянутых единиц нечетная. В элементе ИСКПЮЧАЩЕЕ ИЛИ происходит сравнение этого потенциала с выходным сигналом триггера 12, благодаря чему на его выходе вьфабаты5 вается низкий потенциал, когда сумма единиц на информационных выходах счетчика 15 и триггера 12 четная, и высокий пртенциал, если сумма единиц нечетная. Так как код, генерируемьй

0 триггером 12 и счетчиком 15, соответствует номеру ЧК, вычисленной коррелятором 3 после начала работы устройства, получается, что в моменты времени, когда в корреляторе идет про-

2 цесс вычисления отсчетов первой, четвертой, шестой, седьмой и т.д. ЧК, которым соответствует четная сумма единиц на иг ормационных выходах счетчика 15 и триггера 12,оказывается открытым элемент И 39 и отсчеты упомянутых ЧК записьшаются в блок 1.1 ; памяти по адресам с нулевого по ()-и (NA - количество отсчетов в ЧК) первой ЧК, с по (2Н1-1)-й

5 четвертой ЧК и т.д.

0

В моменты времени, когда в корреляторе 3 идет процесс вычисления отсчетов второй, третьей, пятой, восьмой и т.д. ЧК, которым соответствует нечетная сумма указанных единиц, оказьшается открытым элемент И 38 и отсчеты ЧК записьшаются в блок 26 памяти по адресам с нулевого по ()-й второй ЧК, с по

го адреса, который может принимать значения от О до N порядковому номеру очередной пары подряд вычисленных ЧК (N - количество частньш коррело- грамм). Размещение каждой из ЧК указанной пары в блоке 11 или в блоке 26 рассмотрено вьше. Процесс записи отсчетов ЧК в блоки 11 и 26 памяти оканчивается синхронно с моментом времени, когда счетчик 15 переходит в состояние О и на его выходе воз- .никает импульс, устанавливающий триггер 13 в состояние 1,При .этом в блоках 11 и 26 памяти оказываются записанными отсчеты N ЧК, измеренных последовательно без разрьшов во времени. Коррелятором 3. Причем половину N/2 ЧК - в блоке . 11 и половину N/2 ЧК - в блоке 26.

В соответствии с новым состоянием 1. триггера 13 элементы И 5 и 29 седьмой и шестой групп и элементы И 6, 8 и 40 оказываются открытыми, а элементы И 4 первой группы и элемент И 7 оказываются закрытыми. Это соответствует режиму расчета отсчетов ЧК

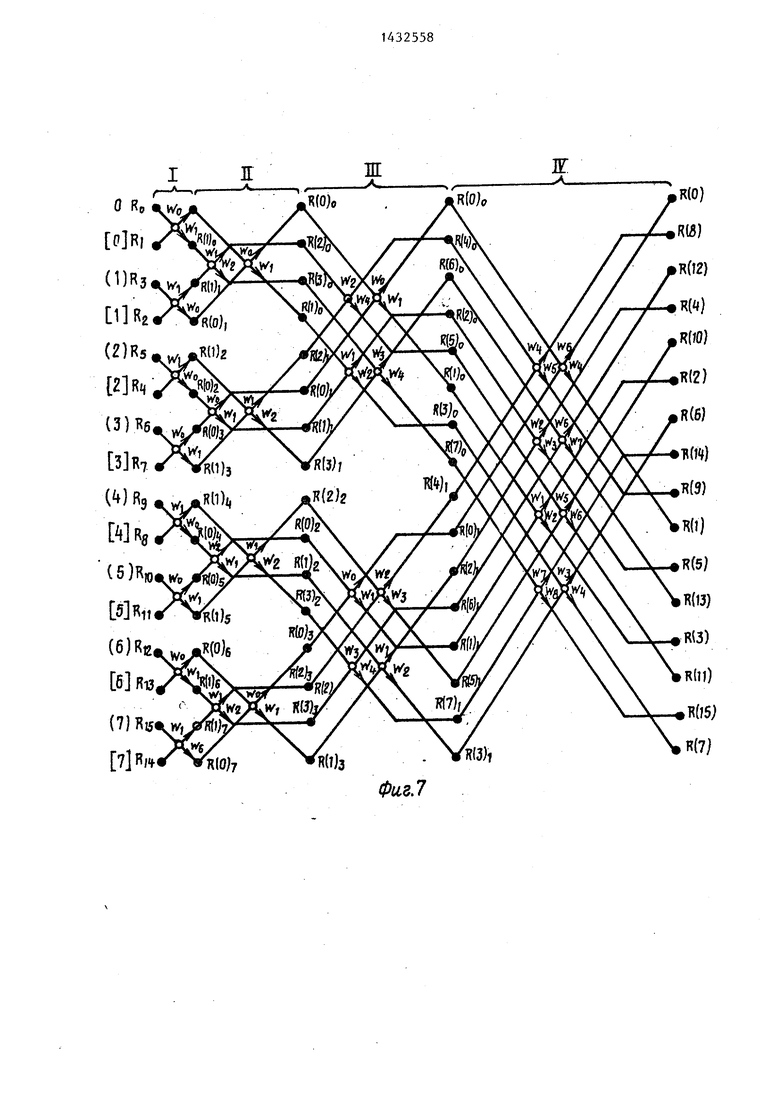

В направленном графе алгоритма вычисления отсчетов РК (фиг.7) количещих подряд отсчетов выше расположенной одноименной коррелограммы, полученных в предьдущем цикле, получается по одному отсчету пары промежуточ 35 ных РК, одна из которых имитирует вдвое большее изменение задержки, а другая - вдвое большее плюс единица.

ство N ЧК принято равным шестнадцати, 30 фиг. 7 коррелограммы и двух следую- тогда N равно четырем. Слева в круглых скобках приведены старшие адреса ячеек блока 11 памятд, а в квадратных скобках - старшие адреса ячеек блока 26 памяти, по которым происходит запись отсчетов ЧК, полученных последовательно во времени и обозначенных индексами RQ, R, R,..., и Ki5 соответственно нулевая, первая, вТорая, ... четырнадцатая и о пятнадцатая ЧК (или их отсчеты). Справа индексами R(0), R(1), R(2),..., R(14), R(15) обозначены результирующие коррелограммы (РК) (или их отсчеты), моделирующие изменение задержки между входными сигналами за общее время Т на нуль, один, .два, ..., четырнадцать, пятнадцать интервалов ut соответственно. Wj, обозначает операцию суммирования каждого отсчёта ниже расположенной коррелограммы с отсчетом выше расположенной коррелограммы с тем же аргументом. Ц, Wi;, Wi,, W4, W5, We, W(, Wj обозначают операцию суммирования каждого отсчета ниже расположенной i

Например, пусть в произвольном микроцикле очередного цикла рассчиты вается по одному отсчету коррёлограм с индексами R(l)j, и R(l + 1)(, . Тогда в качестве слагаемьк используются отсчеты коррёлограмм, полученных в пре дц дьдущем цикле работы устройства, с

11 индексами K(-j)2|, и Важной

особенностью графа, изображенного на фиг. 7, является то, что в нем на всех этапах расчета обеспечиваются запись и хранение отсчетов пары промежуточных коррёлограмм в разные бло ки памяти. Это допускает возможность одновременного обращения вычислителя к обоим блокам 11 и 26 памяти для одновременного вьиисления одноименны отсчетов сразу двух промежуточных коррёлограмм с индексами R(l)i и R(l+1)j, .

50

55

коррелограммы, с отсчетом вьшзе расположенной коррелограммы, аргумент которого отличается соответственно для

Wj на один, Wd два, Wj три, W четыре, Vf пять, Wg шесть, W семь, Wg, восемь интервалов ut, Коррелограм- мы, получаемые на каждом шаге суммирования отсчетов Bbmie и ниже расположенных коррёлограмм назовем промежуточными РК и обозначим индексом R/IH, где 1 - количество интервалов ДС, на которое моделируется изменение задержки данной промежуточной РК, h - номер очередности ее получения в данном цикле работы устройства.

В первом цикле рассчитьшаются промежуточные коррелограммы с индексами от R(0) до R(1)i7, во втором цикле от R(0)o до К(3)з и т.д. В последнем цикле рассчитываются РК с индексами от К(0) до R(15).

Операция суммирования одного из Iотсчетов ниже расположенной на фиг.7 коррелограммы с отсчетами выше расположенной коррелограммы осуществляется в пределах одного микроцикла (периода следования импульсов, генерируемых на первом выходе блока 18 синхронизации). В каждом микроцикле очередного цикла работы устройства из одного отсчета тшже расположенной на

щих подряд отсчетов выше расположенной одноименной коррелограммы, полученных в предьдущем цикле, получается по одному отсчету пары промежуточ- ных РК, одна из которых имитирует вдвое большее изменение задержки, а другая - вдвое большее плюс единица.

фиг. 7 коррелограммы и двух следую-

фиг. 7 коррелограммы и двух следую-

Например, пусть в произвольном микроцикле очередного цикла рассчитывается по одному отсчету коррёлограмм с индексами R(l)j, и R(l + 1)(, . Тогда в качестве слагаемьк используются отсчеты коррёлограмм, полученных в пре- дьдущем цикле работы устройства, с

11 индексами K(-j)2|, и Важной

особенностью графа, изображенного на фиг. 7, является то, что в нем на всех этапах расчета обеспечиваются запись и хранение отсчетов пары промежуточных коррёлограмм в разные блоки памяти. Это допускает возможность одновременного обращения вычислителя к обоим блокам 11 и 26 памяти для одновременного вьиисления одноименных отсчетов сразу двух промежуточных коррёлограмм с индексами R(l)i и R(l+1)j, .

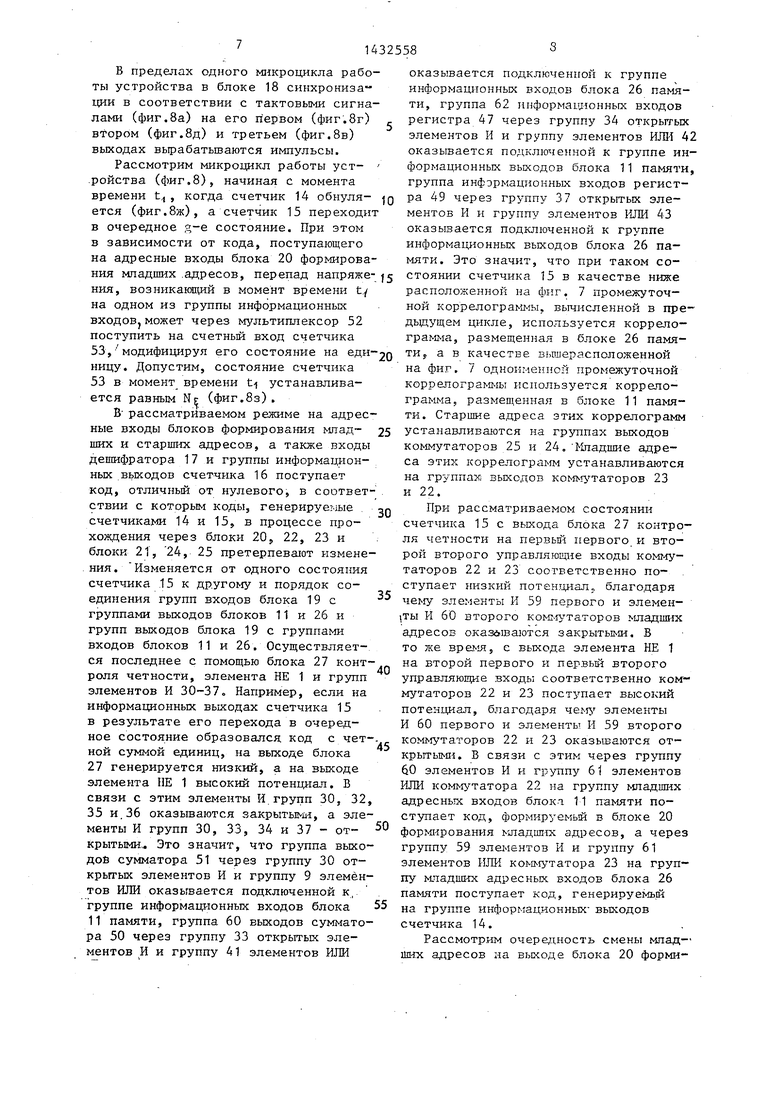

В пределах одного М11кроцикла работы устройства в блоке 18 сннхрониза ции в соответствии с тактовыми сигналами (фиг.8а) на его первом (фиг.Зг) втором (фиг.бд) и третьем (фиг.Вв) выходах вырабатьшаются импульсы.

Рассмотрим микроцикл работы уст- .ройства (фиг.8), начиная с момента времени t, когда счетчик 14 обнуля- ется (фиг.Вж), а счетчик 15 переходит в очередное g-e состояние. При этом в зависимости от кода, поступающего на адресные входы блока 20 формирования младших .адресов, перепад напряження, возникакяций в момент времени t,/ на одном из группы информационных BxoAOBj может через мультиплексор 52 поступить на счетньй вход счетчика 53, модифицируя его состояние на единицу. Допустим, состояние счетчика 53 в момент времени ti устанавливается равным Nr (фиг.Вз).

В рассматриваемом режиме на адресные входы блоков формироваьшя мпад- ших и старших адресов, а также входы дешифратора 17 и группы информационных вькодов счетчика 16 поступает код, отлнчньй от нулевого, в соответствии с которым коды, генерируемые счетчиками 14 и 15, в процессе прохождения через блоки 20, 22, 23 и блоки 21, 24, 25 претерпевают изменения. Изменяется от одного состояния счетчика 15 к другому и порядок соединения групп входов блока 19с группами выходов блоков 11 и 26 и групп выходов блока 19 с группами входов блоков 11 и 26. Осуществляется последнее с помощью блока 27 контроля четности, элемента НЕ 1 и групп элементов И 30-37. Например, если на информационных выходах счетчика 15 в результате его перехода в очередное состояние образовался код с четной суммой единиц, на выходе блока 27 генерируется низкий, а на выходе элемента НЕ 1 высокий потенциал. В связи с этим элементы И групп 30, 32, 35 и. 36 оказываются закрытьп ш, а элементы И групп 30, 33, 34 и 37 - от- крытыми Это значит, что группа выхо- дой сумматора 51 через группу 30 открытых элементов И и группу 9 элементов ИЛИ оказывается подключенной к, группе информационных входов блока 11 памяти, группа 60 выходов сумматора 50 через группу 33 открытых элементов И и группу 41 элементов ИЛИ

Q 5 о

5 Q 5

5

0

оказывается подключенной к группе информационных входов блока 26 памяти, группа 62 ннформащюнных входов регистра 47 через группу 34 открьггьк элементов И и группу элементов ИЛИ 42 оказывается подключенной к группе информационных выходов блока 11 памяти, группа информационных входов регистра 49 через группу 37 открытых элементов И и группу элементов ИЛИ 43 оказывается подключенной к группе информационных выходов блока 26 памяти. Это значит, что при таком состоянии счетчика 15 в качестве ниже расположенной на фиг. 7 промежуточной коррелограммы, вычисленной в пре- дьщущем цикле, используется коррело- грамма, размещенная в блоке 26 памя- тИу а в качестве в-ллерасположенной на фиг, 7 одноименной промежуточной коррелограммы используется коррело- грамма, размещенная в блоке 11 памяти. Старшие адреса этих коррелограмм устанавливаются на группах выходов коммутаторов 25 и 24. Мпадшие адреса этих коррелограьм устанавливаются на группах выходов комм таторов 23 к 22.

При рассматриваемом состоянии счетчика 15 с выхода блока 27 контроля четности на первьй первого и второй второго управляющие входы KOMi-iy- таторов 22 и 23 соответственно по- . ступает низкий потенциал,, благодаря чему элементы И 59 первого и элемен- (ТЫ И 60 второго коммутаторов младших адресов оказбшаются закрытьк ш. В то же время, с выхода элемента НЕ 1 на второй первого и первьй второго управляющие входы соответственно мутаторов 22 и 23 поступает высокий потенциал, благодаря элементы И 60 первого и элементы И 59 второго коммутаторов 22 и 23 оказываются от- KpbiTbiNffl, В связи с этим через группу 60 элементов И и группу 61 элементов ИЛИ коммутатора 22 на группу мпадших адресных входов блока 11 памяти поступает код, формируемьй в блоке 20 формирования младших адресов, а через группу 59 эле1 ентов И и группу 61 элементов ИЛИ коммутатора 23 на группу мпадЕНх адресных входов блока 26 памяти поступает код, генерируемьд на группе инфop {aциoнныx выходов счетчика 14.

Рассмотрим очередность смены млад-- 1ШХ адресов на выходе блока 20 форми

рования младших адресов в пределах рассматриваемого микроцикла работы устройства.

На дополнительном информационном входе и выходе разрешения блока 20 в интервале времени t}-t4 (фиг.8) генерируется нулевой потенциал. Элементы И 54 (фиг.З) закрыты и в качестве младшего адреса на выходе блока 20 генерируется код состояния счетчика. 14, которьй без изменения проходит через сумматор 55. Сигналы, генерируемые на втором и третьем выходах блока 18, объединяются в элементе ИЛИ 44. Б результате, в интервале времени на входе разрешения блока 20 генерируется высокий потен-л циал, открьшающий.: элементы И 54. Благодаря этому, в сумматоре 55 в этем интервале времени суммируются коды счетчиков 14 и 53, а в интервале времени , когда с второго

выхода блока 18 на вход переноса сумматора 55 поступает высокий потенциал (фиг.8г), к ним добавляетс еще единица.

В соответствии с рассматриваемым .состоянием счетчика 15 (он переходит, в состояние, когда сумма единиц на его информационных выходах четная), а с ним и состояниями блоков 20-25 и 27 групп с 30 по 37 элементов И, а также вьше рассмотренной очереднос TbKt смены адресов на группе выходов блока.20 работа устройства в предёла микроциюта осуществляется следуюп им образом.

В интервале времени на информационных выходах блока 11 памяти генерируется М-разрядньй двоичный код (0+N )-го отсчета вьше расположенной на фиг. 7 1-й промежуточной РК. Задним фронтом импульса (фиг.Ви, 1момент времени ti2.), генерируемого в этом интервале времени на выходе элемента ШШ 44, этот код записьшает ся в регистр 47 (фиг.2) третьего слагаемого..

В интервале времени на информационных выходах блока 11 памяти генерируется М-разрядньш двричый код ()ro отсчета вьппе расположенной на фиг. 7 1-й промежуточной РК. На информационных выходах блока 26 памяти в этом же интервале времеш генерируется М-разрядньп1 Д7зоичный код нулевого отсчета нилсе расположенной на фиг. 7 1-й промежуточной РК.

10

20 15

25

Q

фронтом импульса (фиг.би, момент времени (13) , генерируемого в этом интервале времени на выходе элемента РШИ 44, код, хранившийся в регистре 47, переписьюается в регистр 48, код, генерируемьм на выходе бло- ка 11 памяти, записывается в регистр 47,.код, генерируемьй на выходе блока 26 памяти, записывается в регистр 49.

В интервале времени tj-t результат сложения кодов регистров 48 и 49 возникающий на группе выходов сумматора 51 (фиг.2), поступает через группу М открытых элементов И 5, группу М открытых элементов И 30 и группу М элементов ИЛИ 9 на группу информационных входов блока 11 памяти. В этом же интервале времени результат сложения кодов регистров 49 и 47, возникающий на группе выходов cyм iaтopa 50, поступает через группу М- открытых элементов И 29, М открытых элементов И 33 и группу М элементов ИЛИ 41 на группу информационных входов блока 26 памяти. Им- пульсом (фиг.8д), генерируемым в этом интервале времени на выходах эле- ментой. ИЛИ 45 и 46, упомянутые результаты сложения записываются: .первый - в блок 11 памяти на место нулевого отсчета вьше расположенной на фиг. 7 1-й промежуточной РК, вто

рой - в блок 26 памяти на место нулеч вого отсчета ниже расположенной на фиг. 7 1-й промежуточной РК, упомянутые отсчеты которых уже не нужны для дальнейи.мх расчетов.

Когда счетчик 15 находится в состоянии, при- котором сумма единиц на его информап юнных вькодах нечетная, открытыми оказываются группы 31, 32,

33и 36 элементов И, а группы 30, 33,

34и 37 элементов И - закрытыми. ки 11 и 26 памяти в своем взаимодействии с вычислительным блоком 19 меняются местами. Из блока 26 памяти вызьшаются отсчеты расположенной выше на фиг. 7 -промежуточной РК, а из блока 11 памяти ниже расположенной одноименной РКс Коммутатор 23 посту;пает на группу младп1их адресных входов блока 26 памяти код, формируемый в блоке 20 формирования .младших адресов. Коммутатор 22 пропускает на группу младших адресных входов блока 11 памя.ти код, генерируемьй на группе информационных выходов счетчика

Интервал времени, равньй периоду следования выходных импульсов счетчика 15о-назовем циклом работы устройства. Количество циклов работы устройства в рассматриваемом режиме равно logij N. Если количество исходных частных коррелограмм равно шестнадцати (фиг.7), то количество циклов работы устройства равно четырем.

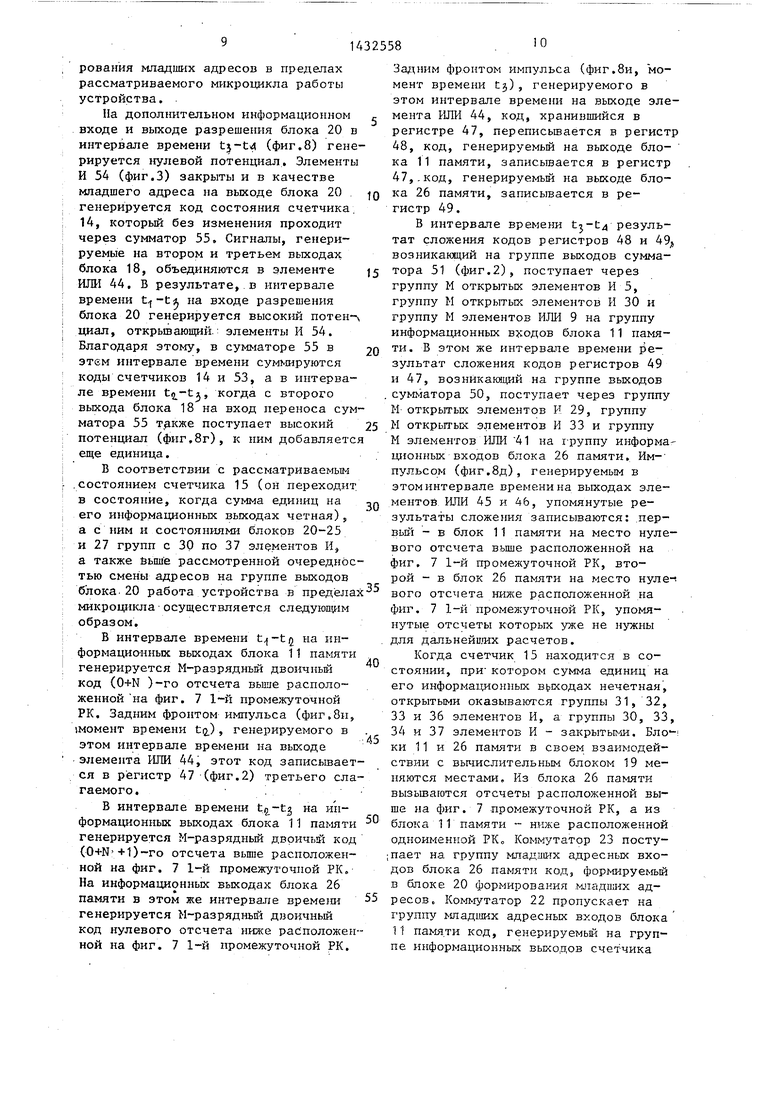

Четыре таблицы (в соответствии с количеством циклов) отражают очередность обращаемости к ячейкам памяти первого 11 и второго 26 блоков памяти на каждом из четырех циклов работы устройства (фиг,9). Римскими цифрами I-IV над таблицами обозначены номера циклов, к которым эти таблицы относятся. В этих таблицах столбик Сч.15 отражает состояние счетчика 15 столбик БП - номер блока памяти, к которому относится строка, находящаяся в таблице справа от него и несущая информацию о коде, генерируемом на его старших адресных входах при данном состоянии счетчика 1,5.Столбики Вых. К.С.А, отображают состояния выходов соответствующего коммутатора старших адресов (если слева находится номер блока 11 памяти, то строка относится к коммутатору 24, если слева номер блока 25 памяти, то строка относится к коммутатору 25). В столбце ПР.РК изображены индексы промежуточных РК R(e)h, отсчеты которых записываются по данному старшему адресу блока памяти, номер которого находится слева в этой строке таблицы.

В течение первого цикла на входы управления режимом блока 20 и 21 и дешифратора 17 из счетчика 16 поступает нулевой код, при котором на всех выходах дешифратора 17, кроме нулевого, вьтрабатьшается низкий потенциал. Благодаря этому () элементов И 57 обоих коммутаторов старших адресов оказьшаются закрытыми. ;В свою очередь мультиплексоры 56 при нулевом коде на адресных входах блока 21 передают на выходы информацию, поступающую на их первые входы, которая без изменений поступает через группы 58 элементов ИЛИ коммутаторов старших адресов на их выходы. Как видно из таблицы 1 (фиг.8), код .Вых.К.С.А. в этом случае полностью

0

5

0

5

0

5

0

5

0

5

совпадает с кодом, поступаю цим на информационные входы блока 21. Мультиплексор 58 блока 20 в рассматриваемом цикле также передает на его выход или на счетный вход счетчика 59 информацию, поступа1сяцук на его первьй вход. Так как эта информация равна-нулю,со- стояние счетчика 59 в рассматриваемом цикле не меняется и все время равно нулю. В связи с этим в каждом микроцикле первого цикла работы устройства отсчеты ниже расположенной корре- лограммы складываются с отсчетами выше расположенной коррелограммы либо без сдвига (получаются промежуточные РК с индексом Р(0)), либо со сдвигом на единицу (получаются отсчеты промежуточных РК с индексом Р(1)).

В течение второго цикла на адресные входы блоков 20 и 21 и дешифратора 17 из счетчика 16 поступает код равный единице, при котором на единичном выходе дешифратора 17 вьфаба- тьтается высокий потенциал, открьшаю- щий первый из группы 57 элементов И, на второй вход которого в коммутаторе 24 поступает сигнал с выхода блока 27 контроля четности, а в коммутаторе 25 - с выхода элемента НЕ 1. Мультиплексоры 56 и 52 при единичном коде на группе адресных входов блоков 21 и 20 передают на выходы ин формацию, поступающую на их вторые информационные входы. Код на информа- ционньк выходах блока 21 в этом случае представляет собой перестановку

разрядов кода, поступающего на инфор-. мационные входы блока 21. А именно первый разряд на место второго, второй - третьего, ..., предпоследний - последнего. На выход первого передается во втором цикле нулевой потенциал. Преобразованный описанным способом код с выхода блока 21 через элементы ИЛИ 58 коммутаторов 24 и 25 старших адресов поступает на их выходы, только в коммутаторах 24 нулевой код первого разряда в первом элементе ИЛИ 58 заменяется кодом, генерируемым в этот момент времени на выходе блока 27, а в коммутаторе 25 нулевой код первого разряда в первом элементе ИЛИ 58 заменяется кодом, генерируемым в этот момент времени на выходе элемента НЕ 1.

Как видно из таблицы II, такой способ формирования старших адресов Способствует тому, что первую половину второго цикла из блоков памяти 11 и 26 в вычислительный блок 19 попарно вызываются отсчеты промежуточных РК с индексом О К(0), а вторую половину - с индексом один Д(1). Иа второй вход ryльтиплeкcopa 52 поступает выход предпоследнего разря- да счетчика 15, отрицательньш перепад напряжения на котором происходит как раз посредине второго цикла. Поэтому первую половину второго цикла в счетчике 53 сохраняется нулевое состояние, а вторую половину - единичное состояние. Первую половину в блоке 20 происходит сдвиг адресов сум суммируемых отсчетов выше расположенных на фиг. 7 коррелограмм на ноль и один интервал t, в результате чего получаются промежуточные РК с индексом О и 1 соответственно R(0) и R(1). Вторую половину второго цикла в блоке 20 происходит сдвиг адресов суммируемых отсчетов, выше расположе ных на фиг. 7 выше соответствующих коррелограмм на один и два интервала At, в результате чего получаются промежуточные РК с индексом два и три соответственно R(2) и R(3),

В течение третьего цикла на адресные входы управления режимом блоков 20 и 21 и дeIШiфpaтopa 17 из счетчика 16 поступает код, равный двум, при котором на выходе два дешифратора 17 вьфабатывается высокий потенциал, открывающий второй из группы 57 элементов И. Мультиплексоры 56 и 52 при коде два на группе информационных входов блоков 21 и 20 передают на выходы информацию, поступающую на их третьи входы. Код на информационных вькодах блока 21 в- этом случае представляет перестановку разрядов кода, поступающего на его информационные входы в порядке - первьш разряд на место третьего, второй - четвертого, ..., предпоследиш на место первого. рулевой потенциал в третьем цикле передается на выход второго мультиплексора 56. При этом нулевые коды уже вторых разрядов заменяются в коммутаторе 24 кодом, генерируемьш на выходе блока 27, а в коммутаторе 25 кодом, генерируемым на выходе элемента НЕ 1..

Как видно из таблицы III, в первую четверть третьего 1щкла из блоков 11 3-1 26 памяти в вычислительньй блок 19 попарно вызываются отсчеты

0

5

0

5

0

5

0

5

промежуточных РК с индексом ноль R(0), вторую четверть - с индексом один R(1), третью четверть - с индексом два R(2), четвертую четверть- с индексом три R(3). На третий вход мультиплексора 52 поступает выход третьего от конца разряда счетчика 15, отрицательньй перепад напряжения на котором происходит три раза каждый раз через четверть длительности цикла. В результате первую четверть третьего цикла счетчик 53 находится в состоянии ноль, вторую - один, третью.- два, четвертую - три. Первую четверть третьего цикла в блоке 20 происходит сдвиг адресов суммируемых отсчетов на ноль и один интервал At, в результате чего получаются промежуточные РК с индексом ноль и единица соответственно R(0) и R(1), Вторую четверть третьего цикла в блоке 20 происходит сдвиг адресов суммируемых отсчетов на один и . два интервала jtit, в результате чего получаются промежуточные РК с индексом два и три соответственно R(2) и 11(3) . Третью четверть третьего цикла в блоке 20 происходит сдвиг адресов суммируемых отсчетов промежуточных РК с индексом R(2) на: два и три интервала At, в результате чего полу- . чаются промежуточные РК с индексом четыре и пять соответственно R(4) и R(5). Четвертую четверть третьего цикла в блоке 20 происходит сдвиг адресов суммируемых отсчетов промежуточных коррелограмм с индексом R(3) на три и-четыре интервала At, в результате чего получаются промежуточные РК с индексом шесть и семь соот ветственно R(6) и R(7).

Последующие циклы работы устройства протекают аналогичным образом. Каждая смена состояния счетчика 16 режимов вызьшает новую перестановку старших адресов, формируемых блоком 21, и коммутацию выходов блоков 27 и 1 на место следующего более старшего разряда в коммутаторах 24 и 25 по описанному принципу. На вход счетчика 53 через мультиплексор 52 коммутируется следунщий, более, млад1иий разряд счетчика 15. Количество моделируемых законов изменения задержки удваивается, пока в последнем цикле не будут вычислены все N результи- руюоще коррелограмм, моделирующих N законов изменения задержки.

51432558

ормула из об р етения

ед вы с ло г ши го ро эл ми во ве вт гр тр эл вт вт хо вх нь нь ши ст вх по pe ро со ши го ин чи го пе rp во со ре по по ши фо че вт гр

(Первой группы, выходы элементов И четвертой и пятой групп подключены соответственно к первым и вторым входам элементов ИЛИ второй группы, выход.переполнения первого счетчика соединен с входом сброса первого триггера, инверсньй выход которого соединен с первым входом первого элемента И, отличающееся тем, что, с целью повьшения быстродейст. ВИЯ, в него введены блок вычисления сумм частных коррелограмм, содержащий три регистра и два сумматора, блок формирования старших адресов, блок формирова шя младших адресов, блок контроля четности, два коммутатора старших адресов, два коммутатора младших адресов, второй триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, два элемента НЕ, пять групп элементов И, две группы элементов ИЛИ, четыре элемента ИЛИ и пять элементов И, причем первьш выход блока синхронизации соединен с первыми входами второго, третьего и четвертого элементов И и счетным входом второго счетчика, выход переполнения которого подключен

10

15

20

25

30

35

40

45

единен с выходом пятого элемента И, выход первого элемента ИЛР1 соединен с N(-M разрядом (N. log. N, N - чи ло частных кoppeлoгpa iм) входы сдви га адресов блока формирования младших адресов и счетным входом третье го счетчика, выход переполнеш я кот рого соединен с первым входом шесто элемента И, входом сброса блока фор мирования младиих адресов и установочным входом первого триггера, инверсный выход которого соединен с вторыми входами элементов И первой группы, а прямой - с вторым входом третьего элемента И, первыми входам элемента И шестой и седьмой групп, вторым входом пятого элемента И и вторым входом шестого элемента И, в ход которого соединен со счетными входом первого счетчика, информацио ньй выход которого соединен с адрес входами блока формирования млад ших адресов и блока формирования старших адресов и информационным входом дешифратора, выход которого подключен к первым входам управлени pesuiMOM первого и второго коммутато ров стариих адресов, выходы которых соединены с адресными входами старших разрядов соответственно первого и второго блоков памяти, группа информационных выходов второго счет чика подключена к первым группам ин формационных входов первого и второ го коммутаторов младших разрядов и первой группе информационных входов блока форми5)ования младших адресов, rpimna информационных выходов с пер вого по ()-й третьего счетчика соединен с группой входов сдвига ад ресов с ()-ro по второй блока формирования адресов, с гру пой информационных входов с первого по (N -2)-и блока формирования стар ших адресов и группой ()-х информационных входов блока контроля четности, выход которого соединен с вторыми входами элементов И третьей группы, первыми входами элементов И

к входу сброса коррелятора, входу за- четвертой группы, восьмой и девятой

пуска блока- синхронизации, первому входу пятого элемента И и счетному входу второго триггера, выход которого соединен с -первым входом элемента ИСКПЮЧА1ОДЕЕ ИЛИ и с вторым входом первого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого СО0

5

0

5

0

5

0

5

единен с выходом пятого элемента И, выход первого элемента ИЛР1 соединен с N(-M разрядом (N. log. N, N - число частных кoppeлoгpa iм) входы сдвига адресов блока формирования младших адресов и счетным входом третьего счетчика, выход переполнеш я которого соединен с первым входом шестого элемента И, входом сброса блока формирования младиих адресов и установочным входом первого триггера, инверсный выход которого соединен с вторыми входами элементов И первой группы, а прямой - с вторым входом третьего элемента И, первыми входами элемента И шестой и седьмой групп, вторым входом пятого элемента И и вторым входом шестого элемента И, выход которого соединен со счетными входом первого счетчика, информацион- ньй выход которого соединен с адрес- входами блока формирования младших адресов и блока формирования старших адресов и информационным входом дешифратора, выход которого подключен к первым входам управления pesuiMOM первого и второго коммутаторов стариих адресов, выходы которых соединены с адресными входами старших разрядов соответственно первого и второго блоков памяти, группа информационных выходов второго счетчика подключена к первым группам информационных входов первого и второго коммутаторов младших разрядов и первой группе информационных входов блока форми5)ования младших адресов, rpimna информационных выходов с первого по ()-й третьего счетчика соединен с группой входов сдвига адресов с ()-ro по второй блока формирования адресов, с группой информационных входов с первого по (N -2)-и блока формирования старших адресов и группой ()-х информационных входов блока контроля четности, выход которого соединен с вторыми входами элементов И третьей группы, первыми входами элементов И

четвертой группы, восьмой и девятой

групп, с вторым входом управления режимом второго коммутатора старших адресов, с первым и вторым входами управления реж1-5мом соответственно второго и первого коммутаторов младших адресов, с вхрдом первого элемента НЕ и с вторым входом элемента ИСКЛЮЧАШЦЕЕ ИЛИ, выход которого подключей к второму входу второго элемента И и через второй элемент НЕ к второму входу четвертого элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого подключен к входу записи ; второго блока памяти, а второй вход 1 соединен с выходом третьего элемента I И и первым входом третьего элемента I ИЛИ, второй вход которого подключен I к выходу второго элемента И, а выход I соединен с входом записи первого бло I ка памяти, ()-й информационньш I выход третьего счетчика соединен с I ()-Mn информационными входа ш блока контроля четности и блока фор- I мирования старших адресов, выход ко- I торого подключен к информационным i входам первого.и второго коммутаторо старш1х адресов, выход первого эле- г мента НЕ соединен с вторьм входом Л управления режимом первого коммутато I ра старших адресов, с вторым и пер- ; вым входами управления ре ;ашом соот- : ветственно второго и первого коммута ; торов младших адресов, вторыми входами элементов И второй группы, первы- ; ми входами элементов И пятой группы, десятой и одиннадцатой групп, выходы : элементов И первой группы подключены к первым входам элементов ИЛИ третье и четвертой групп, выходы которых соединены с информационными входами соответственно первого и второго бло ков памяти, группа информационных ; ВЫХОДОВ nejjBoro блока памяти подклю- j4eHa к вторым входам элементов И четвертой группы, группа информационных выходов второго блока памяти соединена с вторыми входами элементов И пятой группы, второй выход блока синхронизации соединен с вторым информационным входом блока формирования младших адресов и первым входом четвертого элемента ИЛИ, второй вход которого соединен с третьим выходом б;лока синхронизации, а выход - с входом управления режимом блока формирования младших адресов, группа выходов которого соединена с группами вторЬЕХ информационных входов первого и второго коммутаторов младших разрядов, выходы которых подключены к адресным входам младших разрядов соответственно первого и второго бло- ков памяти, выход четвертого элемен- та ИЛИ соединен с тактовыми вxoдa И первого, второго и третьего регист

Q 5 Q 5 5

0

5

0

5

0

ров блока вычисления сумм частных коррелограмм, в блоке вычисления сумм частных коррелограмм выход первого регистра соединен с первыми входами первого сумматора и информационными входами второго регистра, выход которого соединен с первым входом второго сумматора, выход третьего регистра соединен с вторыми входами первого и второго сумматоров, выход элементов 1-ШИ первой группы соединен с информационным входом третьего регистра блока вычисления сумм частных коррелограмм, выход элементов ИЛИ второй группы поключен к информационному входу первого регистра блока вычисления сумм частных коррелограмм, группа выходов первого су1-1матора, блока вычисления сумм частных коррелограмм соединена с вторыми входами элементов И шестой группы, выходы которых подключены к вторым входам элементов И девятой и десятой групп, группа выходов второго сумматора блока вычисления сумм частных коррелограмм подключена к вторым входам элементов И седьмой группы, выходы которых соединены с вторыьга входами элементов И восьмой и одиннадцатой групп, выходы элементов И восьмой и девятой групп соединены с вторыми .входами элементов ИЛИ соответственно третьей и четвертой групп, выходы элементов И десятой и одиннадцатой групп соединены с третьими входами элементов ИЛИ соответственно третьей и четвертой групп.

рая группа которого является первым информатдионным входом блока, вход переноса сумматора является вторым информационным входом блока, а выход сумматора является вькодом блока.

3, Устройство по п.1, о т л и - чающееся тем, что блок формирования старших адресов содержит г группу мультиплексоров на N канала каждьй, причем -адресные входы мультиплексора являются адресными входами блока, (q+1)-fi информационньш вход q-ro мультиплексора подклкг- чен к шине нулевого потенциала, инг формационные входы с первого по q-й q-ro мультиплексора подключены соответственно с q-ro по первый к информационным входам блока, а информационные входы с (q+2)-ro по q-ro мультиплексора, кроме ()-ro муль- типлексора, подключены к (N--q-l)-My информационному входу блока, выходы мультиплексора являются выходами блока.

Ри.2

9иг.З

9uz.

9иг.

ив. б

R{7)

Фи,г.7

U2.S

ж

Ж

Авторы

Даты

1988-10-23—Публикация

1987-04-06—Подача