мационным входом сумматора, перв.ым входом компаратора и является информационным входом блока, выход регистра соединен со вторым информационным входом сумматора и вторым входом компаратора, выход которого соединен с управляющим входом сумматора вход которого является выходомблока..

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелометр | 1982 |

|

SU1026144A1 |

| Коррелометр | 1984 |

|

SU1171806A1 |

| Многоканальный релейный коррелометр | 1982 |

|

SU1062718A1 |

| Многоканальный релейный спектроанализатор | 1983 |

|

SU1140129A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Генератор случайных чисел | 1988 |

|

SU1599856A1 |

1. КОРРЕЛЯТОР, содержащий (h + .1)разрядный счетчик, выходы младших разрядов которого соединены с соответствующими адресными входами блока постоянной памяти и первого блока памяти, выход (п -1)-го разряда счетчика соединен с входом переключения режима первого сумматора, вход счетчика объединен с входом синхронизации первого сумматора, с входом управления записью первого блока памяти и подключен у. выходу генератора тактовых импульсов, выходы -X разрядов счетчика (где i п -т , п -1) соединены с соответствующими младшими адресными входами записи второго блока памяти, вход управления записью которого подключен к выходу (п-т-1)-го разряда счетчика, старшие адресные входь записи и чтения второго блока памяти соответственно подключены к прямому и инверсному выходам п -го разряда счетчика, младшие адресные выходы чтения второго блока памяти подключены к соответствующим выходам блока постоянной памяти, выход второго блока памяти соединен с первым информационным входом первого сумматора, второй информационный вход ко- % торого подключен к выходу первого блока памяти, отличающийс я. тем, что, с целью расширения функциональных возможностей за счет одновременной работы с двумя . опорными сигналами, в него введены второй сумматор, регистр и блок сглаживания, вход синхронизации которого подключен к выходу (п-1)го разряда счетчика, информацион(/) ный вход блока сглаживания подключен к выходу первого блока памяти, выход блока сглаживания является выходом коррелятора, выход первого сумматора соединен с информационным входом регистра, управляющий вход которого подключен к выходу генератора тактовых импульсов , выход регистра соединен с информационным входом первого блока памяти, выход второго сумматора соединен с информационным входом второго блока памяти, управляющий вход и информационные входы второго сумматора являются соответствующими разрядными информационными входами коррелятора. 2. Коррелятор по п. 1, отличающийся тем, что блок сглаживания содержит сумматор, компаратор и регистр, вход синхронизации которого является входом синхронизации блока, информационный вход регистра объединен с первым инфор

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано в системах автоматического управления для обнаружения опорных частотно-модулированных сигналов в анализируемом случайном сигнале.

Цель изобретения - расширение функциональных возможностей за счет одновременной работы с двумя опорными сигналами.

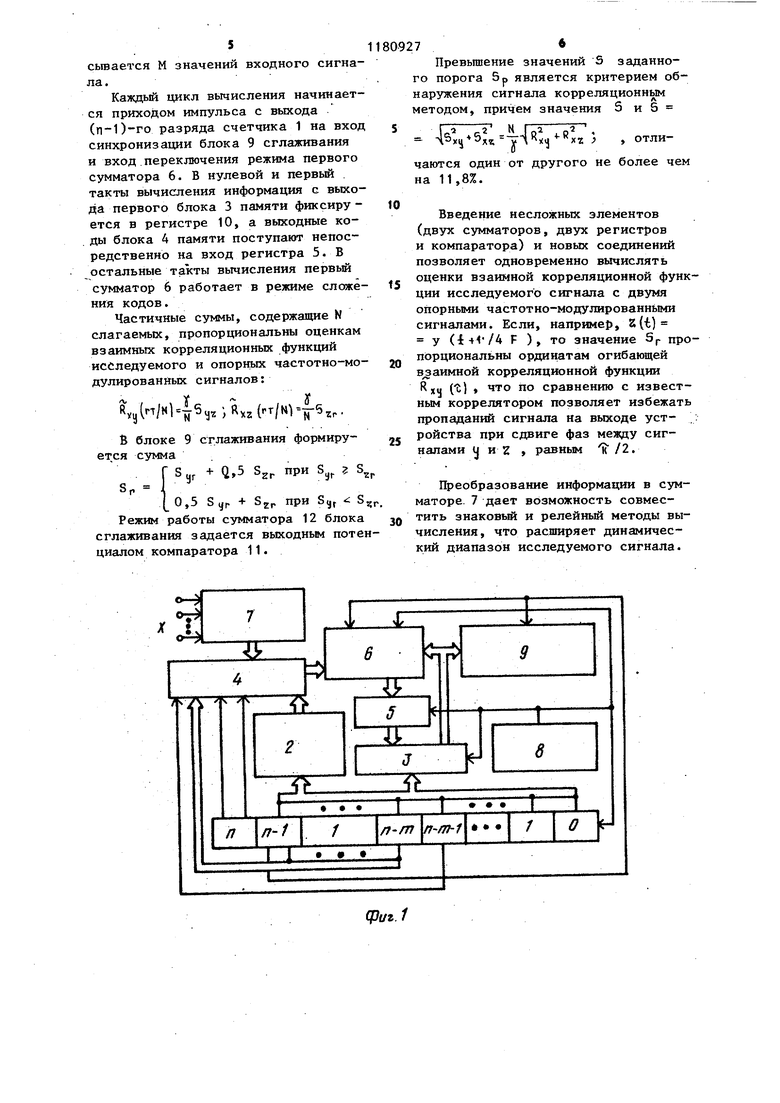

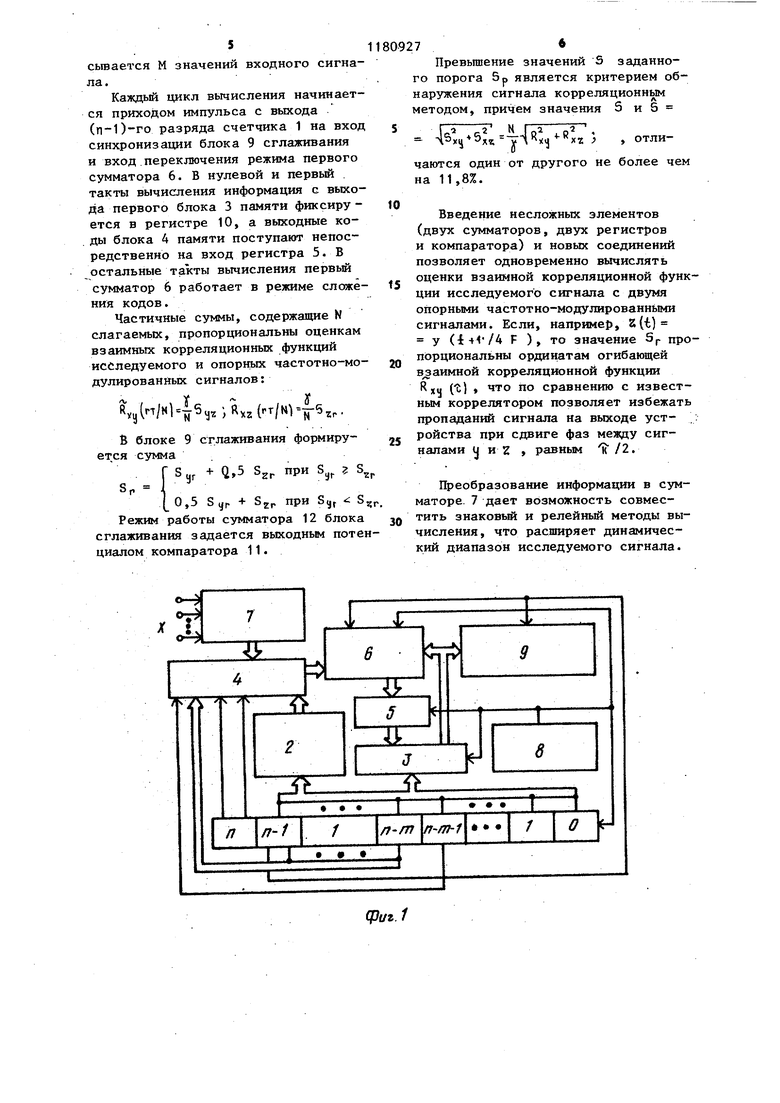

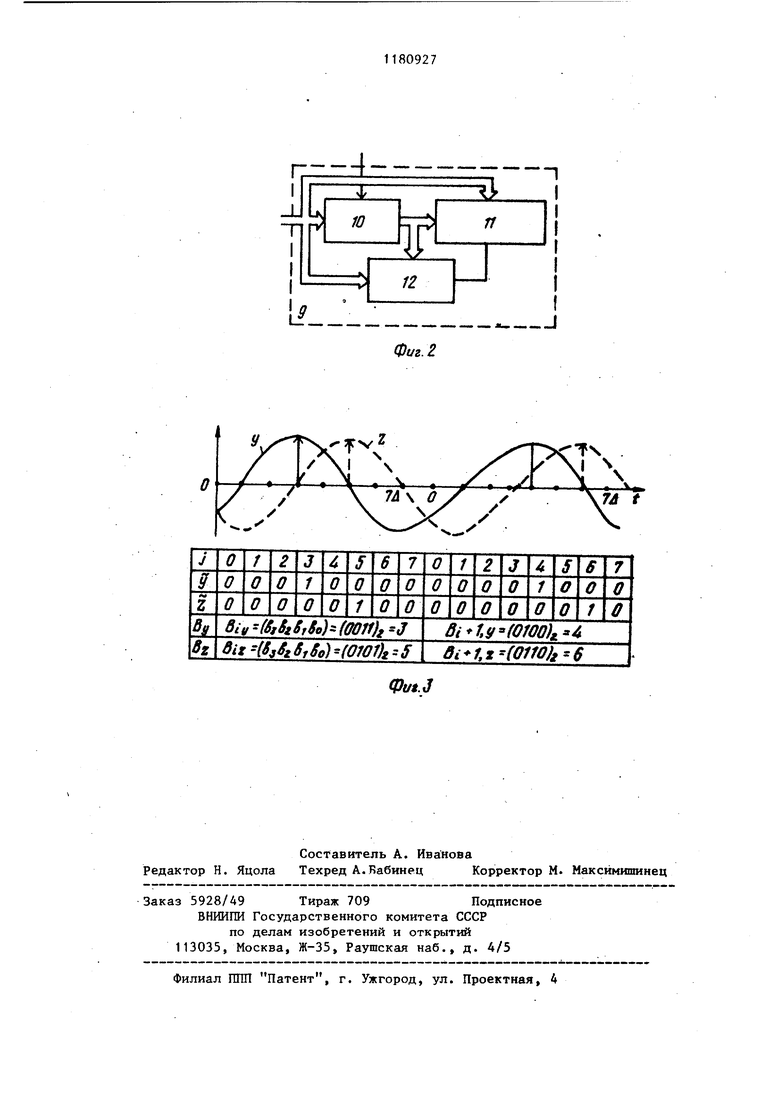

На фиг. 1 представлена структурная схема коррелятора; на фиг. 2 структурная схема блока сглаживания; на фиг. 3 - процесс формирования констант опорных сигналов.

Коррелятор содержит счетчик 1, блок 2 постоянной памяти, первый 3 и второй 4 блоки памяти, первьй регистр 5, первый 6 и второй 7 сумматоры, генератор 8 тактовых импульсов и блок 9 сглаживания, который содержит регистр 10, компаратор 11 и сумматор 12.

Последовательность значений вход ного сигнала х pj (xoXt ... х), где j О, (М-1), г О, 1,2,..., подается на вход устройства, причем младшие разряды входных чисел поступают на соответствующие информационные входы сумматора 7, а старший разряд X );,, - на вход управления сумматора 7, выход которого подключен к информационном входу второго блока 4 памяти, управляющий вход и адресные входы которого подключены соответственно к выходам счетчика 1 и блока 2 постоянной памяти, адресные входы которого объединены с адресными входами первого блока 3 памяти и соответственно соединены с выходами п младших разрядов счетчика 1, выход (п-1)-го разряда которого подключен к входу переключения режима сумматора 6 и входу синхронизации

регистра 10, а вход счетчика 1 соединен с выходом генератора 8 тактовых импульсов, входом синхронизации регистра 5 и управляющим входом блока 3 памяти, информационный вход которого через регистр 5 подключен к выходу первого сумматора 6, первый информационный вход которого соединен с выходом блока А памяти, а второй информационный вход сумматора 6 подключен к выходу блока 3 памяти, информационному входу регистра 10 блока сглаживания, первому, входу компаратора 11 и первому информационному входу сумматора 12, вход которого соединен с выходом компаратора 11, управляющий второй вход которого подключен к выходу регистра 10 и второму информационному входу сумматора 12, вход синхронизации регистра 10 является входом синхронизации блока, вЬкод компаратора соединен с управляющим входом сумматора 12, выход которого является выходом блока 9 сглаживания.

Коррелятор работает следующим образом.

В четные (т +1)-разрядные ячейки памяти блока 2 постоянной памяти записьшаются N чисел В,- (Ъд, Ъ, ..., bm)2 , характеризующих опорный сигнал у sin t2ir Ft + (t)3 , a в нечетные ячейки - N чисел Bj (Ь , Ь, .. . Ьщ )г соответствующих опорному сигналу б)г 2nFt+ S(t). Для формирования чисел в опорные сигналы длительности Т квантуются по времени с частотой f, , где fo - частота следования импульсов с выхода генератора 8 тактовых импульсов. Полученные отсчеты опорных сигналов разбиваются на N блоков по М 2 ординат. Эти ординаты квантуются на два уровня:

J(,npMy(M;tjVt.i)(AA-4JtO/{,i о .R остальных случаях

l,npM2(M;.j)/i,5;(M;+jtO/{,z;;

0 - и о.стальных случаях

Если у,- 1 (2- 1), то j . ( Ьо Ь, ... Ь., )j,bfn 1 . Если в i-oM блоке все числа () равны то В; 0. Процесс формированулю, „,

ния чисел В-- г. ,, , и В:„ , которые характеризуют наличие и расположение

максимумов опорных частотно-модулярованных сигналов в | -м блоке,

для М 8, {, 8 F изображен на

фиг. 3.

Исследуемому центрированному случайному сигналу -AUo X А UQ , где д -1, соответствует двоичный код X ( , .. . XK,,) . .

Во втором сумматоре 7 формируются числа

Гх-А-1, I

.1 Гх-А-1. при X 6 А, 1 Х-А, I при X 7 А.

Режимы работы сумматора 7 задаются значением старшего разряда двоичного числа X. Такое преобразование информации позволяет перевести входные числа в дополнительный код, что исключает выполнение операций вычитания в устройстве и дает возможность совместить два метода вычисления: знаковый при /X(t)/(Jg , и релейный при других X, что позволяет обнаруживать малые сигналы без увеличения разрядности входных чисел. В таблице приведены значения чисел X и X при к 3.

1809274

Значение X записывается с частотой fj во второй блок 4 памяти, который содержит 2М к-разрядных ячеек памяти. Одновременно из зто5 го блока производится чтение информации с частотой QQ ,, при зтом М/{, 2N Так как старшие адресные входы записи и чтения блока А памяти подключены соответственно 10 к прямому и инверсному выходам

П-го разряда счетчика 1, то запись и чтение производится поочередно из разных половин блока 4 памяти. Константы В|, поступая с выхода блоf5 ка 2 постоянной памяти на младшие адресные входы чтения блока 4 памяти, считывают из ячеек памяти значения Х|.д, т.е. на выходе блока 4 памяти однотактной -операцией формируются суммы

20

М-1

(4-)j

X

J

Sb() )i nH -N25

в первом сумматоре 6 формируются частичные суммы

30

ЧП1Ч-0

S

УЧ

«U-i) + С.

S

zrffi-ll rfu-it ) .

которые записываются соответственно в четные и нечетные ячейки первого блока 3 памяти, причем номер

5 четной или нечетной ячейки памяти совпадает с номером частичной суммы, расположенной в ней. При добавлении слагаемого к частичной сумме

0 . с номером о она перемещается в ячейку блока 3 памяти с номером ( + 1), равному количеству слагаемых в частичной сумме. Блок 3 памяти работает в режиме чтения, когда выходные импульсы генератора 8

5 тактовых импульсов ТИО 1, ив режиме записи при нулевых значениях этих импульсов. Считанная из блока 3 памяти информация сохраняется

0 на его выходах до прихода следующего тактового импульса. Отрицательный фронт импульса ТИО записывает информацию с выхода первого сумматора 6 в регистр 5. За один цикл вычисления (2N тактов) в пер5вом сумматоре 6 к каждой частичной сумме добавляется одно слагаемое. За :зто время в блок 4 памяти запи5сьгоается М значений входного сигнала. Каждьй цикл вычисления начинается приходом импульса с выхода ()-го разряда счетчика 1 на вход синхронизации блока 9 сглаживания и вход переключения режима первого сумматора 6. В нулевой и первый такты вычисления информация с выхода первого блока 3 памяти фиксируется в регистре 10, а выходные коды блока А памяти поступают непосредственно на вход регистра 5. В остальные такты вычисления первый сумматор 6 работает в режиме сложения кодов. Частичные суммы, содержащие N слагаемых, пропорциональны оценкам взаимных корреляционных функций исследуемого и опорных частотно-модулированных сигналов: ( / -|fi блоке 9 сглаживания формирует.ся сумма + й,5 Sg при S S, 0,5 S + Sgp при Sy, S Режим работы сумматора 12 блока сглаживания задается выходным потен циалом компаратора 11.

«

Ж

iV

7

/7-//

/7

I Г 4

71

ЗЕ

АУ

JF

rin

n-ffh1 /

/7-/7Г

(Риг.1 76 Превьшение значений S заданного порога 5р является критерием обнаружения сигнала корреляционным методом, причем значения 5 и 6 1 ,R , yij xz у чаются один от другого не более чем на 11,8%. Введение несложных элементов (двух сумматоров, двух регистров и компаратора) и новых соединений позволяет одновременно вычислять оценки взаимной корреляционной функции исследуемого сигнала с двумя опорными частотно-модулированньми сигналами. Если, например, Z(-t) у ( F ), то значение 5 пропорциональны ординатам огибающей взаимной корреляционной функции xtj СЬ) что по сравнению с известным коррелятором позволяет избежать пропаданий сигнала на выходе устройства при сдвиге фаз между сигналами у и z , равным it/2. Преобразование информации в суматоре. 7 дает возможность совмесить знаковый и релейный методы выисления, что расширяет динамичесий диапазон исследуемого сигнала.

Фигг

(put.J

| Цифровой коррелятор для обнаружения эхо-сигналов | 1976 |

|

SU642713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коррелометр | 1982 |

|

SU1026144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-03-05—Подача