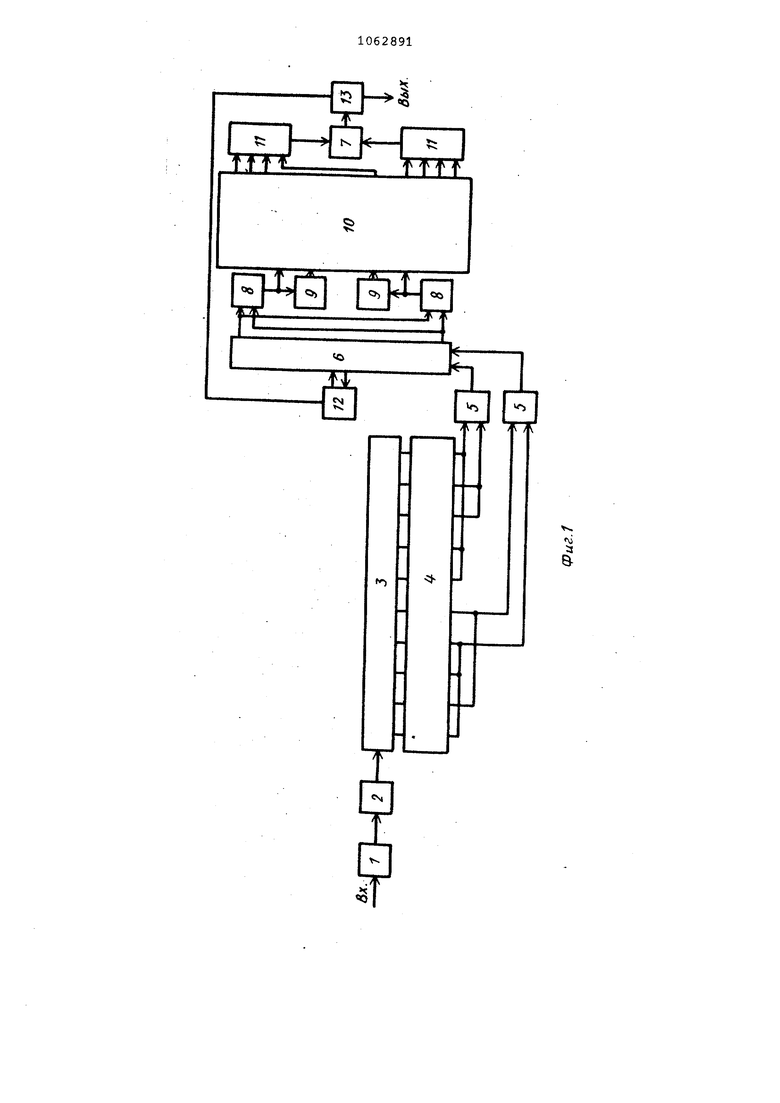

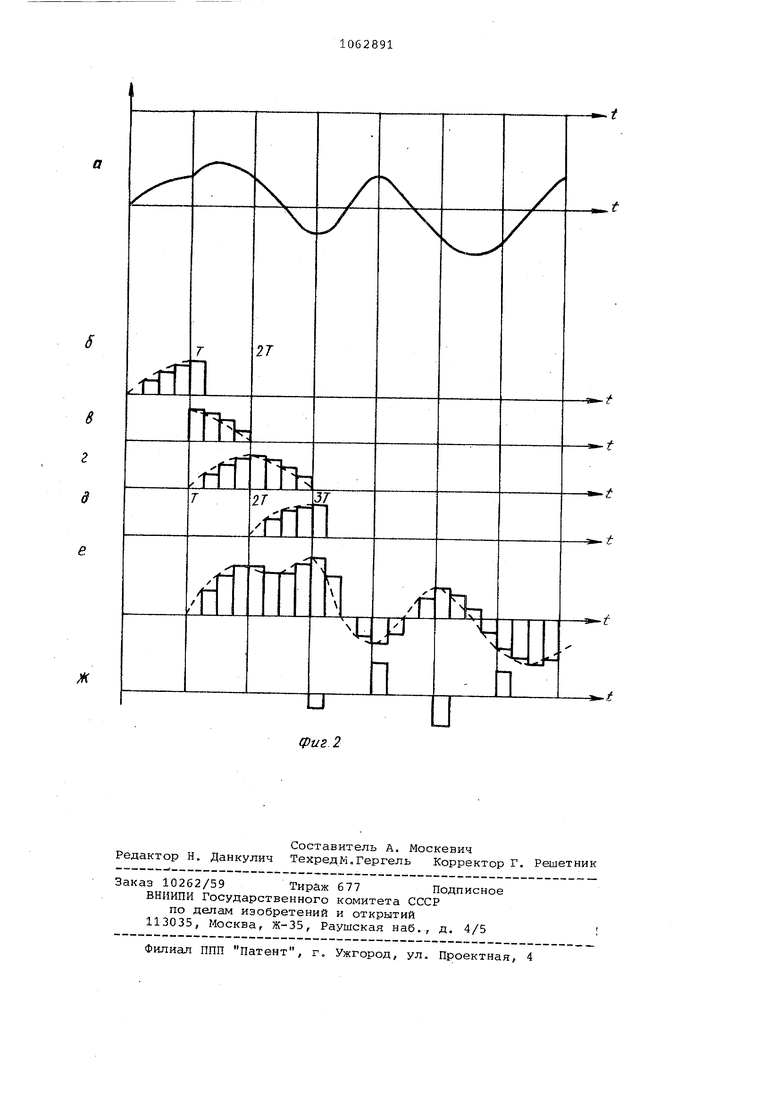

Изобретение относится к техник связи и может использоваться для когерентной высокоскоростной обра ботки сигналов с фазовой манипуля цией в условиях межсимвольной инт ференции. Известен оптимальный демодулят содержащий входные полосовые филь ры, входные ключевые элементы, бл синхронизации, линию задержки, взвешивающие блоки, промежуточные ключевые блоки и блоки выделения огибающей, причем выходы входных полосовых фильтров подкльэчены к Входам входных ключевых элементов которые осуществляют временную ди кретизацию сигналов, при этом рабо той ключевых элементов управляет блок синхронизации, а сигналы с выходов входных кл этевых элементо объединяются и поступают на вход линии задержки к отводам которой подключены вертикальные шины взвеш вающих блоковJкоэффициенты переда чи которых пропорциональны выбороч ным значениям импульсных реакций фильтров, согласованных с обрабатываегллми сигналами, причем горизонтальные шины блоков взвешивания подключены к входам промежуточных ключевых блоков, выходы которых объединены и подключаются к двум входам блоков выделения огибающей f . Однако данный демодулятор имеет низкое быстродействие. Наиболее близким техническим реиением к изобретению является демодулятор дискретных сигналов, содержаний последовательно соединенные полосовой фильтр, дискретизатор и первый элемент задержки выходы которого подключены к входа блока взвешивания, выходы которого соединены с входами операционных усилителей, а также первый сумматор, выход которого подключен к первому входу решающего блока 2j Однако известный демодулятор имеет низкое быстродействие при демодуляции сигналов с фазовой манипуляцией . Цель изобретения - повышение быстродействия при демодуляции сигналов с фазовой манипуляцией. I Поставленная цель достигается тем, что в демодулятор дискретных сигналов, содержаний последователь НС соединенные полосовой фильтр, длскретизатор и первый элемент задержки, выходы которого подключены к входам блока взвешивания, выходы которого соединены с входами операционных усилителей, а также первый сумматор, выход которого подключен к первому входу решающего блока, введены второй суГФлатор, инверторы, второй элемент задержки, блок компенсации, блоки выбора максимального напряжения и дополнительные сумматоры, выходы которых подключены к входам соответствующих инверторов, выходы которых соединены с одними входами блока компенсации, другие входы которого соединены с выходами дополнитель)ых суг/1маторов, к вкодам которых подключены одни выходы второго элемента задержки, входы и другие выходрл которого соединены соответственно с выходами операционных усилителей и с входами второго сумматора, выход которого подключен к второму входу решающего блока, при этом выходы блока ко14пенсации соединены с входами соответствующих блоков выбора максимального напряжения, выходы которых подключены к входам первого сумматора. На фиг.1 представлена блок-схема предлагаемого демодулятора на Фиг.2 - эпюры напряжений, поясняющие его работу. Демодулятор дискретных сигналов содержит полосовой фильтр 1, дискретизатор 2, первый элемент 3 задержки, блок 4 взвешивания, dnepaционные усилители 5, второй элемент 6 задержки, первый сум латор 7, дополнительные суглматоры 8, инверторы 9, блок 10 компенсации, блоки 11 выбора максимального напряжения, второй cyt-uviaTop 12, решающий блок 13. Демодулятор работает следуклдим образом. Непрерывный сигнал с фазовой манипуляцией (основаниеалфавита поступает через полосовой фильтр 1 на дискретизатор 2, на выходе которого формируются последовательности импульсов с амплитудами, пропорциональными выборочным значениям сигнала в соответствующие моменты вpeмeниkt (, 2 ,. . .) . Эти последовательности импульсов поступают На вход первого элемента 3 задержки. К выходаг- первого элемента 3 задержки подключен блок 4 взвешивания, коэффициенты передачи которого пропорциональны выборочны1«1 значениям имтульсной реакции фильтра 1, согласованного с одиночный, ограниченным по спектру, сигналом с фазовой манипуляцией. Выходы блока 4 взвешивания подключены к входам операционных усилителей 5. На выходах операционных усилителей 5 формируются две части импульсного отклика (на интервгшах времени О 1йТи 2Т)на входное воздействие. Выходы операционных усилителей 5подключаются к входам второго эл мента 6 задержки. Запись информации в ячейки памяти второго элемента 6 задержки монет осуществлят ся либо параллельно (двухтактная линия), либо последовательно, то с одного входа линии,, то с другого. При интервале анализа сигнала TO. 2т второго элемента 6 задержки имеется с ячеек памяти четыре отвода. К выходам средних отводов подключены соответствующий дополнител ный сумматор О и инвертор 9, на вы ходе которого формируется импульс ный отклик на всем интервале анализа О : t 2Т, состоящий из суммы двух частей отклика на интервалах О t. 2Т и . При этом все время задержки второго элемента 6задержки, составляет 2Т (от пер вого отвода до среднего отвода и от среднего отвода до послед него -i-2, Т) . К выходам крайних отводов втор го элемента б задержки подключены другой дополнительный cy viaTop 8 и инвертор 9, при помощи которых формируются всевозможные комбинации импульсных откликов, соответст вующих различным комбинациям предыдущих и последующих символов. Таким образом, на ВЕЛходе второго сумматора 12 формируется отклик н ансшизируемый символ (с задержкой на время т и при интервале ан лиза Тд :2т) , а на двух крайних отводах второго элемента б задерж отклики от опережающего символа и от отстающего символа (на интерва лах анализа ). Для реализации оптимального ал ;горитма обработки сигналов с фазовой манипуляцией необходимо учитывать (кортпенсировать) отличие в энергиях приходящих, интерферирующих между собой, сигналов. Компенсация этой энергии, в зависимости от различного чередования предыдущих и последующих симво лов, осуществляется в блоке 10 ком пенсации путем взвешивания или добавления различных коэффициентов к напряжениям на выходах допол нительных сумг аторов 8 и инверторов 9. Таким образом, результаты работы анализируемого сигнала, а так же по отдельности - предыдущих и последующих сигналов, поступают, с одной стороны, на рещ ающий блок 13 и, с другой стороны, на блоки 11 выбора максимального напряжения При этом на блоках 11 осуществляет ся выбор максимального сигнала из совокупности всевозможных чередова ний лишь предыдущих и последующих сигналов. Каждый из . блоков 11 выбора максимального напряжения выбирает максимальное напряжение с учетом как положительной полярности полезных сигналов, так и отрицательной полярности полезных сигналов. С выходов блоков 11 в моменты времени КТ (,2,..,) на входы первого сумматора 7 поступают два максимальных напряжения (при этом одно противоположной полярности) и на выходе формируется напряжение разности. Физический смысл этого напряжения состоит в том, что оно представляет собой уровень компенсации влияния предыдущих и последукяцих символов на анализируемый. При этом учет влияния осуществляется в соответствии с оптимальным алгоритмом выбора максимально достоверного сигнала (в данном случае применительно к максимально достоверному чередованию предыдущих и последующих символов) . Напряжение с выхода первого сумматора 7 поступает в качестве порогового напряжения на второй вход решающего блока 13, на котором осуществляется сравнение уровня сигнала, соответствующего отклику на анализируеГОлй сигнал (на интервале времени To,2TJ с пороговым значением, сформированным из всевозможных чередований . предыдущих . и последу ощих сигналов. На вь.ходе решающего блока 13 формируется напряжение положительной или отрицательной полярности (.в виде пpямoyгoль ыx импульсов) , применительно к сигналам с фазовой манипуляцией и с интервалом следования Т . Рассмотрим работу предлагаемого демодулятора при следующих .параметрах: В1-Щ манипуляции - фазовая (ni 2); количество ячеек памяти первого элемента 3 задержки на интервале времени Т равной h 4, интервал анализа T( вид ограниченного по |Спектру сигнала ,интерференция распространяется на один предыдущий и один последующий сигнал. Непрерывный, ограниченный по поосе, сигнал (фиг.2а) поступает на вход дискретизатора 2, с помоью которого превращается в последовательность импульсов с амплитудами, равными выборочным значениям сигнала в моменты времени {. - (сС (, 2 ,,..). Выборочные значения сигнала продвигаются по ячейкам па- яти первого элемента 3 задержки в качестве которого используется искретно-аналоговая линия задержки. Количество ячеек первого элемента задержки равно N 8, При этом ячейки с первой по четвертую первого элемента -3 задержки подключены к соответствуьадим входап блока 4, на выходе которого будет импульсный отклик (фиг.Зо) сигнала 9,

Mt) Y(),

т t

(0 - t т) , а ячейки с пятой по восьмую - к другим соответствуюцим входам блока 4, на выходе которого будет импульсный отклик (фиг.2в сигнала ,(i -- C i--lV.

т

Как видно из временных диагра№-1 (фиг. 26 ,в)сумма этих двух импульсных откликов представляет собой полный отклик фильтра, согласованного с сигналом. LI (t на интервале анализа О t. Для сигналов с фазовой манипуляцией (L,(l)«-,) можно показать, что алгоритм оптимальной обработки в условиях межсимвольной интерференции сводится к вычислению значения функции корреляции сигнала 1, i с входным сигналом (фиг.2а) в моменты времени КТ (, 2 , . . .)и сравнению этих значений с пороговым уровнем, который определяется, как результат всевозможных комбинаций предыдущих и последующих сигналов. Для определения этого порогового напряжения в предлагаемом демодуляторе используются соответствующие блоки, на которых осуществляется выбор максимального напряжения (для paccмaтpивae -lыx

сигналов с фазовой манипуляцией) с учетом сим1етричности отклика 1(1). При этом для перебора всевозмо хных комбинаций предыдущих и последующих символов (1 1 1,-1 1 1, 5 11-1, -11 -1) применяется задержка при помощи второго элемента б задержки сумг.1арного отклика сигнала Ц на время Т (фиг.2г). Второй элемент 6 задер;кки может пред0 ставлять собой двухтактную линию (выборочные значения поступают одновременно на два входа и параллельно продвигаются как бы по ячейкам двух линий, к двум средним от5 водам которой (с двух параллельных линий) подключен второй сумматор 12, а крайние отводы подсоединены к первой ячейке одной линии и k последней ячейке другой линии. Таким

0 образом, осуществляется задержка откликов (фиг.2б) на время 2Т (фиг.2д).

Осуществляя перебор комбинаций сигналов (фиг, 2в ,д):, На решающем

5 блоке 13 в соответствии с алгоритмом будет осуществляться сравнение напряжения (фиг.2е) и порогового напряжения (.фиг. 2 ж,При этом регистрируется символ 1, если

д напряжение (фиг.2е) в моменты времени КТ больие напряжения (фиг. 2 jx) и регистрируется символ -1, еели напряжение (фиг.2е) в моменты времени КТ меньше напряжения (фиг.2 ж).

Таким образом, такая реализация предлагаемого демодулятора дискретных сигналов применительно к сигналам с фазовой манипуляцией позволяет существенно увеличить быстродейст0 вие.

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор дискретных сигналов | 1979 |

|

SU788429A1 |

| Демодулятор дискретных сигналов | 1988 |

|

SU1603534A1 |

| Перестраиваемый демодулятор дискретных сигналов | 1986 |

|

SU1401637A1 |

| ДЕМОДУЛЯТОР МНОГОПОЗИЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2246794C1 |

| Демодулятор дискретных сигналов | 1990 |

|

SU1741285A1 |

| Квазикогерентный демодулятор сигналов манипуляции с минимальным сдвигом | 1987 |

|

SU1561214A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

| Устройство приема многочастотных сигналов | 1986 |

|

SU1327298A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ С ЧАСТОТНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙЛИ- '*"^<*"i'^.'''*>& г •'^••tA:'- «i"*" V•''i - *.V.'V/!'WOr..'EHTH04E;••cm | 1973 |

|

SU367562A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

ДЕМОДУЛЯТОР ДНСКРЕТНЬК СИГНАЛОВ, содержащий последовательно соединенные полосовой фильтр, дискретизатор и первый элемент задержки, выходы которого подключены к входам блока взвешивания, выходи которого соединены с входами операционных усилителей, а также первыйсумматор, выход которого подключен к первому входу решающего блока, отличающий с я тем, что, с целььз повышения быстродействия при демодуляции сигналов с фазовой манипуляцией, введены второй сумматор, инверторы, второй элемент задержки, блок когшенсации., блоки выбора максимального напряжения и дополнительные сумматор -, выходы которых подключены к входам соответствующих инверторов, выходы которых соединены с одними входами блока компенсации, другие входы которого соединены с выходаг/1и дополнительных сумматоров, к входам которых подключены одни выходы второго элемента задержки, входы и другие выходы которого соединены соответственно с выходами операционных усилителей и с входами второго су1лматора, выход которого подключен к вто(Л рому входу решающего блока, при этом выходы блока компенсации соединены с входами соответствующих бло ков выбора максимального напряже ния, выходы которых подключены к входам первого сумгиатора.

fU

а Оа

гй:

лИ

37

т

27

Ж

,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Оптимальный демодулятор | 1973 |

|

SU468380A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Демодулятор дискретных сигналов | 1979 |

|

SU788429A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-12-23—Публикация

1982-10-20—Подача