Фи. 1

Изобретение относится к технике; связи и может быть использовано для когерентной обработки сигналов с фазовой манипуляцией в каналах с меяс- символьн9й интерференцией.

Цель изобретения - повьшение помехоустойчивости о

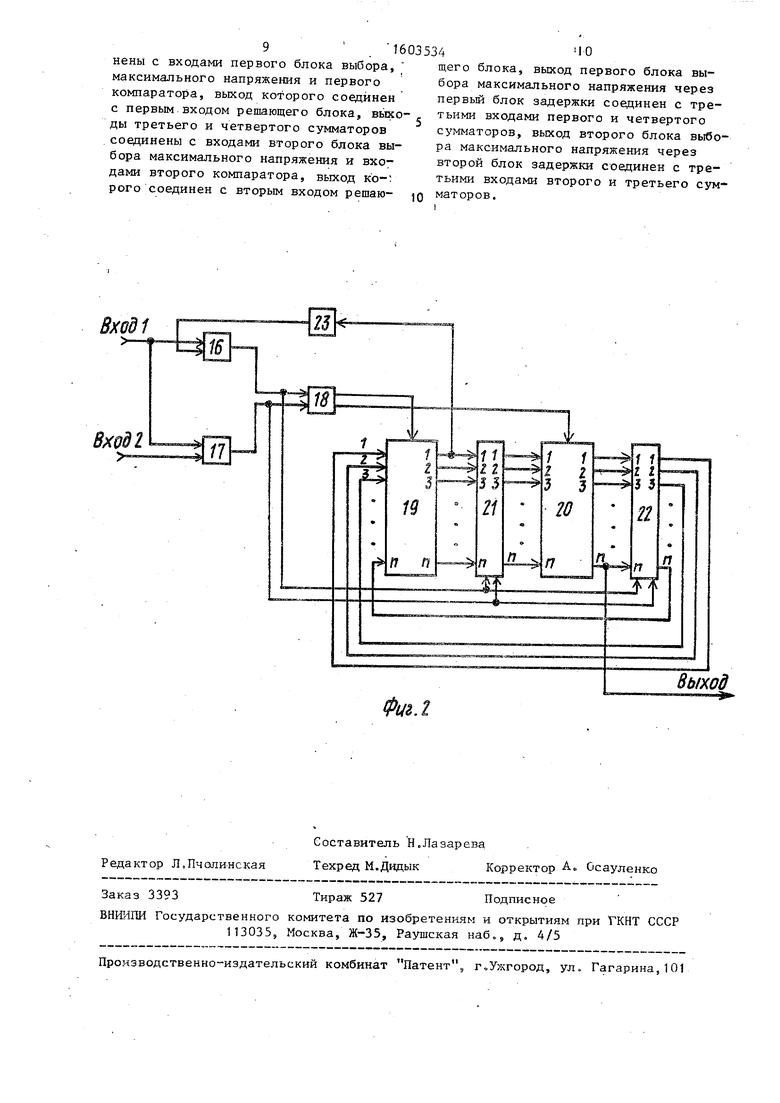

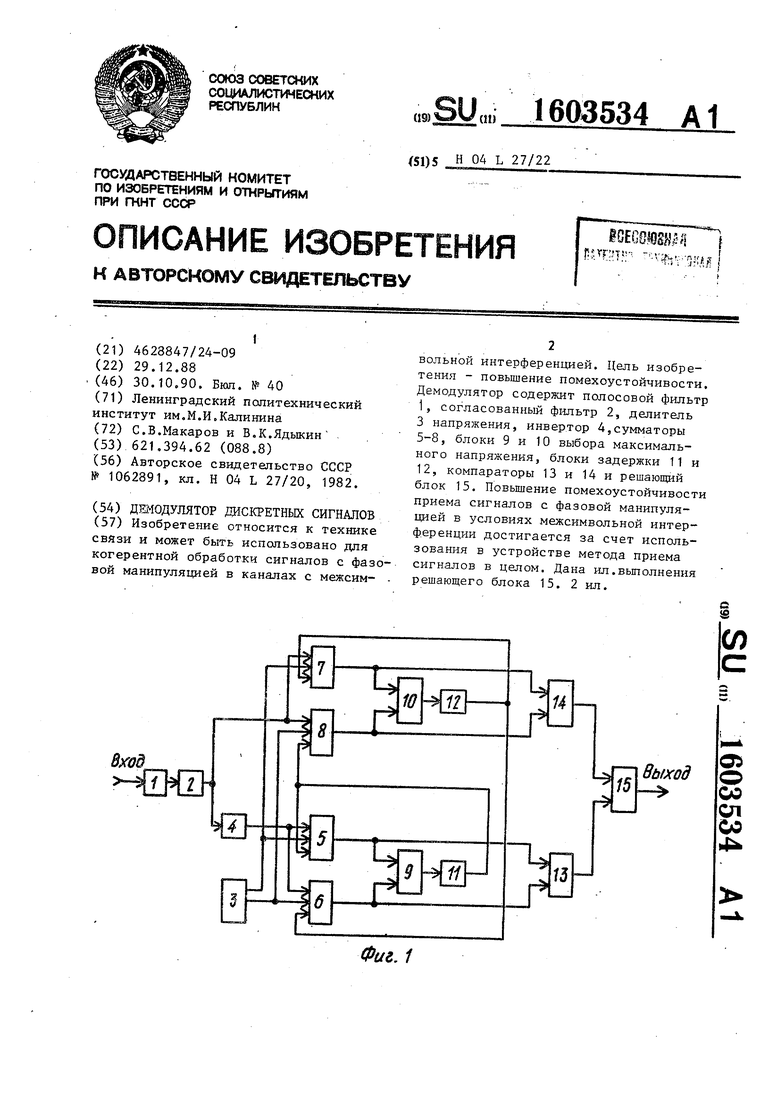

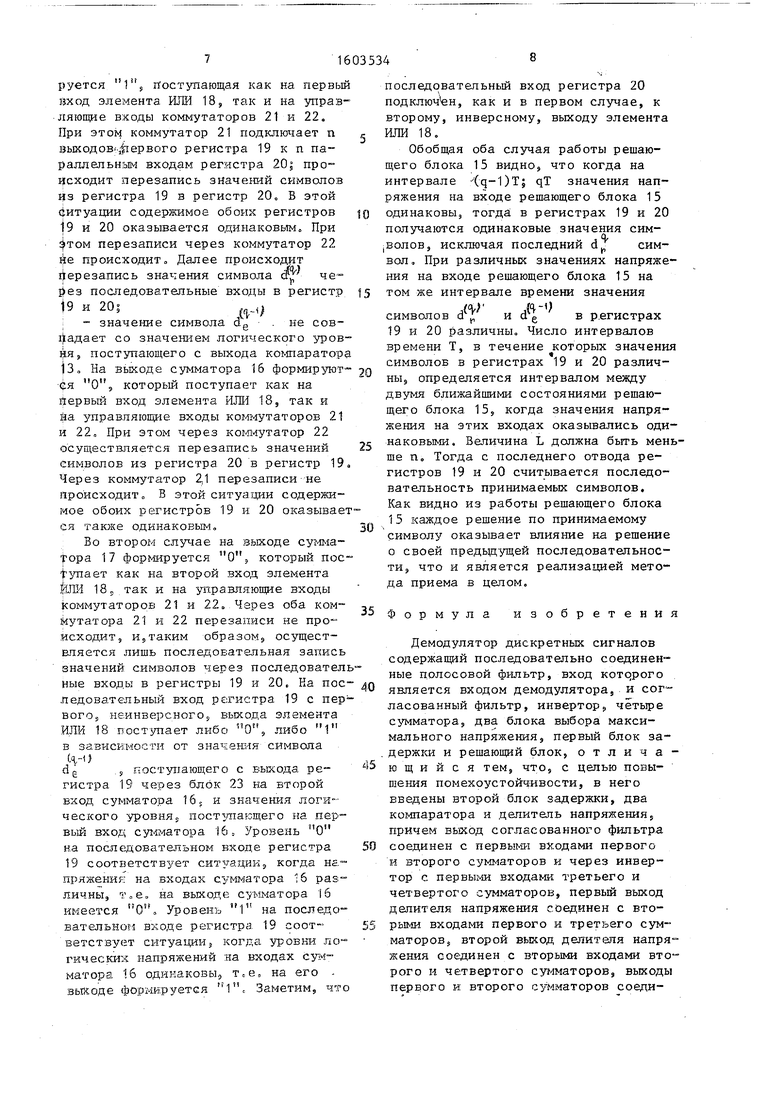

На фиг.1 изображена структурная электрическая предложенного демодулятора; на фиг.2 - схема решающего блока,

Демодулятор содержит полосовой 1, согласованный 2 фильтры, делитель 3 напряжения, инвертор 4, третий 5, четвертый 6, первый 7 и второй 8 сумматоры,, второй 9 и первый 10 блоки выбора максимального напряжения второй 11 и первый 12 блоки задержки,, второй 13 и первый 14 компараторы,, решающий блок 15, состоящий из первого 16 и второго 17 сумматоров по модулю два, элемента ИЛИ.18, первого 19 и второго 20 регистров, первого 21 и второго 22 коммутаторов и блока 23 задержки.

Демодулятор работает следующим образом.

Непрерывный сигнал с двоичной фазовой манипуляцией гшступает че- рез полосовой фильтр 1 на согласованный фильтр 2. Импульсный отклик этог фильтра согласован с формой одиночного сигнала длительностью 2То На выходе согласованного фильтра 2 формируется последовательность импульсов с амплитудами 5 пр опор изгонял ьными выброчным значениям свертки входного сигнала и импулъсног1 отклика этого фильтра,

Для .реализации метода приема в депом последовательности сигналов необходимо прежде всего произвести обработку тзыборочньк значений свертк в момент.; времени qT ,.,) по алгоритму,: макснмиэирующзму величину

(}

г . . (f,

{2 (2d;

1)х -c...

2(2d; -DC, (2d (1

(c.-0

-1)

i 1,2,

50

де -d - значение информационного символа,на интервале времени LCq-DT qT, , равное нулю при i 1 и равное еди- ,,.. ниде при i-2;

Х - значение свертки в моменты

времени q i ;; CQ н Ci- постоянные коэффициенты.

5 0 5

о д

5

50

Для реализации этого правила к выходу согласованного фильтра 2 подключены две пары сумматоров.первый - второй и третий - четвертый, В моменты времени qT на первые входы сумматоров 5 и 6 поступает инвертированное значение свертки X , В тот же момент времени на первые входы второй пары сумматоров с выхода согласованного фильтра 2 поступает неинвертированное значение . Делитель 3 напряжения, выполненный, например, в виде цепочки последовательно включенных резисторов с отводами, предназначен для формирования двух величин постоянного напряжения, пропорциональных значениям: -2C. -С Q и ь 2С -CQ, На второй вход сумматора 5 с выхода делителя 3 напряжения постук пает напряжение, пропорциональное величине -2Сц -Со, а на второй вход второго сумматора 6 - пропорциональное величине + ,

Формирование значений Wj (,2) при происходит с помощью сумматоров 5 и 6s блока 9 выбора максимального напряжения и блока 11, Значение (1 1,2) при формируется в тот же момент времени qT с помощью блоков 7 и 8, 10,1 2о В формировании значений W, и wC V участвуют величины W , полученные в предьдущий момент времени на выходах блока 9 (W ° ) и блока

10 (wf t- V ),

Рассмотрим формирование значений

.

С выхода блока 11 на третий вход сумматора 5 з момент времени дТ пост . тупает значение , На третий вход сумматора 6 с выхода блока 12 в этот же момент времени поступает значение

(-

W , Таким образом в момент времени qT на вькоде сумматора 5 формируется напряжение, пропорциональное вели(q) (Ч,) (q-) чине w / -2Х -2C,-Co+W, . аMI (в}

на выходе сумматора 6 -W / +

tIч

( 2C,-Cj+W- . Значения напряжения с

выходов пары сумматоров 5 и 6 поступают на входы блока 9, который и выбирает максимальное значение напряжения из дв5 поступивших на вход Это значение напряжения через блок 11, задержанное на время Т. поступает на третьи входы сумматоров 5 и 8 в момент времени (q-{-1)T. Значение напряжения с

Г ,

.

выходов сумматоров 5 и 6 поступают кроме того, на входы компаратора 1 на выходе которого форг шруется напжение, соответствующее либо О, л 1. При этом соответствует сиации, когда значение напряжения на выходе сумматора 5 больше значения напряжения на выходе сумматора 6. Аналогично формируется значение

На второй вход сумматора 8 вькода делителя 3 поступает напряжние, пропорциональное величине +2С

..

wW

-Ср, а на второй вход сумматора 7 - напряжение пропорциональное величин -2C CQ. Таким образом, на выходе сумматора 8 в момент времени qT фомируется напряжение, пропорциональное величине w , 2Х +2С ,-С„+

Г

2. t-OJ Og+ W ,а на выходе сумматора 7 в эт же момент времени - напряжение, пропорциональное величине w , 2х -2С,-Со +W

,(«V-)

С выходов сумматор

8 и 7 на входы блока 10 поступают напряжения, пропорциональные значениям W . Максимальное из двух потупивших на вход блока 10 значений напряжения через блок 12 поступает на третьи вход.1 сумматоров 6 и 7. Значения напряжений с выходов этих сумматоров поступают на входы компаратора 14, на выходе которого формируется напряжение, соответствующе либо О, либо 1, причем О соответствует ситуации, когда значение напряжения на выходе сумматора 8 боше значения напряжения на. выходе сумматора 7, Логические напряжения с выходов компараторов 13 и 14 постпают соответственно на второй и пер вьй входы решающего блока 15.

Две последовательности импульсов Которые получаются на выходе ком- параторов 13 и 14, определяют воз- можные сочетания переданных информационных символов. Так, О на вы- коде компаратора 13 на интервале времени (q-l)T; qT , соответствует

паре информационных символов I n л (л)

d d (0; 0)% а 1 единица на выходе компаратора 13 - паре .Н-О ,()

(IjO). В свою очередь,

О на выходе ко таратора 14 на том же интервале времени соответствует паре информационных символов

.( J4,

(0;1), а 1 на выходе

(V)

,W

компаратора 14 - паре d g d .

(1|1). Решающий блок 15 производит последовательный анализ этих пар информационных символов и определяет наиболее достоверную последовательность переданных символов в соответствии с алгоритмом приема в целом.

10

15

Рассмотрим два случая. В первом предполагается, что на интервале времени (q-1)T; qT на выходах обоих коьшараторов 13 и 14 напряжения по своей .полярности совпадают, т.е. имеется либо 1, что соответствует .ситуации когда символ , предшествующий данному d , однозначно определен и равен единице, 20 либо О, что соответствует ситуации

, (1- когда ае,, равен нулю. Для определеш-1я d ння

-,.„чf « -5.

115/;,полученных на поедьщ ущем интервале времени (q-2)T; (q-l)Tl Далее требуется на каждом интервале j()T; qT определить из пар сим.(q-zT /(1- волов dp, d , в которой

)

необходимо учесть значе- пары символов

d e - 4P;

25

f С (а ,1

30 последний символ

g совпадает по значению с первым символом следую- .(И ,HV

щей пары d

Во втором

предполагается, что напряжения на выходах компараторов 13 и 14 на ин5 тервале времени ()T;qT по своим значениям различаются, и в этих условиях значение символа однозначно определить невозможно.

Решаюший блок 15 работает следую0 щим образом.

В первом случае на выходе сумматора по модулю два 17 формируется 1, которая через элемент ИЛИ 18 поступает на последовательные входы регист5 ров 19 и 20, но ,на регистр 20 с инверсией. Кроме того, эта 1 поступает на управляющие входы коммутаторов 21 и 22. На второй вход сумматора 16 поступает задержанное на время

Т с помощью блока 23 значение симво-

0

,ла d.

, находящееся в регистре

19. Для первого случая возможны две,

ситуации:

- значеш-ш символа

,(-

совпадает со значением логического уровня, поступающего с выхода ко шаратора 13. Тогда на выходе сумматора 16 формируется 1, гУоступающая как на первый вход элемента ИЛИ 18, так и на управляющие входы коммутаторов 21 и 22. При этом коммутатор 21 подключает п 15ыходов -,|1ервого регистра 19 к п параллельным входам регистра 20j происходит перезапись значений символов из регистра 19 в регистр 20. В этой (Ситуации содержимое обоих регистров J9 и 20 оказывается одинаковым. При 4том перезаписи через коммутатор 22 происходит. Далее происходит 1)герезапись значения символа сг че™ jje3 последовательные входы в регистр i9 и 20|

д-

; - значение символа dg . не сов- 1 адает со значением логического уров йя, поступающего с выхода компаратор 13. На выходе сумматора 16 формируют фя который поступает как на йервый вход элемента ИЖ 18, так и иа управляющие входы коммутаторов 21 и 22. При этом через коммутатор 22 осуществляется перезапись значений символов из регистра 20 в регистр 19 Через коммутатор 2.1 перезаписи не Происходит. В этой ситуации содержимое обоих регистров 19 и 20 оказываеся таюке одинаковым.

Во втором случае на выходе сумма- Тора 17 формируется 0 % который пос фупает как на второй вход элемента ИЛИ 18, так и на з 1равляющие входы коммутаторов 21 и 22. Через оба ком- йутатора 21 и 22 перезаписи не происходит, и,таким образомэ осуществляется лишь последовательная запись значений символов через последователные входы в регистры 19 и 20. На последовательный вход регистра 19 с пер вого; неинверсного выхода элемента ИЛИ 18 поступает либо О, либо 1 в зависимости от значения символа

,4-

d

Р

поступающего с выхода регистра 19 через блок 23 на второй вход сумматора 16 s и значения логи-- ческого УРОВНЯ; поступающего на первый вход су14матора 16 Уровень О на последовательном входе регистра 19 соответствует ситуации, когда напряжения на входах сумматора 15 различны, т.е. на выходе сумматора 16 имеется О Уровень 1 на после,цо- вательнои входе регистра 19 соответствует ситуации; когда уровни ло™ гических напряжений на входах cyivi- матора 16 одинаковы, т.е, на его вькоде формируется 1. Заметим, что

)

5

последовательный вход регистра 20 подключ ен, как и в первом случае, к второму, инверсному, выходу элемента ИЛИ 18.

Обобщая оба случая работы рещаю- щего блока 15 видно, что когда на интервале (q-1)T; qT значения напряжения на входе рещающего блока 15 одинаковы, тогда; в регистрах 19 и 20 получаются одинаковые значения сим- |Волов, исключая последний dj символ. При различных значениях напряжения на входе решающего блока 15 на том же интервале времени значения

.v .. )

символов d

и d

в регистрах

0

5

0

19 и 20 различны. Число интервалов времени Т, в течение которых значения символов в регистрах 19 и 20 различны, определяется интервалом между двумя ближайщими состояниями рещающего блока 15, когда значения напряжения на этих входах оказывались одинаковыми. Величина L должна быть мень- ще п. Тогда с последнего отвода регистров 19 и 20 считывается последовательность принимаемых символов. Как видно из работы решающего блока 15 каждое решение по принимаемому символу оказывает влияние на решение о своей предьщущей последовательности, что и является реализацией метода приема в целом.

Формула изобретения

Демодулятор дискретных сигналов содержащий последовательно соединенные полосовой фильтр, вход которого

является входом демодулятора, и согласованный фильтр, инвертор., четыре сумматора, два блока выбора максимального напряжения, первый блок за- держки и решающий блок, о т л и ч а ю щ и и с я тем, что, с целью повышения псмехоустой-чивости, в него введены второй блок задержки, два компаратора и делитель напряжения, причем вькод согласованного фильтра

соединен с первы.ми входами первого и второго сумматоров и через инвертор с первыми входами третьего и четвертого сумматоров, первый выход делителя напряжения соединен с вторыми входами первого и третьего сумматоров, второй выход делителя напряжения соединен с вторыми входами второго и четвертого сумматоров, выходы первого и второго сумматоров соедийены с входами первого блока выбора, максимального напряжешя и первого компаратора, выход которого соединен

1603534

щего блока, выход первого блока вы бора максимального напряжения чере первый блок задержки соединен с тр

.i -j ouuTi vjjiuft задержки соединен с то

с первым.входом решающего блока, выхо- тьими входами первого и четвертого ды тоетьегп и иртпот т-г,, ,. и и четвертого

ды третьего и четвертого сумматоров соединены с входами второго блока выбора максимального напряжения и входами второго компаратора, выход ко-; рого соединен с вторым входом решаю10

сумматоров, выход второго блока выб ра максимального напряжения через второй блок задержки соединен с тре тьими входами второго и третьего су маторов.

, н

1603534

щего блока, выход первого блока выбора максимального напряжения через первый блок задержки соединен с тре.i -j ouuTi vjjiuft задержки соединен с то

тьими входами первого и четвертого i- и и четвертого

тьими входами первого и четвертого и и четвертого

10

сумматоров, выход второго блока выбора максимального напряжения через второй блок задержки соединен с третьими входами второго и третьего сумматоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор дискретных сигналов | 1990 |

|

SU1741285A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2005 |

|

RU2310978C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Система связи с относительной фазовой и фазоимпульсной модуляцией | 1987 |

|

SU1559421A1 |

Изобретение относится к технике связи и может быть использовано для когерентной обработки сигналов с фазовой манипуляцией в каналах с межсимвольной интерференцией. Цель изобретения - повышение помехоустойчивости. Демодулятор содержит полосовой фильтр 1, согласованный фильтр 2, делитель 3 напряжения, инвертор 4, сумматоры 5-8, блоки 9 и 10 выбора максимального напряжения, блоки задержки 11 и 12, компараторы 13 и 14 и решающий блок 15. Повышение помехоустойчивости приема сигналов с фазовой манипуляцией в условиях межсимвольной интерференции достигается за счет использования в устройстве метода приема сигналов в целом. Дана ил.выполнения решающего блока 15. 2 ил.

Sxodf

| Демодулятор дискретных сигналов | 1982 |

|

SU1062891A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-10-30—Публикация

1988-12-29—Подача