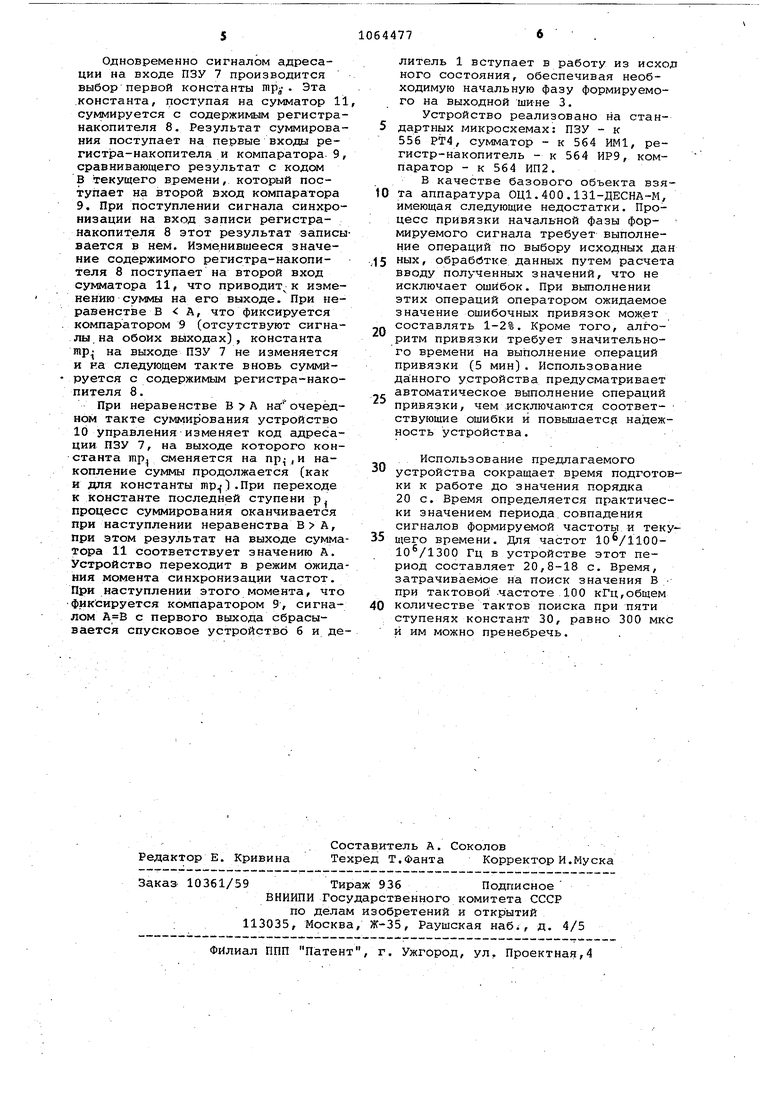

Изобретение относится к импульс ной технике и может использоваться для формирования последовательностей чередующихся когерентных СИ1- налов в устройствах автоматики и вычислительной техники. Делители с переменным коэффициентом деления, выпускаемые серийно в интегральном исполнении, наприме типа 155ИЕ8, 564ИЕ15 и др., при формировании импульсной последова-тельности не обеспечивают восстановление фазы сигнала при возвраще нии к ранее формированной частоте. Известен делитель частоты с пер менным, коэффициентом деления, содержащий декадный двоично-десятичный и управляющий десятичный счетч ки импульсов, переключатель кратно ти деления и элементы совпаденияС Устройство обеспечивает восстановление фазы сигналов при их чередовании, однако частоты формируемых сигналов находятся в кратном соотношении, что ограничивает облас его применения. Наиболее близким по технической сущностик предлагаемому являетсй делитель частоты с переменным коэффициентом деления, содержащий первый делитель часто1 ы/ управляющие входы которого соединены с шиной управляющего кода, а выход - с выходной шиной устройства, второй делитель частоты, вход которого сое динен с шиной входной частоты и пер вым входом первого делителя частоты спусковое устройство, первый/ и второй входы которого соответственно через первый и второй формирователи соединены соответственно с первыми вторым выходами второго делителя частоты, третий вход - с шиной командного сигнала# а выход с входом установки первого делителя частоты t23. Недостаток данного устройства заключается в невысокой эксплуатационной надежности, а именно: в возможности субъективных ошибок оператора в выборе момента перехода к новому значению частоты (сигнал подается на шину командного сигнала сяаибок при расчете и наборе нового значения фазы; и в большом времени подготовки, требующемся на расчет и ввод поправки. Цель изобретения - повышение надежности (эксплуатационной) и умень шение подготовки при смене частоты. Поставленная цель достигается тем, что в. делитель частоты с переменным коэффициентом деления,содержащий первый делитель частоты,управляющие входы которого соединены с шиной управлйющего кода, а выход с выходной шиной устройства, второй делитель частоты, которого соединен с шиной входной частоты, и спусковое устройство,введены программируемое запоминающее устройство (ПЗУ), регистр-накопитель, компаратор, устройство управления и сумматор причем первый вход спускового устройства -соединен с шиной вход- -ной частоты, выход - с входом первого делителя частоты, а второй, третий и Четвертый входы соединены соответственно с первым выходом устройства управления, выходом первого делителя частоты и первым выходом компаратора, второй выход которого соединен с входом управления устройства управления,кодовые входы которого соединены с шиной управляющего кода, а кодовые выходы -С шиной адресации ПЗУ,выход которого подсоединен к первому, кодовому входу сумматора, второй кодовый вход которого соединен с выходом регистра-накопителя,вход записи которого соединен с вторым выходом устройства управления, а кодовый вход -.с выходом сумматора и первым входом компаратора,второй вход которого соединен с выходом второго делителя частоты.. . Введение дополнительных элемен- тов обеспечивает повышение надежности и сокращение времени подготовки к работе устройства за счет автоматизации процесса привязки фазы формируемого сигнала путем отыскания момента совпадения соответствую щих сигналов первого и второг о делителей частоты и запуска первоТо делителя частоты соответственно это- му моменту. На чертеже приведена структурная схема устройства. Делитель частоты с переменным коэффициентом деления содержит первый делитель 1 частоты, управляющие входы которого соединены с шиной 2 управляющего кода, а. выход с выходной шиной 3 устройства, второй делитель 4 частоты, вход которого соединен с шиной 5 входной частоты, -спусковое устройство б, программируемое- запоминающее устройство (ПЗУ) 7, регистр-накопитель 8, компаратор 9, устройство 10 управления и сумматор 11, причем первый вход спускового устройства б соединен с шиной 5 входной частоты, выход - с входом первого делителя 1 частоты а второй, третий и- четвертый входы соединены соответственно с первым выходом устройства 10 управления, выходом, первого делителя 1 частоты и первым выходом компаратора 9, второй выход, которого соединен с входом управления устройства 10 управления, кодовые входы которого соединены с шиной 2 управляющего кода,,а кодовые выходы - с шиной адресации ПЗУ.7,вы ход которого подсоединен к первому кодовому входу сумматора 11,второй кодовый вход которого соединен с вы ходом регистра-накопителя 8, вход з писи которого соединен с вторым выходом устройства 10 управления, а кодовый вход - с выходом сумматора 11 и первым входом компаратора 9, второй вход которого соединен с выходом второго делителя 4 частоты .. . Спусковое устройство б может содержать два триггера и два элемента совпадения, первый вход первого из которых соединен с первым входом,а выход - с выходом спускового устройства, второй вход - с выходом первого триггера и входом сброса второго триггера, вход запуска которого соединен с вторым входом спускового устройства, а выход - с первым ВХОДОМ;второго элемента совпадения, второй вход которого соединен с третьимвходом спускового устройства, четвертый вход которого соединен с входом сброса первого триггера, вход запуска которого соединен с выходом второго элемента совпадения. - , . . Устройство 10 управления может содержать счетчик импульсов, тактовый вход которого соединен с входом управления устройства и первым входом первого элемента совпадения , выход которого соединен с. входом сброса, триггера, выход которого соединен с первым входом второго элемента совпадения, второй вход которого подключен к выходу генератора тактовой частоты, а выход - к второму выходу устройства, первый выход которого соединен с входом за пуска триггера, выходом первого дешифратора и входом сброса счетчика импульсов, выход которого соеди-нен с входом второго дешифратора,выход которого подключен к второму входу первого элемента совпадения, кодовые входы устройства соединеныс входом первого дешифратора и первой группой кодовых выходов устройства, вторая группа кодовых выходов устройства подключена к входам второго дешифратора. СЧетчик. импульсов ведет отсчет констант; код текущей константы с его выхода объединяясь с кодом Х...Х шины 2 управляющего кода, образуеткод Х...Хд адресации ПЗУ 7. Первый дешифратор выявляет моменты смены рабочих частот (код 0000), сигналом с его выхода устанавливается в йсходное состояние счетчик импульсов и перебрасывается триггер в состоя ние, при котором через второй элемент совпадения поступают на регистр-накопитель 8, образуя последовательность импульсов записи. Второй дешифратор выявляет состояние счетчика импульсов, соответствующее последующей константе (код 1010). При объединении сигнала с выхода этого дешифратора с сигналом В А, поступалощим с второго выхода компаратора 9, происходит сброс триггера. Воздействуя на вход второго элемента совпадения, триггер прекращает поступление импульсов записи на второй выход устройства, фиксируя окончание поиска значения В,.. В основу работы предлагаемого устройства положена периодичность совпадения сигналов делителя 1с сигналами делителя 4; формирующего, например, сигналы шкалы текущего времени. Задача сводится к нахожде.ний числа В, соответствующего моменту времени Т, ближайшему к моменту Тд (началу перехода на очередную частоту) и кратному периоду совпадения t{ упомянутых сигналов. Найденное значение В и соответствующий ему сосент Т определяет исходную фазу сигнала при очередной привязке. Значение В и значение А, .численно равное Т, при этом связа,ны выражениемA-a.. «., - целочисленное частное; Р- -модуль, численно равный периоду t совпадения сигналов, пропорциональный коэффициенту деления устройства; ч,- - наименьший остаток, Поиск значения В для сокращения времени производится в несколько ступеней/ при этом промежуточные модули .РТ Р пР; пропорциона 1ьны (т и п - целые положительные числа), Численные значения модулей ступеней, соответствующих требующимся коэффициентам деления, записаны в ПЗУ в виде констант. Устройство работает следующим образом. Переход на очередную частоту в момент Тд сопровождается изменением управляющего кода, поступающего по шине 2. При этом сигналом с устройства 10 на второй вход подготавливается спусковое устройство б, а изменившийся управляющий код изменяет коэффициент деления делителя 1. При переходе делителя 1 в исходное состояние сигналом с его выхода на третий вход вводится спусковое устройство б, развивая цепь шины 5 входной частоты на вход делителя 1,

Одновременно сигналом адресации на входе ПЗУ 7 производится выбор первой константы . Эта .константа, поступая на сумматор 11 суммируется с содержимым регистранакопителя 8, Результат суммирования поступает на первые входы регистра-накопителя и компаратора. 9, сравнивающего результат с кодом В текущего времени, который поступает на второй вход компаратора 9. При поступлении сигнала синхронизации на вход записи регистранакопителя 8 этот результат записывается в нем. Изменившееся значение содержимого регистра-накопителя 8 поступает на второй вход сумматора 11, что приводит к изменению сумиы на его выходе. При неравенстве В А, что фиксируется компаратором 9 (отсутствуют сигналы, на обоих выходах), константа тр на выходе ПЗУ 7 не изменяется и на cлeдsw.щeм такте вновь суммируется с содержимым регистра-накопителя 8.

При неравенстве наочерёдном такте суммирования устройство 10 управления изменяет код адресации ПЗУ 7, на выходе которого константа тпр сменяется на пр , и накопление суммы продолжается (как и для константы .При переходе к константе последней ступени р процесс суммирования оканчивается при наступлении неравенства В А, при этом результат на выходе сумматора 11 соответствует значению А. Устройство переходит в режим ожидания момента синхронизации частот. При наступлении этого момента, что фиксируется компаратором 9, сигналом с первого выхода сбрасывается спусковое устройство б и делитель 1 вступает в работу из исход ного состояния, обеспечивая необходимую начальную фазу формируемого на выходной шине 3.

Устройство реализовано на стан5 дартных микросхемах: ПЗУ - к

556 РТ4, сумматор - к 564 ИМ1, регистр-накопитель - к 564 ИР9, компаратор - к 564 ИП2.

В качестве базового объекта взяO та аппаратура ОЦ1.400.131-ДЕСНА-М, имеющая следующие недостатки. Процесс привязки начальной фазы формируемого сигнала требует выполнение операций по выбору исходных дан 5 ных, обрабйтке данных путем расчета вводу полученных значений, что не исключает ошибок. При выполнении этих операций оператором ожидаемое значение ошибочных привязок может составлять 1-2%. Кроме того, алгоритм привязки требует значительного времени на выполнение операций привязки (5 мин). Использование данного устройства предусматривает автоматическое выполнение операций привязки, чем :исключаштся соответ- ствующие ошибки и повышается надежность устройства.

Использование предлагаемого устройства сокращает время подготовки к работе до значения порядка 20 с. Время определяется практически значением периода совпадения сигналов формируемой частоты и теку 5 щего времени. Для частот 10 /110010 /1300 Гц в устройстве этот период составляет 20,8-18 с. Время, затрачиваемое на поиск значения В при тактовой .частоте 100 кГц,общем количестве тактов поиска при пяти ступенях констант 30, равно 300 мкс и им можно пренебречь.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РАЗЛИЧЕНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1987 |

|

SU1841020A2 |

| Цифровой синтезатор частот | 1983 |

|

SU1193803A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2380716C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| ПРИЕМОИНДИКАТОР СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1993 |

|

RU2067771C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Устройство для передачи многочастотных сигналов | 1989 |

|

SU1700760A1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий первый делитель частоты, управляющие входы которого соединены с шиной управляющего кода, а выход с выходной шиной устройства, второй делитель частоты, вход которого . соединен с шиной входной частоты, и спусковое устройство, отличающийся тем, что, с целью повышения надежности и уменьшения : времени подго овки при смене частоты, в него введены программируемое запоминающее устройство (ПЗУ), регистр-накопитель , компаратор, устройство управления и сумматор, причем первый вход спускового устройства соединен с шиной .входной частоты, выход - с входом первого делителя частоты, а второй, третий и четвёртый входы соединены соответственно с первым выходом устройства управления, выходом первого делителя чабтоты и первым выходом компаратора, второй выход которого соединен с входом управления устройства управления, ксэдовые входы которого соединены сшиной управляющего кода, а кодовые выходы - с шиной адресации ПЗУ, выход которого подсоединен к первому кодовому входу сумматора, второй кодовый вход которого (О соединен с выходом регистра-накопителя, вход записи которого соединен с вторы}4 выходом устройства управления, а кодовый вход- с выходом сумматора и первым входом компаратора, второй вход которого соединен с выходом второго делителя частоты. да 4 4 J -si

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СЧЕТНОЕ УСТРОЙСТВО | 0 |

|

SU325708A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Делитель частоты с переменным коэффициентом деления | 1975 |

|

SU600735A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1983-12-30—Публикация

1982-10-06—Подача