вого, пторого, третьего и четвертого регистров памяти, а также общая шина преобразователя кодов являются выходами преобразователя кодов, при этом кодовый вход первого гтеремножителя кодов , второй кодовый вход первого сумматорам первый кодовый вход третьего перемножителякодов объединены и являются вторым кодовым входом преобразователя кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1982 |

|

SU1084992A1 |

| Синтезатор частот | 1987 |

|

SU1417165A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1429285A1 |

| Формирователь многочастотного сигнала | 1986 |

|

SU1401554A1 |

| Синтезатор частот | 1986 |

|

SU1337990A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Синтезатор частот | 1988 |

|

SU1584105A2 |

| Цифровой синтезатор частоты | 1986 |

|

SU1363458A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

1. ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ, содержащий последовательно соединенные генератор импульсов, делитель частоты с переменным коэффициентом деления, управляемую линию задержки, распре/;елитель импульсов, коммутатор и цифроаналоговый преобразователь, а также накапливающий сумматор, управляющий выход которого подключен к управляющему входу делителя частоты с переменным коэффидиентом деления, а первый и второй кодовые входы накапливающего сумматора соединены соответственно с первым и вторым кодовыми выходами блока управления, отличающийся тем, что, с целью уменьшения уровня побочных составляющих в спектре выходного сигнала, между кодовыми выходами накапливающего сумматора и второй группой входов коммутатора введен преобразователь кодов, второй кодовый вход которого подключен к второму кодовому выходу блока управления, тактовый вход накапливающего сумматора и тактовый вход преобразователя кодов объединены и подключены к выходу делителя частоты с переменным коэффициентом деления. а вход управления управляемой линии задержки подключен к выходу генератора импульсов. 2. Синтезатор по п. 1, отличающийся тем, что преобразователь кодов содержит последовательно соединенные первый перемножитель кодов, первый сумматор, второй сумматор, третий сумматор и первый регистр памяти, последовательно соединенные второй перемнржитель кодов и второй регистр памяти, третий перемножитель кодов, последовательно соединенные четвертый сумматор и третий регистр паI мяти, последовательно соединенные пятый сумматор и четвертый регистр (Л памяти, кодовый вход второго перемножителя кодов объединен с вторым кодовым входом третьего.перемножителя кодов и является первым кодовым входом преобразователя кодов, второй кодовый вход третьего сумматора .объединен -с первым кодовым со входом четвертого сумматора и под00 ключен к выходу второго перемно00 .жителя кодов, выход третьего -перемо ножителя кодов подключен к второму кодовому входу второго сумматора, второй кодовый вход четве зтого сумматора и первый кодовый вход пятого сумматора объединены и подключены к выходу первого перемножителя кодов, второй кодовый вход пятого сумматора подключен к выходу третьего сумматора, тактовые входы первого, второго, третьего и четвертого регистров памяти объединены и являются тактовым входом преобразователя кодов, кодовые выходы первого перемножителя кодов, пер

1

Изобретение относится к радиотехнике и может использоваться для формирования сетки частот в устройствах радиосвязи, телеметрии и измерительной техники.

Цель изобретения - уменьшение уровня побочных составляющих в спектре выходного сигнала.

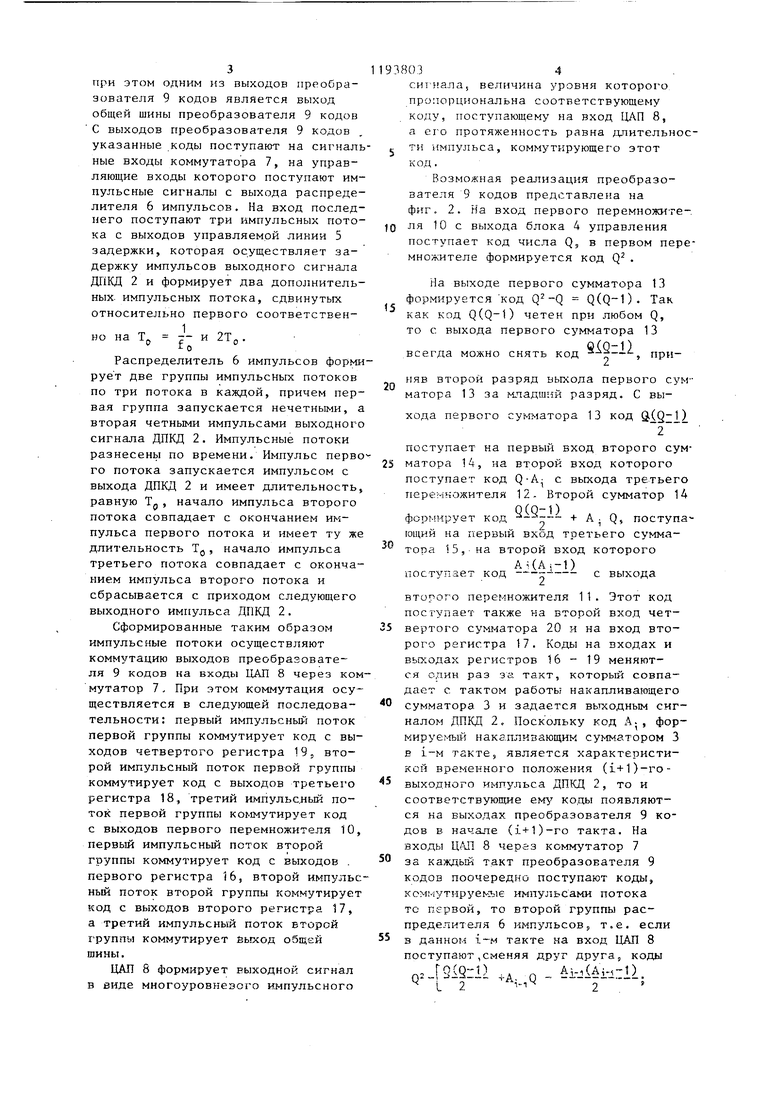

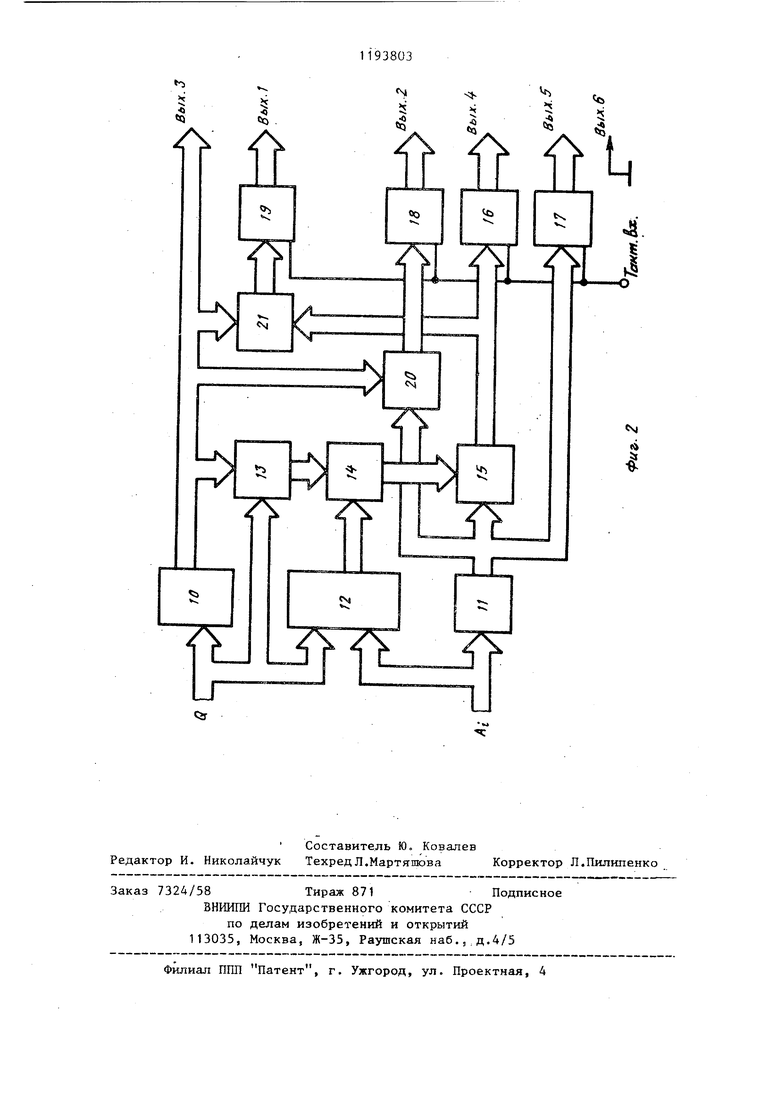

На фиг. 1 приведена структурная электрическая схема цифрового синт затора частот; на фиг, 2 - структурная электрическая схема преобразователя кодов.

Цифровой синтезатор частот со держит генератор, 1 импульсов, делитель 2 частоты с переменным коэффициентом,деления (ДПКД), накапливающий сумматор 3, блок 4 управления, управляемую линию 5 задержки, распределитель 6 импульсов, коммутатор 7, цифроаналоговый преобразователь (ЦДЛ) 8,и преобразователь 9 кодов.

Преобразователь. 9 кодов содержи первый 10, второй 11 и третий 12 перемножители кодов, первьй 13, второй 14 и третий 15 сумматоры, первый 16, второй 17, третий 18 и четвертый 19 регистры памяти, четвертый 20 и пятый 21 сумматоры.

Цифровой синтезатор частот работает следующим образом.

При соотношении частот генератора 1 импульсов fji и выходной

частоты ДПКД 2 ...,,, равном

|... „ . -|- . АПКД

где N - целое число;

- - несократимая прави-пьная

дробь,

коэффициёнт деления ДПКД 2 устанаь ливается равным N, ас выходов блока

4 управления на кодовые входы накапливающего сумматора 3 поступают коды чисел аир. Сигнал переноса накапливающего сумматора 3 поступает на управляющий вход ДПКД 2 и устанавливает его коэффициент деления равным N+1. В следующем такте работы сигналом с выхода ДПКД 2 он возвращается в исходное состояние с коэффициентом деления N. Накапливающий сумматор в каждом i-м такте суммирует код с выхода накапливающего сумматора А. с кодом числа q и сравнивает сумму этих кодов, полученную в предыдущем такте, с кодом числа Q. При этом код А. пропорционален смещению (i+1)-ro выходного импульса .ДПКД 2 относительно соответствующего импульса гипоте- , тической последовательности. Код А поступает на первый кодовый вход преобразователя 9 кодов, на второй кодовый вход которого поступает код числа Q из блока 4 управления. Преобразователь 9 кодов преобра.зует коды чисел Q и А, таким образо что на выходах преобразователя 9 кодов формируются следующие коды: на вькоде первого регистра 16 0.1911) . А.(А,Н) .

на выходе второго регистра 17

Aj(Aill) , 2

на выходе третьего регистра 18

П2 ). Q -2- .

на вькоде четвертого регистра 19

Q. .. 9(ОН) , „ л1|л:1)

на выходе первого перемножителя 10

QS 3 при этом одним из выходов преобразователя 9 кодов является выход общей шины преобразователя 9 кодов С выходов преобразователя 9 кодов указанные коды поступают на сигналь ные входы коммутатора 7, на управляющие входы которого поступают импульсные сигналы с выхода распределителя 6 импульсов. На вход последнего поступают три импульсных потока с выходов управляемой линии 5 задержки, которая осуществляет задержку импульсов выходного сигнал:а ДПКД 2 и формирует два дополнительных, импульсных потока, сдвинутых относительно первого соответственно на Tj, f 21,.,. о Распределитель 6 импульсов форми рует две группы импульсных потоков по три потока в каждой, причем первая группа запускается нечетными, а вторая четными импульсами выходного сигнала ДПКД 2. Импульсные потоки разнесены по в реме ни. Импульс перво го потока запускается импульсом с выхода ДПКД 2 и имеет длительность равную Tjj , начало импульса второго потока совпадает с окончанием импульса первого потока и имеет ту же длительность , начало импульса третьего потока совпадает с окончанием импульса второго потока и сбрасывается с приходом следующего выходного импульса ДПКД 2, Сформированные таким образом импульсные потоки осуществляют коммутацию выходов преобразователя 9 кодов на входы ЦАП 8 через ком мутатор 7, При этом коммутация осуществляется в следующей последовательности: первый импульсный поток первой группы коммутирует код с выходов четвертого регистра 19, второй импульсный поток первой группы коммутирует код с выходов третьего регистра 18, третий импульс.ньш поток первой группы коммутирует код с выходов первого перемножителя 10 первый импульсный поток второй группы коммутирует код с выходов . первого регистра 16, второй импульс ный поток второй группы коммутирует код с выходов второго регистра 17, а третий импульсный поток второй группы коммутирует выход общей шины. ЦАП 8 формирует выходной сигнал в виде многоуровневого импульсного 034 сигнала, величина уровня которого пропорциональна соответствующему коду, поступающему на вход ЦЛП 8, а его протяженность равна длительности импульса, коммутирующего этот код. Возможная реализация преобразователя 9 кодов представлена на фиг. 2. На вход первого перемножителя 10 с выхода блока 4 управления поступает код числа Q, в первом перемножителе формируется код Q. На выходе первого сумматора 13 формируется код Q(Q-1). Так как код Q(Q-1) четен при любом Q, то с выхода первого сумматора 13 QlQ-ll всегда можно снять код --, приняв второй разряд выхода первого сумматора 13 за младший разряд. С выхода первого сумматора 13 код S(Q;1) поступает на первый вход второго сумматера 14, на второй вход которого поступает код Q-A- с выхода третьего перемкожителя 12. Второй сумматор 14 форЕ.Ирует код + А. Q, поступа гощий на Г1ервый вход третьего сумматора 15, на второй вход которого AUA.;-1) поступает с выхода второго перемножителя 11. Этот код поступает также на второй вход четвертого сумматора 20 и на вход второго регистра 17. Коды на входах и выходах регистров 16 - 19 меняются один раз за такт, который совпадает с тактом работы накапливающего сумматора 3 и задается выходным сигналом ДПКД 2, Поскольку код А-, формируемьш накапливающим сумматором 3 в L-M такте, является характеристикой временного положения (i+1)-roвыходного импульса ДПКД 2, то и соответствующие ко,ды появляются на выходах преобразователя 9 кодов в начале (1-ь1)-го такта. На входы НАЛ В через коммутатор 7 за каждый такт преобразователя 9 кодов поочередно поступают коды, коммутируемые импульсами потока тс первой, то второй группы распределителя 6 импульсовр т.е. если в данном г-м такте на вход ЦАП 8 поступают ,сменяя друг друга, коды ). ГоСО-О ,.A,Q 2

)

и Q

Q

то в .последующем (1+1)-м такте на вход ЦЛП 8 поступают коды

Ai()

912:1)

A,Q

2

А XAt-1)

и ноль.

Таким образом, частота выходного сигнала цифрового синтезатора частот равна

f f4Li 8ых 2

В качестве перемножителей 10 - 1 можно использовать матрицы постоянных запоминающих устройств.

Подавление паразитных составляющих в спектре выходного сигнала обеспечивается за счет формирования многоуровневого сигнала, в котором достигается увеличение амплитуд одних гармоник и уменьшение других. Это достигается за счет того, что импульсные сигналы, участвующие в суммировании, сдвинуты относительно исходного на

t - Q

где tj - временной интервал между началом первого и -го импульса; f 0,...,Q-1,

что приводит к неполному подав лению паразитных гармонических составляющих в спектре результирующего сигнала. Однако в данном случае наблюдается увеличение амплитуд

,

гармоник, кратных частоте f

2Т

15 и уменьшение амплитуд всех прочих гармоник

1АП11А Ш.

i-S

Т Q

Т T(NQ + а) Следовательно, f ,

а это

выходная частота цифрового синтезатора частот. i

Выигрьщ по подавлению паразитных

составляющих в спектре выходного сигнала не хуже 20tgN(flB), где N коэффициент деления ДПКД 2.

i

I

Co

Л

IT

I I

Ьч

гЧи

CM

0

N

fU

«

| Шапиро Д.Н., Паин А..А | |||

| Основы теории синтеза частот | |||

| - М.: Радио и связь, 1.981, с | |||

| Затвор для дверей холодильных камер | 1920 |

|

SU182A1 |

| Синтезатор частот | 1982 |

|

SU1084992A1 |

Авторы

Даты

1985-11-23—Публикация

1983-12-21—Подача