а:

СП

ш

00

со

Изобретение относится к приборестроению и может быть использовано для записи на диаграммной ленте, совокупности контролируекых и экстр полируемых технологических параметров (двух или более одновременно) в виде кривых.

Известно устройство для регистрации значений контролируемых пара-, метров, содержащее датчики параметров , соединенные через входной коммутатор с уравновешивающей измерительной системой, выход которой подключен к реверсивному двигателю, свзанному с кареткой печатающего механизма, синхронный двигатель привода диаграммной ленты, связанный с печатающим механизмом и входным коммутатором, счетчик импульсов и дешифратор, профилированный кулачок и второй коммутатор, связанные с валом синхронного двигателя, повторитель сигналов, связанный с валом реверсивного двигателя, нормально

разомкнутые контакты, взаимодействукицие с профили зованным кулачком,

.включенные между выходом повторителя сигналов датчиков и входами второго коммутатора и счетчика импульсов, квантователи сигналов, подключенные к выходам второго коммутатора, блоки памяти, включенные между выходами квантователей сигналов и входами дешифратора, цифро-аналоговый преобразователь, подключенный к выходам дешифратора, формирователь импульсов сброса, соединённый с выходом счетчика импульсов, и элемент задержки, включенный между формирователем импульсов сброса и вход ми сброса блоков памяти Г1 .

Недостатком этого устройства является то, что око не- позволяет экстраполировать как обобщенную кривую, так и отдельные параметры,применение же многомерных экстраполяторов вызывает технические трудности в связи с их сложностью. Операции экстраполяции необходимы при оценке состояния большинства промьвдленных объектов, так как последние содержат запаздывания в измерительных или регулируюпшх каналах.

Целью изобретения является расширение функциональньрс возможностей устройства.

Поставленна5Р цель достигается тем, что в устройство для регистрации значений контролируекых параметров введены последовательно включенные зкстраполятор, дополнительные квантователь, и блок памяти а также второй и третий цифро-аналоговые преобразователи, причем вход экстраполятора соединен с выходом первого цифро-аналогового преобразователя входы второго и третьего цифро-айало.говых преобразо

вателей соединены с выходами дополнительного блока памяти, их выходел с информационными входами входного коммутатора, а вход сброса дополнитёльного блока памяти соединен с 5 выходом элемента задержки.

Экстраполятор выполнен в виде последовательно включенных первого блока сравнения,, ограничителя, интегратора, блока задержки, второго

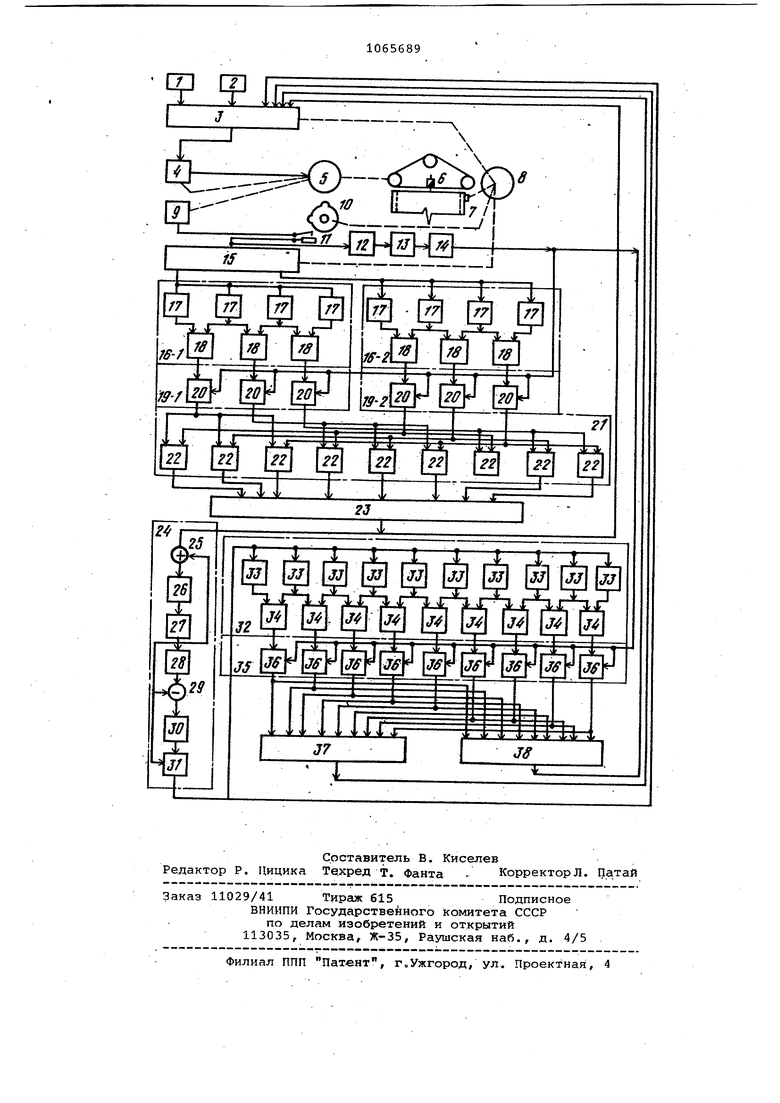

0 блока сравнения, масштабирующего блока и сумматора, причем выход интегратора соединен с вторыми, входами блоков сравнения и сумматора. На чертеже представлена блок5 схема устройства для двух контролируемых параметров при трех уровнях их- квантования. По аналогии может быть построен регистратор и для большого числа параметров и уровней квантования.

Устройство для регистрации многомерных данных содержит датчики 1 и 2 регистрируемых параметров,входной коммутатор 3, измерительную схе5 реверсивный двигатель 5 при- . вода каретки печатающего механизма

6, носитель записи в виде диаграммнрй 7, синхронный двигатель 8 повторитель 9.сигналов, профилированный кулачок 10, нормально разомкнутые крнтакты 11, счетчик 12 импульсов, формирователь 13 импульсов сброса, элемент 14 задержки, второй коммутатор 15„ первые квантователи сигналов с первого и второго датчи5 .ков 16-1 .и 16-2 соответственно,

состоящие из дискриминаторов (пороговьЬс элементов) 17 и схем 18 антисовпадений, nepBbie блоки 19-1 и 19-2 памяти, содержащиепо три ячейки 20 памяти (по числу уровней квантования сигнала), -дешифратор 21, выполненный из схем 22- совпадений, первый цифро-аналоговый преобразователь 23, Экстраполятор 24, со5 держащий первый блок 25 сравнения, ограничитель 26, интегратор 27, блок 28 задержки, второй блок 29 сравнения, масштабирующий блок 30, сумматор 31, второй квантователь 32

Q сигналов, состоящий из пороговых элементов 33, схем 34 антисовпадёний, второй блок 35 памяти, содержащий девять ячеек 36 памяти, второй цифро-аналоговый преобразователь 37, третий цифро-аналоговый преобразователь 38.

Устройство работает следующим образом.

Электрические сигналы с датчиков 1 и 2, пропорциональные значениям измеряемЕЛХ параметров, поступают на входной коммутатор 3, выполненный в виде двухполюсного переключателя и управляемый двигателем 8. Коммутатор 3 подключает в

5 начале каждого цикла регистрации выход первого датчика к входу измерительной схекш 4, которая управляет двигателем 5. Двигатель 5 перемещает каретку с печающим механизмом 6 и движок реохорда измерительной схемы 4 до уравновешивания сигнала. Одновременно с перемещением карет ки и движка реохорда измерительной системы двигатель 5 перемещает повторителя 9 сигналов. Следовательно, каждому значению регистрируемого сигнала соответствует равнозначное положение движков реохордов измерительной системы 4 и повторителя 9 сигналов.В момент наступления равновесия сигнал на входе-двигателя 5 становит ся равным нулю, и двигатель 5 останавлхивается, двигатель 8 через механизм привода воздействует на печатающий механизм 6, который отпечатывает на равномерно движущейся диаграммной ленте 7 точку и цифру, соответствующую номеру датчика, подключенного к входу измерительной схемы 4; положение точки по ширине: диаграмг/1ной ленты пропорционально величине сигнала, поступающего с датчика. В этот же момент кулачок 10, закрепленный на валу синхронного ДВИгателя 8, замыкает нормально разомкнутые контакты 11, через которые электрический сигнал от повторителя 9 сигналов поступает «а вход, второго коммутатора 15 и счетчика 12 импульсов..

С первого выхода коммутатора 15 сигнал, пропорциональный значению первого регистрируемого параме.тра, поступает на вход первого квантователя 16-1 первого параметра.

Первый квантователь 16-1 содержит при трех УРОВНЯХ квантователя, сигнала четыре дискриминатора (пороговых элемента) 17 с общими входами, подключенными к первому выходу второго коммутатора 15, и три схемы 18 антисовпадений.Аналогично устроен квантователь 16-2, но входы его дискриминаторов подключены к второму коммутатору 15 второго выхода.

Диск1)иминаторы 17 выполнены в виде, например, триггерных бхем с одним устойчивым состоянием равновесия, -которые срабатывают, если на их вход поступает сигнал, превышающий некоторый пороговый уровень. Пороги срабатывания соседних дискриминаторов отличаются на величину интервала квантования сигнала по уровню, Схемы 18 антисовпадений представляют собой логические устройства, которые срабатывают только в том случае, если на один вход схемы поступает сигнал,а на другой -не поступает.

Таким образом, при поступлении i сигнала на вход первого кнантоват еля 16-1 сигнал появится на выходе той схемы 18 антисовпадений., которая подключена к дискриминаторам 17 с порогами срабатывания выше и ниже уровня входного сигнала. Сигна с выхода сработавшей схемы 18 антисовпадений квантователя 16-1 поступает на информационный вход ячейки 20 памяти первого, блока 1.9-1 памяти

Блок 19-1 памяти сигналов первого датчика содержит три ячейки 20 памяти, входы которых подключены непосредственно к выходам соответствуквдих схем 18 антисовпадений квантователя 16-1. Каждая ячейка 20 памяти выполнена в виде триггервой схемы с двумя устойчивыми состояниями равновесия и с двумя входами - информационным и сбрасывающим. При поступлении сигнала на информационный вход ячейки 20 памяти схема приходит в одно из состояний равновесия, а на выходе формирователя сигнал, фиксируя тем самым сигнал из квантователя 16-1.

Далее сигнал с выхода ячейки 20 памяти блока 19-1 памяти поступает в первый дешифратор 21 на вход одно из схем 22 совпадений, подключенной непосредственно к выходу сработавшей ячейки 20 памяти.

Выходы дешифратора 21 подключены к соответствующим входгм первого цифро-аналогового преобразователя 23, на выходе которого формируется яналовый сигнал, например, в виде напряжения постоянного тока, величина которого пропорциональна номеру сработавшей схемы 22 совпадений дешифратора 21, и, следовательно, сочетанию квантованных значений сиг налов датчиков 1 и 2. Аналоговый сигнал, полученный с первого цифроаналргового преобразователя 23, поступает на вход коммутатора 3 и вход экстраполятора 24.

Экстраполятор 24 выполняет следующее преобразование .,

I

Y((t)+ f.vCt),

(1)

где Y Ct+i;) - значение выходного сигт нала Y(t) экстраПолятора, экстраполированного на интервал вре мени V ; Y(t) - сглаженное значение

входного сигнала Y(t) экстраполятора; v{t) - оценка скорости изменения сиг,нала.

Для реализации выражения (1) из входного сигнала экстраполятора 24 в первом блоке 25 сравнения вычитается выходной сигнал интегратора 27, сигнал полученной разности поступает на ограничитель 26, вйполненный в

виде усилителя с насыщением, где срезаются отдельные, большие по величине (грубые)выбросы, что повышает точность дальнейпдего преобразования сигнала. Выходной сигнал ограничителя 26 подается на интегратор 27, на выходе которого получается сигнал о сглаженном значении обобщенной кривой Y(t).Этот сигнал задержива.ется на интервал а времени в блоке задержки 27 и поступает на второй блок 29 сравнения, где вычитается из.выходного сигнала интегратора 27. Выходной сигнал второго блока 29 сравнения поступает на масштабирукяций блок 30,, где умножается на коэффициент b С/л, тем самым получается сигнал о второй, составляфгцей правой части (1). В сумматоре 32 суммируется выходной сигнал интегратора, 27 и масштабирующего блока 30. В результате на выходе сумматора 31 получается сигнал ).

Далее производится квантование выходного сигнала экстраполятора ; 24 на девять уровней. Эта/операция осуществляется аналогично квантованию в блоках 16-1 и 16-2. Для выполнения указанной операции используется второй квантователь 32, состоящий из дискриминаторов33 и схем 34 антисовпадений.

Квантованный выходной сигнал из второго квантователя 32 поступает на второй блок 35 памяти, содержащий девять ячеек памяти, функциони -. рующий аналогично ячейкам первого ; блока памяти. Сигнал с выходов ячеек 36 блока 35 памяти поступает ;на второй и третий цифро-аналоговые преобразователи 37 и 38.. На входах второго 37 и третьего 38 цифроаналоговых преобразователей получаются аналоговые сигналы, величина которых пропорциональна номеру ячейки памяти, с которой поступил сигнал. Выходной сигнал второго цифроаналогового преобразователя является Экстраполированным сигналом первого датчика 1, а третьего - второго датчика 2. ..

На вход коммутатора 3 подаются, таким образом, дополнительно к сигналам от датчиков сигналы: с первого цифро-аналогового преобразователя 23 - сигнал о значении обобщенной кривой:, экстраполированное значение этой кривой - с выхода экстраполятора 24;;экстраполированные значения каждого из двух входных сигналов - с выходов второго 37 и третьего 38 цифро-аналоговых преобразова. телей.

Коммутатор 15 работает следующим образом. Контакты 11 в момент регистрации с преобразователя 23

5 не замыкаются, так как кулачок 10 имеет только два выступа (по числу датчиков технологических параметров) и сигнал с повторителя 9 на коммутатор 15 не поступает и дальнейшей об0 работке, не подвергается.

При каЛдом замыкании контактов 11 счетчик 12 фиксирует импульс, а при каждом втором импульсе счетчик 12 вырабатывает сигнал, включающий

5 формирователь 13 сбрасывающего

импульса, выполненный, например, в виде электромагнитного реле, с выхода которого сигнал поступает на блок 14 задержки, а с выхода последQ него через определенный промежуток времени, требуемый для обработки и регистрации сигнала с цифро-аналогового преобразователя 23, и на сбрасывакядие входы ячеек 20 и 36 памяти.

5 При этом сработавшие ячейки памяти возвращаются в исходное состояние.

Таким образом, в ходе регистрации на равномерно движущейся диаграммной ленте печатаются шесть кривых,

Q образованных последовательностью точек, две из которых отображают сигнал с датчиков 2 и 1, третья характеризует их совместное изменение и является обобщенной оценкой состоя ния объекта управления, четвертая экстраполированное значение обобщенHojl оценки состояния объекта, пятая и шестая кривые - экстраполированное значение сигналов первого и второго датчиков.

0 Аналогично может быть выполнен регистратор многомерных данных и от большого числа датчиков при большем числе уррвней квантования сигналов. Предлагаемое устройство регистра5 ции многомерных данных обладает по сравнению с базовым объектом более широкими функциональными возможностями за счет экстраполяции обобщенной кривой и последующей развертки

0 ее вэкстраполированные сигналы от. Дельных датчиков.

ртображение сигналов двух и более числа датчиков в виде обобщенной. е крийой, ее экстраполированного значенйя, экстраполированных значений этих кривых позволяет оперативно и точно оценить и предсказать поведение объекта управления, принимать .Волее точные управляющие воздействия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации значений контролируемых параметров | 1981 |

|

SU958857A1 |

| Устройство для регистрации значений контролируемых параметров | 1982 |

|

SU1095037A2 |

| Двухотсчетный следящий привод | 1989 |

|

SU1700535A1 |

| Устройство автоматической коррекции координатных искажений телевизионного изображения | 1981 |

|

SU1012456A1 |

| Цифровой растровый индикатор | 1983 |

|

SU1111111A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ НЕРОВНОСТЕЙ НА ПОВЕРХНОСТИ КАТАНИЯ РЕЛЬСА | 1992 |

|

RU2035534C1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство кодирования телевизионного сигнала | 1986 |

|

SU1381730A1 |

1. УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ЗНАЧЕНИЙ КОНТРОЛИРУЕМЫХ ПАРАМЕТРОВ по авт.св. 958857, о т личающееся тем, что, q целью расширения функциональных возможностей, в него введены после-: довательно соединенные экстраполятор, дополнительные квантователь и блок памяти, а также второй и третий цифро-аналоговые прёобразова- . тели, причем, вход экстраполятора соединен с выходом первого цифроаналогового преобразователя, входы второго и третьего цифро-аналогового преобразователя соединены с выходами дополнительного блока памяти, их выходы - с информацйонными входами входного коммутатора, а вход сброса дополнительного блока памяти подключен к выходу элемента эадерл ки. 2. Устройство по П.1, о т л и ч а ю we е с я тем, что, экстраполятор выполнен в виде последовательI но соединенных первого блока сравнения, ограничителя, интегратора, (Л блока задержки, второго блока сравнения, масштабирующего блока и сумматора, причем выход интегратора подключен к вторым входам блоков с|}авнения и сумматора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для регистрации значений контролируемых параметров | 1981 |

|

SU958857A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| . | |||

Авторы

Даты

1984-01-07—Публикация

1982-05-31—Подача