Изобретение относится к измери тельной технике и может использоватся для ком,1утации сигналов в адаптивных измерительных системах с двумя ступенями коммутации.

Известно устройство для адаптивной ком2У утации, содержащее датчики, анализаторы, сумматор, делитель,блоки сравнения, блок оптимального кодирования, блок программного управления, переключатель и блок коммутации

Недостаток указанного устройства - невозможность использования его в адаптивных измерительных системах с двумя ступенями коммутации вследствие отсутствия второго блока коммутации и согласования частот первой и второй ступени коммутации.

Наиболее близким по технической сущности к предлагаемому является устройство д.пя а даптивной двухступенчатой коммутации, содержащее групы датчиков, выходы которых соединены с информационными входами первого коммутатора и через соответствующие блоки определения частоты опроса с первыми информационными входами блока переключателей и соответствующими входами первого.сумма.тора, выходы первого сумматора соеднены с вторыми информационными входами блока переключателей, выходы которого соединены непосредственно с первыми входами делителя частоты через второй сум,1атор с вторыми входами делителя частоты и переключателя и первым входом второго блока сравнения, выходкоторого через переключатель соединен с первым входо блока программного управления, выходы делителя частоты соединены с .ми входами блока кодирования и первого блока сравнения, вторые, входы которого соединены с первыми выходами блока кодирования, вторые выходы которого соединены с вторыми входами блока программного управления, выходы которого соединены с входами блока памяти, первый, второй, третьи, четвертые и пятые выходы блока памяти соединены соответственно с третьим входом первого блока сравнения, управляющим входом блока переключателей, вторыми входами второго блока сравнения, управляющими входами второго коммутатора , выходы коммутаторов соединены с выходами устройства 12.

Известное устройство характеризуется достаточным быстродействием п р и к ом м у т а и и н к: у с о ч н о с т а ц и о i-j а р н ых процессов со значительной длиной участков стаиионарности. В этик ус ловиях оно может обеспечивать малое количество перестроек пpoгpaм Ы опроса. При сокращении длины участков стацио 1арности уменьшается

время на обработку поступающей информации и поиск программы опроса, причем время Обработки и поиска сокр щается во столько ра, во сколько происходит самое большое уменьшение длины участков стационарности. Для определения допустимой программы опроса устройство осуществляет большой объем операций в блоке кодирования и блоке памяти, которые являются медленнодействующими блоками: блок кодирования - в силу сложности его технической реализации при обработке больших объемов поступающей информации, а блок памяти - в силу работы его в режиме накапливания поступающей информации, вследствие этого известное устройство обладает недо.статочИым быстродействием при коммутации процессов с небольшой длиной участков стационарности и теряет свойство адаптации к изменениям характеристик коммутируемых процессов.

Цель изобретения - повышение быстродействия устройства.

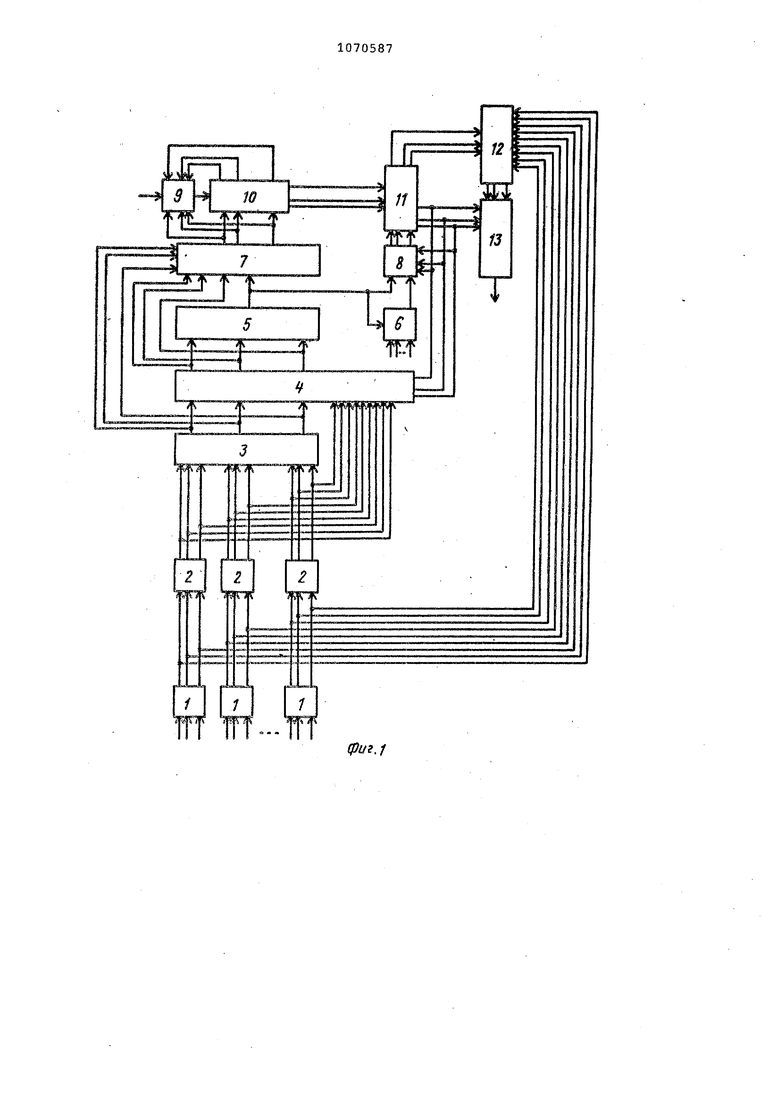

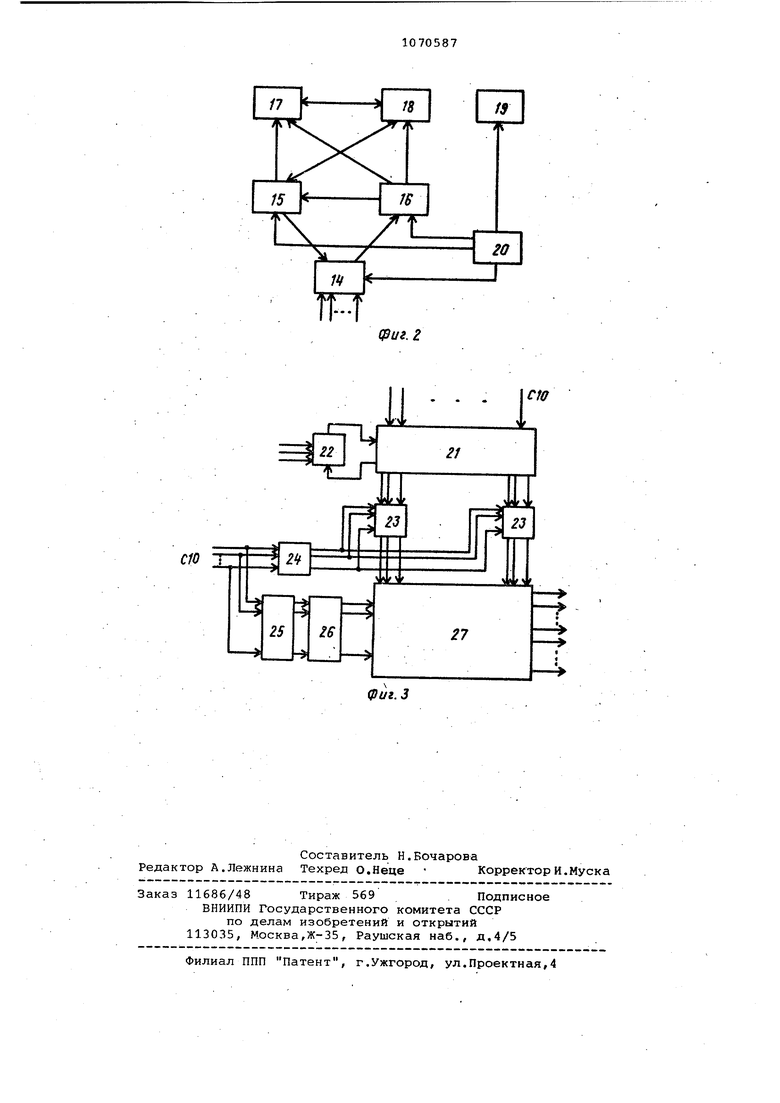

Указанная цель достигается тем, что в устройстве для адаптивной двухступенчатой коммутации, содержащем группы датчиков, выходы которых соединены непосредственно с первыми входами первого коммутатора и через соответствующие блоки определения частоты опроса с первыми входами блока переключателей и первого сумматора, выходы первого сумматора соединены с вторыми входами блока переключателей, выходы которого соединены с первыми входами делителя и второго сумматора, выход второго сумматора соединен с первыми входами первого блока сравнения и переключателя и втоpbifvi входом делителя, выходы делителя соединены с первыми входами второго блока сравнения и блока кодирования, первые выходы которого соединены с вторыми входами второго блока сравнения, выход его соединен с вторым входом блока кодирования, выходы блока кодирования соединены с первыми входами блока программного управления, выход первого блока сравнения соединен с вторым входом переключателя, выходы которого соединены с вторыми входами блока программного управления, и второй коммутатор, выход которого соединен с выходом устройства, первые выходы блока программного управления срединены с вторыми входами первого коммутатора, выходы которого соединены с первыми входами второго коммутатора, вторые выходы блока программного управления соединены с вторыми входами второго коммутатора, третьими входами переключателя, третьи входы делителя ; подключены квыходам первого сумматора, второй вход первого блока сравнения и третий вход второго бло ка сравнения подключены соответстве но к первому и второму входам устройства. Кроме того, блок программного уп равления выполнен на счетчиках, переключателе, дешифраторе, регистрах сдвига и ключах, первые выходы первого счетчика соединены с первыми входами первых ключей, вторые входы которых соединены с выходами регистра сдвига, выходы - с первыми входами переключателя, выходы второго счетчика через дешифратор соед нены с вторыми входами переключател первые и вторые выходы которого сое динены соответственно с первыми и вторыми выходами блока программного управления, второй выход первого счетчика соединен с первым входом второго ключа, выход которого соеди нен с первым входом первого счетчик вторые входы первого счетчика и объ диненные входы регистров сдвига и : второго счетчика и второй вход второго ключа соединены соответственно с первыми и вторыми входами блока программного управления. На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 и 3 - примеры реализации бло.ков кодирования и программного управления соответственно. Устройство содержит группы датчиков 1 информации, блоки 2 определения частоты опроса, первый сумматор 3, блок 4 переключателей; второй сум матор 5, первый блок 6 сравнения, делитель 7, переключатель 8, второй блок 9 сравнения, блок 10 кодирования, блок 11 программного управления, первый коммутатор 12 и второй коммутатор 13. Блок 10 кодирования включает элемент 14 памяти, регистры 15-17, элемент 18 сравнения, счетчик 19 и синхронизатор 20. Блок 11 программного управления содержит счетчик 21, ключ 22, ключи 23, регистры 24, счетчик 25, дешиф.ратор 26 и переключатель 27. Устройство работает следующим образом. Измеряемые сигналы непрерывно подаются с выходов .групп датчиков 1 информации на входы блоков 2, каждый .из которых определяет текущие необходимые частоты опроса датчиков Р, , 14-7 П . iFiiJ J f ( необходимая частота опроса i-ro датчика ,1-й группы датчиков 1 информации,И; - число датчиков в j-й группе). Далее с помощью сумматора 3 вычисляются необходимые частоты опроса каждой группы датчиков информации fi) Блок 4 переключателей работает таким образом, что входы, соединенные с выходами сумматора 3, открыты, а входы, соединенные с выходами блоков 2, закрыты до тех пор, пока не поступят сигналы на третьи входы блока 4 переключателей. С по-, мощью сумматора 5 и делителя 7 вычисляются относительные необходимые частоты опроса cl-j ,в соответствии с выражением л о-: . С выходов делителя 7 сигналы,пре порциональные величинам j t подаются на входы блока 10 кодирования, который находит оптимальные величины относительных допустимых частот опроса и кодированные сигналы адресной системы каждой группы датчиков 1. В данном случае 1 допустимые частоты опро.са групп датчиков 1 информации, при использовании которых на выходе устройства можно получить последовательность равноотстоящих отсчетов и равномерное следование отсчетов . Процесс кодирования состоит из операций упорядочивания набора относительных необходи.мых частот в порядке убывания и операции оптимального кодирования. В строках элемента 14 памяти, входящего в состав блока 10 кодирования, записаны кодовые слова. В адресной части кодовых слов записано значение относительной необходимой частоты, остальные разряды предназначены для записи номера канала и вспомогательной промежуточной информации. Работой всего блока управляет синхронизатор 20. Упорядочивание набора относительных необходимых частот в порядке убывания производится путем сравнения адресной части кодовых слов на элементе 18 и размещения их в порядке убывания отноентельных необходимых частот в элементе 14 памяти. Процесс оптимального кодирования осуществляется в два этапа: прямой и обратный. При прямом ходе выполняются следующие операции. Из элемента 14 памяти выбираются по два кодовых слова с наименьшими значениями относительных нерегистрах 15 и 0б к од имых частот. В 1б им прис ваиваются порядковые носе значением мера LS соответствии с гетчикча 19, Номера записываются во вспомогательных разрядах кодовых С.Г1О1Э , В регистре 17 формируется новое с.поио путем сумгч ирования значен относительных необход.имых частот, эаписапиык в адресной части, двух выбранных кодовых слов и записи это cyMviH в адресную часть нового кодового слова. Новому кодовому слову с понотью счетчика 19 присваивгается порядковьзй номер, который записывается во вспомогательную часть. Два вкбра.нных кодовых слова исключаются из набора и записываются в последни ячейки свободной части элемента 14 памяти,- а новое слово включается в не.бор -Т записывается в такую строку чтобы упорядоченность набора не на1;::У1: г J:.C}) ,. Oj ЗраПИ -) ПОВТОРЯЮТСЯ ДО те;х пор,- покгг в -упориддоченном наборе не останется одпо слово. По окон чании этапа прямого хода начинается фо ; миров,:;нке адресной системы оггрос а а налов.. Содержимое адресной час ти всех колювых слов стирается и ис пользуется для записи адресных ко--14 памяти в доных елоа наибольбираются ПС овыми номерами. Слово ЫИМИ номером переводится в со старшим реЕистг 1.7, а два друг1- Х с.)Ова 15 и 1G. Содержи.мое aj.ipe в регистры с ной -lariTH слова со старшим номером переписывается в адресные части, дву ос1альпыХ выбранных слов, Saiervi в следугоми адресной части одного из этих слов записывается О, другого -- 1. Во вспомогательном рсгЗряде 1СПЖЛОГО слова прибав..11иется единип.а прм каждом запо7П ении разря да адресной . Слона из регистров переп-тсы-аются в элемент 14 памяти. По окончании прочасса в каиодо слове буд.йт записано число К,- , рав ное 1-ислу двоичных разрядов .в кодовом слоне адреса даг-птого кана.)1а и адрескке коповгле с.г1Ова всех каналов BctniLie си111алы адресной си величинами Тактовые импульсы, соответствующие длгнаг. тсодоп адресной систе 4ы к ; IJ я номерам измерите1.ьных каналов , пос1уг ают на входы регистров 24 и счсггчиков 25. Сигнгшы с В-ыходо счетчиков 25 дешифруются дешифраторами 26- на выходах которых формиру ются сигнллы, выбираю л ие шттны перек..;я (г1ереклк1чаемоГ| д зодной .-ггригты н г:ПС11петств; И с номерами измерительных каналов. Выходы сдвига регистров 24 управляют работой п групп ключей 23, подключая к входам 21 ky число ключей в кажсчетчиковдои из п групп. Адресные коды N;J , поступающие с выходов счетчиков 21 на входы п групп ключей 23, открывают К; число ключей , -ari- jiv JX iru ас: ri JB КЭЖДОЙ группе и переключают диоды в перек-лючаемой диодной матрице 27 в соответствии с адресными кодами. Сигнал с выхода счетчиков 21 поступает на вход ключа 22 и пропускает на вход счетчика импульсы с частотой f. выходах переключаемой диодной матрицы 27 получаем последовательность импульсов с частотами пределение последовательности импульсов опроса, поступающих с выхода h f.--IZ. сумматора 5, с частотой последовательностей с частотами с полученной в соответствии адресной системой, осуществляется лля того или иного участка стационарности измеряемых сигналов. Участок стационарности измеряемого сигнала - это такой участок, на котором norpeujHocTb приближения набора fj-JT набором f-(в смысле выбранного критерия на превосходит заранее заданной величины Z (например, допустимую величину погрешности приближения набора ff I набором вводимой в блок 9 сравнения. При превышении погрешностью приближения этой величины необходимо изменить h , т.е. перестроить адресную систему и передать ее на приемный коней. Набор допустимых частот ) поступающих от внешнего такгового генератора на входы блока б сравнения, соответствует нескольким скоростям записи данных на регистраторе, нескольким несущим частотам в канале связи или тактовым частотам ЦВМ. В процессе работы устройгства в блоке б сравнения выбирается ближайшее к fj- значение f, .Необходимое в этом случае распределение между каналами разностной частоты uf fj((- о осуществляется в блоке 11 в соответствии с набором {t) так, что величина f распределяется между каналами с весами { bj) .Режим подачи на вход блока программного управления последовательностей импульсов с частотами fg или f OK устанавливается с помощью переключателя 8. Одновременно п-ри поступлении импульсов опроса с частотами , на первый блок 12 коммутации импульсы опроса поступают на входы переключателя 8 и третьи входы блока 4 переключате лей ; При этом входы блока 4 перекл чателей, соединенные с выходами суммирования 3, закрываются и откр ваются входы блока 4 Переключателе соединенные с выходами блоков 2. Дальнейшая обработка информации ве дется аналогично описанному выше. помощью сумматора 5 и делителя 7 н ходятся относительные.необходимые Г ij f (Им1,1, частоты опроса датчиков в соответствии с выражением --4 И С выхода блока 9 кодиривамин на бор относительных допустимых часто опроса датчиков (,. -- и кодироJванные сигналы адресной системы jfNjjl I поступают на входы блока 11 программного управления. Переход от относительных допустимых частот ы:опроса датчиков к допустиffViiTмнм частотам опроса датчиков в блоке 11 осуществляется .распределением последовательности импульсов опроса, поступающих с , поступающих выхода переключателя S с частотами на IZ rni 8 с частотами I J J 1 1 последовательностей с частотами )-l j-l соответствии с получен-Импульсы опной адресной системой. Гг // роса с частотами, ,| управляют {1 JJ М работой второго блока коммутации, подключающего датчики к входам nep-i вого блока коммутации, работой которого управляют импульсы опроса с частотами |ij) . С выхода первого.;, блока коммутации информационные сигналы передаются в канал связи. Таким образом, быстродействие предлагаемого устройства по сравнению с известными повышается благодаря введению дополнительных связей от блока программного управления к блоку переключателей, переключателю и двум коммутаторам. При этом время обработки информации сокращается на время задержки в блоке памяти, что составляет приблизительно 3-5 с, т.е. скорость обработки информации увеличивается на 20-30%.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной двухступенчатой коммутации | 1980 |

|

SU926706A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО ВЫЗОВА | 2005 |

|

RU2299525C1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Телеметрическое устройство | 1979 |

|

SU858061A1 |

УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ ДВУХСТУПЕНЧАТОЙ КОММУТАЦИИ, содержащее группы датчиков, выходы которых соединены непосредственно с первыми входами первого коммутатора и через соответствующие блоки определения частоты опроса с первыми входами блока переключателей и первого сумматора, выходы первого сумматора соединены с вторыми входами блока переключателей, выходи которого соединены с первыми входами делителя и второго сумматора, выход второго сумматора соединен с первыми входами первого блока сравнения и переключателя и вторым входом делителя, выходы делителя соединены с первыми входами второго блока сравнения и блока кодирования, первые выходы которого соединены с вторыми входами второг.о блока сравнения, выход его соединен с вторым входом блока кодирования, выходы блока кодирования соединены с первыми входами блока программного управления, выход первого блока сравнения соединен с вторым входом переключателя, выходы которого соединены с вторыми входами блока программного управления, и второй коммутатор, выход которого соединен с -,J выходом устройства, отличающееся тем, что, с целью повышения быстродействия, первые выходы блока программного управления соединены с вторыми входами первого коммутатора, выходы которого соединены с первыми входами второго коммутатора, вторые выходы блока программного управления соединены с вторыми входами второго коммутатора, третьими входами переключателя, третьи входы делителя подключены к выходам первого сумматора,второй вход первого блска сравнения и третий в.ход второго блока сравнения подключены соответственно к первому и второму входам устройства. 2. Устройство ПОП.1, отличающееся тем, что блок программного управления выполнен на счетчиках, переключателе, дешифраторе, регистрах сдвига и ключах,первые выходы первого счетчика - соединены с первьт-ги входами первых ключей, вторьте входы которых соединены с выходами регистра сдвига, выходы - с первыми входами переключателя, выходы второго счетчика через дешифратор соединены с вторыми входами переключателя, первые и-вторые выходы которого соединены соответственно -; с первыми и вторыми выходами программного управления, второй Btj ход первого счетчика соединен с первым входом второго ключа, выход которого соединен с первым входом первого счетчика, вторые входы первого счетчика и объединенные входы -регистров сдвига и второго счетчика и второй вход второго |слюча соединены соответственно с п :рвыми и вторыми входами блока программного управления.

11

фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для АДАПТИВНОЙ КОММУТАЦИИ | 0 |

|

SU335711A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для адаптивной двухступенчатой коммутации | 1980 |

|

SU926706A1 |

Авторы

Даты

1984-01-30—Публикация

1982-07-19—Подача