эуют лшну задания режима устройства, замыкающие контакты первого аналогового переключателя объединены с соответствующими замыкающими контактами второго аналогового переключателя выходы дешифратора шины адреса соединены с соответствующими управляющими входами И-разрядных цифроаналоговых преобразователей группы и И-разрядных аналого-цифровых преобразователей группы, выходы фиксации конца кодирования h-разрядных аналого-цифровых преобразователей соединены с входами первого элемента ИЛИ, выход которого соединен с синхровходом буферного регистра и является шиной Конец кодирования устройства, выход стартстопного1 генератора соединен со счетным входом счетчика, установочный вход которого объединен с установочным входом регистра последовательных приближений и соединен с шиной начальной установки устройства, выход дешифратора конца цикла опроса соединен с входом регистра последовательных приближений, выходы которого соединены с первыми входами элементов И и с адресными входами постоянного запоминающего блока выходы элементов группы соединены с входами второго элемента ИЛИ, выход

0856

которого является тиной Ноиснравность. устройства, первые R выходов буферного регистра (где ) соединены с входами третьего элемлпа ИЛИ, выход которого соединен с первым входом первого элемента И-НЕ группы, второй вход которого подключен к инверсноьгу выходу (К+1)-го разряда буферного регистра, выход (К+1)-го разряда буферного регистра соединен с первым входом второго элемента И-НЕ группы, второй вход которого соединен с инверсным выходом (К-|-2)-го разряда буферного регистра, выход (К+2)-го разряда буферного регистра соединен с первым входом третьего элемента И-НЕ группы, второй вход которого соединен с инверсным выходом (К.-(-3)-го разряда буферного регистра, выход (и-1)-го разряда буферного регистра соединен с первым входом последнего элемента И-НЕ группы, второй вход которого подключен к инверсному входуh -го разряда буферного регистра, выходы элементов И-НЕ группы соединены соответственно с вторыми входами элементов И группы, кроме последнего, второй вход последнего элемента И группы соединен с выходом h-го разряда буферного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| Устройство для преобразования сигналов информационно-измерительной системы | 1982 |

|

SU1062751A1 |

| Устройство для ввода информации | 1988 |

|

SU1513438A1 |

| Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов | 1988 |

|

SU1640696A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU930656A1 |

| Устройство для ввода-вывода аналоговых сигналов | 1981 |

|

SU1015369A1 |

| Аналого-цифровой преобразователь с коррекцией погрешности | 1988 |

|

SU1688473A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Последовательно-параллельный аналого-цифровой преобразователь | 1987 |

|

SU1462475A1 |

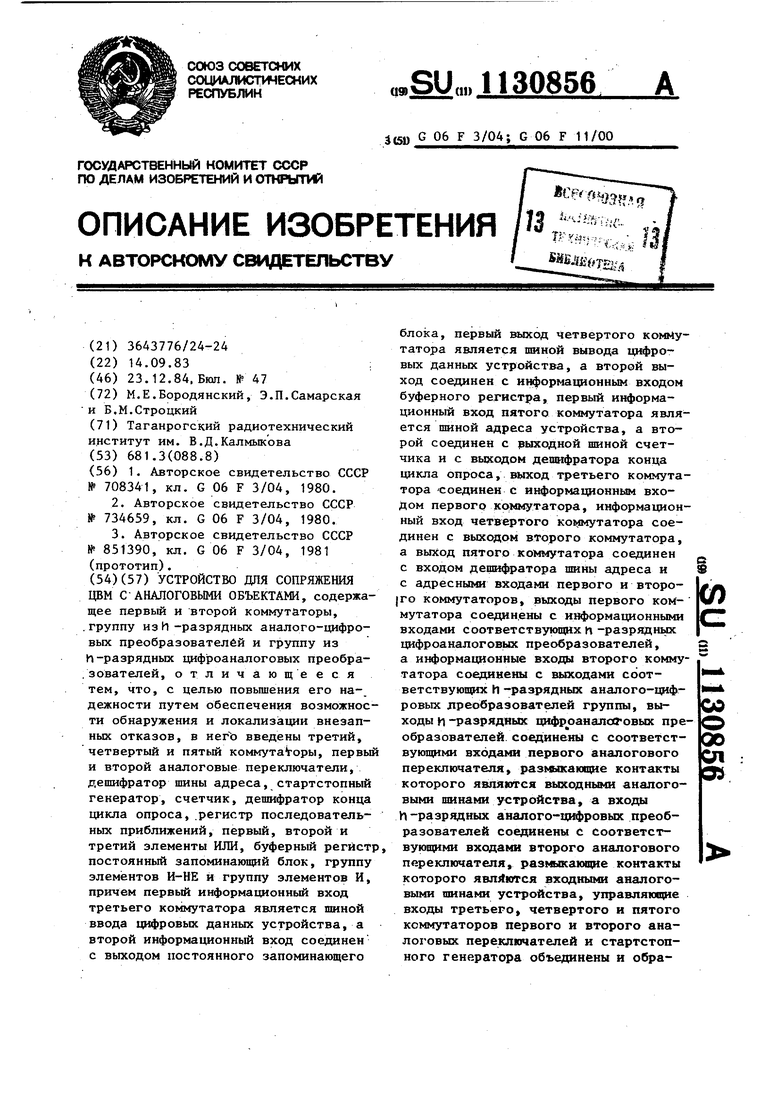

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С АНАЛОГОВЫМИ ОБЪЕКТАМИ, содержащее первый и второй коммутаторы, .группу из h -разрядных аналого-цифровых преобразователей и группу из h-разрядных цифроаналоговых преобра.зователей, отличающееся тем, что, с целью повышения его на-, дежности путем обеспечения возможности обнаружения и локализации внезапных отказов, в негЪ введены третий, четвертый и пятый коммутаторы, первый и второй аналоговые переключатели, дешифратор шины адреса, стартстопный генератор, счетчик, дешифратор конца цикла опроса, .регистр последовательных приближений, первый, второй и третий элементы ИЛИ, буферный регистр, постоянный запоминающий блок, группу элементов И-НЕ и группу элементов И, причем первый информационный вход третьего коммутатора является шиной ввода цифровых данных устройства, а второй информационный вход соединен с выходом постоянного запоминающего блока, первый выход четвертого коммутатора является шиной вывода цифровых данных устройства, а второй выход соединен с информационным входом буферного регистра, первый информационный вход пятого коммутатора является шиной адреса устройства, а второй соединен с выходной шиной счетчика и с выходом дешифратора конца цикла опроса, выход третьего коммутатора Соединен с информационным входом первого коммутатора, информационный вход четвертого ко1 |1мутатора соединен с выходом второго коммутатора, а выход пятого коммутатора соединен с входом дешифратора шины адреса и с адресными входами первого и второ|го коммутаторов, выходы первого коммутатора соединены с информационными входами соответствующих п -разрядных цифроаналоговых преобразователей, а информационные входы второго коммутатора соединешл с выходами соответствующих h-разрядных аналого-циф00 ровых лреобразователей группы, выходы и -разрядных цифроанапс(Говых преобразователей, соединены с соответстх ел вующими входами первого аналогового 99 переключателя paз б Iкaюlциe контакты которого являются выходными аналоговыми шинами у :тройства, а входы h-разрядных аналого-цифровых преобразователей соединены с соответствукнцими входами второго аналогового переключателя, pasffiAcaxMiQie контакты которого язлЛкгеся входными аналоговыми шинами устройства, управляю1ф1е входы третьего четвертого и пятого коммутаторов первого и второго аналоговых переключателей и стартстопного генератора объединены и обра

1

Изобретение относится к вычислительной технике и может быть исполь зовано в качестве устройства сопряжения цифровой и аналоговой вычислительных машин, а также для связицифровой вычислительной машины с объектом.

Известны различные устройства ввода-вывода аналоговой информации в цифровую вычислительную машину, например, устройство для ввода аналоговых величин в цифровую вычислительную машину, содержащее преобразователь напряжения в частоту, выхо которого через счетчик соединен с выходом преобразователя кода в частоту, преобразователь напряжения в код, выход которого соединен с выходом преобразователя параллельного кода в последовательный, преобразователь последовательного кода в параллельный, выход которого соединен с входом преобразователя кода в напряжение, генератор эталонной частоты, блок сравнения, пороговый блок три переключательных элемента и два аналоговых ключа, причем выходы преобразователей кода в частоту, параллельного кода в последовательный и кода в напряжение являются соответственно первым, вторым и третьим входами устройства, первый вход устройства и выход преобразователя кода в напряжение через первый переключательный элемент соединены с входом преобразователя напряжения в частоту, второй вход устройства и выход генератора эталонного напряжения через второй переключательный элемент соединен с входом преобразователя

3 1

напряжения в код, третий вхсчд устройства и выход преобразоЕШтеля пяраллельного кода в последовательный через третий переключательный элемент соеднр еиы с входом преобразователя последовательного кода в параллельный, первый и второй входы блока сравнения через первый и второй аналоговые ключи соответственно соединены с выходами генератора эталонной частоты и преобразователя кода в частоту соответственно, а выход блока сравнения через пороговый блок соединен с четвертым выходом устройства СП.

Однако введенные в состав устройства средства аппаратного контроля, нацеленные на проверку метрологических характеристик преобразователей, при использовании их для обнаружения внезапных отказов устройств имеют аппаратную избыточность, большое время проверки и не позволяют локализовать место неисправности.

Известно также устройство сброса информации, содержащее блок выборки мультиплексор, блок коррекции, блок программного управления, блок запуска, группу аналого-цифровых преобразователей, дешифратор, группу блоков аналоговой памяти, группу элементов задержки, причем входы блока выборки являются входами устройства, выход муль1иплексора является выходом устройства, а входы мультиплексора соединены с первыми выходами аналогоцифровых преобразователей группы, вторые выходы которых соединены с входами блока коррекции, первый выход которого подключен к первому входу блока запуска, а второй вход блока коррекции соединен с входом блока программного управления, входвыход которого является входом-выходом устройства, первый выход блока программного управления соединен с вторым входом блока запуска, второй выход блока программного управления подключен к входу дешифратора, выход которого подсоединен к входу блока выборки, первые входы.блока аналоговой памяти группы соединены с выходом блока выборки, вторые входы блоков аналоговой памяти группы и входы элементов задержки группы соединены с выходами блока запуска, а выходы блоков аналоговой памяти группы подключены к первым входам соответствую08564

1ЦИХ аналого-цифровых преобразователей группы, вторые входы которых соединены с выходами соответствующих элементов задержки группы 2. 5 Недостатком этого устройства сброса информации является отсутствие встроенных средств аппаратного контроля внезапных отказов узлов и блоков, что не позволяет осуществлять

0 автономную проверку устройства и, следовательно, требует проверки в составе системы, что неизбежно понижает коэффициент готовности системы

в целом. I

5

Наиболее близким техническим решением к изобретению является многоканальное устройство сопряжения источников и приемников информации, содержащее в каждом канале блок

0 унитарного кодирования, выход которого соединен через входной цифроаналоговый преобразователь с входом .блока суммирования, группу аналогоцифровых и цифроаналоговых преобра5зователей, блок памяти, коммутаторы, блок приоритета, распределительный блок, выходной аналого-цифровой преобразователь, элемент НЕ, деишфратор наличия не менее двух одновре менных сигналов, причем выходы аналого-цифровых преобразователей канала группы соединены с первой группой входа блока памяти, выходы блока памяти канала соединены с входа5 ми первой группы входов коммутаторов каналов и с входами блока приоритета канала, первая и вторая группы выходов блока приоритетов канала соединены с вторыми группами входов

0 соответственно коммутатора каналов и блока памяти, выход коммутатора канала соединен с соответствующей группой выходов устройства, выход блока суммирования канала соединен

5 с входами одноименных аналого-цифровых преобразователей каналов группы, выходы одноименных цифроаналоговых преобразоватапей каналов группы соединены с группой входов блока

0 суммирования соответствующего канала, выход блока суммирования канала соединен с входом выходного аналогоцифрового преобразователя, первый вход блока унитарного кодирования

5 канала соединен с соответствующим

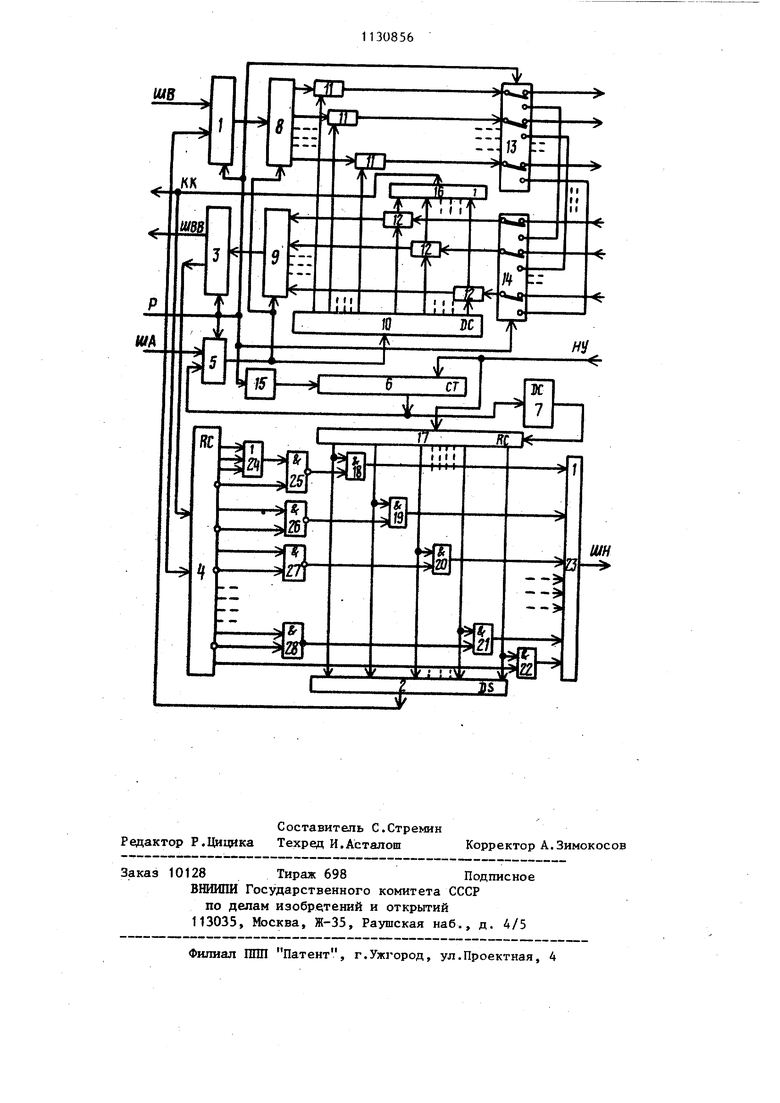

входом устройства, выходы блока памяти канала через дешифратор наличия не менее двух одновременных сигналов канала соединены с входами цифро-ан логовых преобразователей канала гру пы, а выход выходного аналого-цифро вого преобразователя канала через элемент НЕ канала соединен с вторым входом блока унитарного кодирования С 3 7, Недостатком известного многоканального устройства сопряжения исто ников и приемников информации является отсутствие аппаратных средств обнаружения и локализации внезапных отказов. Цель изобретения - повышение надежности путем обеспечения возможности обнаружения и локализации внезапных отказов. Поставленная цель достигается тем что в устройство, содержащее первый и второй коммутаторы, группу из h-разрядных аналого-цифровых преобразователей и группу изh-разрядных -цифроаналоговых преобразователей, введены третий, четвертый и пятый коммутаторы, первый и второй аналоговые переключатели, дешифратор шины адреса, стартстопный генератор, счетчик, дешифратор конца цикла опроса, регистр последовательных приближений; первый, второй и трети элементы ИЛИ, буферный регистр, постоянный запоминающий блок, группа элементов И-НЕ и группа элементов И причем первый информационный вход третьего коммутатора является шиной ввода цифровых данных устройства,а второй информационный вход соедин с выходом постоянного запоминающего блока, первый выход четвертого комму татора является шиной вывода цифровых данных устройства, а второй выход соединен с информационным входом буферного регистра, первый информационный вход пятого коммутатора является шиной адреса устройства, а второй соединен с выходной шиной счетчика и с выходом дешифратора ко ца цикла опроса, выход третьего ком мутатора соединен с информационным входом первого коммутатора, информационный вход четвертого коммутатора соединен с выходом второго коммутатора , а выход пятого коммутатора с входом дешифратора шины соединен адресными входами первог адреса и и второго коммутаторов, выходы йерв го коммутатора соединены с информационными входа1Ф1 соответствующих h-разрядных цифроаналоговых преобразователей, а информационные входы второго коммутатора соединены с вы-, ходами соответствующих и -разрядных аналого-цифровых преобразователей, группы, выходыh-разрядных цифроаналоговых преобразователей соединены с соответствующими входами первого аналогового переключателя, размыкающие контакты которого являются выходными аналоговыми шинами устройства, а входы h-разрядных аналого-цифровых преобразователей соединены с соответствующими входами второго аналогового переключателя, размыкающие контакты которого являются входными аналоговыми шинами устройства, управляющие входы третьего, четвертого и пятого коммутаторов первого и второго аналоговых переключателей и стартстопного генератора объединены-и образуют шину задания режима устройства, замыкающие контакты первого аналогового переключателя объединены с соответствующими замыкающими контактами второго аналогового переключателя, выходы дешифратора шины адреса соединены с соответствующими управляющими входами и -разрядных цифроаналоговых преобразователей группы и h-разрядных аналого-цифровьпс преобразователей группы, выходы фиксации конца кодирования И -разрядных аналого-цифровых преобразователей соединены с входами первого элемента ИЛИ, выход которого соединен с синхровходом буферного регистра и является шиной Конец кодирования устройства, выход стартстопного генератора соединен со счетным входом счетчика, установочный вход которого объединен с установочным входом регистра последовательных приближений и соединен с шиной начальной установки устройства, выход дешифратора конца цикла опроса соединен с входом регистра последовательных приближений, выходы которых соединены с первыми входами элементов И и соединены с адресными входами постоянного запоминающего блока, выходы элементов И группы соединены с входами второго элемента ИЛИ, выход которого является шиной Неисправность устройства. первые ft выходов буферного регистра (где ) соединены с входами третьего элемента ИЛИ, выход которого соеинен с первым входом первого элемента И-HI-; сруппы, второй вход которого подклн)чен к инверсному выходу (К+1)-го разряда буферного регистра выход (К+1)-го разряда буферного регистра соединен с первым входом второго элемента И-НЕ группы, второй вход которого соединен с инверсным выходом (К+2)-го разряда буферного регистра, выход (К+2)-го разряда буферного регистра соединен.с первым входом третьего элемента И-НЕ группы, второй вход которого подключен к инверсному выходу (К+3)-го разряда буферного регистра, выход (h-l)-ro разряда буферного регистра соединен с первым входом последнего элемента И-НЕ группы, второй вход которого подключен к инверсному входу h-ro разряда буферного регистра, выходы элементов И-НЕ группы соединены соответственно с вторыми входами элементов И группы, кроме последнего, второй вход последнего элемента И группы соединен с выходом h-го разряда буферного -регистра. На чертеже дана блок-схема предла гаемого устройства. Устройство содержит третий 1 коммутатор,постоянно запоминающий блок 2, четвертый 3 коммутатор, буферный регистр 4, пятый 5 коммутатор счетчик 6, дешифратор 7 цикла опроса первый 8 и второй 9 коммутаторы, дешифратор 10 адреса, группу цифроаналоговых преобразователей 11, груп 1пу аналого-цифровых преобразователей 12, первый 13 и второй 14 анало говые переключатели, генератор 15, первый элемент ИЛИ 16, регистр 17 последовательного приближения, элементы И 18 - 22, элементы ИЛИ 23 и элементы И-НЕ 25-28.. Устройство работает следующим об разом. Потенциалом на шине задания режима устройства Ъпределяется режим работ многоканального устройства ввода-вы вода , который бывает рабочим и конт рольным. В рабочем режиме потенциал на шине задания режима отсутствует.и в этом случае шина вывода данных че рез шинный коммутатор 1 поступает на вход коммутатора 8, шина вывода данных через пшнный переключатель 3 подключается к выходу коммутатора 9 шина адреса через шинньШ переключатель 5 подключается к адресным входам коммутаторов 8 и 9 и к входу де шифратора 10 шины адреса, стартстопный генератор 15 остановлен, контакты аналоговых переключателей 13 и 14 находятся в нормально замкнутом состоянии и выходы И-разрядных цифрйаналоговых преобразователей 11 группы непосредственно подключены к выходной аналоговой шине устройства, а входы h-разрядных аналого-цифровых преобразователей 12 поразрядного кодирования группы непосредственно подключены к входной аналоговой шине устройства. Вывод информации через устройство ввода-вывода осуществляется по шине вьшода через шинный переключатель 1, коммутатор 8 и группу ii-разрядных цифроаналоговых преобразователей 11. Адресация заданного канала цифроаналогового преобразования осуществляется по шине адреса, по сигналам которой коммутатор 8 подключает шину ввода к входу соответств тощего п -разрядного цифроаналогового преобразователя, а запись кода числа в регистр цифроаналогового преобразователя осуществляется по строб-сигналу с дешифратора 10 шины адреса. Далее информация в аналоговой форме через нормально замкнутые контакты аналогового преобразователя 13 поступает на выходную аналоговую шину устройства. Ввод информации через устройство ввода-вывода осуществляется по шине ввода через шинный переключатель 3, коммутатор 9 и и-разрядные аналогоцифровые преобразователи поразрядного кодирования. Адресация заданного канала аналого-цифрового преобразования осуществляется по шине адреса, по сигналам которой коммутатор 9 подключает шину вьтода устройства к выходу соответствующего п-разрядного аналого-1р фрового преобразователя поразрядногокодирования. Сигнал Начало кодирования на соответствующий аналого-цифровой преобразователь 12 группы поступает с дешифратора 10 шины адреса радиально. Сигнал Конец кодирования на шину Конец кодирования поступает с соответствуницего выхода адресованного аналого-цифрового преобразователя через элемент ИЛИ 16 по завершению процесса кодирования. Наличие сигнала Конец кодирования свидетельствует о готовности даннык на шине вывода. Аналоговая информация поступает на входы h-разрядных аналого-цифровых преобразова телей поразрядного кодирования с входной аналоговой шины через нормально замкнутые контакты аналогово го переключателя 14. Таким образом, в рабочем режиме устройство ввода-вывода работает по соответствующей адресации канала преобразования. При этом вьтод инфо мации осуществляется синхронно с адресацией, а ввод - после поступле ния сигнала Конец кодирования от ранее адресованного канала аналогоцифрового преобразования. При этом тракт цифроаналогового преобразования также состоит из Р каналов. Линейные И-разрядные цифроаналоговые преобразователи реализуют функцию, определяемую выражением Oьш(-OC, i.0I гдеОвых - напряжение на выходе ииФроаналогового пре образователя; UOH опорное напряжение; зн разрядные коэффициен ты двойного кода; п - число разрядов цифро аналогового преобразователя;. -- при включенном разряд при выключенном разря Линейные М -разряднью аналого-циф ровые преобразователи 12 поразрядно го кодирования описываются выражением . 1 г 1 ) UBx-l PnIIo l где Uj,f - напряжение на входе аналого-цифрового преобразо вателя ; k - масщтабный коэффициент; Р)«, - вес мпадшего разряда ана лого-цифрового преобразо вателя; cCi - разрядный коэффициент; i - номер такта, в котором происходит определение значения ot- ; п - число разрядов аналогоцифрового преобразовател В контрольном режиме сигнальный потенциал на щине задания режима устройства осуществляет переключени шинных коммутаторов 1, 3 и 5, анало говых переключателей 13 и 14 и запускает стартстопный генератор 15. При этом вход коммутатора 8 через шинный переключатель 1 подключается к выходу постоянно запоминающего блока 2, выход коммутатора 9 подключается через шинный переключатель 3 к входу буферного регистра 4, адресные входы коммутаторов 8 и 9 и вход дешифратора 10 шины адреса подключаются через шинный переключатель 5 к выходу счетчика 6, переключатели 13 и 14 осуществляют отключение выходов h-разрядных цифроаналоговых преобразователей 11 группы от выходной аналоговой шины, входов И-разрядных аналого-цифровых преобразователей 12 поразрядного кодирования группы от входной аналоговой шины и коммутируют выход каждого из Р цифроаналоговых преобразователей 11 гр.уппы .на соответствующий вход каждого из Р аналого-цифровых преобразователей 12 группы. С помощью Р-полюсных аналоговых переключателей 13 и 14 формируется измерительная схема, позволяющая подавать на вход каждого аналого-цифрового преобразователя 12 группы тестовый сигнал от соответствующего цифроаналогового преобразователя 11 группы. Таким образом, в контрольном режиме многоканальное устройство вводавывода отключается от внешних цепей, каналы вывода замыкаются на каналы ввода, адресация каналов осуществляется от выходной шины счетчика 6, который начинает работать в циклическом режиме от стартстопного генератора 15, в качестве входного и выходного регистров данных выступают соответственно выходная шина постоянного запоминакицего блока 2 и буферный регистр 4. Информация, заносимая с выходной шины постоянного запоминающего устройства через шинный переключатель 1 и коммутатор 8 в адресуемый цифроаналоговый -преобразователь 11 группы, преобразуется в аналоговую форму. Далее поступает на вход соответствующего аналого-цифрового преобразователя 12 группы, где преобразуется вновь в цифровую форму по команде с дешифратора 10 шины адреса, и через коммутатор 9 и шинный переключатель 3 заносится в буферный регистр 4. Построенная проверочная схема позволяет выявлять неисправные узлы как в 1ШФРОЕЮЙ части канала ввода-вывода, так и аналоговой. С помощью блоков 17-28 осуществляется обнаружение и локализация внезапных отказов. Основной объем оборудования многоканального устройства ввода-вывода составляют аналого-цифровые и цифроаналоговые преобразователи. Поэтому система обнаружения и локализации внезапных отказов ориентирована в первую очередь на поиск неисправностей в узлах преобразователей. Для устройств, имеющих нормированные мет рологические характеристики, которыми являются аналого-цифровые и цифро аналоговые преобразователи, разделяют внезапные отказы, приводящие к явному отказу устройства, и постепен ные, наличие которых может быть обнаружено только вследствие метрологи ческой поверки. Первый тип отказов характеризует надежность устройства в обычном смысле, второй - метрологи ческую надежность средств измерения. В основу работы системы обнаружения и локализации внезапных отказов положен тот факт, что физическая реализация и -разрядных цифроаналоговых преобразователей и И-разрядных аналого-цифровых преобразователей поразрядного кодирования предполагает наличие в каждом из них одинаковых наборов эталонных мер и логических операторов. Действительно, для реализации и -разрядного цифроаналогового преобразователя, математической моделью которого является выражение (1), необходим набор эталонов веса которых расположены по двоичному закону, и набор ключей, выполняющих роль двоичных коэффициентов cL,. Аналогично, для физической реализации и-разрядного аналого-цифрового преобразователя поразрядного кодирования, математической моделью которо го является вьфажение (2), необходим набор из И эталонов, веса которых расположены по двоичному закону, и h переключателей, реализующих двоич ные коэффициенты . В случае отказ любого из узлов, реализующих в стру туре цифроаналогового или аналогоцифрового преобразователей функцию эталона, коэффициента cL или логических устройств управления, произо дет грубый сбой в работе устройства равносильный отказу всего устройства 1 При условии равенства диапазонов выходного сигналам -разрядного цифроаналогового преобразователя и входного h-разрядного аналого-цифрового преобразователя поразрядного кодирования подключение входа аналого-цифрового преобразователя к выходу цифроаналогового преобразователя позволяет осуществлять проверку отсутствия внезапных отказов узлов. Действительно, если в структур.е цифроаналогового преобразователя для создания выходного сигнала Uj к.сумматору подключен эталон с весом 2 , и номинальное значение этого эталона удовлетворяет требованиям метрологической точности, то для компенсации входного сигнала Ux в структуре аналого-цифрового преобразователя поразрядного кодирования к вычитающему узлу необходимо также подключить эталон с весом , что найдет отражение в выходном коде аналого-1Щфрового преобразователя. Внезапный отказ узла, реализующего эталон, или ключевого элемента, реализующего коэффициент oti,, как в цифроаналоговом так и в аналого-цифровом преобразователях вызовет обязательное расхождение входного и выходного кодов проверочной схемы. Основываясь на сказанном, можно принять следующий порядок обнаружения и локализации внезапных отказов. Если для преобразователей зона допуска погрешности равна Д, то, подавая на вход цифроаналогового преобразователя код N,0 О О в котором только k-й разряд имеет единичное значение, причем входной код N удовлетворяет условию Usbixi: N-,2A-4-9 где Я-2h В6С младшего разряда, для исправных цифроаналогового и аналого-цифрового преобразователей на выходе последнего возможны следующие предельные кодовые комбинации: .1111 000 -при сложении погрещностей преобразо вателей с положительным знаком) - при сложении погрешностей преобразователей с отрицательным знаком . Объединение k младших разрядов в группу с эквивалентным весом 1 необходимо в том случае, еслий -7р. В случае применения в составе устройства ввода-вывода точных преоб разователей величинаfe 1. Для преобразователей с погрешностью, превышающей 0,25cj , или при наличии высокого уровня шумов в соединительных целях необходимо группу младших разрядов, различимых на фоне шумов, рассматривать как единый разряд с ве сом Q. Анализ кодовых комбинаций N, и N;) позволяет сделать следующие заключения : если в младших fe разрядах выходного кода аналого-цифрового преоб разователя появилась хотя бы одна единица, то можно считать, что эталонный вес Q исправен и он включился т.е. ключ тоже исправен при работе на включение; если (k + 1) разряд выходного кода аналого-цифрового пре образователя равен О, то ключо{.( не включен постоянно; другие значения указанных разрядов на выходе ана лого-цифрового преобразователя можно считать сбойными, свидетельствующими о наличии внезапных отказов. Таким образом, тестовая кодовая комбинация N) позволяет осуществить проверку на отсутствие внезапного отказа эталона с эквивалентным весом Q, правильную работу ключей oto на включение и ключа oi. I.+ 1) на вьпслю чение как в цифроаналоговом, так и в аналого-цифровом преобразователях объединенных в проверочной схеме. Причем, в целях анализа нет необходимости сравнивать всю кодовую комбинацию N с выходным кодом аналогоцифрового преобразователя, а достаточно проверить наличие единицы хотя бы в одном из k младших разрядов выходного кода и наличие нуля в (К+1)разряде. Следующей тестовой кодовой комбинаци-ей может быть код N, 000... 0101 1..l . Как и в предьщущем случае, после наложения norpemtiocTH днойного преобразования, на выходе аналого-цифрового преобразователя возможно получение следующих двух крайних по величине отклонения кодовых комбинаи;ий гЛ/г,-ООО...ШО,..0, h ...0110...О Анализируя коды N и Nj можно заметить, что при отсутствии внезапных отказов и при нахождении метрологических характеристик узлов в пределах нормы, единица в (fe+1)-M разряде сохраняется, а в (k+2)-M - появиться не может. Следовательно, если выходная кодовая комбинация находится в диапазоне между кодами Njii и , можно утверждать: эталон с весом Q(H41) исправен как в аналого-цифровом, так и в цифроаналоговом преобразователях; ключевые элементы o((it4) правильно работают на включении(предьщущим тестовым кодом они были проверены на выключение) ; ключевые элементы ai( правильно работают на выключение. Для вывода приведенных утверждений достаточно при наличии априорной информации о результатах проверки тестовым кодом N и о ведении проверки тестовым кодом Nj. проанализировать разряды f, и (fe + 1) выходного кода (аналого-цифрового преобразователя. Если (+1)-й разряд равен единице, а (+2)-й - нулю, то внезапные отказы проверяемых на данном этапе узлов отсутствуют. Все другие значения указанных разрядов кодовой комбинации N2.1 свидетельствуют о наличии внезапного отказа. Следующей тестовой кодовой комбинацией может быть код N3 О О ... О 1 0,0 1 1 ... 1, После наложения погрешности двойного преобразования на выходе аналого-цифрового преобразователя возможно получение следующих двух крайних по величине отклонения кодовых комбинацийNj,0 О 1000 О О 1 О ,1 О Из анализа Nji и N следует, что 1511 при отсутствии внезапных отказов, разряд (h+2) всегда равен единице, а разряд (k+3) всегда равен нулю. Проверкой состояния разрядов (k+2) и ()+3) выходного кода аналого-цифрового преобразователя осуществляется контроль исправности эталона разряда ((,) , правильность работы ключей с(.(к+2) на включение (на выключение они уже проверены) и правильность работы ключей o((y,j)Ha выключение. Аналогичным образом, сохраняя в тестовой кодовой комбинации значение младших разрядов как в N или в N3 и перемещая единицу в остальных (h-fe) разрядах последовательно в N, (k+3)-й разряд, в Ng - (+4)-й разряд и т.д., осуществляется контроль на отсутствие внезапных отказов узлов цифроаналогового преобразователя вплоть до разряда с номером (h-1) Знаковый разряд проверяется только на включении, так как при его неисправной работе.в выключенном положеНИИ бьша бы невозможна исправная работа цифроаналогового и аналого-цифрового преобразователей при проверке предьщущих разрядов. В контрольном режиме сигналов на шине начальной установки осуществляется сброс счетчика 6 и регистра 17 последовательных приближений. При этом нулевой код на выходной шине счетчика 6 адресует первый цифроаналоговый преобразователь 11 группы, а выходы регистра 17 последовательных приближений адресуют первое кодовое слово в постоянном запоминающем уст ройстве 2. Следует отметить, что ре гистр 17 последовательных приближений функционирует аналогично микро-: схеме 155 ИР 17(133 ИР 17), но на выходных шииах происходит последова тельное перемещение единицы. Постоянное запоминающее устройство 2 яв ляется ПЗУ статического типа, оснащенное выходным регистром. Однако, в силу специфических особенностей устройства, в нем используются толь ко ячейки с адресами: Первая тестовая кодовая комбинация N с выхода постоянно запоминающего устройства 2 через шинный переключатель 13 и адресованный с выхода счетчика 6 ка,нал коммутатора 8 поступает на вход первого цифроаналогового преобразователя 11 группы. Адресованный с выхода того же счетчика 6 через дешифратор 10 шины адреса соответственно тот же цифроаналоговый преобразователь по строб-сигналу с дешифратора записывает тестовый код N в свой регистр и преобразует его в аналоговый сигнал, который поступает на вход первого аналого-цифрового преобразователя 12 группы. После некоторой выдержки времени, устанавливаемой тактовой частотой стартстопного генератора 15, необходимой для установления аналогового сигнала на выходе цифроаналогового преобразователя с заданной точностью, счетчик 6 насчитает единицу, и адрес на его выходной шине изменяется. Следует отметить, что в устройст-, ве ввода все каналы хщфроаналогового преобразования имеют четные адреса, а каналы аналого-цифрового преобразования - нечетные. Насчитывание первой единицы в счетчике 6 приводит к запуску первого аналого-цифрового преобразователя 12 в группе сигналом запуска через дешифратор 10 шины адреса. Одновременно выход кодирующего аналого-цифрового преобразователя через адресуемый канал коммутатора 9 и шинный переключатель 3 подключается к входу буферного регистра 4. По завершению процесса кодирования по сигналу Конец кодировани}Р через Р-входовую схему ИЛИ 16 результат преобразования заносится в буферный регистр 4. Необходимым условием является ,;од, где Тр - период стартстопного генеpaiTopa 15; время кодирования аналогоцифрового преобразовател. Таким образом, результат двойного преобразования тестового кода N заносится в буферный регистр 4. При этом осуществляется проверка первых К и (k+1)-ro разрядов первых преобразонателей 11 и 12 в группах. Дейст вительно, если в первых / разрядах есть хотя бы одна единица, а в (k+1)-M разряде нуль, то на входе элемента И-НЕ 25 будут две единицы, а на ее выходе О. В этом случае ,на выходе элемента И 18 будет также нуль, несмотря на то, что она разбло кирована по первому входу от регистра 17 последовательных приближений. Нуль на выходе элемента И 18 соответ ствует нулю на шине неисправности (выход (п-Й)-входовой схемы ИЛИ 23). Если же ни на одном из первых К выходов буферного регистра 4 не будет единицы или на инверсном (Ц+1)-м выходе будет нуль, что свидетельствует о сбое в проверяемых цифроаналоговом или аналого-цифровом преобразователях, то на выходе элемента И-НЕ 25 появляется единица, которая пройдет через элемент И 18 и через элемент ИЛИ 23 на шину неисправности. Появле ние единицы на выходе элемента ИЛИ 23 свидетельствует о наличии сбоя. При насчитывании следующей единицы в счетчик 6 происходит установка следующего адреса на его выходе. Теперь адресуется второй цифроаналоговый преобразователь 11 группы, в который аналогично описанной последова тельности заносится код из постоянно го запоминающего блока 2. При насчитывании следующей единицы в счетчик 6 формрфуется код, адресующий второй аналоготцифровой преобразователь 12 группы, результат кодирования которого, аналогично описанному процес су для первого аналого-цифрового пре образователя группы, заносится в буферный регистр 4. Полученная кодовая комбинация с помощью элементов И18И22, элементов И 23, 24, элементов И-НЕ 25-28, проверяется на отсутствие сбоя. Далее адресуется третий 1У1фроаналоговый преобразователь 11 группы, а затем третий аналого-цифро вой преобразователь 12 группы и т.д. Таким гбразом, осуществляется проверка всех цифроаналоговых 11 и аналого-цифровых 12 преобразователей групп попарно при тестовом коде N;, . Последним адресом, который формирует счетчик 6, является адрес (2Р-1). При поступлении очередного импульса счетчик 6 сбрасывается, т.е. формирует вновь нулевой адрес, а дещифратор 7 конца цикла опроса формирует импульс на входе регистра 17 последовательных приближений, вследствие чего единичный потенциал перемещает.ся с первого выхода регистра 17 на второй. При этом разблокируется элемент И 19, а на выходе постоянного запоминающего блока 2 устанавливается следующая тестовая кодовая комбинация Nji. Процесс занесения кода Nj в цифроаналоговые преобразователи 11 группы, считывание результатов двойного преобразования с аналого-цифровых преобразователей 12 группы и занесение кодовой в буферный регистр 4 происходит аналогично, как и для кода N. Однако результат двойного преобразования для тестового кода N должен обязательно содержать единицу в (Ь+1)-м разряде и нуль - в (+2)-м разряде. Выполнение этого условия проверяется элементами И-НЕ 26. и И 19. Результат проверки определяется состоянием выхода элемента ИЛИ 23. После проверки всех пар цифроаналоговых 11 и аналого-цифровых 12 преобразователей групп попарно на тестовый код Nj вновь происходит сброс счетчика 6 и насчитывание очередной единицы в регистр 17 последовательных приближений. Это.приводит к началу нового цикла проверки при кодовой комбинации NJ, которая считывается из постоянного запоминающего устройства 2. Проверка выходной кодовой комбинации осуществляется аналогично с помощью элементов И-НЕ 27 и И 20. После проверки всех цифроаналоговых и аналого-цифровых преобразователей последней кодовой комбнацией N(h-K) процесс может продолжаться с выходом на новый макроцикл, так как регистр 17 последовательных приближений работает по циклическому принципу. Выход из контрольного режима осуществляется изменением потенциала на шине задания режима устройства. Таким образом, контролируя состояние выхода элемента ИЛИ 23, можно определить факт наличия отказов катастрофического характера в структуре цифроаналогового или аналого-цифрового преобразователей. При этом неисправность определяется с точностью до номера разряда в паре преобразователей, которые адресуют в данный момент. 191 Важной характеристикой-системы обнаружения и локализации внезапных отказов является полное время проверки всех каналов устройства ввода-вы1юда, определяемое выражением (h-K)(t,+tyHK te. + tc|}|, ( полное время проверки всех каналов устройства вводавывода ; время установления контрол ного режима, включающее время срабатывания шинных переключателей и аналогово го переключателя; tj - время занесения тестовых в регистры памяти кодов цифроаналоговых преобразователей;- время установления аналого вых. сигналов на выходах цифроаналоговых преобразователей с заданной точностью;- время кодирования аналогоцифровмх преобразователей 6 время считывания результатов кодирования аналог 1цифровых преобразователей из их выходных регистров; время анализа выходного кода аналого-цифровых преобразователей;число параллельных контуров проверки. Пользуясь выражением (3) для многоканального устройства ввода-вьтода,. имеющего в своем составе 6А канала цифроаналогового преобразования и 64 канала аналого-цифрового преобразования, при средних характеристиках преобразователей, т.е. мкс, ti, 15 МКС, t|, 25 МКС, Чг мкс, мкс, мкс, , , получают tv,p -ic 0,2 с. Столь малое время проверки многоканального устройства ввода-вывода позволяет осуществлять контроль перед каждым циклом его использования без сколь-нибудь значительного задействования ЦВМ для этих целей. Наоборот, программная реализация поиска и локализации внезапных отказов требует значительного времени задействования ЦВМ для проверки многоканального устройства ввода-вывода. Основная причина заключается в длинных программах-драйверах обмена.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для ввода аналоговых величин в цифровую вычислительную машину | 1977 |

|

SU708341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-12-23—Публикация

1983-09-14—Подача