(5) УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ ДВУХСТУПЕНЧАТОЙ

КОММУТАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивной двухступенчатой коммутации | 1982 |

|

SU1070587A1 |

| Устройство для адаптивной коммутации | 1977 |

|

SU660291A1 |

| УСТРОЙСТВО для АДАПТИВНОЙ КОММУТАЦИИ | 1972 |

|

SU335711A1 |

| Адаптивный коммутатор | 1982 |

|

SU1061170A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1449989A1 |

| Устройство для передачи информации | 1977 |

|

SU746660A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

1

. Изобретение относится к телемеханике и может использоваться для коммутации сигналов в адаптивных измерительных системах с двумя ступенями коммутации.

Известно адаптивное измерительное устройство, содержащее тактовый генератор, коммутатор, соединенный с анализатором и ключевым элементом, блок памяти, триггеры и формирователь адреса , Это устройство применяется в адаптивных измерительных системах с одной ступенью коммутации П.

Недостатком этого устройства яв- . ляется невозможность его использования в адаптивных измерительных системах с двухступенчатой коммутацией.

Наиболее близким по технической сущности к предлагаемому является устройство для адаптивной коммутации, содержащее блоки сравнения,сумматор, выход которого соединен со входом делителя, блок программного

управления, выходы которого подключены к управляющим входам коммутато- ра, переключатель, блок датчиков, выходы которого соединены со входами анализатора информации и с информационными входами коммутатора, блок кодирования, один вход которого связан с выходом первого блока сравнения , входы которого непосредственно и через блок кодирования соединены с выходами делителя, выходы анализатора информации связаны со входами сумматора, один вход блока программного управления через переключатель соединен с выходами второго блока сравнения и сумматора, другой вход с выходом блока кодирования .

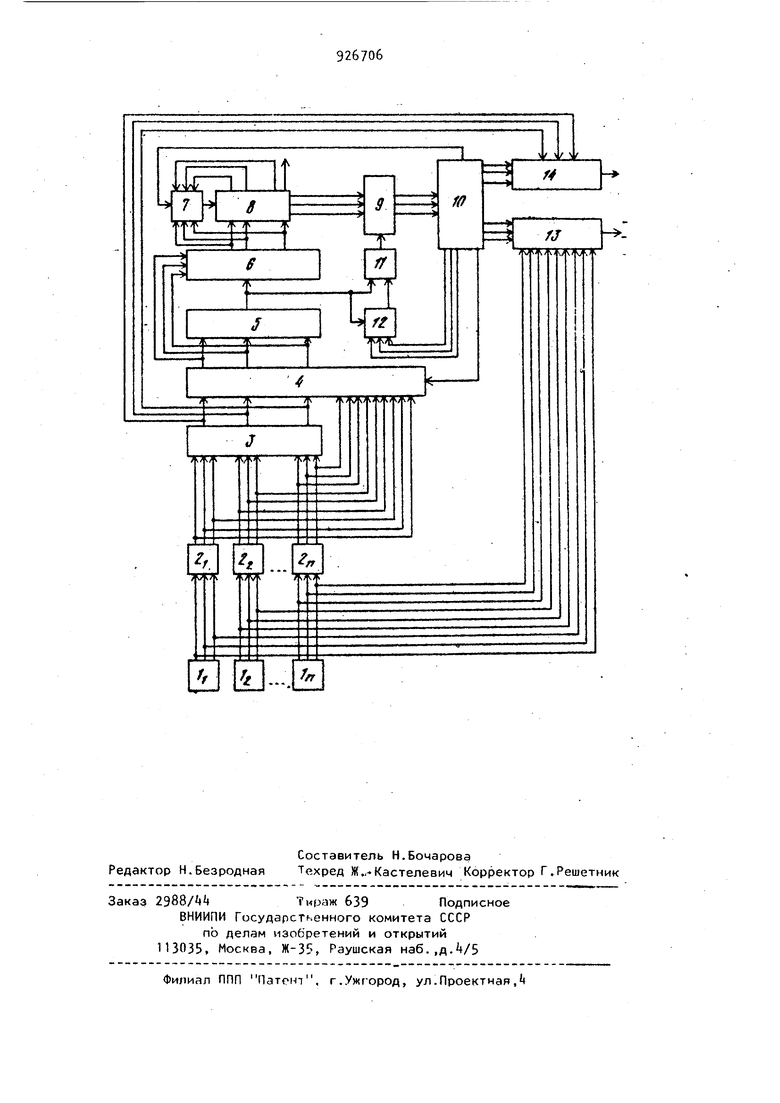

Недостаток такого устройства состоит в том, что оно не обеспечивает согласования частот первой и второй ступени коммутации и обслуживания большого числа датчиков информации, т.е. объем обрабатываемой информации невелик. мутации получить последовател HocTta равностоящих отсчетов и равно мерное следование отсчетов по каждо из каналов. Кодированные-сигналы ад ресной системы поступают на входы блока 9 программного управ ления, причем их разрядность связана с зйличинами соотношениемЬоГ 2 Переход от отHocPiтельных допустимых частот опроса первой ступени коммутации 4 допустимым частотам опроса i ojll блоке 9 осущес вляется распределением последовател ности импульсов опроса, поступающих с выхода блока 5 с частотой F на п последовательностей с частсгтами S соответствии с полу ченной адресной системой. Набор допустимых частот V Км поступаю щих на входы второго блока 12 сравнения из блока 10 памяти, соответствует нескольким скоростям записи данных на регистре {не показан), нескольким несущим частотам в канале связи или тактовым частотам ЦВМ. В процессе работы устройства на пер вом этапе в блоке 12 сравнения выби рается ближайшее к F значение F. Необходимое в этом случае распределение между каналами разностей частоты &f осуществляется в блоке 9 в соответствии с набором {bjjj так, что величина дГ распре деляется между каналами с весами ГЬлД . Режим подачи на вход блока 9 программного управления последовательностей импульсов с частотами F или f устанавливается с помощью переключателей 11. При поступлении информационных сигналов в бло 10 памяти из блока 9 программного управления начинается второй этап рЬ боты устройства - определение набора допустимых частот второй ступени коммутации. Вырабатывается управляющий импульс, закрывающий входы блока 4 переключателей, соединенных с выходами первого сумматора 3 иоткрывающий входы блока 4 переключателей соединенные с выходами первого анализатора 2 информации. Набор необходимых частот опроса второй ступени коммутации ft « с помощью- сум матора 5 и делителя 6 преобразуется в набор относительнь1х необходимых 6 tj 1 в соответстi 1J1 ВИИ с выражением С выходов делителя 6 сигналы, пропорциональные величинам подаются на входы блока 8 кодирования, который находит оптимальные величины относительных допустимых частот оп-, роса второй ступени коммутации и кодированные сигналы адресной систеfn- . В данном случае L. 11i J 1 1 Я ГГо где j - допустимые частоты опроса каналов j-ro коммутатора, при использовании которых на выходе второй ступени коммутации можно получить последовательность равностоящих отсчетов и равномерное следование отсчетов по каждому из каналов, На этом этапе в блок 7 сравнения из. блока 10 памяти вводится значение величины 1 из набора допустимых погрешностей приближения Sjl . При превышении погрешностью приближения, набора - --UElii r ответствующего значения допустимой погрешности необходимо изменить на. тГг 1 Ч; «I 1, , т.е. перестроить адресную систему и передать ее на приемный конец. Переход от относительных допустимых частот опроса второй ступени коммутации {Ъ ii 1 ° пустимым частотам опроса в блоке 9 осуществляется распределением последовательности импульсов опроса, поступающих с выхода сумматора 5 с частотой fo на m J последоваг «- 1 Шгами t,j в сотельностей с частотами ответствии с полученной адресной системой и частотой fр, поступающей , на вход блока 9 программного управления из блока 10 памяти через блок 12 сравнения и переключатель 11. При поступлении информационных сигналов в блок 10 памяти вырабатывается управ лякяций импульс, открывающий mij входов блока переключателей, соединенных с т выходами второго анализатора информации. Дальнейшие действия устройства аналогичны описанным выше. Цель изобретения - повышение информативности устройства. Указанная цель достигается тем, что в.устройство для адаптивной коммутации, содержащее первую группу датчиков, выходы которой соединены с первыми информационными входами первого коммутатора и входами первого анализатора информации, выходы которого соединены с первыми входами первого сумматора, делитель частоты, выходы которого связаны с первыми входами первого блока сравнения и первыми входами блока кодирования, первые выходы которого роединены со вторыми входами первого блока сравнения, выход которого соединен со вторым входом блока кодирования,вторые выходы блока кодирования связаны с первыми входами блока программного управления, второй вход которого соедине с выходом переключателя,первый вход которого связан с выходом второго блока сравнения введены п-1 группа датчиков, п-1 анализатор информации, второй сумматор, второй коммутатор, бло,к памяти и блок переключателей, выходы п-1 групп датчи ков соединены с соответствующими п-1 информационными входами первого коммутатора и входами соответствующих п-1 анализаторов информации, выходы которых связаны с соответствующими п-1 входами первого сумматора, выходы всех п анализаторов информации соединены с соответствующими пер выми информационными входами блока переключателей, выходы первого сумма тора связаны с информационными входа ми второго коммутатора и соответству ющими вторыми информационными входами блока переключателей, выходы которого соединены с первыми входами делителя частоты и входами второго сумматора, выход второго сумматора связан со вторым входом делителя частоты, вторым входом переключателя и первым входом второго блока сравнения, выходы блока программного управления соединены со входами блока памяти, первый, второй, третьи четвертые и пятые выходы блока памяти связаны соответственного с тре-: тьим входом первого блока сравнения управляющим входом блока переключателей j, вторыми входами творого блока сравнения, управляющими входами первого коммутатора и управляющими входами второго коммутатора, выходы коммутаторов соединены с выходами устройства. На чертеже изображена структурная блок-схема устройства. Устройство содержит п групп датчиков, анализаторов 2 ,-2 информации, первый сумматор 3, блок U переключателей, второй сумматор 5,делитель 6 частоты, первый блок 7 сравнения , блок 8 кодирования, блок 9 программного управления, блок 10 памяти, переключатель 11, второй блок 12 сравнения, первый коммутатор 13, второй коммутатор 1. Измеряемые сигналы непрерывно подаются с выходов п трупп 1 - 1| датчиков информации на выходы п анализаторов 2.-2р информации, каждый из которых определяет текущие необходимые частоты опроса каналов (не показан) {{,J} , Ui,j- необходимая частота опроса 1-го канала j-й группы датчиков информации. Далее с помощью сумматора 3 вычисляются необходимые частоты опроса первой ступени коммутации . Блок/ переключателей работает таким образом, что на первом этапе (определение допустимых частот первой ступени коммутации) выходы блока k переключателей , соединенные с выходами анализаторов информации, закрыты. С помощью сумматора 5 и дели- , теля 6 частоты находятся относительные необходимые частоты опроса Ад; в соответствии с выражением с выходов делителя Ь частоты сигналы, пропорциональные величинам подаются на входы блока 8 кодирования, который находит оптимальные величины относительных допустимых частот опроса первой ступени коммутации {toj}j и кодированные сигналы адресной системы. В данном случае Гс I Д - дЬпустимые частоты опроса каналов, при использовании которых на выходе первой ступени ком7Устройство работает таким образом д тех пор, пока в блок ТО памяти не поступят значения последнего набора допустимых частот опрела второй сту пени коммутации , IP этом сигналы, соответствующие наборам поступают на управляющие входы коммутатора Н, а сигналы соответствуют наборам ГГ,,)11ГГТ-1П 11 iiiJ-1 J-1 управляющие входы коммутатора 13. Предлагаемое устройство имеет большую информативность по сравнени с известными и позволяет создавать адаптивные телеметрические системы с двумя ступенями коммутации, обладающие способностью обработки бояЬшого объема информации за счет увеличения числа обслуживаемых групп датчиков при небопьшом объеме служеб- 20 ми

ной информации.

Формула изобретения

Устройство для адаптивной двухступенчатой коммутации, содержащее первую группу датчиков, выходы которых соединены с первыми информационными входами первого коммутатора и входами первого анализатора информации, выходы которого соединены с первыми входами первого сумматора, делитель частоты, выходы которого соединены с первыми входами первого блока сравнения и первыми входами блсЗка кодирования, первые выходы которого соединены с вторыми входами первого блока сравнения, выход которого соединен с вторым входом блока кодирования, вторые выходы блока кодирования соединены с первыми входами блока программного управления, второй вход которого соединен с выходом переключателя, первый вход которого соединен с выходом второго блока сравнения, отличающеблока переключателей, выходы которого соединены с первыми входами делителя частоты и входами второго сумматора, выход второго сумматора соединен с вторым входом делителя частоты, вторым входом переключателя и первым входом второго блока сравнения, выходы блока программного управления соединены с входами блока памяти, первый, второй, третьи, четвертые, и пятые выходы блока памяти соединены соответственно с третьим входом первого блока сравнения, управляющим входом блока переключателей, вторыми входами второго блока сравнения , управляющими входами первого коммутатора и управляющими входами второго коммутатора, выходы коммутаторов соединены с выходами устройства

Источники информации, приняьые во внимание при экспертизе

Авторы

Даты

1982-05-07—Публикация

1980-04-07—Подача