.сумматор по модулю два, третий и четвертый элементы И, первые входы которых объединены и являются одним из входов блока, вторые входы третьего и четвертого элемеЕ1тов И подключены к выходу элемента ИЛИ, а третьи

входы - к В1-.1ХОДУ сумматора по модулю два, нходи которого и вход1:Л элемента ИЛИ соотЕетственно объедине -щ и я:вля отся другими входаг/ш блока, выходами которого являются выходы третье о И- четвертого элементов И,-.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| ОТКАЗОУСТОЙЧИВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2014 |

|

RU2579954C2 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Запоминающее устройство | 1981 |

|

SU972590A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1374286A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

1. ЗАПО№ НА10ЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ИНФОРМАЦИИ, содержащее накопитель, блок кодирования информации, блоки коррекции ошибок, регистры, коммутатор, триггер, блок обнаружения ошибок, формирователь сигналов ошибок, блок суш-шрования сигналов ошибок, дешифраторы/ элементы И и элемент НЕ, причем выходы блока кодирования информации соединены с одними из входов комг.1 татора, выходы которого подключены к информационным входам накопителя, адресные входы которого соединены с адресными.входами первого регистра, один из выходов и вход разрешения считывания которого подключены соответственно к одному из входов и одному из выходов блока обнаружения ошибок, другие входы которого и один из входов блока суммирования сигналов ошибок соединены с выходами формирователя сигнала ошибок, входы которого подключены к выходам накопителя, входам второго регистра и одним из входов первого блока коррекции ошибок, выходы которого соединены с одними из входов второго блока коррекции ошибок, выходы второго блока коррекции ошибок подключены к входам третьего регистра, другие входыKONMyTaTopa соединены соответственно с инверсными выходами второго регистра, первьоми входами первого и второго элементов И и выходом триггера, единичный вход которого подключен к выходу элемента НЕ и второму входу второго элемента И, выход которого соединен с входом разрешения записи первого регистра, другие выходы которого подключены к входам первого дешифратора и другим входам блока сум.мирования сигналов ошибок, выходы которого соединены с входа vM второго дешифратора, выходы первого и второго дешифраторов подключены соответственно к другиь входам второго и первого блоков коррекции ошибок, второй вход первого элемента И и вход элемента НЕ соединены с другим выходом блока обнаруи жения ошибок, выход третьего регистра, первый и второй выходы блока кодирования информации являются соответственно информационным выходом, информационным и управляющим входами устройства, нулевой вход триггера и выход первого элемента И являются соответственно.установочным, входом и выходом сигналов прерывания устройства, другой выход 1 блока обнаружения ошибок и адресные входы первого регистра являются О соответственно управляющим выходом ж и адресными входами устройства, отличающееся тем, что, с ц.елью повышения быстродействия устройства, в него введены блок сравнения, блок приоритета и постоянный накопитель, выходы которого подключены к информационным входам первого регистра, а входы - к выходам блока приоритета, входы которого соединены с выходами блока сравнения, одни из входов которого подключены к прямым выходам второго регистра, а другие входы - к выходам накопителя. 2. Устройство по П.1, о т л ичающееся тем, что блок обнаружения ошибок содержит элемент ИЛИ,

Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам. Известно запом11нающее устройство с Коррекцией информации, которое со держит накопитель, схемы логики обращения и коррекции одного отказа и одного сбоя элементов памяти или двух отказов элементов памяти и име ет, словарную организацию Cl. Недостатком данного устройства является низкое быстродействие. Наиболее близким к предлагаемому является запоминаощее устройство с коррекцией информации, содержадцее первые и вторую входные шины данных соединенные с первыми и вторым входами блока кодирования, выходами соединенного с Первыми входами коммутатора, вторые и третий входы ком мутатора соединены соответственно с инверсными выходами регистра кодового слова, выходом триггера и первыми входами первого и второго элементов И, причем счетный вход триггера соединен с вторым входом второго элемента И и выходом элемента НЕ, установочный вход триггера соединен с ишной установки в нуль, вход элемента НЕ соединен с первым выходом блока определения ошибок, шиной управления и вторым входом первого элемента И, выходы коммутатора соединены с входами накопителя, выходными 1 шинаг ш соединен ного с входами регистра кодового слова, блока вычисления синдрома и первыми входами второго блока кор рекции ошибок, выходы блока вычисле ния синдрома соединены с первыми входами блока получения второго при нака и первыми входами блока опреде ления ошибок, второй вход блока определения ошибок соединен с пер,вым выходом регистра хранения признаков, выходами соединенного с вторы входами блока получения второго при нака И: входами блока декодирования первого признака, второй выход блока определения онибок соединен с пе вым входом регистра хранения призна ков, второй вход которого соединен с шиной адреса и .вторыми входами накопителя, третий вход регистра хранения признакои соединен с выходом второго элемента И, выход первого элемента И соединеЕ: с шиной прерывания, вы.ходы блока получения в орого Г1ризна1 ;а соединены с входами блока декодирования второго призна.-ка, выходы блоков декодирования первого и второго признаков соединен;соответственно с вторыми входами первого и второго блоков коррекции ошибок, первые входы первого блока коррекции ошибок соединены с выходами второго блока коррекции ошибок, первые и второй выходы первого блока коррекции ошибок соединены с. первыми и BTOpuN входаг.да выходного регистра, выходы которого являются выходами устройства 12}, Недостатком известного устройства является низкое быстродействие в режиме ко1эрекции однократных ошибок из-за необходкмосаи гаждый раз при появлении оигнбок определять памяти путем повторной записи в накопитель скорректированного счкта:-ного слова и повторного вычислени;: признака ошибки для распозназаиия ее причины произошел сбой или элс;мента ., Цель изобретения - лоБышение быстродействия устройства, Поставленная цель досткгаетоя тем, что в 3anoivU-iHaioiiiee устройстве с коррекцией информацией, содержаш.ес накопитель, блок кодировани.я информации , блоки коррекции ошибок, регистры , ком утатор, триггер, блок обнаружения ошибок, формирователь сигналов ошибок, блок суь мирования сигналов ошибок, дешифраторы, эл.ементы И и элемент НЕ, причем выходы блока кодирования информации соединены с одними из входов та тора, выходы которого подключены к информационные входаг 1 накопителя, адресные входы которого соединены с адресн з ми входама первого регистра, один из выходов и вход, разрешения считывания подключенк соответствеико к одном;/ .из входов и одному из выходов блока обнаружения ошибок, другие входы которого и один из входов блока суг-о-шрования сигналов ошибок соедииень: с выходами формирователя сигнала ошибок входы которого подключены к выходам накопителя, входам второго регистра и одним из входов первого блока коррекции ошибок, выходы которого соединены с одними из входов второго блока коррекции ошибок, выходы втоIporo блока коррекции ошибок подключены к входам третьего регистра, другие входы коммутатора соединены соответственно с инвepcны 1и выходами второго регистра, первыми входами первого и второго элементов И и выходом триггера, единичный вход которого подключен к выходу элемента НЕ и второму входу второго элемента И, выход которого соединен с входом разрешения записи первого регистра, другие выходы которого подключены к входам первого дешифратора и другим входам блока суммирования сигналов ошибок, выходы которого соединены с входами второго дешифратора, выходы первого и втрого дешифраторов подключены соотвественно к другим входам второго и первого блоков коррекции ошибок, втрой вход первого элемента И и вход элемента НЕ соединены с другим выходом блока обнаружения ошибок, выход третьего регистра, первый и второй входы блока кодирования информации являются соответственно информационным выходом, информационным и управляющим входами устройства, нулевой вход триггера и выход первого элемента И являются соответственно устаь овочным входом и выходом сигналов прерывания устройства, другой выход блока обнаружения ошибок и адресные входы первого регистра являются соответственно управляющим выходом и адресными входами устройсва, введены блок сравнения, блок приоритета и постоянный накопитель, выходы которого подключены к информационным входам первого регистра, а входы - к выходам блока приоритета, входы которого соединены с выходами блока сравнения, одни из входов которого подключены к прямым выходам второго регистра, а другие входы - к выходам накопителя.

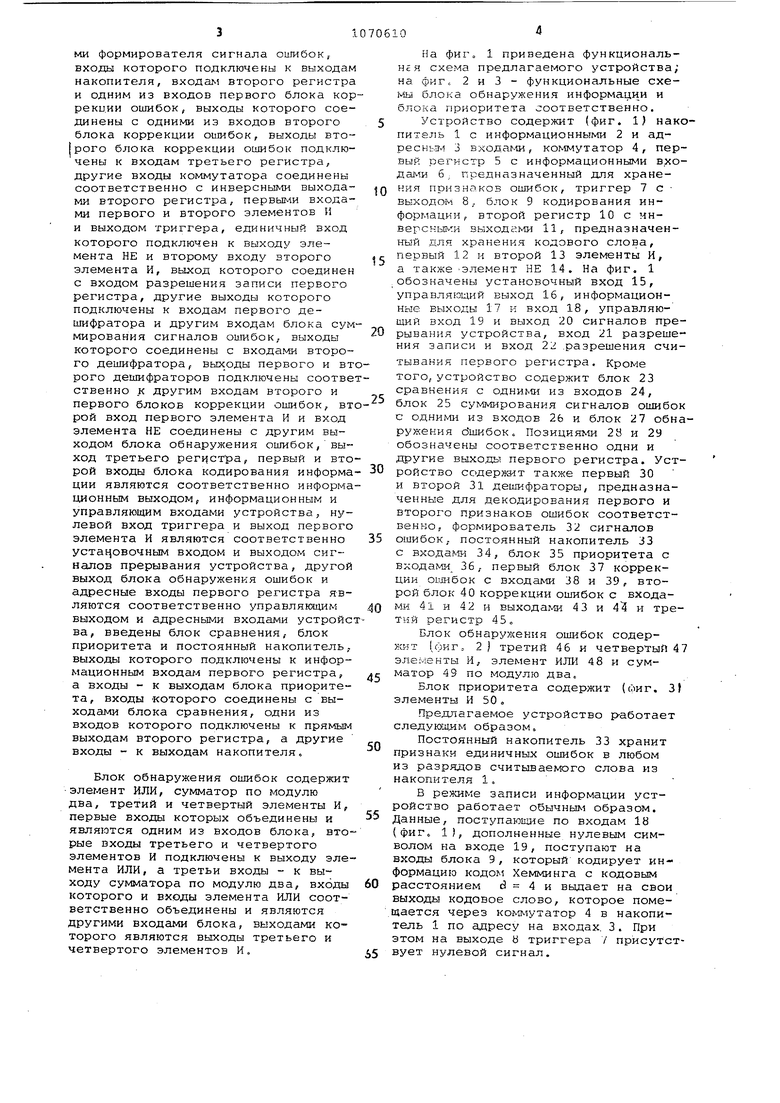

Блок обнаружения ошибок содержит элемент ИЛИ, сумматор по модулю два, третий и четвертый элементы И, первые входы которых объединены и являются одним из входов блока, вторые входы третьего и четвертого элементов И подключены к выходу элемента ИЛИ, а третьи входы - к выходу сумматора по модулю два, входы которого и входы элемента ИЛИ соответственно объединены и являются другими входами блока, выходами которого являются выходы третьего и четвертого элементов И

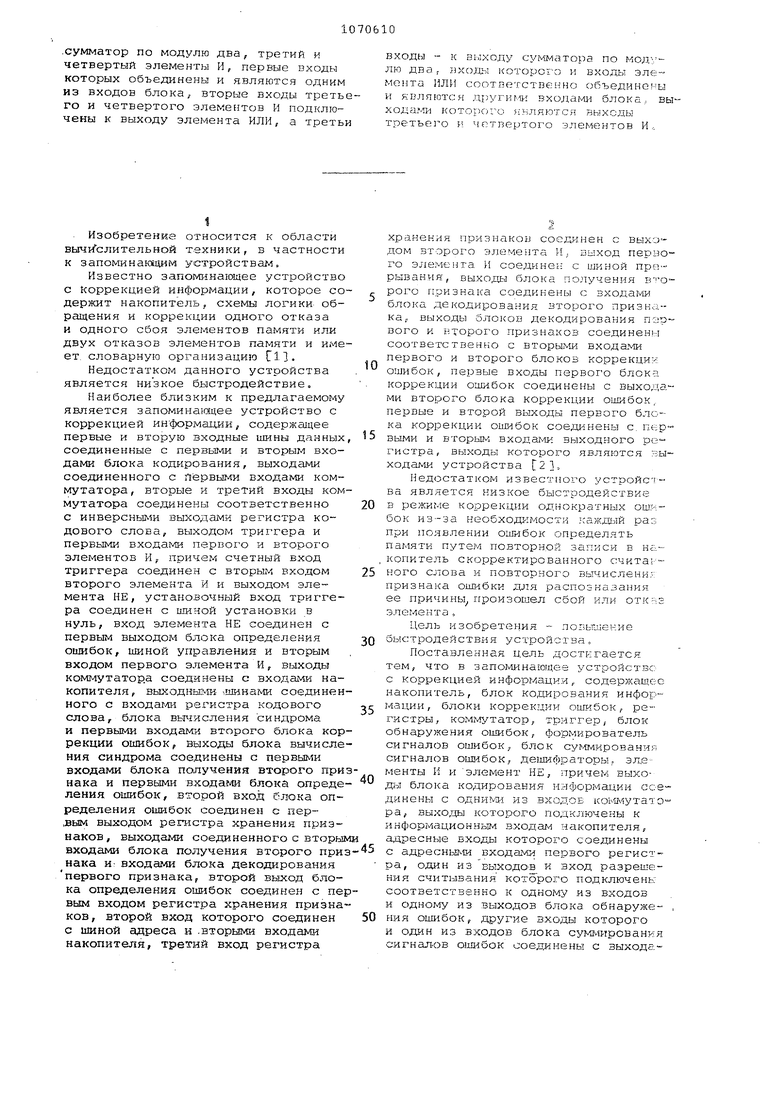

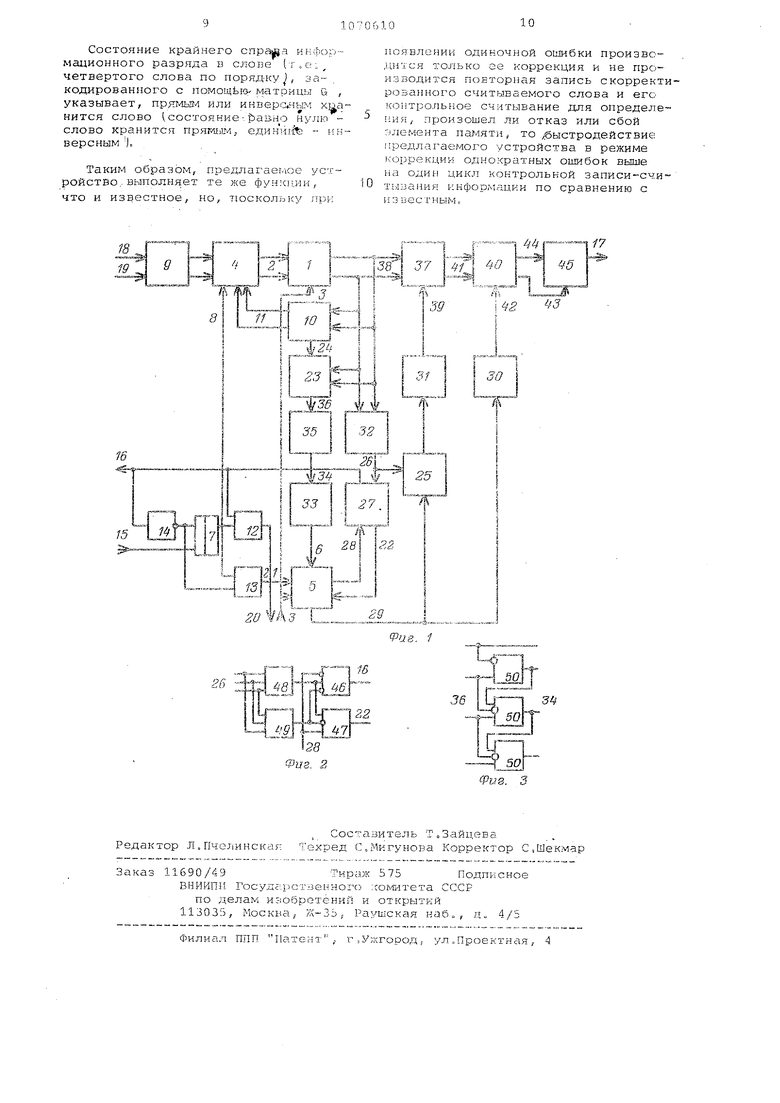

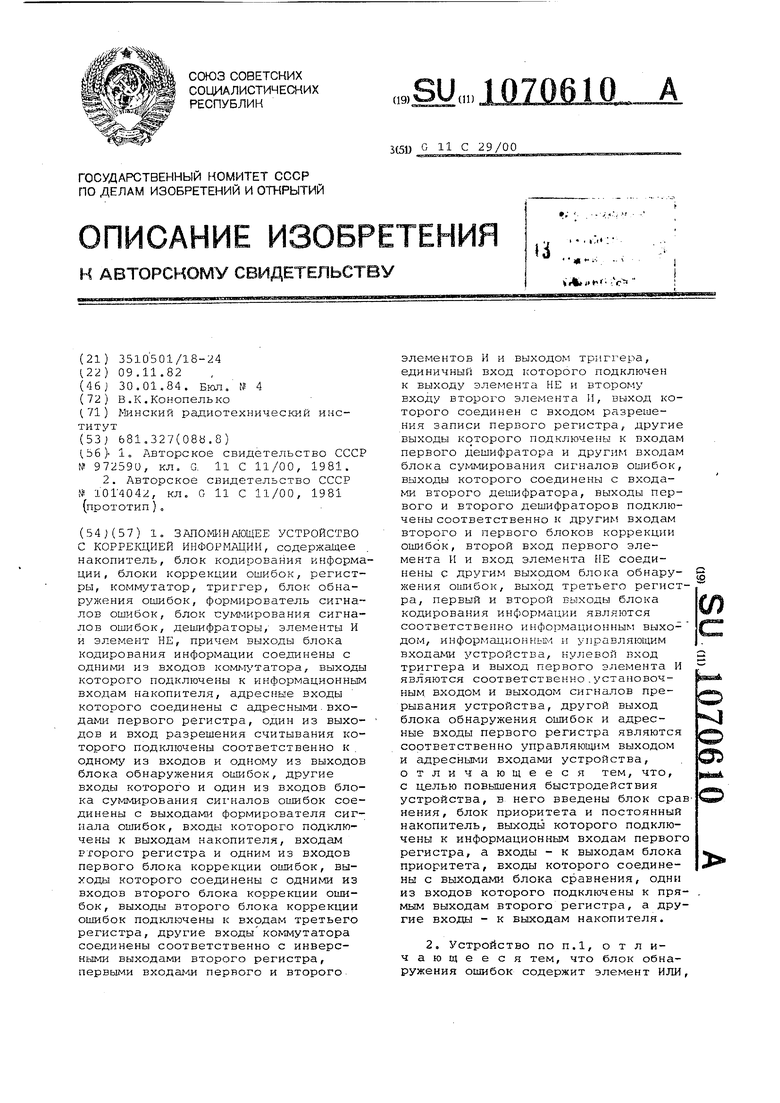

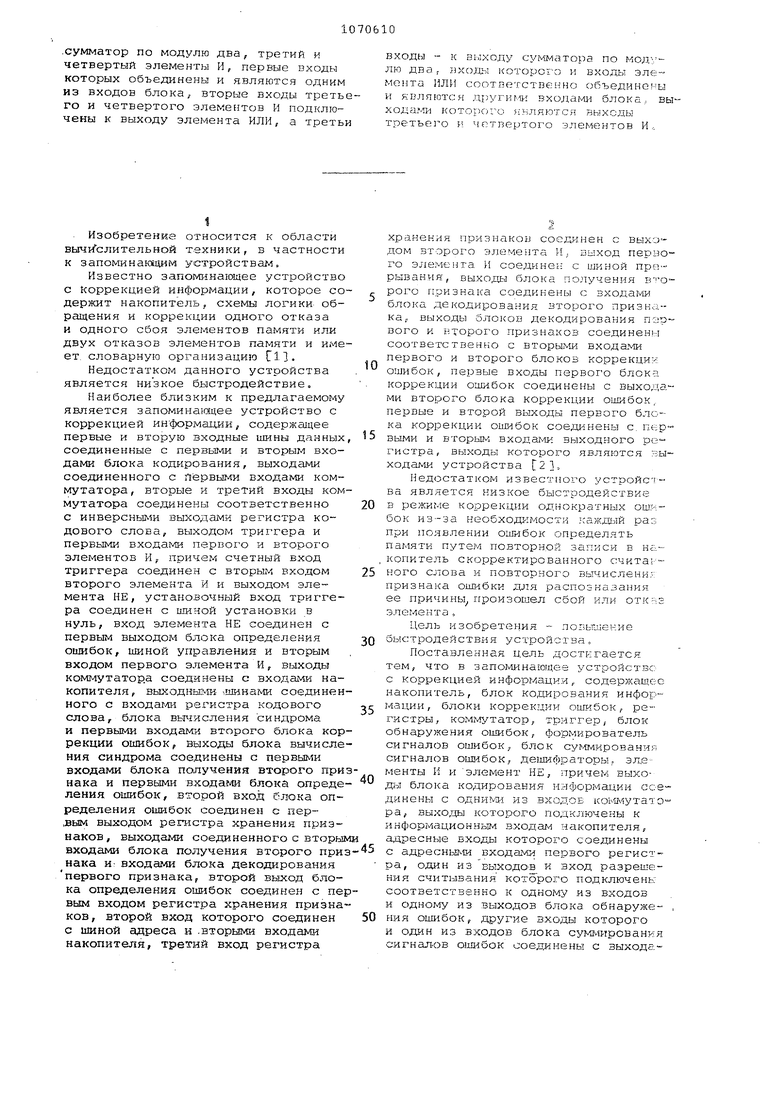

На фиг, 1 приведена функциональнгя схема предлагаемого устройства; на фиг. 2 и 3 - функциональные схемы блока обнаружения информаци и и блока приоритета соответственно.

Устройство содержит (фиг. 1) накопитель 1 с информационными 2 и адpecHb3vi 3 вxoд,, коммутатор 4, первый регистр 5 с информационньгми входами 6, предназначенный для хранения признаков ошибок, триггер 7 с выходом 8. блок 9 кодирования информации, второй регистр 10 с инверсны и выходами 11, предназначенный для хранения кодового слова, первый 12 и второй 13 элементы И, а также Элемент НЕ 14. На фиг. 1 обозначены установочный вход 15, управляю дий выход 16, информационные выходы 17 и вход 18, управляющий вход 19 и выход 20 сигналов прерывания устройства, вход 21 разрешения записи и вход 22 .разрешения считывания первого регистра. Кроме того,устройство содержит блок 23 сравнения с одними из входов 24, блок 25 суммирования сигналов ошибок с одними из входов 26 и блок 27 обнаружения ошибоко Позициями 28 и 29 обозначены соответственно одни и другие выхо,ды первого регистра. Устройство содержит также первый 30 и второй 31 дешифраторы, предназначенные для декодирования первого и второго признаков ошибок соответственно, формирователь 32 сигналов ошибок, постоянный накопитель 33 с входа.щ 34, блок 35 приоритета с входами 36, первый блок 37 коррекции ошибок с входадш 38 и 39, второй блок 40 коррекции ошибок с входами 41 и 42 и выходами 43 и 4 и треТлй регистр 45

Блок обнаружения ошибок содержит 1,фиг,- 2 ) третий 46 и четвертый 4 элементы И, элемент ИЛИ 48 и сумматор 49 по модулю два.

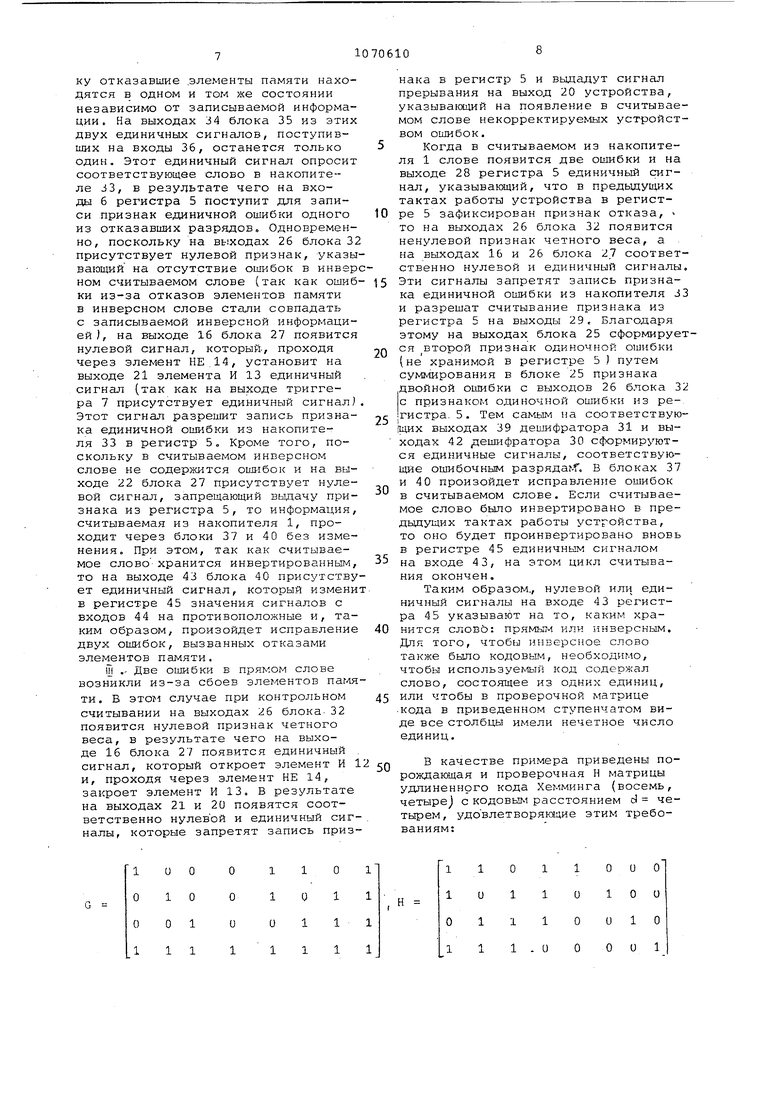

Блок приоритета содержит (соиг. 3 элементы И 50.

Предлагаемое устройство р-аботает следугадим образом.

Постоянный накопитель 33 хранит признаки единичных ошибок в любом из разрядов считываемого слова из накопителя 1.

В режиме записи информации устройство работает обычнЕлм образом. Данные, поступающие по входам 18 (фиг. 1), дополненные нулевым символом на входе 19, поступают на входы блока 9, который кодирует информацию кодом Хемминга с кодовым расстоянием d 4 и выдает на свои выходы кодовое слово, которое поме.щается через коммутатор 4 в накопитель 1 по адресу на входах. 3. При этом на выходе В триггера / присутствует нулевой сигнал. В счит|д|В аиия выходние ддан ные с вьлходов Нсэкопителя 1 подаются на блок 32 и одновременно на входы регистра 10,- блока 23 и блока 37, При налргчии оашбки ее признак вырабатывается на выходах 26 блока 32. При пер}5оначальном появлении однократной { - 1 ошибки вычисленный признак ие равен нулю и имеет нечетный вес,, о чем свидетельствует единичный сигнал на вьяходе сумматора 49 (фиг. 2К При этом регистр 5 вырабатывает нулевой сигнал нгг выходе 28, а блок 27 вырабатывает на выходах 16 и 22 нулевые сигналы которые запрешаюг выдачу нулевого признака из регистра 5 на выходн 29 и перезс.пис) инверсного слова с выходов 11 регистра 10 в накопитeл J 1, поскОЛьку триггер 7 остается в нулевом состоянии. Одновременно на выходе 21 элемента И 13 устанавливаете; нулевой сигнал, запре1л аю1дий запись из б, 33 признака ошибки в регистр 5, тем на выход блока 25 поступгзет без измене ния вычисле)иый блоком 32 признак ошибки, который дешифрируется блоком 31 и производит исправление в блоке 32 первой появившейся оимбки ИсправленН1-р1е инфОрмационные символы поступают через блок 40 без изменения нг1 входы регистра 4Ь При этом поскольку считываемое слово не инвертировалось ранее, то на выходе 43 блока 40 присутствует нул вой сигнал, который оставляет без изменения сигналЕл с входов 44 реги ра 40, Эти сигналы без изменения поступают на выходы 17 устройства. В случае, если в считываемом сл ве нет ошибки; т,ео вычисленный бл ком 32 признак ошибки равен Hyjuo, на выходгьк элементе ИЛИ 48 ((1м5г.2 и элементов 1 46 и 47 блока 27 устанавливаются нулевЕле сигналы, которые 3anpeitiaroT запись инверсного слова с выходов 11 регистра 10 (фиГо 1) через коммутатор 4 в нако питель 1 и считывание признака оши ки из реги-,стрл 5. Тем самым, как и D предыттущем случае, считываемое слово из накопителя 1 поступает че рез блоки 37 и 40 и регистр 45 ,на выходы 17 без измеЕсенин, т.е. пра вилвным. В случае, когдгг в .считываемом из накопителя 1 слове впервые появ ляются две ошибки на что указывае нулевой сигнал на выходе 28 регист ра 5 и .ненулевой признак ошибки на выходах 26 блока 32, то на выхо де 16 блока 27 появляется единичны сигнал. Этот сигнал поступает на в ход 16 и указывает на необхоядимост расширения цикла считывания« Одковременпо этот сиг-нал, проходя чере элемент 111:: 14,- устаЕ1авливает триг-гер 7 в единичное состояние- и тем CciMbiM разрешает запись инверсного cjEOBa с ВЕ-1ХОД.ОВ 11 регистра 10 в на со 1итель 1, Затем производится контрольное с-рггывание инверсно хдза1п--1мого слова и сравнение его в блоке 23 с прумым словом, хранимы : в регистре 10 При этом возможны три следующих случая, I Две О1ииб1-:и в прямом слове возникли из-за отказа и сбоя элеменTOI3 nai-.iHTn, В это:--; случае на одном из выходов 6jEOK-a 23, соответствующем отказав1; ему разряду, появится единичный сигнал, гюсЕГольку отказавший элемент памяти находится в одiiOM и том же состоянии незав Симо от записьпзаемой информации. Этот (.ХЦиничн.ый сип-игл опросит соответе.гв-ую,ее С.11СБО в --акопителте 33, в результа-.ге чего на входы 6 регистра 5 поступит для записи п.ризнак единичной -еьиибки отказавшего разряда. Одновременно, п-осколь уу на ьы ходах 26 блока 32 присутствует Hei-ryдевой признак еди1 ичной ошио; и в и - версном считываемом слове (ошибка из-за сбоя элемег-;та .-1Яти ., на выходе 16 (злока 27 появится нулевой -сигнггл, который, проходя через элемент HI; 14, установит на выходе 21 элемент И 13 единичный сигна.п (так на Еыхо.те тригтера 7 присутстг ует едипичн лй си1нал|. Этот сигнал разрешит запись призЕ ака единичной ошибки отказав1иего разряда из накопит-еля 33 а регисгр 5„ Кроме того, поскольку в считываемом игзверсном слове содержится одна огибка из-за сбоя элемента на -сопителя 1, то на выходе 22 блока 27 сформиру-ется нулевой сигнал, который запрс;-Tiii выдачу прпзнака единичной ошиСки из регистра 5 Поэтому ЕШ выходы блока 25 поступит без изменсрниу. признак один-очной ОЕяибки, сформирован ый блоком J2, который, дежифрируясь дешифратором 31, исправит ошибку в блоке 37, Исп завлен1Гп е и 1фОрмационные символы, поступят через блок 40 без изменения на входы periiCTpa 45, При этом поскольку считываемое слово хранится p вepтированным.на присутствующий выход 43 блока 40 единичный сигнал изменит в регис-тре 45 змачения сигналов о входов 44 па противоположные значения. Таким образом, произойдет исправление двух ошибоЕс 3 хранимой информгщии, вызнанных сбоем и отказом элементов пагу-1яти накопителя 1. У. Две ошибки в прямом слове возникли из-за отказов элементов памя-ти В этом случае при -;онтрольном считывании на двух выходах блока 23,соответст}зующих отказавшим разрядам, появятся единичные сигналы, поскольку отказавише .элементы памяти нахо дятся в одном и том же состоянии независимо от записываемой информа ции. На выходах 34 блока 35 из этих двух единичных сигналов, поступивших на входы 36, останется только один. Этот единичный сигнал опросит соответствующее слово в накопителе ЗЗ, в результате чего на входы 6 регистра 5 поступит для записи признак единичной ошибки одного из отказавших разрядов. Одновременно, поскольку на вь ходах 26 блока 3 присутствует нулевой признак, указы вающий на отсутствие ошибок в инвер ном считываемом слове (так как оыиб ки из-за отказов элементов памяти в инверсном слове стгизи совпадать с записываемой инверсной информацией, на выходе 16 блока 27 появится нулевой сигнал, который-, проходя через элемент НЕ. 14, установит на выходе 21 элемента И 13 единичный сигнал (так как на выходе триггера 7 присутствует единичный сигнал Этот сигнал разрешит запись признака единичной ошибки из накопителя 33 в регистр 5 о Кроме того, поскольку в считываемом инверсном слове не содержится ошибок и на выходе 22 блока 27 присутствует нул.евой сигнал, запрещающий выдачу признака из регистра 5, то информация считываемая из накопителя 1, проходит через блоки 37 и 40 без изменения. При этом, так как считываемое слово хранится инвертированным то на выходе 43 блока 40 присутству ет единичный сигнал, который измени в регистре 45 значения сигналов с входов 44 на противоположные и, таким образом, произойдет исправление двух ошибок, вызванных отказами элементов памяти. Ш .- Две ошибки в прямом слове возникли из-за сбоев элементов паг/ш ти. В этом случае при контрольном считывании на выходах 26 блока-32 появится нулевой признак четного веса, в результате чего на выходе 16 блока 27 появится единичный сигнал, который откроет элемент И и, проходя через элемент НЕ 14, закроет элемент И 13. В результате на выходах 21 и 20 появятся соответственно нулевой и единичный сиг налы, которые запретят запись приз

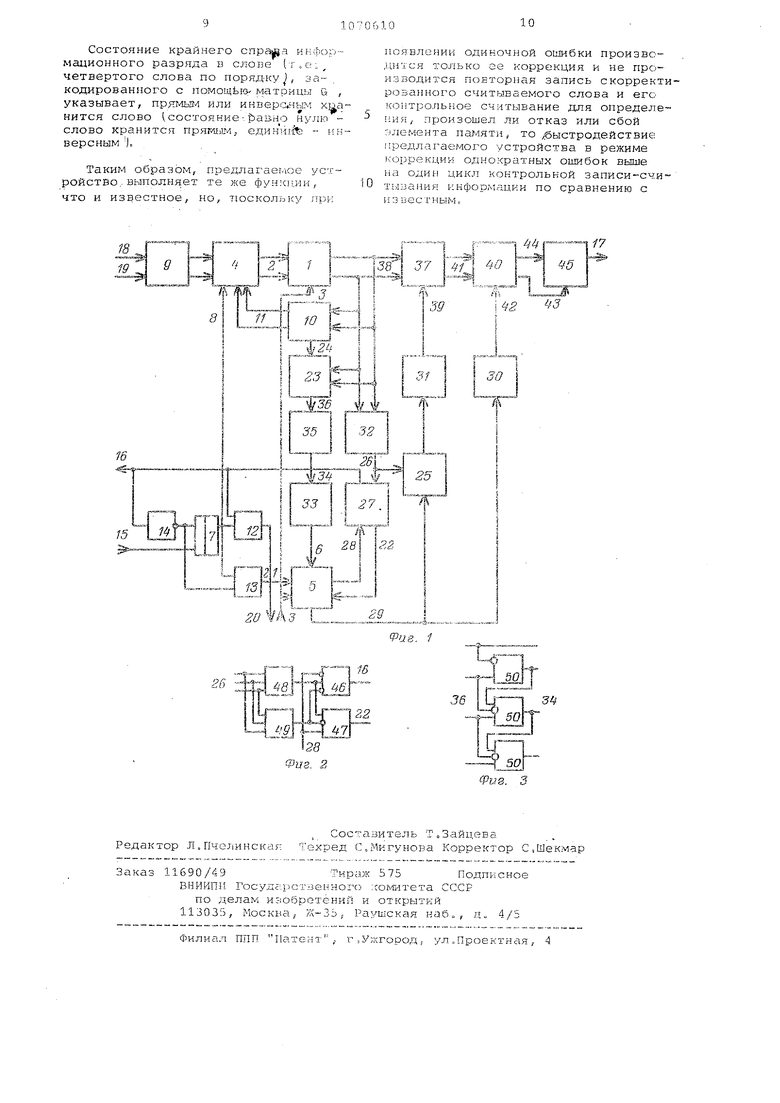

Н нака в регистр 5 и выдадут сигнал прерывания на выход 20 устройства, указываквдий на появление в считываемом слове нeкoppeктиpye ыx устройством ошибок. Когда в считываемом из накопителя 1 слове появится две ошибки и на выходе 28 регистра 5 единичный сигнал, указывающий, что в предыдущих тактах работы устройства в регистре 5 зафиксирован признак отказа, то на выходах 26 блока 32 появится ненулевой признак четного веса, а на выходах 16 и 26 блока 27 соответственно нулевой и единичный сигналы. Эти сигналы запретят запись признака единичной ошибки из накопителя 33 и разрешат считывание признака из регистра 5 на выходы 29. Благодаря этому на выходах блока 25 сформируется второй признак одиночной ошибки (не хранимой в регистре 5 ) путем суммирования в блоке 25 признака двойной ошибки с выходов 26 блока 32 с признаком одиночной ошибки из регистра. 5. Тем самыдМ на соответствую щих выходах 39 дешифратора 31 и выходах 42 дешифратора 30 сформируются единичные сигналы, соответствующие ошибочным разряда -Г. В блоках 37 и 40 произойдет исправление ошибок в считываемом слове. Если считываемое слово было инвертировано в предыдущих тактах работы устройства, то оно будет проинвертировано вновь в регистре 45 единичным сигналом на входе 43, на этом цикл считывания окончен. Таким образом., нулевой или единичный сигналы на входе 43 регистра 45 указывают на то, каким хранится словЬ: прямы1 или гкчверсным. Для. того, чтобы и.мверсное слово также было кодовым, необходимо, чтобы используемый код содержал слово, состоящее из одних единиц, или чтобы в проверочной матрице кода в приведенном ступенчатом виде все столбцы имели нечетное число единиц. В качестве примера приведены порождаквдая и проверочная И матрицы удлиненного кода Хемминга (восемь, четыре) с кодовым расстоянием d четырем, удовлетворякщие этим требованиям:

Состояние крайнего информационного разряда в слове (г,е;:, четвертого слова по порядку, закодированного с 1омощЬиз- матрицы 6 , указывает, прямьи- или .ным хианится слово (, состояние . jbaBHo нулю слово кранится пряма1.м, едини1-№ - инверсным ).

Таким образом, предлагаег/юе устройство., выполняет те же фун.чп.ии,

что и известное, но, тюскольку при

появлении одиночной ошибки произво.цится только ее коррекция и не производится повторная запись скорректированного считываемого слова и его контрольное считывание для определе ;ия,- произошел ли отказ или сбой элемента памяти, то быстродействие предлагаемого устройства в режиме коррекции однократных ошибок выше на один цикл контрольной записи-счятьпзания информации по сравнению с известным.

I W f

I -,

1 -iJ p. I j3f I

s 1

f i..i.n-eMr J i SLixr---,., i J

I ±щ jL,t

И ,7/7

g, /

1 r

HrrCr

J6 -3«

/ -rth - pLM

soj ifys. 3

Авторы

Даты

1984-01-30—Публикация

1982-11-09—Подача