Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти с повышенной надежностью и ограниченным энергопотреблением.

Гель изобретения - уменьшение потребляемой мощности.

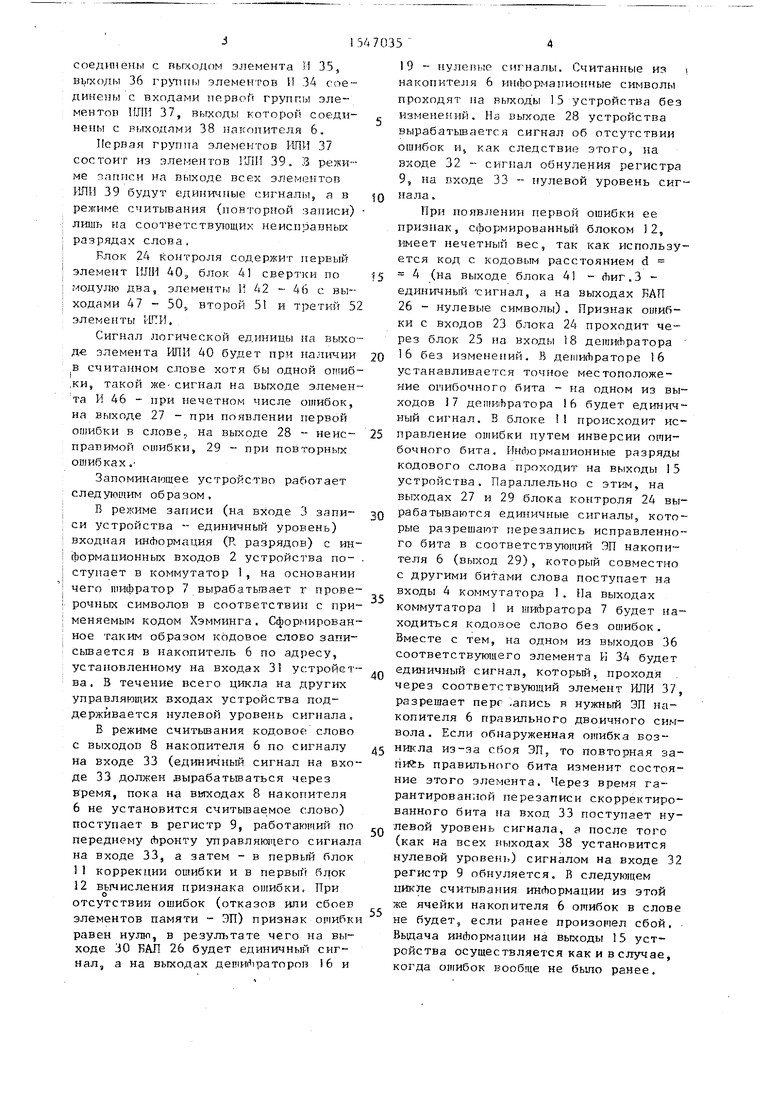

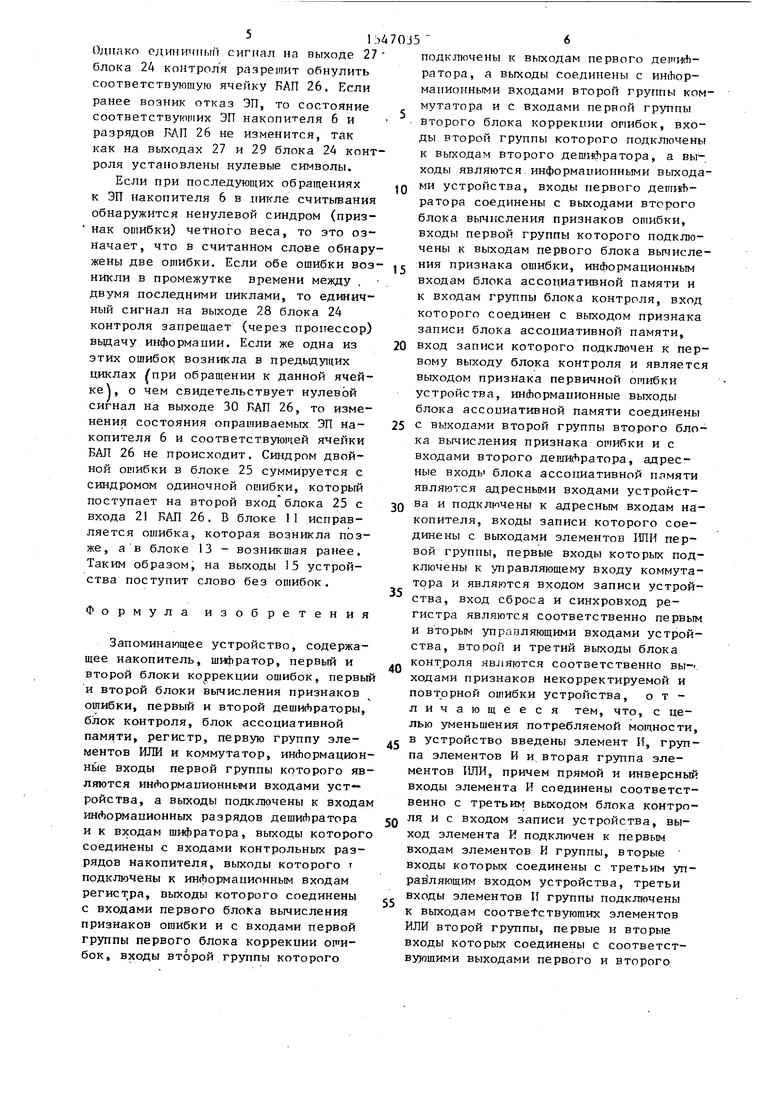

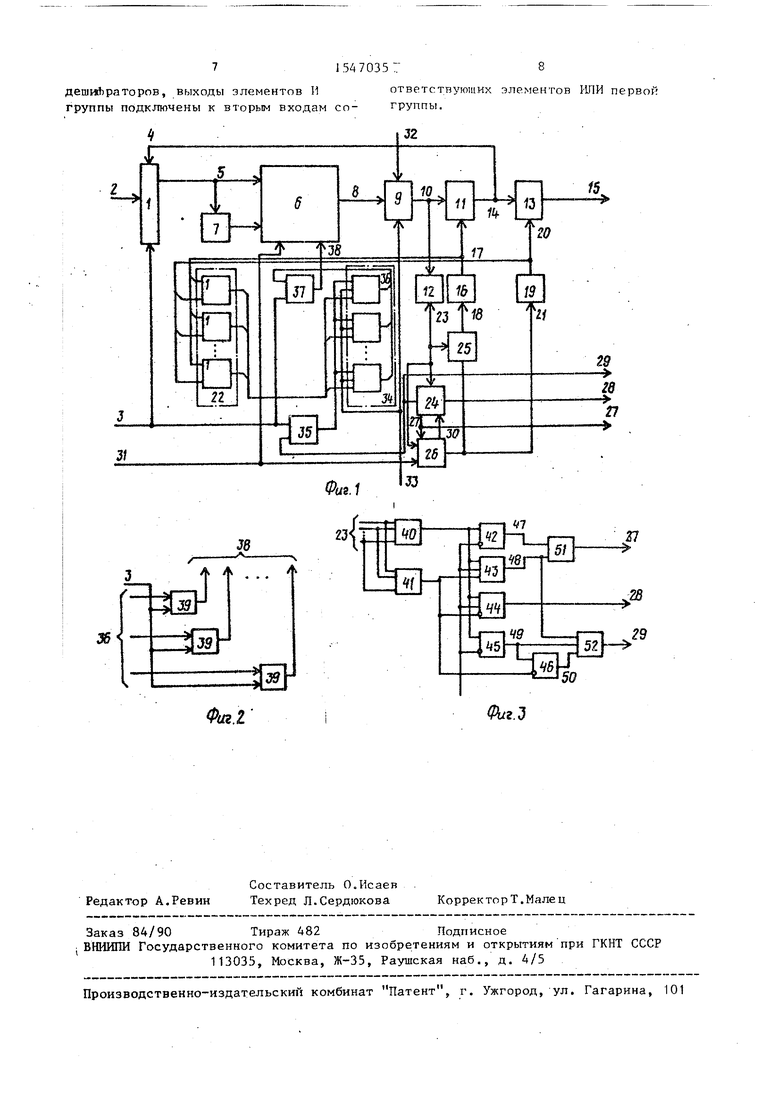

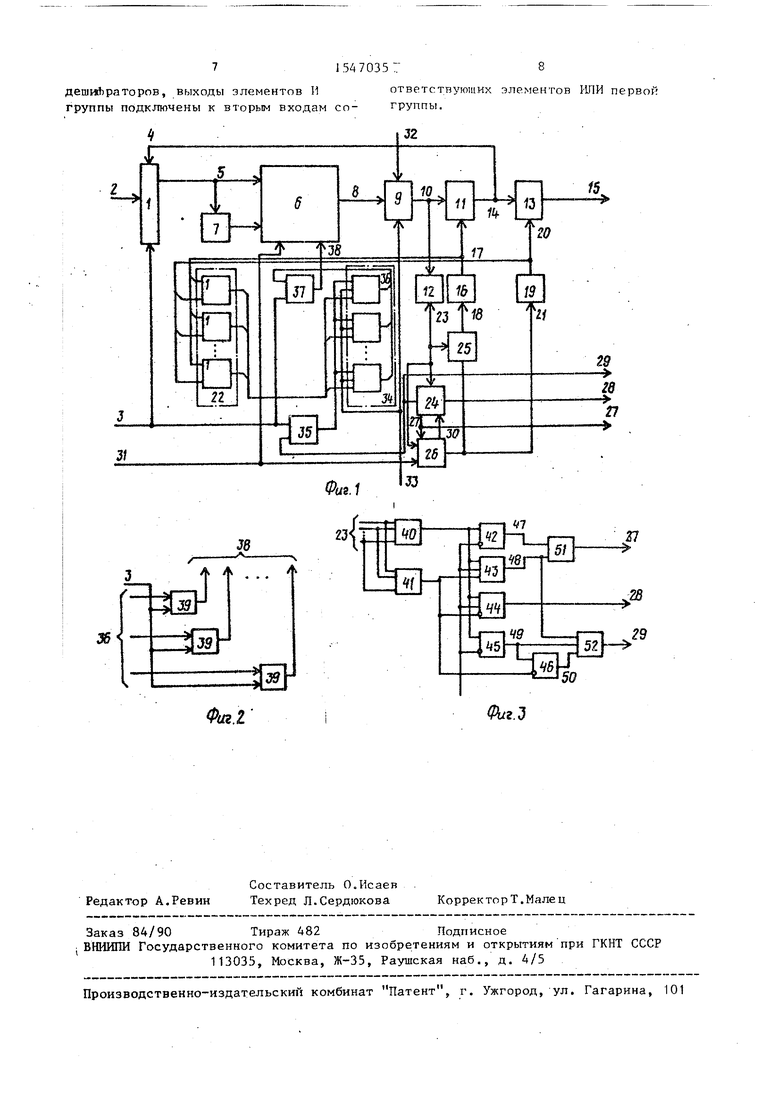

На Фиг.1 изображена схема запоминающего устройства; на Лиг.2 - схема включения элементов ИЛИ первой группы; на Фиг.З - пример реализации блока контроля.

Запоминающее устройство содержит коммутатор 1, информационные входы 2 устройства, вход 3 записи устройства, входы 4 коммутатора 1, выходы 5 коммутатора 1, накопитель 6, шифратор 7, выходы 8 накопителя 6, регистр 9, выходами 10 соединенный с входами первого блока 11 коррекции ошибок и с входами первого блока 12 вычисления признака ошибки, второй блок 13 коррекции ошибок с входами 14, информационные выходы 15 устройства, первый дешифратор 16 с выходами 17 и входами 18,второй дешифратор 19 с выходами 20 и входами 21, элементы ИЛИ 22, входы 23 блока 24 контроля, второй блок

25вычисления признака ошибки, блок

26ассоциативной памяти (РАН), первый 27, второй 28 и третий 29 выходы блока 24 контроля, первый выход 30 признака записи БАЛ 26,адресные входы 31 устройства, первый 32 и второй 33 управляющие входы устройства, группу элементов И 34, первые входы которых.

СП

HU

4

§Ј

соединены с выходом элемента И 35, выходы 36 группы элементов И 34 соединены с входами первой группы элементов ИЛИ 37, выходы которой соединены с выходами 38 накопителя 6,

Первая группа элементов ИЛИ 37 состоит из элементов 1ПИ 39. 3 резки-- ме записи на выходе всех элементов ИЛИ 39 будут единичные сигналы, а в режиме считывания (повторной записи) лишь на соответствующих неисправных разрядах слова,

Клок 24 контроля содержит первый элемент ИЛИ 40 блок 41 свертки по модулю два, элементы И 42 - 46 с выходами 47 - 50„ второй 51 и третий 52 элементы ИЛИ.

Сигнал логической единицы на выходе элемента ИЛИ 40 будет при наличии в считанном спове хотя бы одной ошибки, такой же сигнал на выходе элемен - та И 46 - при нечетном числе ошибок, на выходе 27 - при появлении первой ошибки в слове,, на выходе 28 - неисправимой ошибки, 29 - при повторных ошибках.

Запоминающее устройство работает следующим образом,

В режиме записи (на входе 3 записи устройства -- единичный уровень) входная информация (R разрядов) с ин сЬормаиионных входов 2 устройства поступает в коммутатор 1, на основании чего шифратор 7 вырабатывает г проверочных символов в соответствии с применяемым кодом Хэмминга. Сформированное таким образом кодовое слово записывается в накопитель 6 по адресу, установленному на входах 31 устройства. В течение всего цикла на других управляющих входах устройства поддерживается нулевой уровень сигнала, В режиме считывания кодовое слово с выходов 8 накопителя 6 по сигналу на входе 33 (единичный сигнал на входе 33 должен вырабатываться через время, пока на выходах 8 накопителя 6 не установится считываемое слово) поступает в регистр 9, работающий по переднему Фронту управляющего сигнала на входе 33, а затем - в первый блок

11коррекции ошибки и в первый блок

12вычисления признака ошибки. При отсутствии ошибок (отказов или сбоев элементов памяти - ЭП) признак ошибки равен нулю, в результате чего на выходе 30 БАЛ 26 будет единичный сигнал, а на выходах дешифраторов 16 и

5

0

5

0

5

0

5

0

5

19 - нулевые сигнапы. Считанные из i накопителя 6 информационные символы проходят на выходы 15 устройства без изменений. На выходе 28 устройства вырабатывается сигнал об отсутствии ошибок и, как следствие этого, на входе 32 - сигнал обнуления регистра 9, на входе 33 - нулевой уровень сигнала.

При появлении первой ошибки ее признак, сформированный блоком 12, имеет нечетный вес, так как используется код с кодовым расстоянием d 4 (на выходе блока 41 - Фиг.З - единичный сигнал, а на выходах БАП 26 - нулевые символы). Признак ошибки с входов 23 блока 24 проходит через блок 25 на входы 18 дешифратора 16 без изменений. В дешифраторе 16 устанавливается точное местоположение ошибочного бита - на одном из выходов J7 дешифратора 16 будет единичный сигнал. В блоке 11 происходит исправление ошибки путем инверсии ошибочного бита. Информационные разряды кодового слова проходит на выходы 15 устройства. Параллельно с этим, на выходах 27 и 29 блока контроля 24 вырабатываются единичные сигналы, которые разрешают перезапись исправленного бита в соответствующий ЭП накопителя 6 (выход 29), который совместно с другими битами слова поступает на входы 4 коммутатора 1. На выходах коммутатора 1 и шифратора 7 будет находиться кодовое слово без ошибок. Вместе с тем, на одном из выходов 36 соответствующего элемента К 34 будет единичный сигнал, который, проходя через соответствующий элемент ИЛИ 37, разрешает перс .апись в нужный ЭП накопителя 6 правильного двоичного символа. Если обнаруженная ошибка возникла из-за сбоя ЭП, то повторная запить правильного бита изменит состояние этого элемента. Через время гарантированной перезаписи скорректированного бита на вход 33 поступает нулевой уровень сигнала, а после того (как на всех выходах 38 установится нулевой уровень) сигналом на входе 32 регистр 9 обнуляется, В следующем цикле считывания информации из этой же ячейки накопителя 6 ошибок в слове не будет, если ранее произошел сбой. Выдача информации на выходы 15 устройства осуществляется как и в случае, когда ошибок вообще не было ранее.

ке

сигнал на выходе 30 БАП 26, то изменения состояния опрашиваемых ЭП накопителя 6 и соответствующей ячейки БАЛ 26 не происходит. Синдром двойной ошибки в блоке 25 суммируется с синдромом одиночной ошибки, который поступает на второй вход блока 25 с входа 21 БАП 26. В блоке 11 исправляется ошибка, которая возникла позже, а в блоке 13 - возникшая ранее. Таким образом, на выходы 15 устройства поступит слово без ошибок.

Формула изобретения

Запоминающее устройство, содержащее накопитель, шифратор, первый и второй блоки коррекции ошибок, первый и второй блоки вычисления признаков ошибки, первый и второй дешиАраторы, блок контроля, блок ассоциативной памяти, регистр, первую группу элементов ИЛИ и коммутатор, информационные входы первой группы которого являются информационными входами устройства, а выходы подключены к входам информационных разрядов дешифратора и к входам шифратора, выходы которого соединены с входами контрольных разрядов накопителя, выходы которого т подключены к информационным входам регистра, выходы которого соединены с входами первого блока вычисления признаков ошибки и с входами первой группы первого блока коррекции ошибок, входы второй группы которого

10

Однако единичный сигнал на выходе 27 блока 24 контроля разрешит обнулить соответствующую ячейку НАП 26. Если

ранее возник отказ ЭП, то состояние соответствующих ЭП накопителя 6 и разрядов ЛАП 26 не изменится, так как на выходах 27 и 29 блока 24 контроля установлены нулевые символы.

Если при последующих обращениях к ЭП накопителя 6 в пикле считывания обнаружится ненулевой синдром (приз- нак ошибки) четного веса, то это означает, что в считанном слове обнаружены две ошибки. Если обе ошибки воз- никли в промежутке времени между , двумя последними циклами, то единичный сигнал на выходе 28 блока 24 контроля запрещает (через процессор) выдачу информации. Если же одна из этих ошибок возникла в предыдущих циклах /при обращении к данной ячей- ;, о чем свидетельствует нулевой

20

30

25

с

35

40

50

55

подключены к выходам первого дешифратора, я выходы соединены с инФор0

0

0

мациопными входами второй группы коммутатора и с входами первой группы второго блока коррекции ошибок, входы второй группы которого подключены к выходам второго дешифратора, а выходы являются информационными выходами устройства, входы первого дешифратора соединены с выходами второго блока вычисления признаков ошибки, входы первой группы которого подключены к выходам первого блока вычисления признака ошибки, информационным входам блока ассоциативной памяти и к входам группы блока контроля, вход которого соединен с выходом признака записи блока ассоциативной памяти, вход записи которого подключен к первому выходу блока контроля и является выходом признака первичной ошибки устройства, информационные выходы блока ассоциативной памяти соединены

5 с выходами второй группы второго блока вычисления признака ошибки и с входами второго дешифратора, адресные входы блока ассоциативной памяти являются адресными входами устройства и подключены к адресным входам накопителя, входы записи которого соединены с выходами элементов ИЛИ первой группы, первые входы которых подключены к управляющему входу коммутатора и являются входом записи устройства, вход сброса и синхровход регистра являются соответственно первым и вторым управляющими входами устройства, второй и третий выходы блока контроля являются соответственно вы-- ходами признаков некорректируемой и повторной ошибки устройства, отличающееся тем, что, с целью уменьшения потребляемой мощности,

с в устройство введены элемент И, группа элементов И и вторая группа элементов ИЛИ, причем прямой и инверсный входы элемента И соединены соответственно с третьим выходом блока контроля и с входом записи устройства, выход элемента И подключен к первым входам элементов И группы, вторые входы которых соединены с третьим управляющим входом устройства, третьи входы элементов И группы подключены к выходам соответствующих элементов ИЛИ второй группы, первые и вторые входы которых соединены с соответствующими выходами первого и второго

5

0

0

дешифраторов, выходы элементов Иответствуюших элементов 1ШИ первой

группы подключены к вторым входам со- группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU1010659A2 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

| Запоминающее устройство с автономным контролем | 1981 |

|

SU970479A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти с повышенной надежностью и ограниченным энергопотреблением. целью изобретения является уменьшение потребляемой мощности. Устройство содержит накопитель, шифратор, первый и второй блоки коррекции ошибок, первый и второй блоки вычисления признака ошибки, первый и второй дешифраторы, блок контроля, блок ассоциативной памяти, регистр, первую и вторую группы элементов ИЛИ, коммутатор, группу элементов И и элемент И. В устройстве при обнаружении кодом Хэмминга первичной корректируемой ошибки производится занесение синдрома ошибки в блок ассоциативной памяти и перезапись исправленной информации в накопитель. Цель изобретения достигается тем, что сигнал перезаписи подается только на вход неисправного разряда накопителя. 3 ил.

38

И

Фиг2

Фаг.Ъ

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Солесос | 1922 |

|

SU29A1 |

| Авторское свидетельство СССР N 1195393, кл | |||

| Солесос | 1922 |

|

SU29A1 |

Авторы

Даты

1990-02-28—Публикация

1988-06-13—Подача