4;

00 со

эо

Из ретение относится к вычисли- тельной технике и может быть использовано для построения эапоминаюп1их устройств с коррекцией ошибок.

Целью изобретения является повышение надежности устройства.

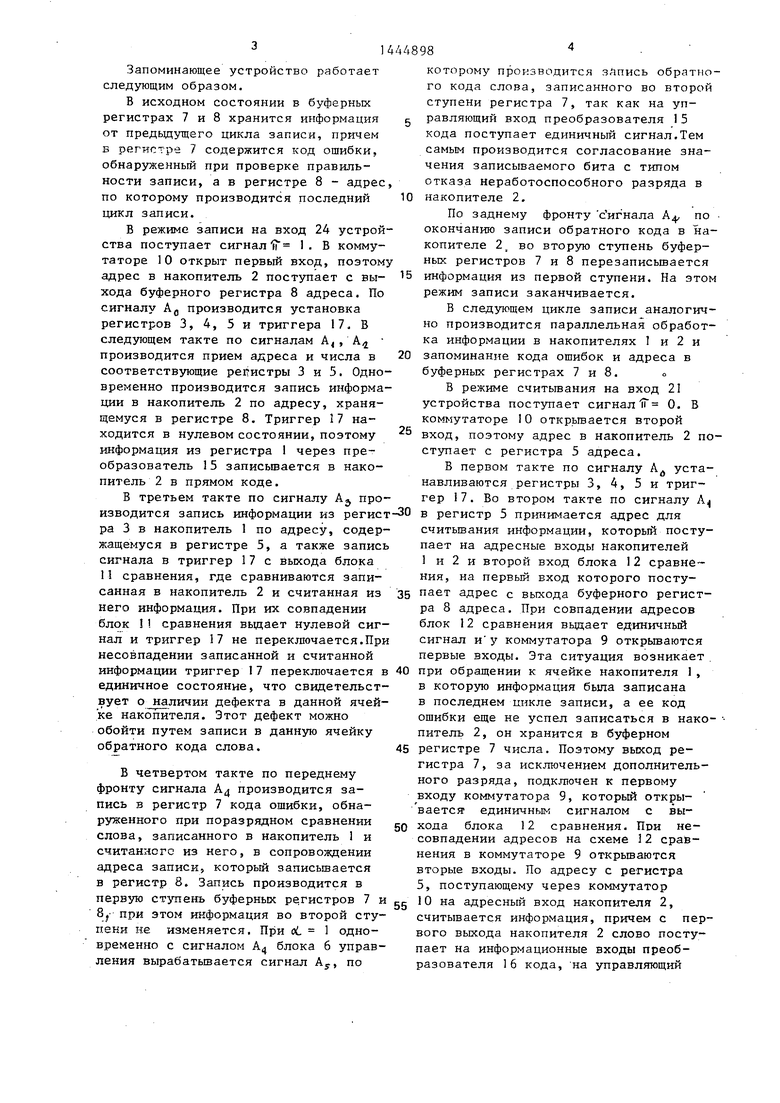

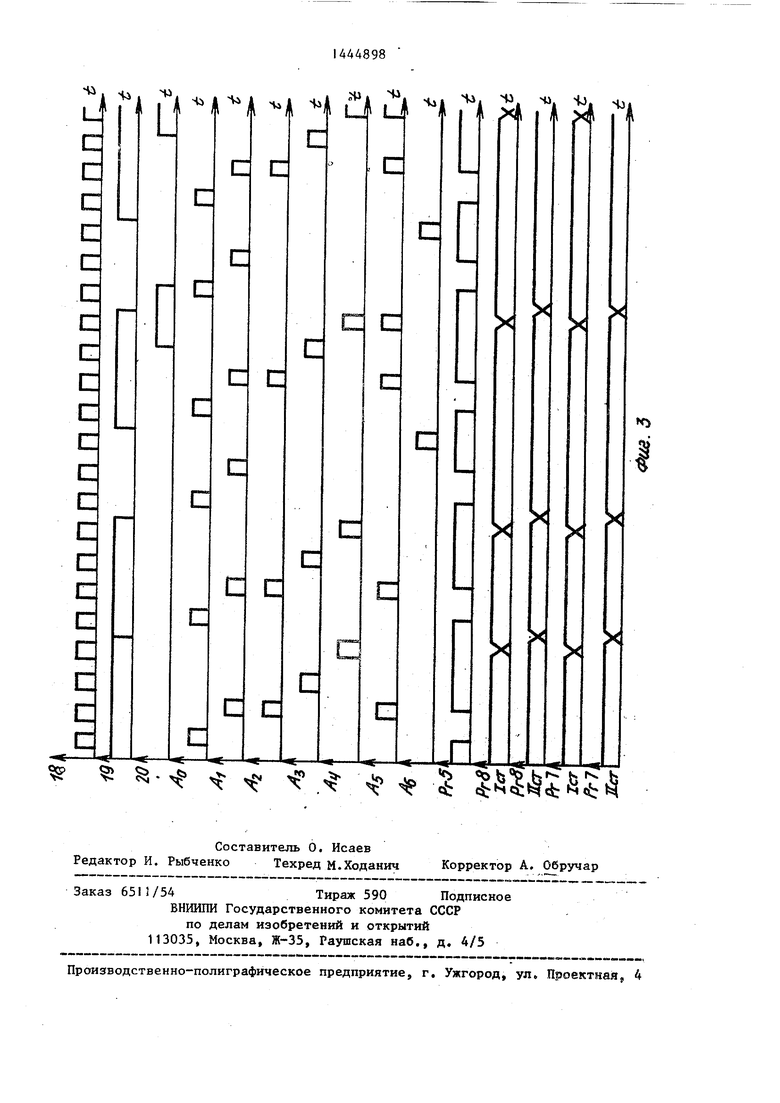

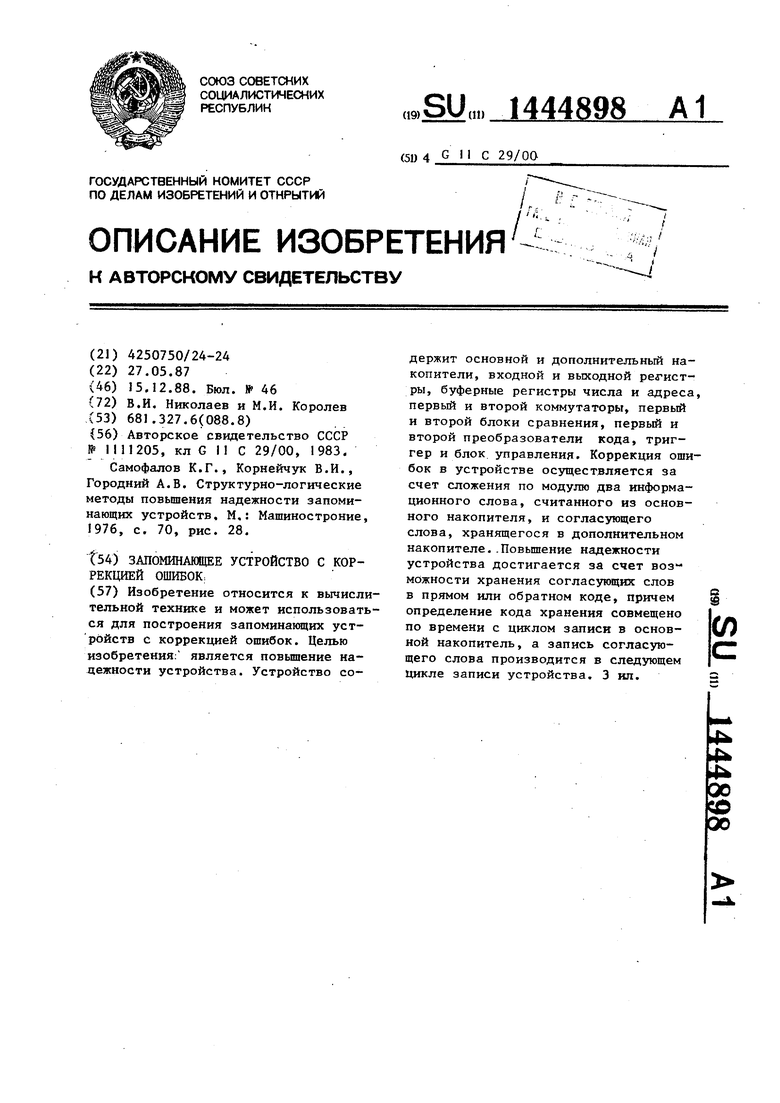

На фиг. 1 представлена схема запоминающего устройства с коррекцией ошибок; на фиг. 2 - схема блока уп- равления; на фиг. 3 - временная диаграмма работы устройства.

Устройсто (фиг. 1) содержит основной 1 и дополнительный 2 накопители, входной 3 и выходной 4 регист- ры, регистр 5 адреса, блок 6 управления, буферный регистр 7 числа, буферный регистр 8 адреса, первый 9 и второй 10 коммутаторы, первый 11 и второй 12 блоки сравнения, первую 13 и вторую 14 группы сумматоров по модулю два, первый 15 и второй 16 преобразователи кода, триггер 17.Бло 6 управления имеет вход 18 синхронизации, вход признака 19 записи-чте- ния и вход 20 признака перехода, уп- правляющие выходы Ад-А.Устройство имеет информационные 21 и адресные 22 входы, вход 23 синхронизации и вход 24 признака записи-чтения ин- формационные выходы 25.

Блок 6 управления (фиг. 2) содержит счетчик 26, дешифратор 27, первую группу элементов И 28, группу элементов ИЛИ 29, элемент НЕ 30, эле мент 31 задержки, вторую группу элементов И 32.

Основной накопитель 1 предназначен для хранения информации. В дополнительном накопителе 2 хранятся прямые и обратные коды ошибок одноименных ячеек основного накопителя 1 Для определения вида хранимого кода введен дополнительный разряд: 1 соответствует обратному коду, О - прямому коду.. Информационное слово считывается с первого выхода накопителя 2, дополнительный разряд --с второго выхода.

Буферные регистры 7 числа и 8 адреса выполнены на базе двухступенчатых D-триггеров. По переднему фронт Сигнала А4. информация записывается в первую ступень триггеров, по заднему фронту - во вторую ступень. Разрядность регистра 7 равна разрядности слова дополнительного накопителя 2. В Дополнительный разряд регистра 7 всегда записывается О, что свидетельствует о хранении прямого кода числа.

Коммутатор 9 при наличии на его управляющем входе высокого уровня разрешает прохождение информации с первого входа иначе - с второго входа Коммутатора 10 работает аналогично.

1 2 сравнения сравнивает слова, поступающие на первый и второй входы, и при их совпадении льщает единичный сигнал. Блок 11 сравнения работает аналогично, только сигнал вьда- ется с инверсного выхода.

Преобразователь 15 кода при наличии высокого уровня на его управляющем входе вьщеляет обратньй код числа, поступившего на информационные входы, иначе - прямой код. Преобразователь 16 вьвполнен аналогично.

Элемент 17 выполнен на базе D-триг гера. Он вьщает сигнал оЬ.

Блок 6 управления вырабатьшает сигналы Ag-Ag. На первый вход 18 блока 6 с первого управляющего входа 23 устройства поступают тактовые сигналы, которые задают частоту выработки управляющих сигналов. На второй вход 19 блока 6 с входа 24 поступает сигнал режима работы устройства . При 1Г О производится считьшание информации, а при IT 1 - запись информации. На третий вход блока 6 поступает сигналов с выхода триггера 17. I

Дешифратор 27 блока 6 управления , вырабатьшает сигналы В зави- симости от режима работы, состояния дешифратора 27 и значения сигнала ei на входе 20 блок 6 вырабатьшает сигналы Ag-Ag по следующим правилам:

АО Уо . А, У, ,

А, Г.у,

, Аф у, , А, 1Г- у, ,

АИ Т -Уг- В зависимости от режима работы и

состояния дешифратора 27 счетчик 26 управляется следующ1-1М сигналом:

R 1Г- Yi V у, .

Последовательность выработки управляющих сигналов Ajj-A в зависимости от режима работы (ir) к от сигнала на входе 20 (ot) представлена на фиг. 3.

Запоминающее устройство работает следующим образом.

В исходном состоянии в буферных регистрах 7 и 8 хранится информация от предьщущего цикла записи, причем в регистре 7 содержится код ошибки, обнаруженный при проверке правильности записи, а в регистре 8 - адрес, по которому производится последний цикл записи.

В режиме записи на вход 24 устройства поступает сигнал (Г 1. В коммутаторе 10 открыт первый вход, поэтому адрес в накопитель 2 поступает с выхода буферного регистра 8 адреса. По сигналу Ад производится установка регистров 3, 4, 5 и триггера 17. В следующем такте по сигналам А, А производится прием адреса и числа в соответствующие регистры 3 и 5. Одновременно производится запись информации в накопитель 2 по адресу, хранящемуся в регистре 8. Триггер 17 находится в нулевом состоянии, поэтому информация из регистра 1 через преобразователь 15 записьшается в накопитель 2 в прямом коде.

В третьем такте по сигналу А прокоторому производится зЛпись обра го кода слова, записанного во вто ступени регистра 7, так как на уп с равляющий вход преобразователя 15 кода поступает единичный сигнал.Т самым производится согласование зн чения записываемого бита с типом отказа неработоспособного разряда 10 накопителе 2.

По заднему фронту с иг нала k окончанию записи обратного кода в копителе 2 во вторую ступень буфе ных регистров 7 и 8 перезаписьшает 15 информация из первой ступени. На э режим записи заканчивается.

В следующем цикле записи аналог но производится параллельная обраб ка информации в накопителях 1 и 2 20 запоминание кода ошибок и адреса в буферных регистрах 7 и 8. о

В режиме считьшания на вход 21 устройства поступает сигнал 1Г 0. коммутаторе 10 открьшается второй вход, поэтому адрес в накопитель 2 ступает с регистра 5 адреса.

В первом такте по сигналу А ус навливаются регистры 3, 4, 5 и три гер 17. Во втором такте по сигналу

изводится запись информации из регист-30 в регистр 5 принимается адрес для

которому производится зЛпись обратного кода слова, записанного во второй ступени регистра 7, так как на уп- равляющий вход преобразователя 15 кода поступает единичный сигнал.Тем самым производится согласование значения записываемого бита с типом отказа неработоспособного разряда в накопителе 2.

По заднему фронту с иг нала k по окончанию записи обратного кода в накопителе 2 во вторую ступень буферных регистров 7 и 8 перезаписьшается информация из первой ступени. На этом режим записи заканчивается.

В следующем цикле записи аналогично производится параллельная обработка информации в накопителях 1 и 2 и запоминание кода ошибок и адреса в буферных регистрах 7 и 8. о

В режиме считьшания на вход 21 устройства поступает сигнал 1Г 0. В коммутаторе 10 открьшается второй вход, поэтому адрес в накопитель 2 поступает с регистра 5 адреса.

В первом такте по сигналу А устанавливаются регистры 3, 4, 5 и триггер 17. Во втором такте по сигналу А

в регистр 5 принимается адрес для

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для коррекции ошибок | 1986 |

|

SU1372364A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372366A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1265860A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к вычислительной технике и может использоваться для построения запоминающих устройств с коррекцией ошибок. Целью изобретения: является повьшение надежности устройства. Устройство содержит основной и дополнительный накопители, входной и выходной регистры, буферные регистры числа и адреса, первый и второй коммутаторы, первый н второй блоки сравнения, первый и второй преобразователи кода, триггер и блок управления. Коррекция ошибок в устройстве осуществляется за счет сложения по модулю два информационного слова, считанного из основного накопителя, и согласующего слова, хранящегося в дополнительном накопителе..Повышение надежности устройства достигается за счет возможности хранения согласующих слов в прямом или обратном коде, причем определение кода хранения совмещено по времени с циклом записи в основной накопитель, а запись согласующего слова производится в следующем цикле записи устройства. 3 ил. (Л

ра 3 в накопитель 1 по адресу, содержащемуся в регистре 5, а также запись сигнала в триггер 17 с выхода блока 11 сравнения, где сравниваются записанная в накопитель 2 и считанная из него информация. При их совпадении блок сравнения вьщает нулевой сигнал и триггер 17 не переключается.При несовпадении записанной и считанной информации триггер 17 перекл очается в единичное состояние, что свидетельствует о наличии дефекта в данной ячейке накопителя. Этот дефект можно обойти путем записи в данную ячейку обратного кода слова.

В четвертом такте по переднему фронту сигнала А4 производится запись в регистр 7 кода ошибки, обнаруженного при поразрядном сравнении слова, записанного в накопитель 1 и считанного из него, в сопровождении адреса записи, который записьшается в регистр 8. Запись производится в первую ступень буферных регистров 7 и 8j при этом информация во второй ступени не изменяется. При oL 1 одновременно с сигналом А блока 6 управления вырабатьтается сигнал Ау, по

5 0 5

0

5

считьшания информации, который поступает на адресные входы накопителей 1 и 2 и второй вход блока 12 сравнения, на первый вход которого поступает адрес с выхода буферного регистра 8 адреса. При совпадении адресов блок 12 сравнения выдает единичный сигнал и у коммутатора 9 открываются первые входы. Эта ситуация возникает . при обращении к ячейке накопителя 1, в которую информация была записана в последнем цикле записи, а ее код ошибки еще не успел записаться в накопитель 2, он хранится в буферном регистре 7 числа. Поэтому выход регистра 7, за исключением дополнительного разряда, подключен к первому входу коммутатора 9, который открывается единичным сигналом с выхода блока 12 сравнения. Пои несовпадении адресов на схеме 12 сравнения в коммутаторе 9 открьюаются вторые входы. По адресу с регистра 5, поступающему через коммутатор 10 на адресный вход накопителя 2, считывается информация, причем с первого выхода накопителя 2 слово поступает на информационные входы преобразователя 16 кода, на управляющий

вход которого поступает дополнительный , разряд с второго выхода накопителя 2. При единичном значении дополнительного разряда, что свидетельствует о хранении в ячейке накопителя 2 обратного кода числа, преобразователь 16 кода проинвер- тирует обратный код слова. Таким образом, на выходе коммутатора 9 появляется код ошибки, который поступает на соответствующие вторые входы группы I4 сумматоров по модулю два, на первые входы которой поступает слово, считанное из накопителя 1 по адресу, хранящемуся в регистре 5 адреса. Группа 14 сумматоров по модулю два исправляет обнаруженные ранее ошибки /путем инвертирования ошибочных разрядов, В третьем такте по сигналу Ag в выходной регистр 4 записывается запрашиваемое слово, которое выдается на информационные выходы 25. .На этом режим считьша- ния Заканчивается,

Формула изобретения

Запоминающее устройство с коррекцией ошибок, содержащее входной регистр, информационные входы которого являются одноименными входами устройства, а выходы соединены с информа- ционньми входами основного накопителя, адресные входы которого подключены к выходам регистра адреса, информационные входы которого являются -адресными входами устройства, выходной регистр, выходы которого являются информационными выходами устройства, входы сброса регистра адреса, входного и выходного регистров . подключены к первому синхровыходу блока управления, синхровыходы с второго по шестой которого соединены соответственно с синхровыходами ре- 5истра адреса и входного регистра, входом записи основного накопителя, синхровходом выходного регистра и с входом записи дополнительного накопителя, входы синхронизации и признака записи-чтения блока управления являются одноименными входами устройства, первый коммутатор, отличающееся тем, что, с целью повышения надежности устройства, в него введены буферный регистр числа, буфеный регистр адреса, первый и второй блоки сравнения, первая и вторая гру

пь сумматоров по модулю два, первьш и второй преобразователи кода,второй коммутатор и триггер, причем выходы

g основного накопителя соединены с первыми входами второй группы сумматоров по модулю два и с вторыми входами первой группы сумматоров по модулю

два, первые входы которых подключены 0 к выходам входного регистра, а выходы соединены с информационными входами буферного регистра числа, выходы которого подключены к информационным входам первого преобразователя кода,

5 к входам первой группы первого блока сравнения и к информационным входам первой группы первого коммутатора, информационные входы второй группы и управляющий вход которого соедине0 ны соответственно с выходами второго преобразователя кода и с выходом второго блоки сравнения, входы первой группы которого подключены к выходам буферного регистра адреса и к инфор5 мационным входам первой группы второго коммутатора, информационные входы второй группы которого соединены с входами второй группы второго блока сравнения, с информационными

0 входами буферного регистра адреса и с выходами регистра адреса, информационные входы и управляющий вход второго преобразователя кода подключены к соответствующим выходам до-35 полнительного накопителя и к входам второй группы первого блока сравнения, выход которого соединен с инфор- мадионньм входом триггера, выход которого подклю ен к входу признака

40 перехода блока управления и к управляющему входу первого преобразователя кода, выходы которого соединены с информационными входами дополнительного накопителя, адресные входы которого

45 подключены к выходам второго коммутатора, управляющий вход которого соединен с входом признака записи- чтения устройства, выходы первого - коммутатора подключены к вторым вхо50 дам второй группы сумматоров по модулю два, выходы которых подсоединены к информационным входам выходного регистра, первый и четвертый выходы блока управления соединены соответственно

55 с входом сброса и синхровходом триггера, а седьмой выход подключен к синхровьйсодам буферного регистра чис- ла и буферного регистра адреса.

стг

26

30

Фае. i

Ж О

27 2

5/

Фиг: 2

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Самофалов К.Г., Корнейчук В.И., Городний А.В | |||

| Структурно-логические методы повышения надежности запоминающих устройств, М,: Машиностроние, 1976, с | |||

| Деревянный торцевой шкив | 1922 |

|

SU70A1 |

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

Авторы

Даты

1988-12-15—Публикация

1987-05-27—Подача