n

Изобретение относится к вычислительной технике и может быть использовано при создании высоконадежных запоминающих устройств и систем, выполненных на функциональных узлах с большой степенью интеграции,

Известно запоминающее устройство с самоконтролем, содержащее накопитель, регистры адреса прямого и обратного кодов, блок кодированиядекодирования, схему сравнения, счетчик, распределитель и буферный регистр Щ.

Недостатками данного запоминающего устройства являются большие аппаратурные затраты на реализацию счетчика и распределителя сигналов, что снижает надеямость устройства, и, кроме того, для исправления обна руженных ошибок необходимо дополнительное время на перебор всех возмож ных комбинаций и проверку правильное ти каждого из наборов, что снижает быстродействие системы в целом.

Наиболее близким по технической сущности к изобретению является запоминающее устройство, содержащее накопитель, подключенный к входам. регистров прямого и обратного кодов выходы которых подключены к блоку обнаружения отказавших разрядов, корректирующее устройство, вход которого соединен с выходом регистра прямого кода, первый информационный выход - с блоком элементов И, второй информационньй выкод - со . схемой равенства кодов, к второму входу которой подключен выход блока обнаружения отказавших разрядивj и блок управления 2j .

Недостатком известного устройства являе.тся низкая корректирующая . способность Применяемого кода.

Цель изобретения - повы51ение надежности запоминающего устройства.

Указанная цель достигается тем, что в запоминающее устройство с исправлением ошибок, содержащее накопитель, первый и второй регистры, первый блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-ИЛИ, блок декодирования, блок управления, причем информационный вход накопителя соединен с одними выходами первого регист ра, выходы накопителя подключены к информационным входам первого и второго регистров, выходы второго регистра и другие выходы первого регистра соединены с входами первого

36242

блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого подключены к одним входам элемента , выход которо го соединен с первьм входом блока 5 ,управления, второй, третий и четвертый входы которого являются управляющими входами устройства, первый, второй и третий выходы блока управления подключены соответственно к

О управляющим входам накопителя и первого, и второго регистров, четвертый выход, блока управления является контрольным выходом устройства, введены коммутатор, второй блок элементов

S ИСКЛЮЧАЩЕЕ ИЛИ, дешифратор, элемент ИЛИ, третий регистр, причем информационные входы коммутатора соединены с выходами второго регистра и другими выходами первого регистра, пятый

0 и шестой выходы блока управления подключены к управляющим входам коммутатора, выходы которого соедннены с входами блока декодирования, выходы которого подключены к входам

5 дешифратора и элемента ИЛИ, выход которого соединен с пятым входом блока управления, выходы коммутатора и дешифратора соединены с входами второго блока элементов ИСКЛЮЧАЮЩЕЕ

0 ИЛИ, выходы которого подключены к информационньпх входам третьего регистра, выходы которого являются информационными выходами устройства, управляющий вход третьего регистра подключен к седьмому выходу блока управления, выходы дешифратора сйединены с другими входами элемента Иили.- ,

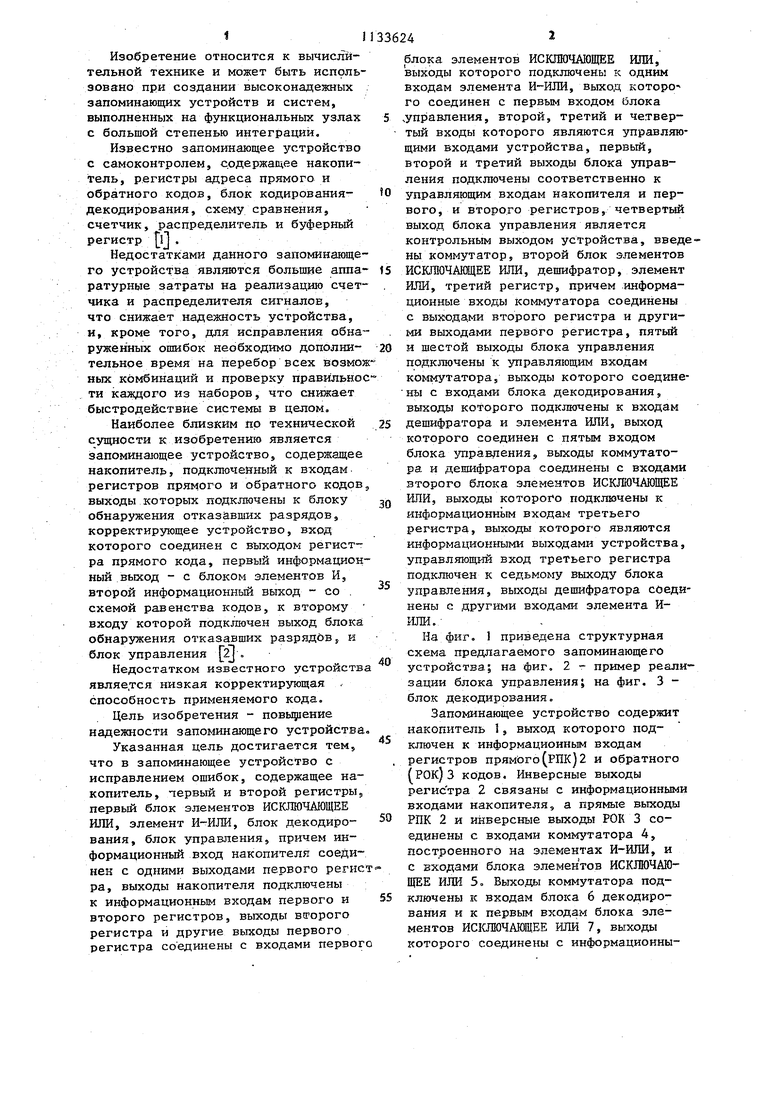

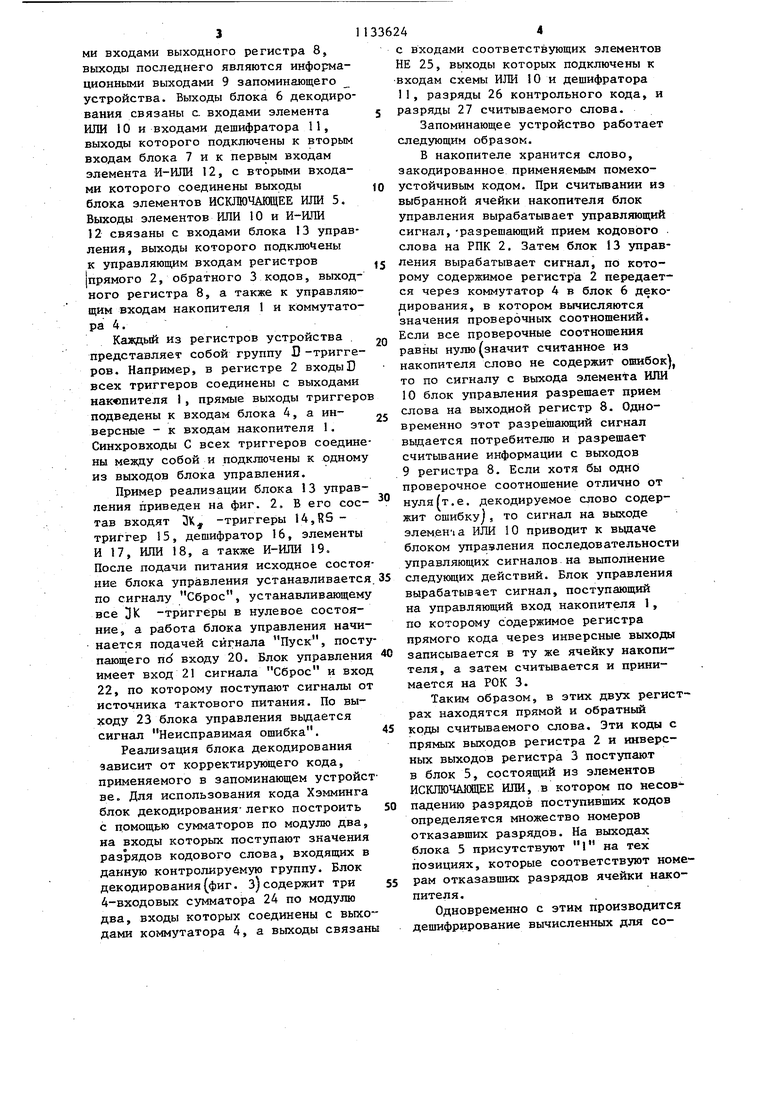

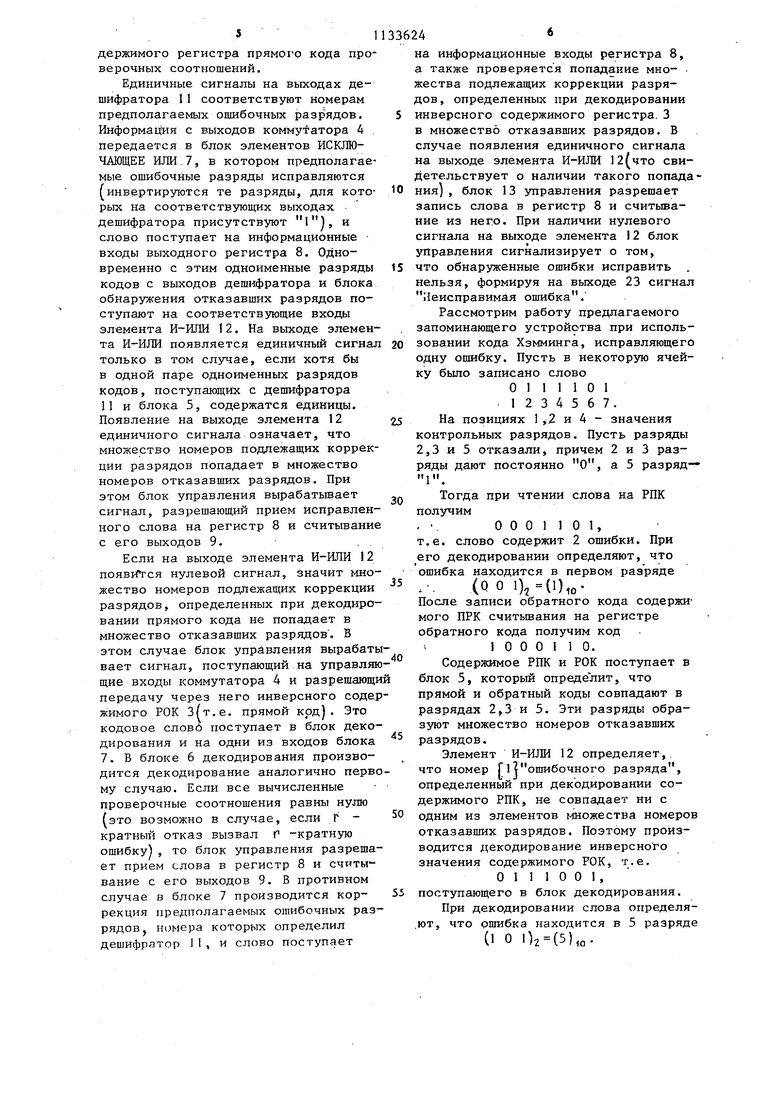

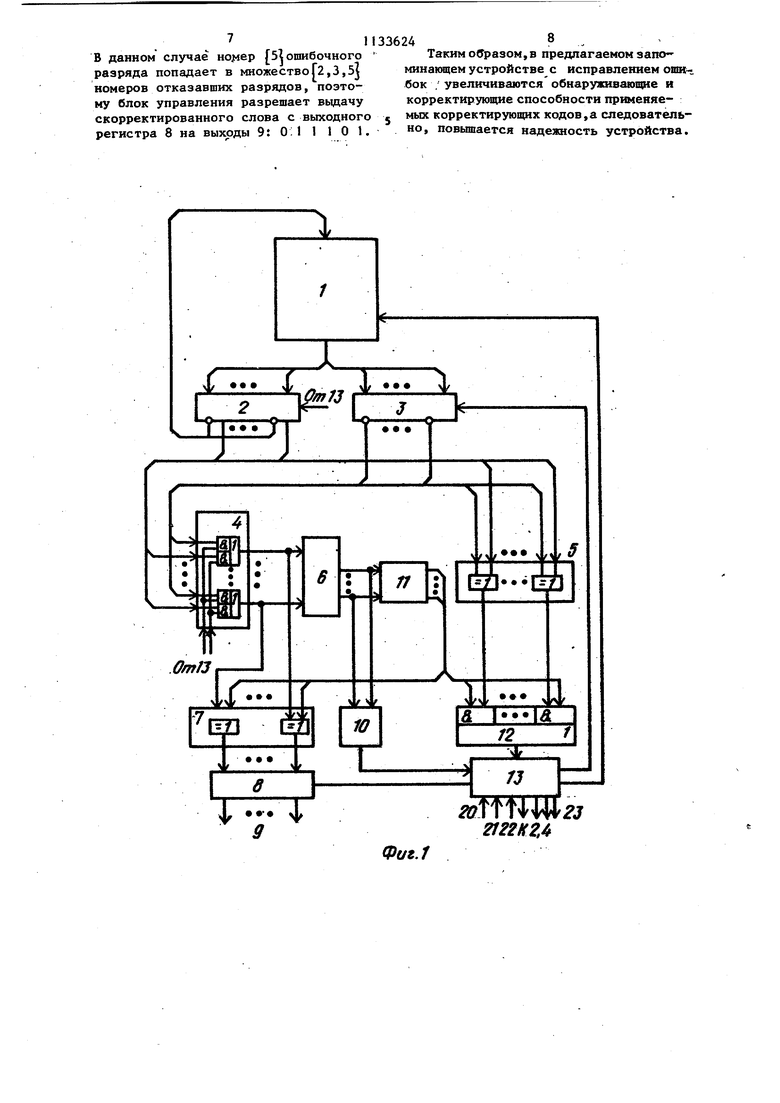

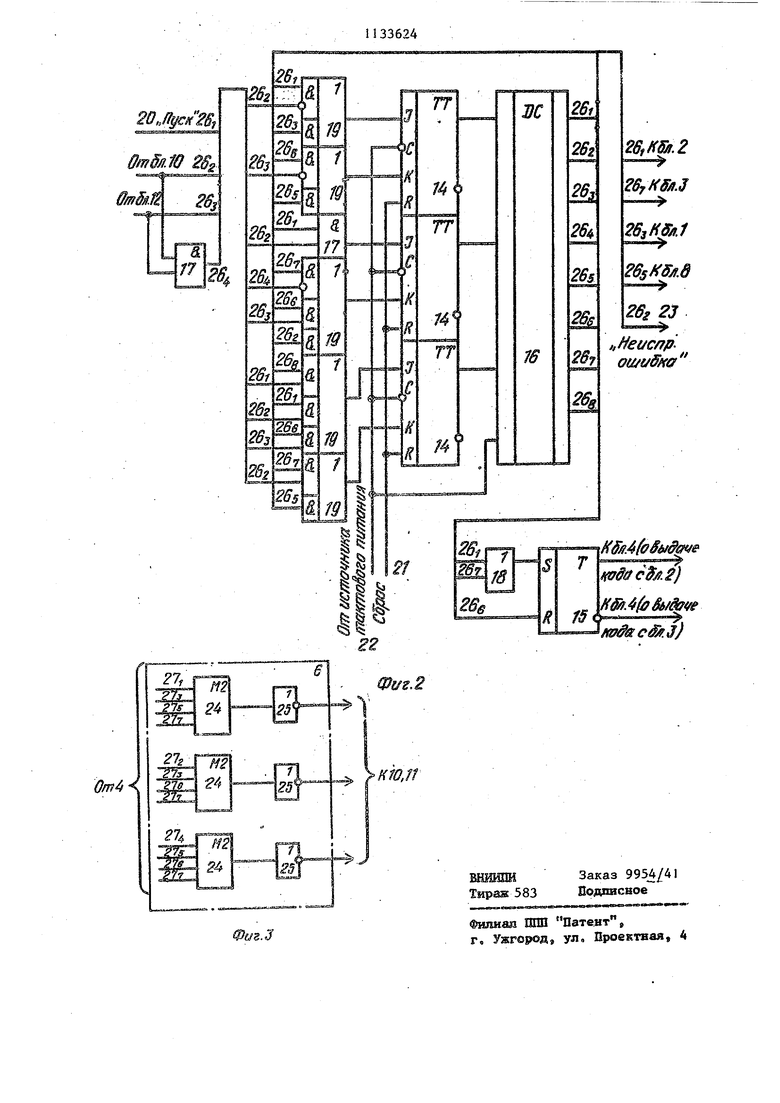

На фиг. 1 приведена структурная схема предлагаемого запоминающего устройства; на фиг, 2 - пример реализации блока управления; на фиг. 3 блок декодирования.

Запоминающее устройство содержит накопитель i, выход которого подключен к информационным входам , регистров прямОго(Р11К)2 и обратного РОК)3 кодов. Инверсные выходы регистра 2 связаны с информационными входами накопителя, а прямые выходы

9 РПК 2 и инверсные выходы РОК 3 соединены с входами коммутатора 4, построенного на элементах И-ЕПИ, и с входами блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 5о Выходы коммутатора подключены к входам блока 6 декодирования и к первым входам блока элементов ИС1ШОЧАЮЩЕЕ ИЛИ 7, выходы которого соединены с информационны311

и входами выходного регистра 8, ыходы последнего являются информаионными выходами 9 запоминающего стройства. Выходы блока 6 декодироания связаны с. входами элемента ЛИ 10 и входами дешифратора 11, ыходы которого подключены к вторым ходам блока 7 и к первым входам элемента И-ИЛИ 12, с вторыми входаи которого соединены выходы блока элементов ИСКЛЮЧАЩЕЕ ИЛИ 5. Выходы элементов ИЛИ 10 и И-ИЛИ 12 связаны с входами блока 13 управления, выходы которого подключены к управляющим входам регистров прямого 2, обратного 3 кодов, выходного регистра 8, а также к управляющим входам накопителя 1 и коммутатора 4.

Каждый из регистров устройства представляет собой группу D -триггеров. Например, в регистре 2 входыD всех триггеров соединены с выходами нак«пителя 1, прямые выходы триггеров подведены к входам блока 4, а инверсные - к входам накопителя 1. Синхровходы С всех триггеров соединены между собой и подключены к одному из выходов блока управления.

Пример реализации блока 13 управления приведен на фиг. 2. В его состав входят ЗХ -триггеры t4,RSтриггер 15, дешифратор 16, элементы И 17, ИЛИ 18, а также И-Ш1И 19. После подачи питания исходное состояние блока управления устанавливается по сигналу Сброс, устанавливающему все 2 -триггеры в нулевое состояние, а работа блока управления начинается подачей сигнала Пуск, поступающего nd входу 20. Блок управления имеет вход 21 сигнала Сброс и вход 22, по которому поступают сигналы от источника тактового питания. По выходу 23 блока управления выдается сигнал Неисправимая ошибка.

Реализация блока декодирования зависит от корректирующего кода, применяемого в запоминающем устройстве. Для использования кода Хэмминга блок декодирования- легко построить с помощью сумматоров по модулю два, на входы которых поступают значения разрядов кодового слова, входящих в даннзто контролируемую группу. Блок декодирования(фиг. З)содержит три 4-входовых сумматора 24 по модулю два, входы которых соединены с выходами коммутатора 4, а выходы связаны

36244

с входами соответствующих элементов НЕ 25, выходы которых подключены к входам схемы ИЖ 10 и дешифратора 1, разряды 26 контрольного кода, и

разряды 27 считываемого слова.

Запоминающее устройство работает следующим образом.

В накопителе хранится слово, закодированное применяемым помехоустойчивым кодом. При считьгеании из выбранной ячейки накопителя блок управления вырабатывает управляющий сигнал,-разрешающий прием кодового . слова на РПК 2, Затем блок 13 управления вырабатывает сигнал, по которому содержимое регистра 2 передается через коммутатор 4 в блок 6 декодирования, в котором вычисляются значения проверочных соотношений.

Если все проверочные соотношения

U . /

равны нулю значит считанное из накопителя слово не содержит ошибок), то по сигналу с выхода элемента ИЛИ 10 блок управления разрешает прием слова на выходной регистр 8. Одновременно этот разрешающий сигнал вьщается потребителю и разрешает считьшание информации с выходов 9 регистра В. Если хотя бы однб проверочное соотношение отлично от .е. декодируемое слово содержит ошибку, то сигнал на выходе элененча ИЛИ 10 приводит к вьдаче блоком управления последовательности управляющих сигналов на выполнение

следукяцих действий. Блок управления вырабатывает сигнал, поступающий на управляющий вход накопителя 1, по которому содержимое регистра прямого кода через инверсные выходы

записывается в ту же ячейку накопителя, а затем считывается и принимается на РОК 3.

Таким образом, в этих двух регистрах находятся прямой и обратный

5 коды считываемого слова. Эти коды с прямых выходов регистра 2 и инверсных выходов регистра 3 поступают в блок 5, состоящий из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, в котором по несов

0 падению разрядов поступивших кодов определяется множество номеров отказавших разрядов. На выходах блока 5 присутствуют 1 на тех позициях, которые соответствуют номерам отказавших разрядов ячейки накопителя.

Одновременно с этим производится дешифрирование вычисленных для содержимого регистра прямого кода проверочных соотношений. Единичные сигналы на выходах дешифратора 11 соответствуют номерам предполагаемых ошибочных разрядов. Информация с выходов коммутатора 4 передается в блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 7, в котором предполагаемые ошибочные разряды исправляются (инвертируются те разряды, для которых на соответствующих выходах дешифратора присутствуют , и слово поступает на информационные входы выходного регистра 8. Одновременно с этим одноименные разряды кодов с выходов дешифратора и блока обнаружения отказавших разрядов поступают на соответствующие входы элемента И-ИЛИ 12. На выходе элемента И-ИЛИ появляется единичный сигнал только в том случае, если хотя бы в одной паре одноименных разрядов кодов, поступающих с дешифратора 11 и блока 5, содержатся единицы. Появление на выходе элемента 12 единичного сигнала означает, что множество номеров подлежащих коррекции разрядов попадает в множество номеров отказавших разрядов. При этом блок управления вырабатьюает сигнал, разрешающий прием исправленного слова на регистр 8 и считывание с его выходов 9. Если на выходе элемента И-ИЛИ 12 появгЛся нулевой сигнал, значит множество номеров подлежащих коррекции разрядов, определенных при декодировании прямого кода не попадает в множество отказавших разрядов . В этом случае блок управления вырабаты вает сигнал, поступающий на управляю щие входы коммутатора 4 и разрешающи передачу через него инверсного содер жимого РОК 3/т.е. прямой код). Это кодовое слово поступает в блок декодирования и на одни из входов блока 7. В блоке 6 декодирования производится декодирование аналогично перво му случаю. Если все вычисленные проверочные соотношения равны нулю (это возможно в случае, если Г кратный отказ вызвал Г -кратную ошибку), то блок управления разрешает прием слова в регистр 8 и считы вание с его выходов 9. В противном случае в блоке 7 производится коррекция предполагаемых ошибочных разрядов, номера которых определил дешифратор 11, и слово поступает 46 на информационные входы регистра 8, а также проверяется попадание мно- . жества подлежащих коррекции разрядов , определенных при декодировании инверсного содержимого регистра. 3 в множество отказавших разрядов. В случае появления единичного сигнала на выходе элемента И-ИЛИ 12(что свидетельствует о наличии такого попада ния), блок 13 управления разрешает запись слова в регистр 8 и считывание из него. При наличии нулевого сигнала на выходе элемента I2 блок управления сигнализирует о том, что обнаруженные ошибки исправить нельзя, формируя на выходе 23 сигнал ;1еисправимая ошибка. Рассмотрим работу предлагаемого запоминающего устройства при использовании кода Хэмминга, исправляющего одну ошибку. Пусть в некоторую ячейку было записано слово 0111101 1234567. На позициях и 4 - значения контрольных разрядов. Пусть разряды 2,3 И 5 отказали, причем 2 и 3 разряды дают постоянно О, а 5 разряд- Тогда при чтении слова на РПК получим 0001101, т.е. слово содержит 2 ошибки. При его декодировании определяют, что ошибка находится в первом разряде (QO 1)(0,оПосле записи обратного кода содержимого ПРК считьшания на регистре обратного кода получим код 10001 10. Содержимое РПК и РОК поступает в блок 5, который определит, что прямой и обратный коды совпадают в разрядах 2,3 и 5. Эти разряды образуют множество номеров отказавших разрядов. Элемент И-ИЛИ 12 определяет,, что номер Г1| ошибочного разряда, определенный при декодировании содержимого РПК, не совпадает ни с одним из элементов i-шожества номеров отказавших разрядов. Поэтому производится декодирование инверсного значения содержимого РОК, т.е. 0111001, поступающего в блок декодирования. При декодировании слова определячто ошибка находится в 5 разряде (1 О 1)2 (5,о. 7, В данном случае номер 5 ошибочного разряда попадает в множество 2,3,5 номеров отказавших разрядов, поэтому блок управления разрешает выдачу скорректированного слова с выходного регистра 8 на выходы 9: 0:1 1 1 О 1. 1336 , 248 . Таким образом,в предлагаемом запо минающем устройстве с исправлением оши бок . увеличиваются обнаруживающие и корректирующие способности примеяяемых корректирующих кодов,а следовательно, повышается надежность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Запоминающее устройство | 1988 |

|

SU1531175A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1075312A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1983 |

|

SU1138836A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1152042A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С . ИСПРАВЛЕНИЕМ ОШИБОК, содержащее накопитель, первый и второй регистры, первый блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-ИЛИ, блок декодирования, блок управления, причем информационный вход накопителя соединен с одними выходами первого регистра, выходы накопителя подключены к информационным входам первого,и второго регистров, выходы второго регистра и другие выходы первого регистра соединены с входами первого блока элементов ИСЮЮЧАЩЕЕ ИЛИ, выходы которого подключены к одним входам элемента И-ШШ, выход которого соединен с первым входом блока управления, второй, третий и четвертый . входы которого являются управляющими входами устройства, первый, второй и третий выходы блока управления подключены соответственно к управляющим входам накопителя и первого, и второго регистров, четвертый выход блока управления является контрольным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены коммутатор, второй блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, дешифратор, элемент ИЛИ, третий регистр, причем информационные входы коммутатора соединены с выходами второго регистра и да|угими выходами первого регистра, пятый и шестой выходы (Л блока управления подключены к управляющим входам коммутатора, выходы которого соединены с входами блока декодирования, выходы которого подключены к входам дешифратора и элемента ИЛИ, выход которого соединен с пятым входом блока управления, э со выходы коммутатора и дешифратора соединены с входами второго блока Эд элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого подключены к информацион о ным входам третьего регистра, вы ходы которого являются информационными выходами устройства, управляющий вход третьего регистра подключен к седьмому выходу блока управления, выходы дешифратора соединены с другими входами элемента И-ИЛИ.

л. JL

ff

ггггк2.4

Фи1,1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Солесос | 1922 |

|

SU29A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

Авторы

Даты

1985-01-07—Публикация

1983-11-16—Подача