11

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройство

Целью изобретения является повышение надежности устройства.

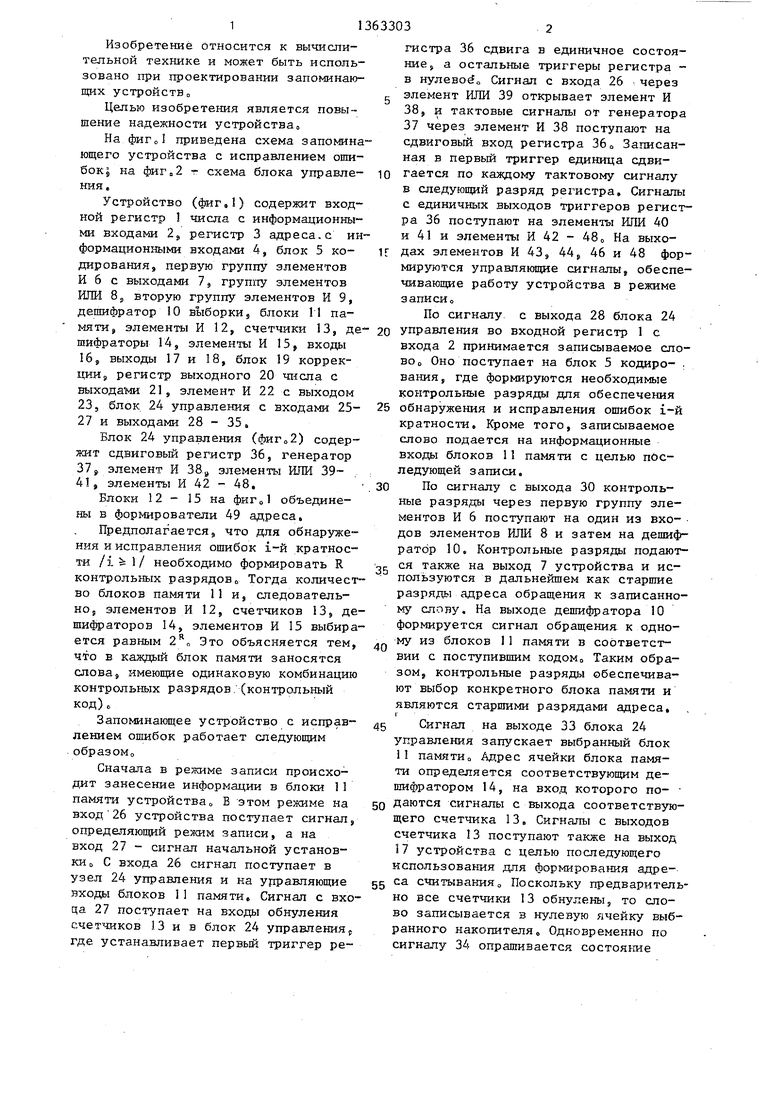

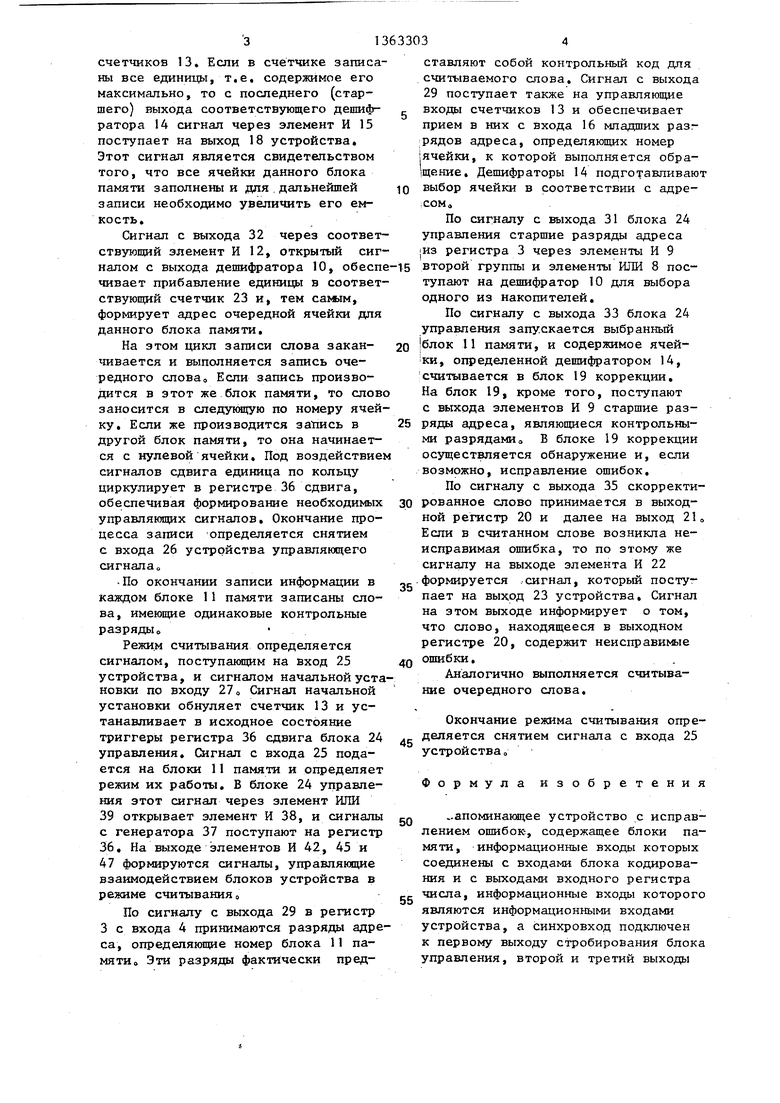

На фиго приведена схема запоминающего устройства с исправлением опш- бок| на фиг,2 г- схема блока управле- ния.

Устройство (фиг,) содержит входной регистр 1 числа с информационными входами 2,, регистр 3 адреса, с информационными входами 4, блок 5 ко- дирования, первую группу элементов

И 6 с выходами 7 j группу элементов ИЛИ 85 вторую группу элементов И 9, дешифратор 0 выборки, блоки М па30

мяти, элементы И 12, счетчики 13, де- 20 управления во входной регистр 1 с шифраторы 14, элементы И 15, входы 16, выходы 17 и 18, блок 19 коррекции, регистр выходного 20 числа с выходами 21, элемент И 22 с выходом 23, блок 24 управления с входами 25- 27 и выходами 28 - 35,

Блок 24 управления (фиг„2) содержит сдвиговый регистр 36, генератор 37 элемент И 38 элементы ИЛИ 39- ,, : 41, элементы И 42 - 48,

Блоки 12 - 15 на фиг„1 объединены в формирователи 49 адреса.

Предполагается, что для обнаружения и исправления ошибок i-й кратности необходима формировать R контрольных разрядов о Тогда количество блоков памяти 11 и, следовательно, элементов И 12, счетчиков 13, дешифраторов 14, элементов И 15 выбирается равным Это объясняется тем, что в каждый блок памяти заносятся

35

входа 2 принимается записываемое с во о Оно поступает на блок 5 кодиро вания, где формируются необходимые контрольные разряды для обеспечени 25 обнаружения и исправления ошибок i кратности. Кроме того, записываемо слово подается на информационные входы блоков 11 памяти с целью пос ледующей записи.

По сигналу с выхода 30 контроль ные разряды через первую группу эл ментов И 6 поступают на один из вх дов элементов ШШ 8 и затем на деш ратор 10. Контрольные разряды пода ся также на выход 7 устройства и и пользуются в дальнейшем как старши разряды адреса обращения к записан му слову. На выходе дешифратора 10 формируется сигнал обращения к одн му из блоков 11 памяти в соответст вии с поступившим кодомо Таким обр зом, контрольные разряды обеспечив ют выбор конкретного блока памяти являются старшими разрядами адреса

40

слова, имеющие одинаковую комбинацию контрольных разрядов;(контрольный код).

Запоминающее устройство с испра.в- лением ошибок работает следующим - образом

Сначала в режиме записи происходит занесение информации в блоки 11 памяти устройства о Б этом режиме на вход 26 устройства поступает сигнал, определяющий режим записи, а на вход 27 - сигнал начальной установки о С входа 26 сигнал поступает в узел 24 управления и на управляющие входы блоков 11 памяти. Сигнал с вхо- ца 27 поступает на входы обнуления счетчиков 13 и в блок 24 управления где устанавливает первый триггер регистра 36 сдвига в единичное состояние j а остальные триггеры регистра - в нулевого Сигнал с входа 26 через элемент ИЛИ 39 открывает элемент И 38, и тактовые сигналы от генератора 37 через элемент И 38 поступают на сдвиговый вход регистра 36 о Записанная в первый триггер единица сдвигается по каждому тактовому сигналу в следующий разряд регистра. Сигналы с единичных выходов триггеров регистра 36 поступают на элементы ИЛИ 40 и 41 и элементы И 42 - 48о На выходах элементов И 43, 44, 46 и 48 формируются управляющие сигналы, обеспечивающие работу устройства в режиме записио

По сигналу с выхода 28 блока 24

0

0 управления во входной регистр 1 с

5

входа 2 принимается записываемое слово о Оно поступает на блок 5 кодиро- : вания, где формируются необходимые контрольные разряды для обеспечения 5 обнаружения и исправления ошибок i-й кратности. Кроме того, записываемое слово подается на информационные входы блоков 11 памяти с целью последующей записи.

По сигналу с выхода 30 контрольные разряды через первую группу элементов И 6 поступают на один из вхо- дов элементов ШШ 8 и затем на дешифратор 10. Контрольные разряды подаются также на выход 7 устройства и используются в дальнейшем как старшие разряды адреса обращения к записанному слову. На выходе дешифратора 10 формируется сигнал обращения к одному из блоков 11 памяти в соответствии с поступившим кодомо Таким образом, контрольные разряды обеспечивают выбор конкретного блока памяти и являются старшими разрядами адреса.

Сигнал на выходе 33 блока 24 управления запускает выбранный блок 11 памяти о Адрес ячейки блока памяти определяется соответствующим дешифратором 14, на вход которого по- 0 даются сигналы с выхода соответствующего счетчика 13, Сигналы с выходов счетчика 13 поступают также на выход 17 устройства с целью последующего использования для формирования адре-- са считывания о Поскольку предварительно все счетчики 13 обнулены, то слово записывается в нулевую ячейку выбранного накопителя Одновременно по сигналу 34 опрашивается состояние

0

5

5

313

счетчиков 13. Если в счетчике записаны все единицы, т.е. содержимое его максимально, то с последнего (старшего) выхода соответствующего дешиф- ратора 14 сигнал через элемент И 15 поступает на выход 18 устройства. Этот сигнал является свидетельством того, что все ячейки данного блока памяти заполнены и для . дальнейшей записи необходимо увеличить его емкость.

Сигнал с выхода 32 через соответствующий элемент И 12, открытый сиг

налом с выхода дешифратора 10, обеспе-15 второй группы и элементы ЩШ 8 посчивает прибавление единицы в соответствующий счетчик 23 и, тем caiejM, формирует адрес очередной ячейки для данного блока памяти.

На этом цикл записи слова заканчивается и выполняется запись очередного сповао Если запись производится в этот же блок памяти, то слово заносится в следующую по номеру ячейку. Если же производится запись в другой блок памяти, то она начинается с нулевой ячейки. Под воздействием сигналов сдвига единица по кольцу циркулирует в регистре 36 сдвига, обеспечивая формирование необходимых управлянщих сигналов. Окончание процесса записи определяется снятием с входа 26 устройства управляющего сигнала

-По окончании записи информации в каждом блоке 11 памяти записаны слова, имеюпще одинаковые контрольные разрядыо

Режим считывания определяется сигналом, поступающим на вход 25 устройства, и сигналом начальной установки по входу 27 о Сигнал начальной установки обнуляет счетчик 13 и устанавливает в исходное состояние триггеры регистра 36 сдвига блока 24 управления. Сигнал с входа 25 подается на блоки 11 памяти и определяет режим их работы, В блоке 24 управления этот сигнал через элемент РШИ 39 открывает элемент И 38, и сигналы с генератора 37 поступают на регистр 36, На выходе элементов И 42, 45 и 47 формируются сигналы, управлявшие взаимодействием блоков устройства в режиме считывания о

По сигналу с выхода 29 в регистр 3 с входа 4 принимаются разряды адреса, определяющие номер блока 11 памяти Эти разряды фактически представляют собой контрольный код для считываемого слова. Сигнал с выхода 29 поступает также на управляющие входы счетчиков 13 и обеспечивает прием в них с входа 16 младших разг рядов адреса, определяющих номер 1ячейки, к которой выполняется обращение. Дешифраторы 14 подготавливаю выбор ячейки в соответствии с адре:СОМо

По сигналу с выхода 31 блока 24 управления старшие разряды адреса I из регистра 3 через элементы И 9

0

5

0

5

0

5

0

5

тупают на дешифратор 10 для выбора одного из накопителей.

По сигналу с выхода 33 блока 24 управления запускается выбранный блок 11 памяти, и содержимое ячей- ки, определенной дешифратором 14, считывается в блок 19 коррекции. На блок 19, кроме того, поступают с выхода элементов И 9 старшие разряды адреса, являющиеся контрольными разрядами В блоке 19 коррекции осущест)вляется обнаружение и, если возможно, исправление ошибок.

По сигналу с выхода 35 скорректированное слово принимается в выходной регистр 20 и далее на выход 21 Если в считанном слове возникла неисправимая ошибка, то по этому же сигналу на выходе элемента И 22 -формируется .сигнал, который поступает на выход 23 устройства. Сигнал на этом выходе информирует о том, что слово, находящееся в выходном регистре 20, содержит неисправимые ошибки.

Аналогично выполняется считывание очередного слова,

Окончание режима считывания определяется снятием сигнала с входа 25 устройства

Формула изобретения

.апоминакщее устройство с исправлением ошибок, содержащее блоки памяти, информационные входы которых соединены с входами блока кодирования и с выходами входного регистра числа, информационные входы которого являются информационными входами устройства, а синхровход подключен к первому выходу стробирования блока управления, второй и третий выходы

стробирования которого соединены соответственно с синхровходами регистра адреса и регистра выходного числа, выходы которого являются ин- формационными выходами устройства, а информационные входы подключены к информационным выходам блока коррекции, входь информационных разрядов которого соединены с выходами блоков памяти, а входы контрольных разрядов подключены к выходам элементов И второй группы и к вторым входам элементов ИЛИ группы, первые входы которых соединены с выхода ми элементов И первой группы, первые входы которых подключены к выходам блока кодирования, а вторые -входы соединены с выходом признака записи блока управления, выход признака чтения которого подключен к вторым входам элементов И второй группы, первые входы которых соединены с выходами регистра адреса, информационные входы которого являются входами старших разрядов адреса устройства, входы признаков записи и чтения блока управления соединены с одноименными входами блоков памяти и являются входами записи и чтения устройст- ва, вход начальной установки блока управления является одноименным входом устройства, выход обращения блока управления соединен с одноименным входами блоков памяти, выходыоэлемен тов ИЛИ подключены к входам дешифраJ5 З 33

L-l-1 -4r

и.

5 0 0 5

5

тора выборки, выходы которого соединены с входами выборки соответствующих блоков памяти, выходы элементов первой группы являются выходами старших разрядов адреса устройства, о т- ли чающееся тем, что, с целью повышения надежности, в устройство введены формирователи адреса по числу блоков.памяти и элемент И, причем входы элемента И соединены с выходом признака ошибки блока коррекции и с третьим выходом стробирования блока управления, четвертый и второй выходы стробирования которого подключены соответственно к первому и второму синхровходам формирователей адреса, адресные входы кото-: рых являются входами младших разрядов адреса устройства, выход признака инкрементирования адреса блока управления соединен с одноименными входами формирователей адреса, входы выборки которых подключены к соответствующим выходам дешифратора выборки, входы начальной установки формирователей адреса подключены к одноименному входу устройства, адресные выходы формирователей адреса соединены с адресными входами соот- ветствуюшях блоков памяти, выходы признака переполнения формирователей адреса являются одноименными выходами устройства, а выход элемента И является выходом признака ошибки устройства, гэ 2i

t ,

П

л к ы

Редактор Л.Веселовская Техред Л.Олийнык

Заказ 6369/45Тираж 588Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб. , д. 4/5

Производственно-полиграфическое предпр1штие, г.Ужгород, ул,Проектная,4

Корректор АоЗимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

| Запоминающее устройство с исправ-лЕНиЕМ ОшибОК | 1979 |

|

SU841059A1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| Устройство для поиска информации в памяти | 1986 |

|

SU1392579A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Декодирующее устройство кода Рида-Соломона | 1988 |

|

SU1640830A1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании запоминающих устройств. Целью изобретения является повышение надежности устройства. Устройство содержит накопитель. входной 1 и выходной 20 регистры числа, ;регистр 3 адреса, блок 5 кодирования,- блок коррекции, блок 24 управления, дешифратор 10 выборки, формирователи 49 адреса, первую 6 и вторую 9 группы элементов И, группу 8 элементов ИЛИ, элемент И 12 В уст- ройстве накопитель разделен на блоки памяти, в каждом из которых хранятся слова, имеющие одинаковое значение контрольных разрядов, используемых в качестве старших разрядов кода адреса. Это позволяет исключить необходимость хранения контрольных разрядов в накопителе, что ведет к увеличению надежности всего запоминающего устройства, 2 ил. i (Л со 00 со о со

| Запоминающее устройство с самоконтролем | 1976 |

|

SU618799A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с исправ-лЕНиЕМ ОшибОК | 1979 |

|

SU841059A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-30—Публикация

1986-05-06—Подача