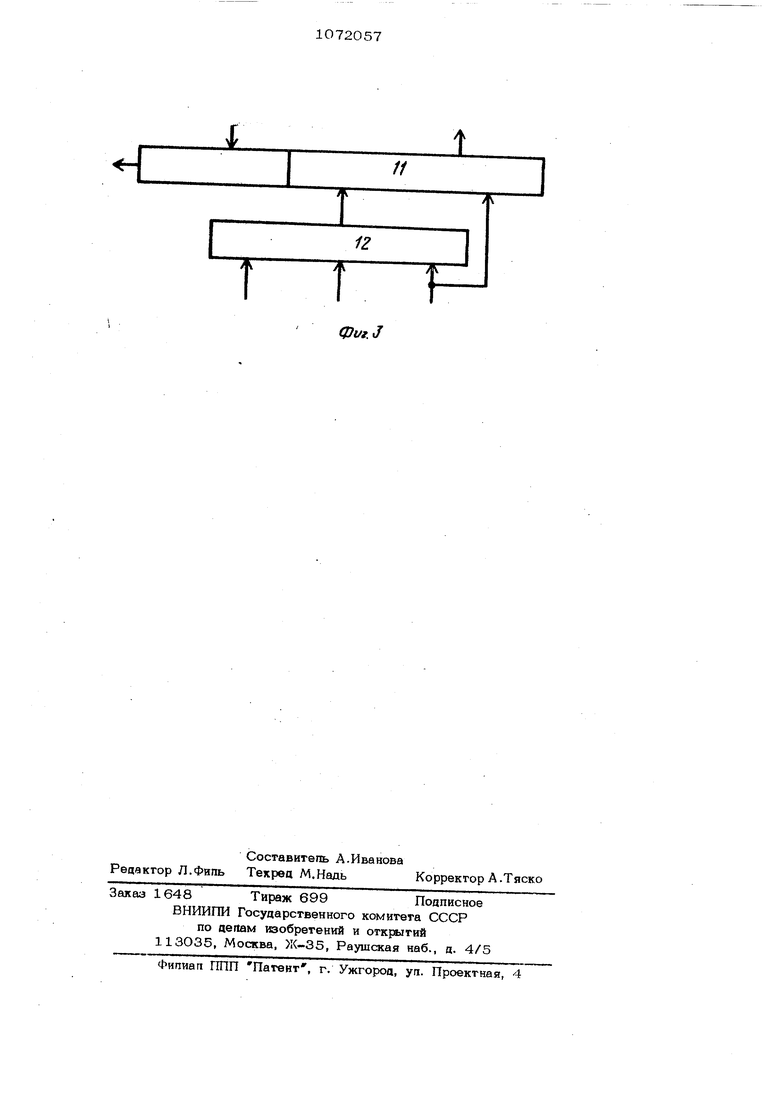

Изобретение относится к измерению характеристик спучайных процессов и пред назначено nns оперативного определения коррепяционной функции текущего стационарного случайного процесса. Известен цифровой коррепятор, содержащий квантоватепи по уровню, на входы которых КЗ блока памяти поступают сдвинутые на время задержки сигнагаы. Квантованные по уровню сигналы поступают через бпок выборки во времени на бпок умножения и цапее на накапливающий счет чик Си . Недостатком этого устройства явпяется низкое быстродействие. Наиболее бпизким по технической сущности к предпагаемому явгюется цифровой коррелятор, соцержащий бпок памяти, вход которого подключен через блок записи к входу устройства, а выходы - к первым входам первого, второго и третьего блоков воспроизведен сигнала, к вторым входам которых параллельно подключены выходы генератора импульсов, первый выход первого блока воспроизведения сигнала последовательно подключен к первому входу; сумматора, первому входу блока yivi , ножения и информационному входу интегра тора, к вторым входам сумматора и блок умножения подключены соответственно выходы второго и третьего бпока воспроизведения сигнала. Причем каждый бпок вос произведения сигнала содержит бпок опроса, сумматор, блок сравнения, первый и второй счетчики Г2J В известном устройстве объем обрабатываемык данных определяется разрядностью N сумматора первого блока воспроизведения сипшла и равен 2 , это обстоятельство не позволяет полностью обрабатывать выборки с произвольным, не кратным степени 2, объемом, т.е. сужаются функциональные возможности цифрового коррелятора. Кроме того, устройство обладает аппаратурной избыточность Цель изобретения - расширение класса решаемых задач. Указанная цель достигается тем, что в цифровом корреляторе, содержащем бпок записи, вход которого является входом коррелятора, а выход соединён с входом записи блока памяти, генератор импульсов бпок суммирования, выход которого соеди нен с первым входом блока умножения, выход которого подключен к информационному входу интегратора, выход которого является выходом коррелятора, блоки воспроизведения сигнала, каждый из которых содержит узел памяти и сумматор, выход которого соединен с адресным входом узла памяти своего бпока воспроизведения сигнала, информационный вход узла памяти каждого бпока воспроизведения сигнала соединен с соответствующим выходом группы выходов блока памяти, управляющий вход узла памяти и первый информационный вход сумматора в каждом блоке воспроизведения сигнала объединены и подключены к выходу генератора импульсов, а информационный выход узпа памяти в каждом блоке воспроизведения сигна гю подключен соответственно к первому и второму входам блока суммирования и к второму входу блока умножения коррелятора, при том первый блок воспроизведения сигнала содержит первую схему сравнения, первый и второй счетчики, выходы которых подключены к соответствующим входам схемы сравнения, а выход первого счетчика дополнительно подключен к второму информационному входу сумматора первого блока воспроизведения сигнала, выход первой схемы сравнения первого блока воспроизведения сигнала подключен к управляющему вхоцу сумматора и первому управляющему входу второго счетчика, второй управляющий вход которого объединен со счетным входом первого счетчика, а счетный вход второго счетчика объединен с первым информационным входом сумматора своего бпока, первый блок воспроизведения сигнала содержит вторую схему сравнения и третий счетчик, выход которого подключен к первому входу второй схемы сравнения, второй вход которой соединен с выходом сумматора своего блока, а выход второй схемы сравнения подключен к счетным входам первого и третьего счетчиков своего блока и к управляющему входу интегратора, выход первой схемы сравнения первого блока воспроизведения сигнала соединен с управляющим входом сумматоров второго и третьего блоков воспроизведения сигнала, выход первого счетчика первого блока воспроизведения сигнала соединен с вторым информационным входом сумматоров второго и третьего блоков воспроизведения сигнала, управляющий выход узпа памяти каждого блока воспроизведения сигнала подключен к соответствующему адресному входу блока памяти. На фиг. 1 представлена структурная схема цифрового коррелятора; на фиг. 2 структурная схема первого блока воспроизведения; на фиг. 3 - структурная схема второго и третьего блоков воспроизведения. 31О7 Входом устройства явпяется вход бпока 1 записи, выход которого подключен к информационному ходу бпока 2 памяти. Выходы бпока 2 памяти подкпючешы к первым входам блоков 3-5 воспроизведения, к вторым входам которых подключен выход генератора 6 импупьсов. Первый выход первого бпока 3 воспроизведения, последовательно подключен к первому входу сумматора 7, первсыу входу блока 8 умножения и информационному входу интегратора 9. К вторым входам сумматора 7 и блока 8 умножения подключены соответственно первые выходы второго и третьего блоков 4 и 5 воспроизведения, третий и четвертый входы каждого из которых подключены соответственно к третьему и четвертому выходам первого блока 3 воспроизведения, пятый выход которого соединен с управляющим входом интегратора 9. В то рые выходы первого, второго и третьего блоков 3,4 и 5 воспроизведения подключены соответственно к второму, третьему и четвертому адресным входам блока 2 памяти. Выход 10 интегратора 9 является выходом устройства. Первый блок 3 воспроизведения сигнала (фиг. 2) содержит узел 11- памяти, сумматор 12, первую схему 13 сравнения первый 14 и. второй 15 счетчики, вторую схему 16 сравнения и реверсивный счетчик 17. Информационный вход и первый выход узла 11 памяти являются соответственно первым входом 18 и первым выходом 19 первого блока 3 воспроизведения сигнала. К адресному входу блока 11 памяти поогключен выход сумматора 12, первый информационный выход которого соединен с вторым входом первого блока 3 воспроизведения сигнала, второй выход которого подключен к второму выходу узла 11 памяти. Третий выход блока 3 воспроизведения сигнала, соединенный с выходом первого счетчика 14, подключен к второму информационному входу сумматора 12 и к первому входу первой схемы 13 сравнения. Второй вход схемы 13 сравнения подключен к выходу второго счетчика 15, а выход схемы 13 сравнения, соединенный с четвертым выходом первого блсжа 3 воспроизведения сигнала, подключен к первому управляющему выходу второго счетчика 15. Счетный вход второго счетчика 15 соединен с управляющим входом узла 11 памяти и первым информацио ным входом сумматора 12, выход которо. го подключен к первому входу второй схе 574 мы 16 сравнения, второй вход которой lidpKTiioHeH к выходу реверсивного счетчвка 17, а выход, соединенный с пятым выходом первого блока 3 воспровзведення сигнала - к счетным входам реверсивного счетчика 17, первого счетчика 14 и к второму управлАющему входу второго счетчика 15. Выход первой схемы 13 сравнения подключен к управляющему входу сумматора 12. Второй и третий блоки 4 и 5 воспровэведения сигнала содержат узел 11 памяти и сумматор 12. Устройство работает следующим обрааом. Блок 1 записи осуществляет дискретизацию во времени входного сигнала и передачу в блок 2 памяти заданного объема выборки N , причем N - произвоп ное число, не превышающее по величине объем памяти блока 2 памяти. Блоки 3-5 воспроизведения сигнала осуществляют воспроизведение заданной последовательности сигналов из блока 2 памяти и перецачу их на соответствующие входы сумматора 7 и блока 8 умножения. На вход интегратора 9 после каждого цикла воспроизведения поступает сигнал, определяемый в соответствии с выражением e(,) где 2 - номер цикла воспроизведения; j - номер воспроизводимой копии, равныйномеру ординаты оценки корреляционной функции; «в вния сигналов, выбранных блоками 3-5 воспроизведения; f,e,n - текущие значения айресов выбранных сигналов, причем при имеем К 2j+ 1; п - 1;(2; е J+ 1. В интеграторе 9 происходит усреднеие сигнала К.- (z) за время воспроизедения одной копии, т.е. С-коэффициент передачи интегратора 9, который управляется сигналом с пятого выхода блока 3 воспроизведения;N 1- максимальное число циклов при воспроизведении одной копии. .Можно показать, что (З) является оценкой корреляционной функиии. Таким образом, на выходе устройства формируется текущее значение оценки корреляционной функции. В исходном состоянии, т.е. перец начапом воспроизвецения первой копии, в счетчик 14 первого бпока 3 воспроизведе ния (обозначим его содержимое через )), в счетчике 15 (обозначим его содержимое через т), в сумматоре 12 (обозначим его содержимое через к) записан О, т.е. j О; : т О; k О. В реверсивный счетчик 17 (обозначим его содержимое через п ) занесен объем выборки N . При поступпении на вход очередного импупьса в счетчик 15 и сумматор 12 заносится , т.е. 1;,.) . При срабатывании схемы 13 сравнения т.е. пригп ,В| счетчике 15 устанавпИ вается О, а в сумматоре 12 - содержимое счетчика 14. Спедоватепьно, содержимое сумматора 12 при т j изменяется в соответствии с выражением X k+i+l.« Выход сумматора 12 подключен к в то рому входу узпа 11 памяти, на вход 18 которого поступают сигналы из бпока 2 памяти в соответствии с содержимым сум матора 12. По сигналу с генератора 6 импульсов, поступающему на управляющий вход адрес ного регистра, содержимое сумматора 12 являющееся адресом, записывается в узеп 11 памяти, по адресному входу и с выхода передается :из узпа 11 памяти в бпок 2 памяти, из которого в соответствии с этим адресом считывается операнд, по входу записывающийся в узел 11 памяти и выставляемый на выход. в схеме 16 сравнения происходит сра нение содержимого сумматора 12 реверсивного счетчика 17. ПриК п сигнал с выхода узла 16 сравнения поступает на вход счетчика 14 и изменяет его содержимое на +1, на вход счетчика 15, устанавливая его в О, и на вычитающий вход реверсивного счетчика 17, изменяя его содержимое на -1, а также через вы ход бпока 3 воспроизведения - на управляющий вход интегратора. В сумматор 12 при этом из счетчика 14 заносится его удвоенное сх аержимое, т.е. перед началом Воспроизвчпення спеауюшей копии К-2 + 1.Так как выход счегчика 14 и выход схемы 13 сравнения первого бпока 3 воспроизведения сигнала через его выход и подключены соответственно к вторым и третьим входам сумматора 12 (фиг. 2) блоков 4 и 5 воспроизведения, их содержимое изменяется а-налогично согдержимому сумматора 12. Исключение составляет тот факт, что при срабатывании схемы 16 сравнения в сумматор блока 4 воспроизведения сигнала заносится j , в сумматор блока 5 воспроизведения сигнала +1, т.е. е j + 1; h 1. Техническая реализация устройства может быть осуществлена с использованием элементов цифровой вычислительной техники. Бпок 1 записи представляет собой аналого-цифровой преобразователь, блок 2 памяти является запоминающим устройством с перезаписью и может быть выполнен на магнитных сердечниках или полупроводниках. Блок 8 умножения, сумматор 7, генератор 6 импульсов, сумматор 12, схемы 13 и 16 сравнения, счетчики 14, 15 и 17, узел 11 памяти могут быть выполнены на интегральных схемах. В интеграторе 9 предусмотрена возможность регулирования коэффициента передачи по управляющему входу. Реверсивный счетчик 17 работает на вычитание. Объем блока 2 памяти определяется необходимым количеством фиксированных отсчетов .иэи-, руемого стационарного случайного процесса. Разрядность блока 1 записи, блока 2 памяти, блоков 3-5 воспроизведения сигнала, сумматора 7, блока 8 умножения, интегратора 9 определяется исходя из требований к устройству по точности и быстродействию. Использование новых элементов - дополнительного блока сравнения и реверсивного счетчика - делает возможной обработку сигналов с произвольным объемом выборки N в пределах емкости блока памяти, т.е. расширяет функциональные возможности предлагаемого устройства по сравнению с прототипом. Кроме того, отсутствие как во втором, так и в третьем блоках воспроизведения предлагаемого устройства узла сравнения и двух счетчиков, имеющих место в аналогичных .блоках прототипа, и налччче новых связей, упрощает структуру устройства.

//

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1979 |

|

SU832560A1 |

| Функциональный преобразователь угла поворота в цифровой код | 1976 |

|

SU636654A1 |

| Автокоррелятор | 1981 |

|

SU1022167A1 |

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Устройство для определения производной корреляционной функции | 1985 |

|

SU1305713A1 |

| Коррелятор | 1989 |

|

SU1665386A1 |

| Автокоррелятор | 1988 |

|

SU1628066A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1732360A2 |

| Аналого-цифровой коррелятор | 1981 |

|

SU1019462A1 |

ЦИФРОВОЙ КОРРЕЛЯТОР, содержащий бпрк записи, вход которого яепяется входом коррелятора, а выход соединен с входом записи блока памяти, генератор импупьсов, блок суммирования, выход которого соединен с первым входом блока умножения, выход которого подключен к информационному входу интегратора, выход которого является выходом коррелятора, блоки воспроизведения сигнапа, каждый из которых содержит узеп памяти и сумматор, выход которого соединен с адресным входом узла памяти своего блока воспроизведения сигнала, информационный вход узпа памяти каждого блока воспроизведения сигнала соединен с соответствующим выходом группы выходов блока памяти, управляющий вход узла памяти и первый информационный вход сумматора в каждом канапе блока воспроизведения сигнала объединены и подключены к выходу генератора импульсов, а информационный выход узла памяти в каждом бпоке воспроизведения сигнала подключен соответственно к первому и второму входам блока суммировагия и к второму входу блока умножения коррелятора, при этом первый бпок воспроизведения сигнаЪа со держит первую схему сравнения, первый и второй счетчики, выходы которых подключены к соответствующим входам схемы сравнения, а выход первого счетчика дополнительно подключен к второму информа.ционному входу сумматора первого блока воспроизведения сигнала, выход первой схемы сравнения первого блока воспроизведения сигнала подключен к управляющему входу сумматора и первому управляющему входу второго счетчика, второй управляющий вход которого объединен со (Л счетным входом первого счетчика, а счетный вход второго счетчика объединен с первым информационным входом сумматора своего блока, отпичающийс я тем, что, с целью расширения класса решаемых задач, первый бпок воспроизведения сигнала содержит вторую схему сравнения и третий счетчик, выход которого подключен к первому входу второй схемы сравнения, второй вход которой соединен с выходом сумматора своего блока, а выход второй схемы сравнения подключен к счетным входам первого и третьего счетчиков своего блока и к управляющему входу интегратора, выход первой схемы сравнения первого бпока воспроизведения сигнапа соединен с управпяющим входом сумматоров второго и третье о блоков; воспроизведения сигнала, выход первого счетчика первого блока воспроизведения сигнала соединен с вторым информационным входом сумматоров второго и третьего бпоков воспроизведения сигналов.

Т

Фt/f.J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Грибанов Ю.М., Весепова Г.П., Андреев В.Н | |||

| Автоматические цифровые корреляторы | |||

| Энергия, 1971, с | |||

| Прибор для определения всасывающей силы почвы | 1921 |

|

SU138A1 |

| Механический грохот | 1922 |

|

SU41A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ моделирования смерти головного мозга в эксперименте | 2023 |

|

RU2798902C1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1984-02-07—Публикация

1982-02-23—Подача