(54) ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Цифровой коррелятор для обнаружения эхосигналов | 1979 |

|

SU879595A1 |

| Цифровой коррелятор для обнаружения эхо-сигналов | 1980 |

|

SU959091A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Цифровой коррелятор | 1986 |

|

SU1336031A1 |

| Цифровой коррелятор | 1984 |

|

SU1264200A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

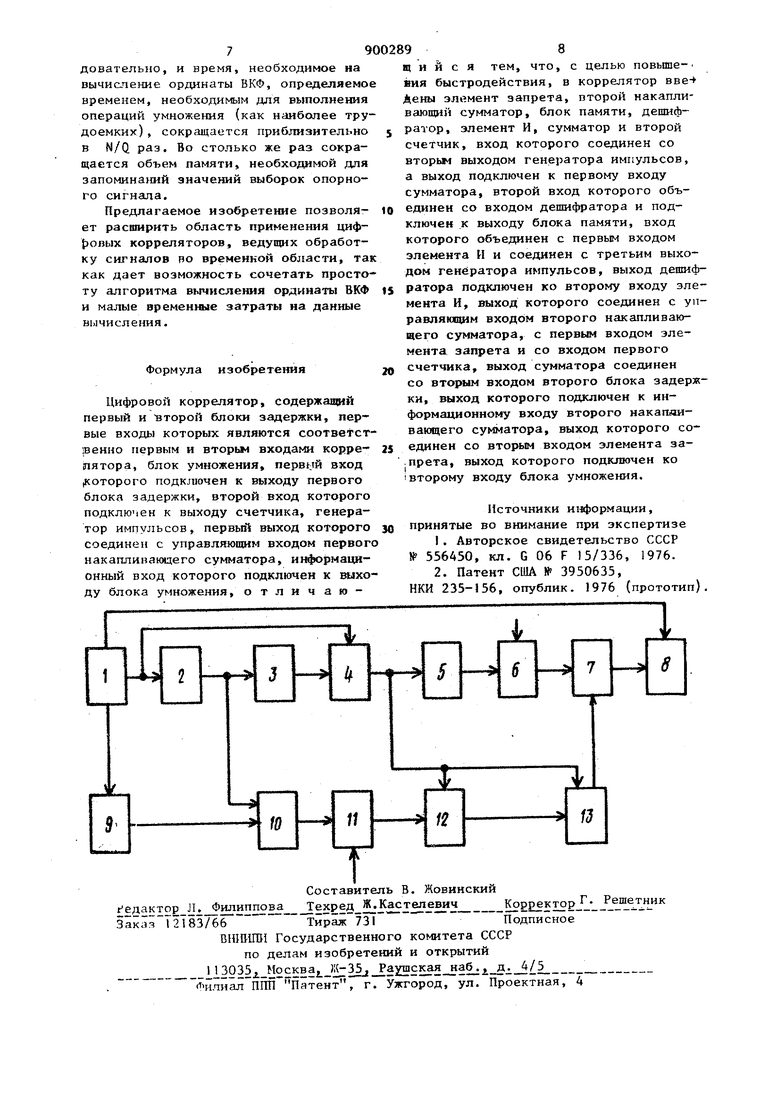

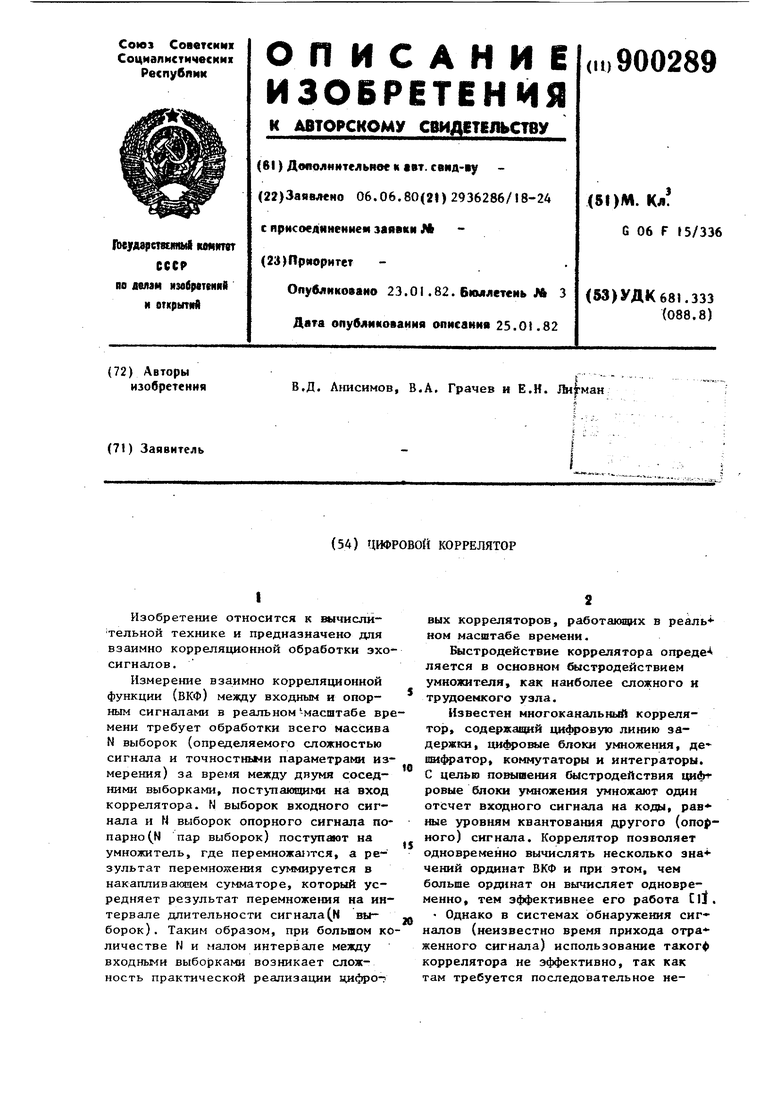

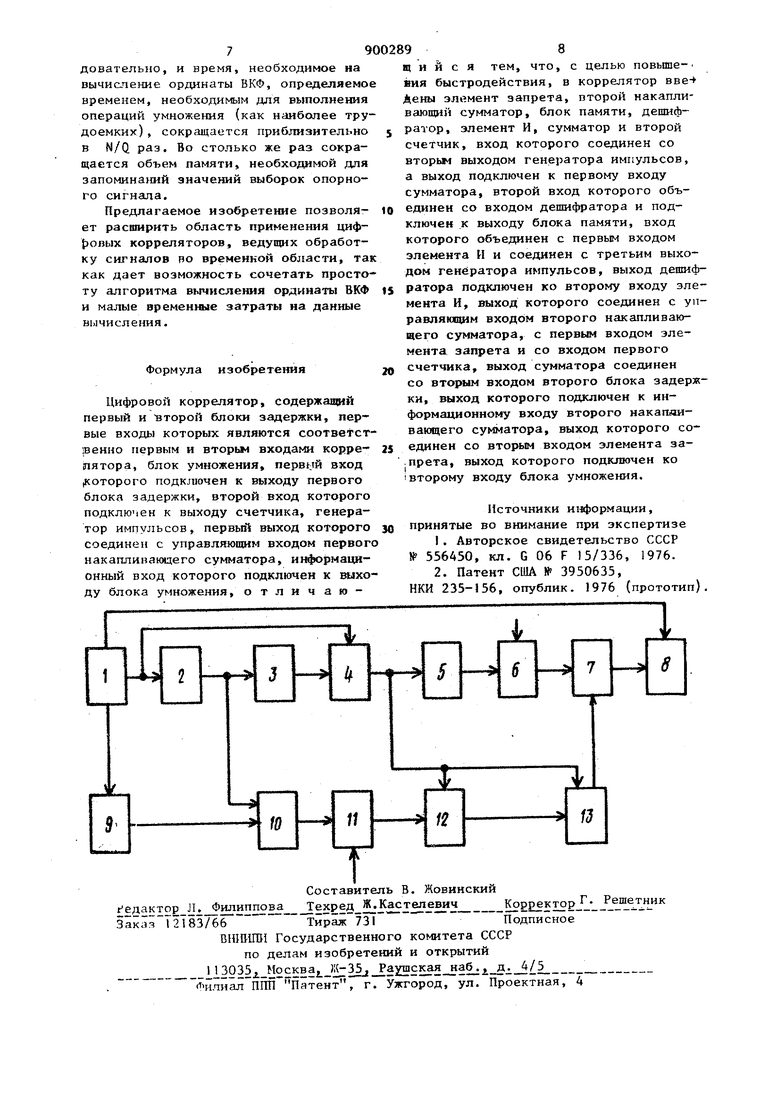

Изобретение относится к вычислительной технике и предназначено для взаимно корреляционной обработки эхо сигналов. Измерение взаимно корреляционной функции (ВКФ) между входным и опорным сигналами в реальном-масштабе вр мени требует обработки всего массива N выборок (определяемого сложностью сигнала и точностньми параметрами из мерения) за время между соседними выборками, пост т1аюцими на вход коррелятора. N выборок входного сигнала и Н выборок опорного сигнала по парно (N пар выборок) поступают на умножитель, где перемножается, а результат перемножения суммируется в накапливакщем сумматоре, который усредняет результат перемножения на интервале длительности сигнала(М выборок) . Таким образом, при большом ко личестве N и малом интервале между входными выборками возникает сложность практической реализации вых корреляторов, работающих в реаль- ном масштабе времени. Быстродействие коррелятора опредв ляется в основном быстродействием умножителя, как наиболее сложного и трудоемкого узла. Известен многоканальпь) коррелятор, содержавши цифровую линию задержки, цидфовые блоки умножения, де ши4фатор, коммутаторы и интеграторы. С целью повышения быстродействия циф ровые блоки умножения умножают один отсчет входного сигнала на коды, рав ные уровням квантования другого (опорного) сигнала. Коррелятор позволяет одновременно вычислять несколько знв чений ординат ВКФ и при этом, чем больше ординат он вычисляет одновременно, тем эффективнее его работа См. Однако в системах обнаружения сигналов (неизвестно время прихода отра женного сигнала) использование таког коррелятора не эффективно, так как там требуется последовательное не39002прерывное вычисление ординат ВКФ, соответствующих определенным моментам времени. Использование одного канала такого коррелятора сводит на нет его Преимущества и приводит к из&лточнос- $ ти аппаратуры. Наиболее близким по технической сущности к предлагаемому изобретению является цифровой коррелятор, содержащий два цифровых устройства з адерж- to ки с памятями (УЗП), счетчик, соединенный с адресными входаьш обоих УЗП, умножитель, соединенный входами с выходами обоих--УЗП, накалливаюдщй сумjiaTOp, соединенный входом с выходом , is умножителя, и генератор импульсов (.ГЙ), соединенный со счетчиком, умножителем й накапливающим сумматором С23. Недостатком коррелятора является то, что использование его в трактах 20 обработки сигналов, работаюцщх в реальном масштабе времени, ограничивается быстродействием умножителя (как наиболёе сложного и трудоемкого узла). Параллелизация узла умножения Be-js дет к значительному увеличению аппаратурных затрат, что при большом числе каналов в тракте обработки не всегда приемлемо. Цель изобретения - повышение быстродействия коррелятора при относивельно незначительном увеличении аппаратуры и при неизменной точности вычисления. Поставленная цель достигается тем, что в цифровой коррелятор, содержащей первый и второй блоки задержки, первые входы которых являются соответ ственно первым н вторым вxoдa в коррелятора, блок умножения, первый вход которого подключен к выходу первого блока задержки, второй вход которого подключен к выходу счетчика, генератор импульсов, первый выход которого соединен с управляющим входом первого накапливающего сумматора, информаци онный вход которого подключен к выХоду блока умножения, введены элемент запрета, второй накапливагадай сумматор, блок памяти, дешифратор, элемент И, сумматор и второй с Гетчик, вход которого соединен со вторым выХодом генератора импульсов, а выход подключен к первому входу сумматора, бторой вход которого объеда1нен со вхо-55 дом дешифратора и подключен к выходу блока памяти, вход которого объединен с первым входом элемента Н и соеди94ней с третьим выходом генератора импульсов, выход дешифратора подключен ко второму входу элемента И, выход которого соединен с управляющим вхоДом второго накапливающего сумматора, с первым входом элемента запрета и со входом первого счетчика, выход сумматора соединен со вторым входом второго блока задержки, выход которого подключен к информационному входу второго накапливающего сумматора, выход которого соединен со вторым входом элемента запрета, выход которого подключен ко второму входу блока умножения, Сущность изобретения заключается в группировании выборок входного сигнала в каждом цикле вычисления ордикаты ВКФ по принципу равенства значаНИИ, соответствующих им в данном цикле выборок опорного сигнала с последукяцим суммированием значений выборок в пределах групп и умножения результатов суммирования с соответствующим группе значением выборки опорного сигнала. Погрешность измерения ординаты ВКФ остается неизменной, что обусловлено свойствами коммутативности и дистрибутивности аргументов функцииН-1 Rxu тг V I 0 .„ которая определяет алгоритмы вычисления ординаты ВКФ. В опорном сигнале обязательно будут встречаться равные по значению выборки, если N , где q - разрядность хода опорной выборки. При обработке сложных сигналов, когда N достигает нескольких тысяч, а q не превышает 4-8, количество групп ограничивается сверху величиной 2, а время необходимое на вычисление одной ординаты, сокращается приблизительно в N/2 раз за счет уменьшения времени, необходимого для выполнения операций умножения. На чертеже представлена структурная схема предлагаемого устройства, Коррелятор содержит последовательно соединенные генератор 1 импульсов, блок 2 памяти, дешифратор 3, элемент И 4, первый счетчик 5, первый блок 6 задержки, блок 7. умножения и первый накапливающий сумматор 8, а также последовательно соединенные второй счетчик 9, сумматор 10, вто590рой блок I1 задержки, второй накапли вающий сумматор 12 и элемент 13 запрета. Выход элемента И 4 соединен с управлякидим входом второго накапливающего сумматора 12 и с управляющим входом элемента I3 запрета, выход которого соединен со вторым входом блока 7 умножения. Второй выход генератора I соединен со входом второго счетчика 9, третий выход генератора соединен с yпpaвляюн9 м входом первого накапливающего сумматора 8, выход блока 2 памяти дополнительно соединен со BTopbW входом су«Ф1атора 10 первый выход генератора 1 импульсов дополнительно соединен со вторьи вхо дом элемента И 4. Цифровой коррелятор работает следующим образом. Выборки входного сигнала последовательно поступают в память блока i} задержки, где каждая выборка хранится в течет1е М циклов, а затем заменяется новой, виовь поступившей. Таким образом, в памяти хранится N текущих значений выборок входного си ала. В паузе между моментами поступ ления в память блока II задержки дву соседних шаборок входного сигнала ос ществляется групповой опрос всех N/ ячеек памяти блока И задержки (память с произвольным доступом) при по мощи сче1чика 9, блока 2 памяти и сумматора 10. Ячейки опра1ш{ваются группами, которые формируются по npH ципу равенства зиачений соответствукщих им выборок опорного сигнала, т.е. в группе объединяются те выборки входного сигнала, которые в данном цикле умножаются на равные по значению выборки опорного сигнала. В блоке 2 памяти хранятся N начал ных кодов адресов ячеек памяти блока II, объединенных по группам и Q-1 кодов Окончания формирования группы, разделяюВ91Х группы. Счетчик 9 формирует код, соответствующий номеру цикла вычислегачя иа сумматоре 10, текущий номер цикла и начальный код суммируются по модулю N, а результат су в«1рования определяет адрес ячейки опроса. Таким образом, записав в блок 2 памяти по группам началыаш кода адресов (соответствующие формировш1ию групп адресов для нулевого цикла вычисления ординаты) и, суммируя с иим теку1да1Й номер цикла, осуществляется формирова9ние адресов ячеек памяти, как и самом цикле, так и от цикла к циклу. С выхода блока I I задержки значения выборок, храня1циеся в опрошенгелх ячейках памяти, последовательно поступают во второй накашшвакжий сумматор 12, где они в пределах своих групп суммируются. В момент, соответствующий окончанию формирования группы, с бло ка 2 памяти поступает на дешифратор S ... код Оконча ше формирования группы. Девюфратор 3 выдает разрешающий потенциал на элемент И 4, через который импульс с генератора 1 проходит на вход счетчика 5, на управляющий вход элемента 13 запрета и на вход Уст. в О накаштивакицего суьдаатора 2. Элемент 13 запрета по данному и.- гпульсу транслирует результат суммирования с накашшвакщего сумматора I на вход блока 7 умножения. В блоке 6 задержки хранятся Q 2 значений выборок опорного сигнала, каяодому из которых соответствует определенная группа входных выборок. Каждая из Q значений выборок умножается в блоке 7 на сумму значений входных выборок в пределах группы. Счетчик 5 последова тельно по каждому импульсу, поступающему с выхода элемента И 4, соотретствующего окончанию формирования группы выборок и сумьадровання в пределах данной группы, формирует код адреса ячейки памяти блока 6. Значение выборки опорного сигнала осуществляет Q операций умножения. Накапливакнций cywiaTop 8 осуществляет суммирование и усреднение результатов умножения. На первом выходе генератора 1 импульсов фop едpyeтcя N ((V-1) импульсов, синхронизирующих работу элемента И 4 и осуществляющих считывание с блока 2 памяти, на втором.выходе г нератора 1 импульсов фо| 1Ируется импульс, задана(Ий код счетчика 9, соответствуманй иомеру цикла вычисления, на третьем выходе генератора I руется импульс, осуществлякя й после вычисления очередной ординаты ВКФ очиение иакаштвающёго сумматора 8. В предлагаемом устройстве в каждом цикле вьршсления ВКФ количество операций умножения на блоке 7 умножения равно Q вместо N операций умножения в известном устройстве, т.е. на каждом цикле время, необхода1мое на операции умножения, сокращается в N/Q раз.Сле дователыю, и время, необходимое на вычисление ординаты ВКФ, определяемо временем, необходимым для выполнения операций умножения (как наиболее тру доемких) , сокращается нриблизительно в N/Q раз. Во столько же раз сокращается объем памяти, необходимой для запоминаний значений выборок опорного сигнала. Предлагаемое изобретение позволяет расширить область применения цифt) корреляторов, ведущих обработку сигналов ро временкой области, та как дает возможность сочетать просто ту алгоритма вычисления ординаты ВКФ и малые аременшле затраты на данные вычисления. Формула изобретения Цифровой коррелятор, содержаао{й первый и второй блокн задержки, нервые входы которых являются соответст венио первым и вторыи входами коррелятора, блок умножения первнй вход |Которого подключен к выходу первого блока задержки, второй вход которого подключен к выходу счетчика, генератор импульсов, nepsbrii выход которого соединен с управляющим входом первого накаплинаюцего сумматора, И1 ормационный вход которого подключен к выходу блока умножения, отличаю9щийся тем, что, с целью повьше-. ВИЯ быстродействия, в коррелятор вве- Дены элемент запрета, второй накапливающий сумматор, блок памяти, дешифратор, элемент И, сумматор и второй счетчик, вход которого соединен со втopь f выходом генератора импульсов, а выход подключен к первому входу сумматора, второй вход которого объединен со входом дешифратора и подключен к выходу блока памяти, вход которого объединен с первым входом элемента И и соединен с третьим выходом генератора импульсов, выход дешифратора подключен ко второму входу элемента И, выход которого соединен с управлякщим входом второго накапливающего сумматора, с первым входом элемента запрета и со входом первого счетчика, выход сумматора соединен со BTOjHJM входом второго блока задержки, выход которого подключен к информационному входу второго накапяиваняцего сумматора, выход которого соединен со вторым входом элемента заПрета, выход которого подключен ко второму входу блока умножения. Источники И1а1 ормации, принятые во внимание при экспертизе . Авторское свидетельство СССР № 556450, кл. G 06 F 15/336, 1976. 2. Патент США № 3950635, НКИ 235-156, опублик. 1976 (прототип).

Авторы

Даты

1982-01-23—Публикация

1980-06-06—Подача