1

изобретение относится к измерению характеристик случайных процессов и предназначено для оперативного определения корреляционной функции текущего стационарного случайного процесса.

известен цифровой коррелятор, содержащий квантователи по уровню, на входы которых из блока памяти поступают сдвинутые на время задержки сигналы. Квантованные по уровню сигналы поступают через блок виборки во времени на блок умножения и далее на накапливакщий счетчик l.

Недостаток устройства - малое быстродействие.

Наиболее близким к предлагаемому является автокоррелятор, содержащий блок памяти, вход которого через блок записи подключен ко входу устройства, выходы блока памяти подключены к первым входам первого и второго блоков воспроизведения, ко вторым входам которых подключен параллельно выход генератора импульсов, первый выход первого блока воспроизведения сигнала подключен последовательно к третьему входу второго блока воспроизведения, к одному из входов блока умножения, входу интегратора и выходу устройства, ко второму входу блока умножения подключен второй выход первого блока воспроизведения 21.

Недостаток устройства - малое бы- . стродействие.

Цель изобретения - увеличение быстродействия цифрового коррелятора.

Поставленная цель достигается, тем,

0 что в цифровой коррелятор, содержащий блок записи, вход которого является входом устройства, а выход подключен ко входу блока памяти, первый и второй выходы которого подключены

5 к первым входам соответственно первого и второго блоков воспроизведения сигнала, вторые входы которых подключены к выходу генератора импульсов, выход первого блока воспроиз0ведения сигнала подключен к третьему входу второго блока воспроизведения сигнала Гк управляяцему входу интегратора, выход второго блока воспроизведения сигнала соединен с первым входом бло5 выход второго блока воспроизведения сигнала соединен с первым входом блока умножения, введены сумматор и третий блок воспроизведения сигнала, три входа которого подключены соответ0/ственно к Третьему выходу блока памяти, к выходу генератора импульсов и к первому выходу первого блока воспроизведения сигнала, входы сумматора соединены соответственно со вторым выходом nejBoro и с выходом третьего блоков воспроизведения сигнала выход сумматора подключен ко второму входу блока умножения, выход которого .соединен с информационные входом интегратора.

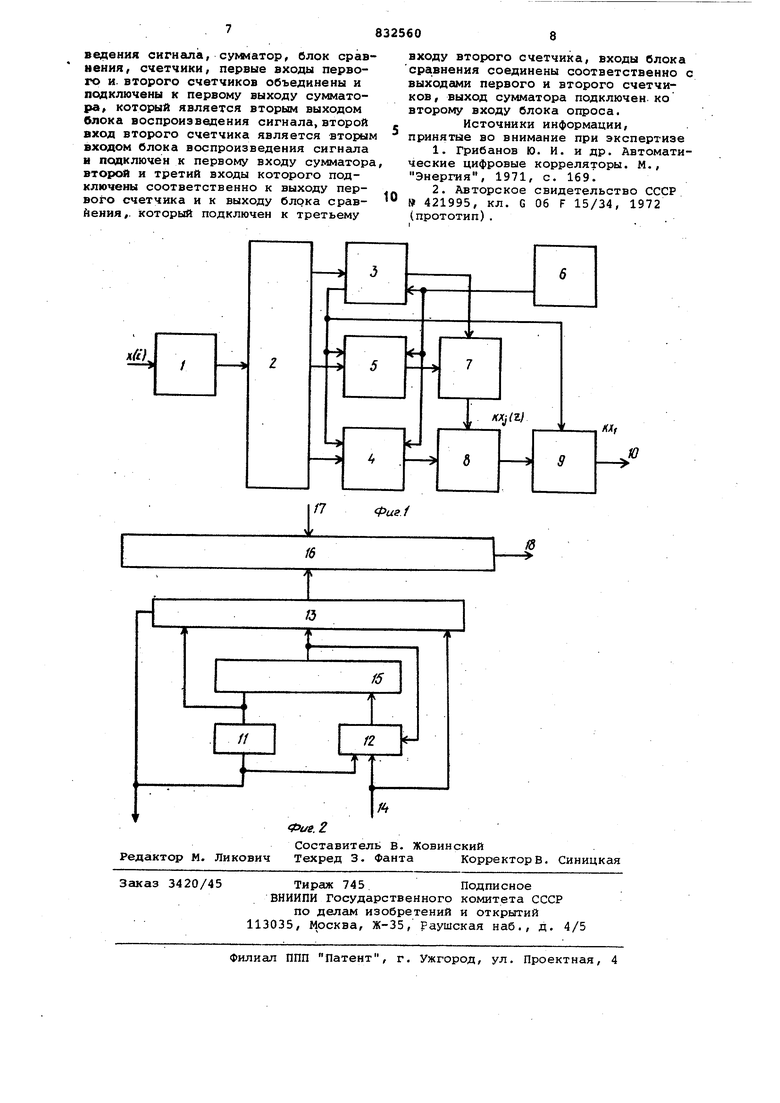

Кроме того, блок воспроизведения сигнала содержит блок опроса, первый вход которого является первым входом блока воспроизведения сигнала, а выход блока опроса является первым выходом блока воспроизведения сигнала, сумматор, блок сравнения, счет.чики, первые входы первого и второго счетчиков объединены и подключены к первому выходу сумматора, которьй является вторымвыходе блока воспроизведения сигнала, второй вход второго счетчика является вторым входом блока воспроизведения сигнала и подключен к первому входу сумматора, второй и третий входы которого подключены соответственно к выходу первого счетчика и к выходу блока сравнения, который подключен к третьему входу второго счетчика, входы блока сравнения соединены соответственно с выходами первого и второго счетчиков, выход сумматора подключен ко втрому входу блока Опроса.

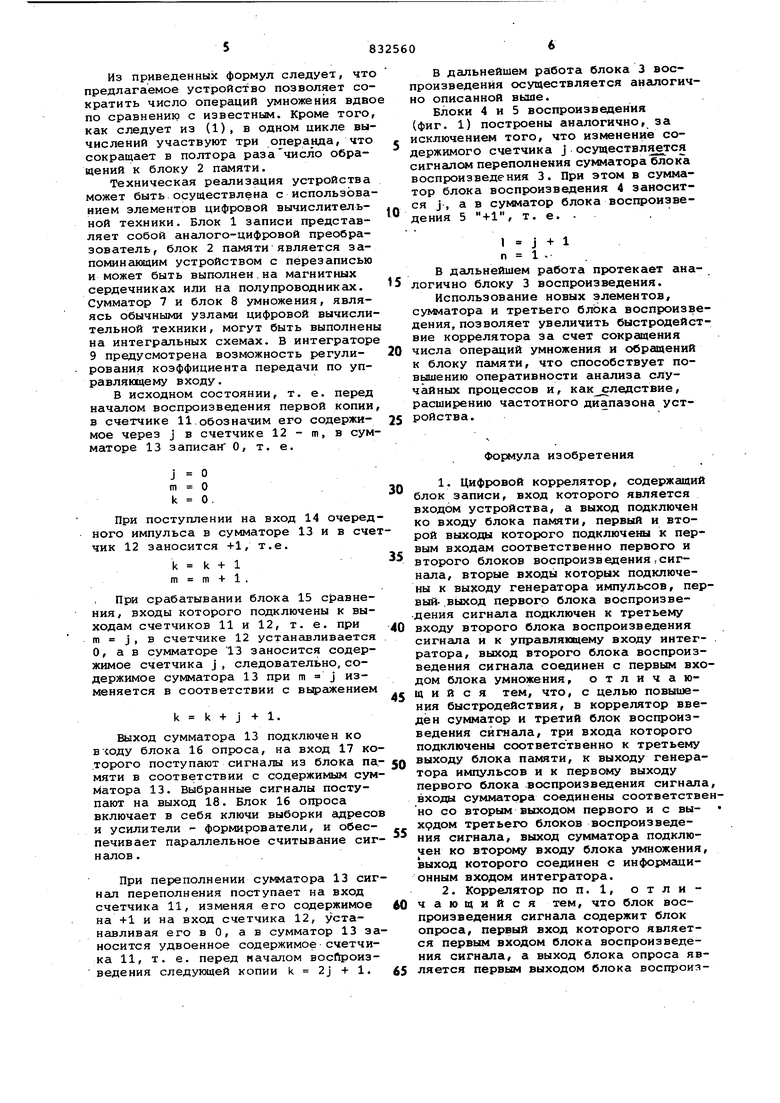

На фиг. 1 представлена структурная схема цифрового коррелятора; на фиг. 2 - структурная электрическая схема блока воспроизведения сигнала.

Входом устройства является вход блока 1 записи, выход которого подключен ко входу блока 2 памяти,.выходы которого подключены к первым входам блоков 3-5 воспроизведения сигналов, ко вторьм входам которых подключен параллельно выход генератора б импульсов. Второй выход блока 3 воспроизведения подключен к первому входу сумматора 7. Ко второму входу сумматора 7 и входу блока 8 умножения подключены выходы, соответственно,блоков 5 и 4 воспроизведения. Второй вход блока 8 соединен с выходами сумматора 7. Первый выход первого блока 3 воспроизведения подключен параллельно к третьим входам блоков 4 и 5 воспроизведения и к управляйвдему входу интегратора 9, вьоход 10 которого является выходом устройства.

Цифровой коррелятор работает следующим образом.

Блок 1 записи осуществляет дискретизацию во времени входного сигнала и передачу в блок 2 памяти заданного объема выборки. Максимальный объем выборки определяется емкостью блока 2 памяти. Блоки 3-5 воспроизведения осуществляют воспроизведение в заданной последовательности сигналов из

блока 2 памяти и передачу их на соответствующие входы сумматора 7-и блока 8 умножения. Обозначим текущие значения адресов сигналов выбранных блоками 3-5 воспроизведения сигнала соответственно k, I, п. С учетом принятых обозначений сигнал, поступающий на вход интегратора 9, после каждого цикла воспроизведения определяется в соответствии с выражением

kx (z) X j (х + х) ,

(1)

деZ

номер цикла воспроизведения копии;

j

номер воспроизводимой копии, равный номеру ординаты оценки корреляционной функции;

значения сигналов выбран е ных блоками воспроизведения 3, 4 и 5;

k, ) , п текущие значения адресов выбранных сигналов, причем при z О имеем

k 2J + 1;

(2)

п 1;

1 j + 1.

9 происходит усред(z) за время воспропии, т. е.

У ),

(3)

kx

коэффициент передачи интеггде с - ратора 9, который управляется сигналом с первого выхода блока 3 воспроизведения;

N, максимальное число циклов при воспроизведении одной копии.

Можно показать, что (3) является оценкой корреляционной функции.

После обработки одной выборки реализации в блок 2 памяти -из блока 1 записи заносится.новая выборка, которая обрабатывается аналогично предыдущей, и т. д. Таким образом, на выходе устройства формируется текущее значение оценки корреляционной функции.

При этом число операций умножения М: при определении одной j-й ординаты корреляционной функции равно

N - 3/

а число операций сложения С равно С 2М N - 3j .

При определении оценки корреляционной функции в соответствии с работой известного коррелятора

N - j .

М С N - j. Из приведенных формул следует, что предлагаемое устройство позволяет сократить число операций умножения вдво по сравнению с известным. Кроме того как следует из (1), в одном цикле вычислений участвуют три операнда, что сокращает в полтора разачисло обращений к блоку 2 памяти. Техническая реализация устройства может быть осуществлена с использованием элементов цифровой вычислительной техники. Блок 1 записи представляет собой аналого-цифровой преобразователь, блок 2 Пс1мяти является запоминающим устройством с перезаписью и может быть выполнен.на магнитных сердечниках или на полупроводниках. Сумматор 7 и блок 8 умножения, являясь обычными узлами цифровой вычисли тельной техники, могут быть выполнен на интегральных схемах. В интеграторе 9 предусмотрена возможность регулирования коэффициента передачи по управляющему входу. В исходном состоянии, т. е. перед началом воспроизведения первой копии в счетчике 11 обозначим его содержимое через j в счетчике 12 - т, в сум маторе 13 записан О, т. е. J О m О k 0. При поступлении на вход 14 очеред ного импульса в сумматоре 13 и в сче чик 12 заносится +1, т.е. k k + 1 m m + 1 . При срабатывании блока 15 сравнения, входы которого подключены к выходам счетчиков 11 и 12, т. е. при m j, в счетчике 12 устанавливается О, а в сумматоре 13 заносится содержимое счетчика j, следовательно, содержимое сумматора 13 при m j изменяется в соответствии с вь5 с1жением k k + j + 1. Выход сумматора 13 подключен ко вчоду блока 16 опроса, на вход 17 ко торого поступают сигналы из блока па мяти в соответствии с содержимым сум матора 13. Выбранные сигналы поступают на выход 18. Блок 16 опроса включает в себя ключи выборки адресо и усилители - формирователи, и обеспечивает параллельное считывгшие сиг налов . При переполнении сумматора 13 сиг НсШ переполнения поступает на вход счетчика 11, изменяя его содержимое на +1 и на вход счетчика 12, устанавливая его в О, а в сумматор 13 за носится удвоенное содержимое счетчика 11, т. е. перед началом восйроизведения следующей копии k 2j + 1. В дальнейшем работа блока 3 воспроизведения осуществляется аналогично описанной вьше. Блоки 4 и 5 воспроизведения (фиг. 1) построены аналогично, за исключением того, что изменение содержимого счетчика J осуществляется сигналом переполнения сумматора блока воспроизведения 3. При этом в сумматор блока воспроизведения 4 заносится j, а в сумматор блока воспроизведения 5 +1, т. е. 1 j + 1 п 1 . В дальнейшем работа протекает аналогично блоку 3 воспроизведения. Использование новых элементов, сумматора и третьего блока воспроизведения, позволяет увеличить быстродействие коррелятора за счет сокращения числа операций умножения и обращений к блоку псИишти, что способствует повышению оперативности анализа случайных процессов и, кaк Jcлeдcтвиe, расширению частотного диапазона устройства. Формула изобретения 1.Циф{ювой коррелятор, содержащий блок записи, вход которого является входом устройства, а выход подключен ко входу блока памяти, первый и второй выходы которого подключены к первым входам соответственно первого и второго блоков воспроизведения,сигнала, вторые входы которых подключены к выходу генератора импульсов, первый- .выход первого блока воспроизведения сигнала подключен к третьему входу второго блока воспроизведения сигнала и к управляющему входу интегратора, выход второго блока воспроизведения сигнала соединен с первым входом блока умножения, отличающийся тем, что, с целью повышения быстродействия, в коррелятор введён сумматор и третий блок воспроизведения сигнала, три входа которого подключены соответственно к третьему выходу блока памяти, к выходу генератора импульсов и к первому выходу первого блока воспроизведения сигнала, входы сумматора соединены соответственно со вторым выходом первого и с вы- хрдом третьего блоков воспроизведения сигнёша, выход сумматора подключен ко второму входу блока умножения, выход которого соединен с информационным входом интегратора. 2.Коррелятор по п. 1, отличающийся тем, что блок воспроизведения сигнала содержит блок опроса, первый вход которого является первым входом блока воспроизведения сигнала, а выход блока опроса является первым выходом блока воспроизведения сигнала, сумыатор, блок сравнения, счетчики, первые входы первого и. второго счетчиков объединены и подключены к первому выходу сумматора который является вторым выходом блока воспроизведения сигнала,второй вход второго счетчика является вторым входом блока воспроизведения сигнала и подключен к первому входу сумматора второй и третий входы которого подключены соответственно к выходу первого счетчика и к выходу блока сравйения,. который подключен к третьему

входу второго счетчика, входы блока сравнения соединены соответственно с выходами первого и второго счетчиков, выход сумматора подключен ко второму входу блока опроса.

Источники информации, принятые во внимание при экспертизе

1.Грибанов Ю. И. и др. Автоматические цифровые корреляторы. М., Энергия, 1971, с. 169.

2.Авторское свидетельство СССР 421995, кл. G Об F 15/34, 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1982 |

|

SU1072057A1 |

| Автокоррелятор | 1988 |

|

SU1628066A1 |

| Цифровой коррелятор | 1979 |

|

SU851412A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Коррелятор | 1982 |

|

SU1042030A1 |

| Цифровой автокоррелятор | 1981 |

|

SU968819A1 |

| Коррелятор | 1987 |

|

SU1444813A1 |

| Цифровой коррелятор | 1980 |

|

SU900289A1 |

| Цифровой коррелятор | 1980 |

|

SU940172A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

Авторы

Даты

1981-05-23—Публикация

1979-07-17—Подача