Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах, к которым предъявляются повышенные требования к достоверности получаемых результатов. Известна дуплексная система вычислительных машин, содержащая блок сравнения результатов, счетчик сбоев, для каждой ЦВМ три группы элемен тов И, блок дополнительных регистров и группу элементов ИЛИ, входы которой через элементы И первой группы соединены соответственно с выходом блока основных регистров ЭВМ второй выход которого через элементы И второй группы подсоединен к вхо ду блока дополнительных регистров, выход которого подсоединен через эле 1ленты И третьей группы к входу блока основных регистров Cl. Недостатком этого устройства является наличие больших аппаратных затрат, что приводит к резкому снижению надежности устройства. Наиболее близким к изобретению по технической сущности является уст ройство для сопряжения двух вычислительных машин, содержащее двенадцать блоков элементовИ, три блока элементов ИЛИ, два дешифратора, два . счетчика сбоев, четыре схемы сравне НИЛ, триггер наличия сбоев, оперативную память, два элемента И-НЕ, элемент ИЛИ и два регистра, причем первый и второй входы устройства через первый и второй блоки элементов И подключены соответственно к. первому и второму входам первого бло ка сравнения, прямой и инверсные вы ходы которого соединены соответствен но с первым входом элемента ИЛИ и с первыми входами элемента И и триг. гера наличия сбоев, первый и второй адресные входы устройства подключены соответственно через третий и четвертый блоки элементов И к первому и второму входам первого блока элементов ИЛИ, выход которого соединен с первым входом оперативной памяти, выход которой соединен с первыми вх f&MK пятого и шестого блоков элемен тов И, а второй вход - с выходом вт iporo блока элементов ИЛИ, входы кот рого соединены соответственно с вых (Дами седьмого и восьмого блоков эле ментов И 23. . Недостаток известного устройства .состоит в больших аппаратурных затратах. Целью изобретения является сокра щение аппаратурных затрат. Поставленная цель достигается тем, что в устройство, содержащее шесть блоков элементов И, два блока сравнения, дешифратор, триггер отсутс вия сбоев, первый элемент И, элемент ИЛИ, первый вход которого соединен с инверсным выходом первого блока сравнения, а выход является выходом наличия сбоя устройства, и счетчик сбоев, выход которого является выходом отказа устройства, причем прямой выход первого блока сравнения соединен с первым входом первого элемента И, а первый и второй входы - соответственно с выходами первого и второго блоков элементов И, первые входы которых являются соответственно первым и вто-. рым входами кодов результата выполнения команды устройства, второй вход первого блока элементов И является первым тактовым входом устройства, первые входы третьего и четвертого блоков элементов И являются соответственно первым и вторым входами адреса результата выполнения команды устройства, группы выходов пятого и шестого блоков элементов И являются соответственно первой и второй группами выходов кодов .результата выполнения команды, введены группа триггеров, два элемента И и два элемента задержки, причем второй вход второго блока элементов И подключен к первому тактовому входу устройства и через первый элемент задержки - к второму вхОдУ первого элемента И, выход которого соединен с первым входом второго элеvEHTa И, выход которого является выходом синхронизации устройства и подключен к первым входам пятого и шестого блоков элементов И, а второй вход соединен с выходом триггера отсутствия сбоев, вторые входы пятого и шестого блоков элементов И соединены с первым входом кода результата выполнения команды устройства, а группы входов - с выходами триггеров группы, первые входы которых подключены к соответствующим выходам дешифратора, а вторые входы - к входу синхронизации устройства к входу, сброса Триггера отсутствия сбоев,, входом установки соединенного с вьг ходом третьего элемента И, перВЕлй вход которого подключен к прямому выходу второго блока сравнения, инверсный выход которого соединен с вторым входом элемента ИЛИ, выходом соединенного с-входом счетчика сбоев, первый и второй входы второго блока сравнения соединены соответственно с выходами третьего и четвертого блоков элементов И вторые входы которых соединены с вторым тактовым входом устройства и через второй элемент задержки - с вторим входом третьего элемента И, вход дешифратора соединен с выходом третьего блока элементов И.

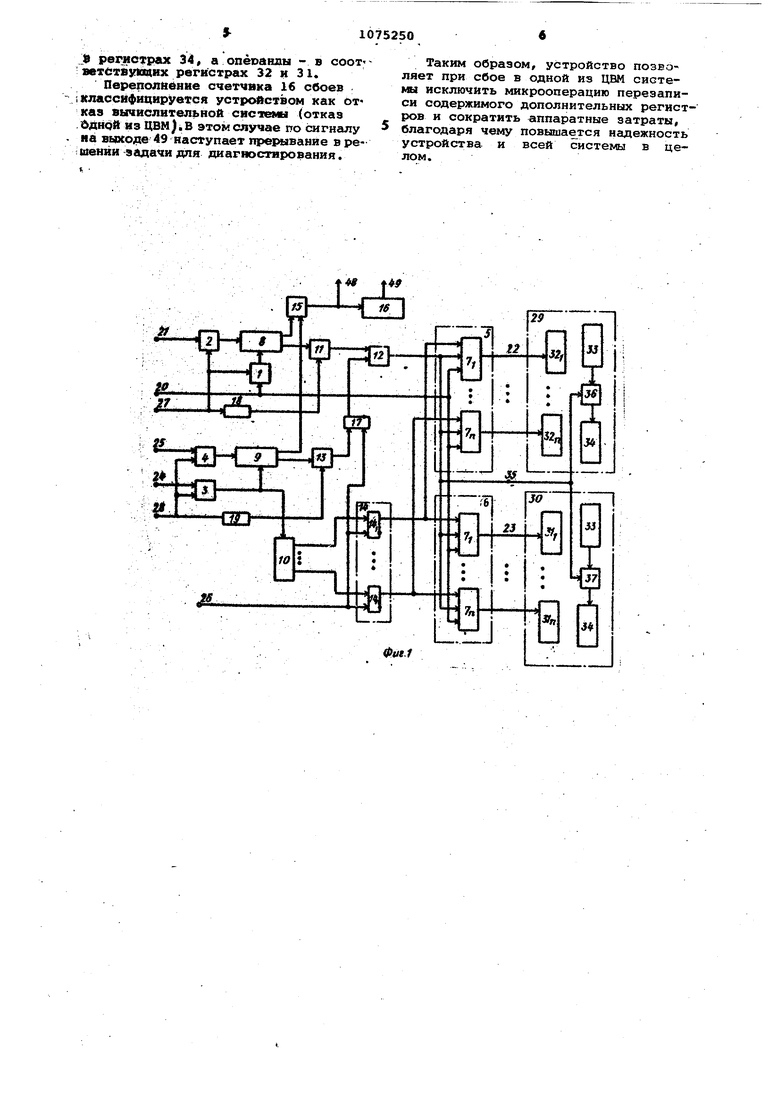

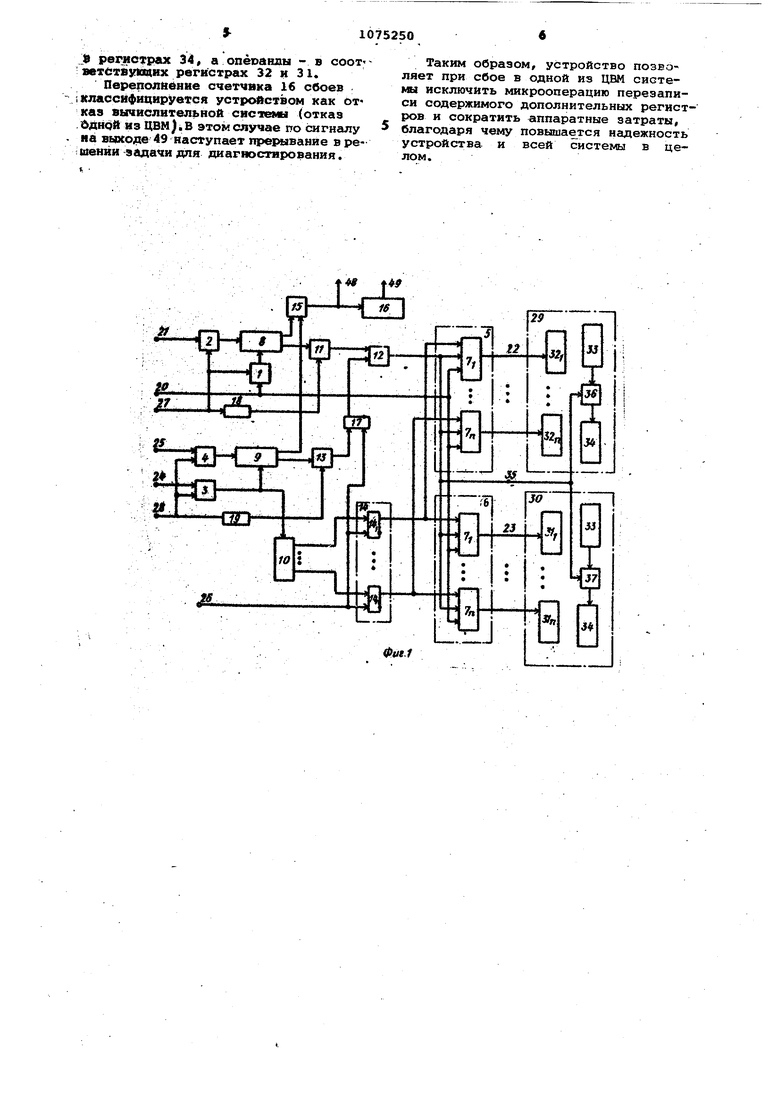

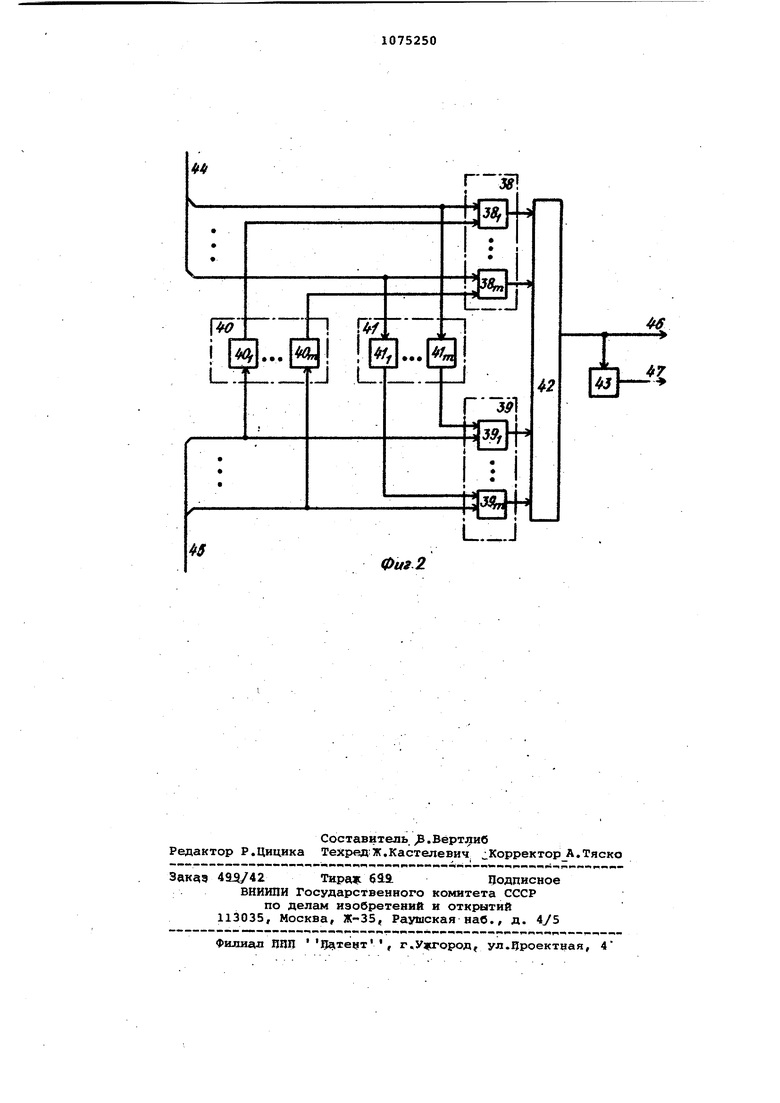

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - функциональная схема блоков сравнения.

Устройство содержит (фиг. 1) блоки 1 - 6 элементов И, группы элементов И 7, вход$щие в состав пятого и шестого блоков 5 и б элементов И, блоки 8 и 9 сравнения,.дешифратор 10 элементы И 11 - 13, триггеры 14 групгы, элемент ИЛИ 15, счетчик 16 сбоев, триггер 17 отсутствия сбоев, элементы задержки 18 и 19, входы 20 и 21 и группы выходов 22 к 23 кодов результата выполнения команды, входы 24 и 25 адреса результата выполнения команды, вход 26 синхронизации и тактовые входы 27 и 28 устройства.

На фиг. 1 показаны ЦВМ 29 и 30, включакяцие регистры 31 и 32 общего назначения (РОН) , регистры 33 и дополнительные регистры 34 слова соетояния программы, выход 35 синхронизации устройства и блоки 36 и 37 элементов И.

Каждый из блоков 8 и 9 сравнения содержит группы элементов И 38 и 39, группы элементов НЕ 40 и 41, эле- . мент ИЛИ 42 и элемент НЕ 43, первый и второй входы 44 и 45 и прямой 46 и инверсный 47 выходы.

На фиг. 1 показаны также выход 48 наличия сбоя и выход 49 отказа.

Устройство работает следующим образом.

В исходном состоянии триггеры 14 и 17 находятся в нулевом состоянии, чго достигается подачей импульса по. входу 26 перед началом выполнения каждой выполняемой команды. Из двух ЦВМ 29 и 30 в устройство по вхо,Дс1М 24 и 25 поступают адреса регистров 32 и 31, в один из которых после выполнения команды должен зано ситься результат. По входам 20 и 21 поступают результаты выполнения команды ЦВМ 29 и ЦВМ 30 соответственно (без записи результатов в регистры 32 и 31).

С приходом тактового импульса на вход 28 в блоке 8 начинается сравнение кодов адресов. Если во всех.разрядах кода адреса РОН ЦВМ 29 и ЦВМ 3 будут одинаковые значения, то на выходах всех элементов И 38 и 39 групп (фиг. 2) будут нулевые потенциалы, на выходе элемента ИЛИ 42 будет также нулевой потенциал, а на выходе элемента НЕ 43 будет единичный потенциал. Сигнал с выхода 47 через элемент И 13 (на второй вход . элемента И 13 подается тактовый нм пульс, задержанный на элементеЗадержки 19)установит триггер 17 в единичное состояние. Кроме того, значение кода адреса РОН ЦВМ 29 с выходов элементов И блока 3 поступает на входы дешифратора (адреса 10 В соответствии с адресом на одном выходе дешифратора 10 появится высокий (единичный) потенциал, который установит соответствующий триггер 14 в единичное состояние. С выхода этого триггера 14 высокий потенциал поступает на входы тех групп 7 элементов И блоков 5 и 6, чфез которые до.пжен записаться результат выполнения команды в згшанные ре..гистры 32 и 31.

Если хотя бы в одном разряде кода адреса РОН значения не одинаковы, то на выходах соответствующих элементов И 38 и 39 будет единичный потенциал. На выходе элемента ИЛИ 42 появится также единичный потенциал, которые через элемент ИЛИ 15 по.ступит на вход счетчика 16 и выход 48 устройства и будет свидетельствовать о наличии сбоя. Сигнал сбоя с выхода 48 поступает в блоки (не показаны обработки прерываний обеих , после чего в них начинает реализовываться микропрограмма повторения сбившейся команды.

После выполнения команды и появления тактового импульса на входе 27 в блок 8 через бЛоки 1 и 2 поступают значения кодов результатов выполнения команды. В блоке 8 происходит сравнение результатов аналогично сравнению кодов адресов РОН в блоке 9. Если коды результатов равны, то на выходе элемента И 11 будет единичный потенциал, который поступает на вход элемента И 12, на другой вход которого поступает единичный потенциал с выхода триггера 17. С Btjхода элемента И 12 единичный потенциал поступает на входы групп элементов И 7 , через которые код результата выполнения команды ЦВМ 29 с входа 20 записывается в соответствующую пару регистров 3 2 и 31, выбранные единичным потенциалом с выхода триггера 14. Кроме того, высокий потенциал с выхода элемента И 12 поступает на входы блоков 36 и 37 и разрешает запись значений регистров 33, слова состояния программы ЦВМ 29 и ЦВМ 30 в дополнительные регистры 34 для хранения в них до получения очередного сигнала о выполнении команды евыхода элемента И 12.

Если хотя бы в одном разряде кода результатов выполнения команд щ}оизойдет несовпадение, то на выходе 4 6 блока 8 появится единичный потенциал, который через элемент ИЛИ 15 поступает на выход 48 устройства и поступает далее в блоки обработки прерываний обеих ЦВМ, которые обеспечивают повторение только одной сбившейся команды. Для этого исходная информация сохранена: номер команды находится

d регистрах 34, a опёоаваы - в COOT: ветбтву1ацих регистрах 32 и 3 1.

Переполнение счетчика 16 сбоев {Классифицируется устрс ством как от

каз вычислительной системы (отказ .йдНой КЗ ЦВМ). В этом случае по сигналу

на выходе 49 наступает прерывание в ре шенйи задачи для диагностирования.

Таким образом, устройство позволяет при сбое в одной из ЦВМ системы исключить микрооперацию перезаписи содержимого дополнительнЕлх регистров и сократить аппаратные затраты, благодаря чему повышае гся надежность устройства и всей системы в целом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения абонентов с ЦВМ | 1990 |

|

SU1777146A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1277123A1 |

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU955019A1 |

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU1035596A2 |

| Устройство для управления дуплексной системой | 1980 |

|

SU900278A1 |

| Преобразователь электрического сигнала в давление жидкости или газа | 1983 |

|

SU1101600A1 |

| Многоканальное устройство для сопряжения абонентов с ЦВМ | 1989 |

|

SU1697081A1 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1987 |

|

SU1432534A1 |

| Устройство для отладки и контроля хода программ | 1988 |

|

SU1529227A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЯЖНИЯ ДВУХМАШИННОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, со1}ержащее шесть блоков элементов И, два блока сравнения, дешифратор, , триггер отсутствия сбоев, первый элемент И, элемент ИЛИ, первый вход . которого соединен с инверснытл ВЕКОдом первого блока сравнения, а выход является выходом наличия сбоя устройства, и счетчик сбоев, ВЕЛХОД которого является выходом отказа устройства, причем прямой выход первого блока сравнения соединен с первым входом первого элемента И, а первый и второй входы - соответственно с выходами первого и второго блоков элементов И, первые входы которых явля ются соответственно первым и вторым входами кодов результата выполнения команды устройства, второй вход первого блоки элементов И является первым тактовым входом устройства, пергвые входы третьего и четвертого блоков элементов И являются соответственно первым и вторым входами адреса результата выполнения команды устройства, группы выходов пятого и шестого блоков элементов И являют(Ся соответственно первой и второй группами выходов кодов результата . выполнения команды, о тличающ е е с я тем, что, с целью сокращения аппаратурных затрат, в устройство введены группа триггеров, два элемента И и два элемента задержки, причем второй вход второго блока элементов И подключен к первому тактовому входу устройства и через первый элемент задержки - к второму входу первого элемента И, выход которого соединен с первым входом второго элемента И, выход которого является выходом синхронизации устройства и подключен к первБм входам пятого и шестого блоков элементов И, а второй вход соединен с выходом триггера-отсутствия Сбоев, вторые входы пятого и шестого ., блоков элементов И соединены с пер- g вым входом кода результата выполненйя команды устройства, а группы |Дов - с выходами триггеров группы, iпервые входы которых подключены к j соответствующим выходам дешифратора, :а вторые входы - к входу синхрониза- g ции устройства и входу сброса триггера отсутствия сбоев, входом уста:новки соединенного с выходом третьего элемента И первый вход которого подключен к прямому вьаходу второго сл ISD сл блока сравнения, инверсный выход I которого соединен с вторым входом , элемента ИЛИ, .выходом соединенного с входом счетчика сбоев, первый и .второй входы второго блока сравнения соединены соответственно с выходами третьего и четвертого блоков элементов И, вторые входы которых соединены с.вторым тактовым входом устройст-j :Ва и через второй элемент задержки вторым входом третьего элемента И, вход дешифратора соединен с выходом Jтретьего блока элементов И.

р :г п ffflr™ J LL . .:.,) ,- 1 Ф1Я.1 ТТЛ П1 :

г

ЁН

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дуплексная система вычислительных машин | 1977 |

|

SU752343A1 |

| G, 06 F 11/00, 1977 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3345003/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-23—Публикация

1982-12-10—Подача