со ел

СП

d:

Изобретение относится к вычислительной технике, и может быть использовано для сопряжения двух ЭВМ в вычислительных системах.

По основному авт. св. № 955019 известно устройство, содержащее первый и второй блоки элементов И, первыми и вторыми входами подключенные соответственно к первым и вторым управляющим и разрешающим входам устройства, а выходами - соответственно к первым и вторым входам первой схемы сравнения, третий и четвертый блоки элементов И, первые;входы которых соединены соответственно с адресными входами устройства, вторые входы - соответственно с первым и вторым выходами первого дешифратора, а выходы - соответственно с первым и вторым входами первого блока элементов ИЛИ, выходом подключенного к адресному входу оперативной памяти, выход которой соединен с информационными входами пятого и шестого блоков элементов И, вторые управлянлцие входы и выходы которых соединены соответственно с первыми и вторыми входами считывания устройства и информационными выходами устройства, а первые управляющие входы - соответственно с выходами первого и второго элементов Jm. первыми входами соединенных соответственно с первым и вторым входами запроса устройства, а вторыми входами - соответственно с вторым и первым выходами перво.го дешифратора, первый и второй вхды которого подключены соответственно к первому и.второму входам запроса устройства, а первый и второй Выходы - соответственно к вторым управлякадим входам седьмого и восьмого блоков элементов И, информационные и первые управляющие входы которых соединены соответственно с первыми и вторыми информационными входами и входами записи устройства, а выходы - соответственно с первым и вторым входами второго блока элементов ИЛИ, выходом подключенного к информационному входу оперативной памяти, первый выход первой схемы сравнения соединен с первыми входами элемента И, триггера наличия сбоя и второго дешифратора, а второй выход с первым входом элемента ИЛИ, вторым входом подключенного к инверсному выходу триггера режима работы а выходом - к выходу режима устройства, вход триггера режима работы соединен р входом режима устройств а прямой выход - с вторым входом элемента И, выход которого являетс выходом прерывания устройства, первые и вторые входы девятого- и десятого блоков элементов И соединены соответственно с первым и вторым входами разрешения устройства И первыми входами в.торой и третьей схемы сравнения, выходом триггера :наличия: сбоя и третьими входами второй и третьей схем сравнения, а выходы - соответственно через первый и второй регистры с вторыми входами второй и третьей схем сравнения, выходы которых подключены соответственно к второму и третьему входам второгодешифратора и через первый и второй счетчики сбоев к первому и второму выходам отказа устройства, выход второго дешифратора является выходом сигнала сбой устройства Ij

Недостаток этого устройства состоит в низкой надежности двухмашинной системы, так как она не обеспечивает возможность .подключения к выходу вычислительной системы выхода наиболее надежно функционирующей вычислительной машины, т.е. той, которая претерпела наименьшее число сбоев. В известном устройстве такое подключение осуществляется произвольным образом без учета информации о происшедших сбоях.

ЦелыГ изобретения - повышение надежности функционирования двухМсшшнной вычислительной системы за счет подключения к выходу сие- , темы выхода той вычислительной машины, которая к данному моменту времени претерпела минимальное число сбоев.

Поставленная цель достигается тем, что в устройство введены одиннадцатый и двенадцатый блоки элементов И, третий блок элементов ИЛИ и четвертая схема сравнения, причем первый и второй входы четвертой схемы сравнения соединены соответственно с выходами первого и второго счетчиков сбоев, а первый и второй выходы - соответственно с первыми входами одиннадцатого и двенадцатого блоков элементов И, вторые входы которых соединены соответственно с первым и вторым входами разрешения устройства, а выходы - соответственно с первым и вторым входами третьего блока элементов ИЛИ, выход которого является управляющим выходом устройства. I

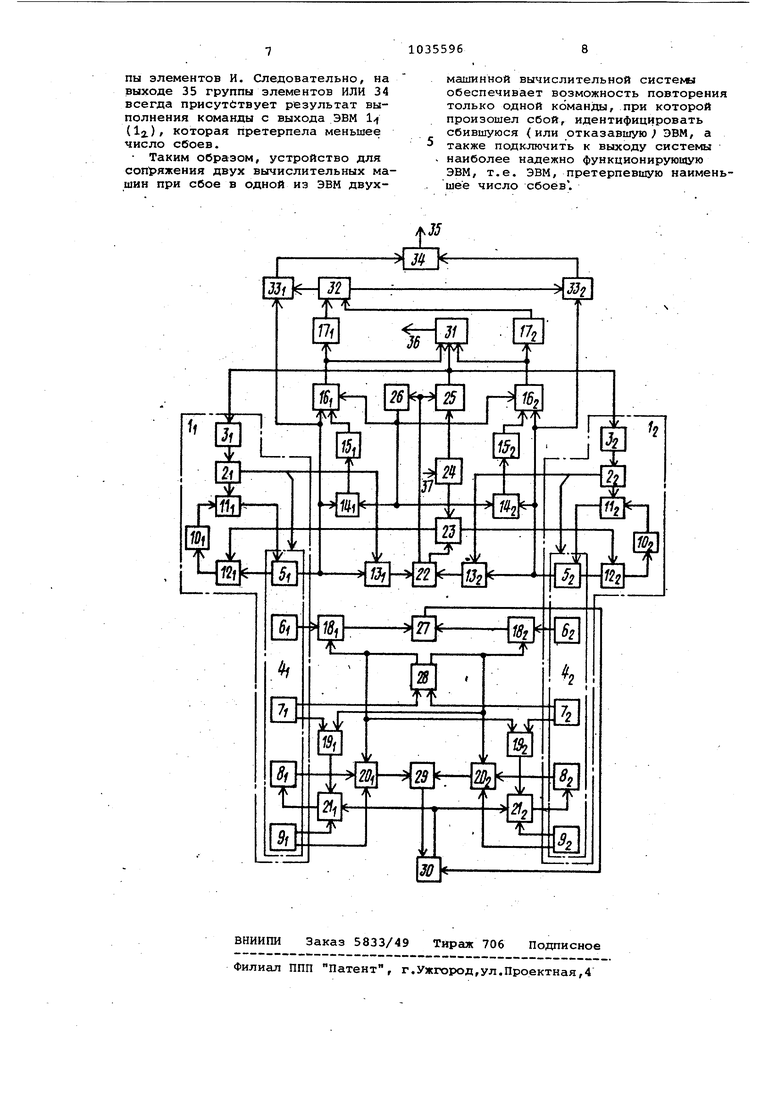

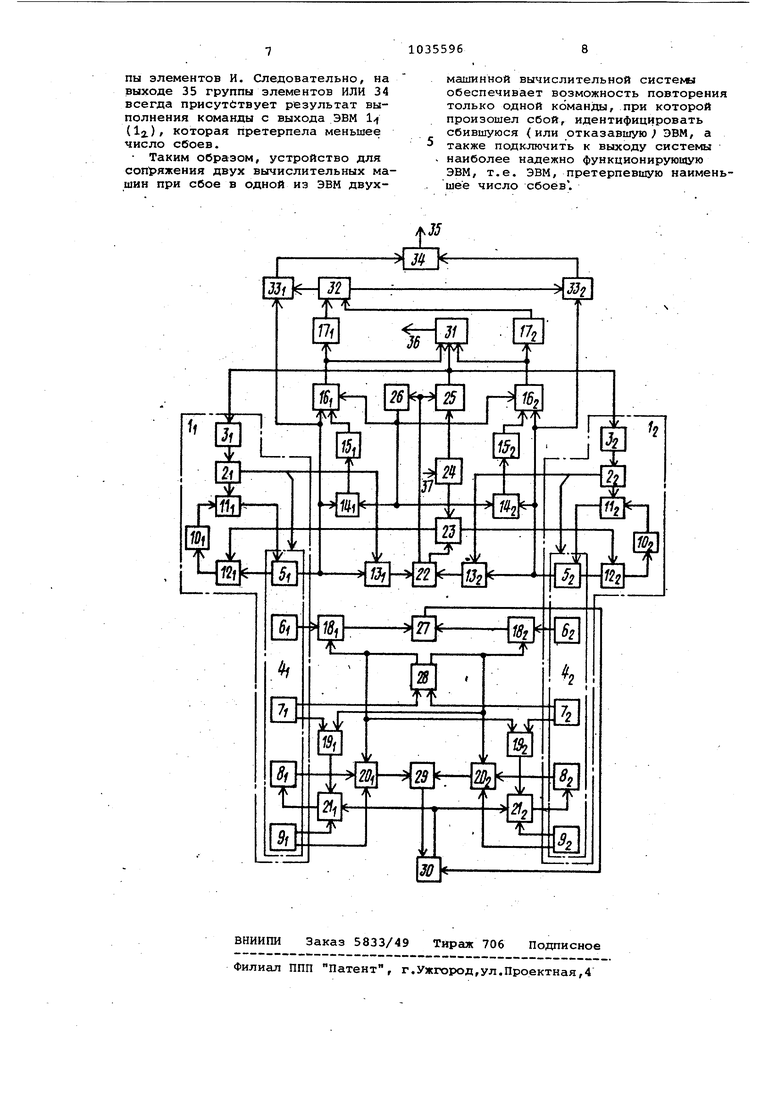

На ,чертеже представлена блоксхема предлагаемого устройства.

Каждая из электронных вычислительных машин (ЭВМ) 1-f и 1. содержит блок 2 управления, блок 3 обработки прерываний, блок 4 регистров в составе регистров 5 общего назначения, регистра б адреса обращений, триггера 7 наличия запроса, информационного регистра 8 и триггера 9 записи-считывания, бло

10дополнительных регистров общего назначения, блоки элементов И

11и 12 (другие блоки ЭВМ, не иллюстрирующие работу -предлагаемого устройства у не показаны, индексы при номерах позиций соответствуют номеру ЭВМ ,

Устройство содержит первый, второй, девятый и десятый блоки элеменг тов и 13 , 132, IV и 142, первый и второй регистры 15 и 15а, вторую и третью схемл le-i и 1б2 сравнения, первый и второй счетчики 17 и 17г сбоев , третий 18 и четвертый 18а блоки элементов И, элементы И-НЕ 19 и 19 j./ седьмой 20, восьмой 20, пятый 21 и шестой 21 г блоки элеме нтов И, первую схему 22 сравнения, элемент ИЛИ 23, триггер 24 режима работы, элемент И 25, триггер 26 наличия сбоя, первый блок 27 элементов ИЛИ, первый дешифратор 28, второй блок 29 элементов ИЛИ, оперативную память ДОП) 30, второй дешифратор 31 , третью схему 32 сравнения, одиннадцатый 33-) и двенадцатый блоки элементов И, третий блок 34 элементов ИЛИ, управляющий выход 35, выход 36 сигнала сбоя устройства и вход 37 задания режима работы устройства.

Особенностью ЭВМ 1 и Ij, система является наличие в них блоков регистров 5 общего назначения, которые обеспечивают вместе с другии блоками выполнение основшлх крм.анд, характерных для современных ЭВМ, например, серии ЕС, команд типа регистр - регистр и регистр память. При выполнении этих команд первый операнд находится на одном из регистров 5, на этом же регистре остается результат вьлполИения команды.

Устройство обеспечивает функционирование дуплексной вычислительной системы в двух основных режимах: в режиме повышенной надежное- ти, при котором обе ЭВМ решают одну и ту же программу, а результаты выполнения команды сравниваются, и в режиме повышенной производительности , при котором каждая ЭВМ выполняет отдельную программу иэ решаемого пакета заданий, в результате чего суммарная производительность вычислительной системы увеличивается вдвое.

Устройство работает следующим образом. .:

В режиме повышенной производительности устройство обеспечивает функционирование системы следующим образом.

В такой режим система переходит при переводе по входу 37 триггера 24 в нулевое состояние с пульта управления системы или по сигналу автомата управления режимами работы дуплексной системы. При этом запрещается прерывание работы ЭВМ по сигналам несравнения в схеме 22 сравнения и обеспечивается.автономная работа ЭВМ, так как на

5 управляемьис входах блоков 12 и 12,z постоянно действует высокий потенциал, поступающий с нулевого выхода триггера 24 через элемент ИЛИ 23. При этом обеспечивается равноправный доступ к РП 30 со стороны каждой ЭВМ.

При необходимости обращения к рП 30 .в-ЭВМ 1 (Ij.) на регистре б-( (6) появляется код адреса обраще5 нйя к ОП, а триггер 7 (7,) наличия запроса перебрасывается в единичное состояние. Высокий потенциал с единичного выхода, триггера 7. (7) поступает на вход дешифратора 28, на котором в этом случае

0

высокий потенциал генерируется только на первом (втором ) выходе, что обеспечивает подачу кода адреса обращения с регистра 6-j б) через блок 18 (18j) и блок 27 на

адресный вход ОП 30. С появлением кода адреса обращения начинается цикл работы ОП 30, при ЭТ9М высокий потенциал с единичного выхода триггера 9 (Э.) при считывании информации поступает на вход .блока 21 {212), на другой/ вход которого подается высокий потенциал с элемента И-НЕ 19 (19), на входы которого поступают низкие потенциалы с нулевого выхода триггера 7

(7) ЭВМ 1 (la), посылающей запрос к ОП, и с второго выхода дешифра.тора 28, Считанная информация поступает на информационный регистр 8

Q (Bj, ) ЭВМ 1 (IT.) через блок 21 (212 При записи ийформации ЭВМ 1., (l) в ОП 30 содержимое информационного регистра 8 (82.) поступает через блок 20 (20,) и блок 29 на информационный вход ОП 30. При этом 4}а первый управляемый вход блока-20 (202.) подается высокий потенциал с нулевого выхода триггера 9 (9), нулевое состояние которого соответствует процедуре записи в ОП 30, а на

0 второй управляющий вход подается высокий потенциал с выхода дешифратора 28. После окончания обращения к ОП ЗХ) содержимое регистров б (6), 8v, (83), триггеров 7 (7)

5 и 9-f (92.) обнуляется.

Конфликтные ситуации, возникающие при одновременном появлении на входе дешифратора 28 запросов от обеих ЭВМ, разрешаются тем, что на выходе дешифратора 28 всегда возбуждается только один выход, например первый, вследствие чего пе редача информации из ОП 30 в ЭВМ 1 или обратно блокируется низким потенциалом с второго выхода дешифратора 28,

В режиме повышенной надежности триггер 24 режима работы находится в единичном состоянии, и система . функционирует следующим образом.

После выполнения каждой команды результат с одного из регистров 5 (52.), в котором записан результат .выполнения команды, подается через блок. 13J 12) на схему 22 сравнения. Сигнал сравнения результатов выполнения команды через элемент ИЛ 23 обеспечивает перезапись содержимого блоков основных регистров 5/1 (52.) через блоки 122 ( ) в бло 10 t (10/2.), и процесс выполнения очередной команды программы продолжается. Сигнал несравнения результатов в схеме 22 сравнения чере открытый элемент И 25 подается в блоки 3 и 3 2. обеих ЭВМ 1 и IT.. По этому сигналу блоки 2 к 2 обес печивают повторение выполнения команды, при которой произошло несравнение результатов, путем выполнения соответствуюшей микропрограммы повторного выполнения команды.

Это происходит следующим образом.

Так как сигнал сравнения с выхода схемы 22 сравнения отсутствует, содержимое блоков 10 и 10 сохраняется прежним, поэтому после подачи управляющего сигнала блоками 2 и 2 на блоки Hi и 122. обеспечивается перезапись содержимого блоков 10 (10) в регистры 5 (5) Такая перезапись обеспечивает возможность повторения команды, при которой произошел сбой.. Oднoвpeмieнно с перезаписью содержимого блоков 10 ( в регистры. 5 (5) осуществляется подача импульса несравнения с выхода схемы 22 сравнения на входы триггера 26 наличия сбоя, который перебрасывается, в единичное состояние, после чего на блоки .14 114) подается разрешающий сигнал, который обеспечивает перезапись результата из регистров 5 (5) в регистры 15,, (15/z). Одновременно содержимое регистра 5 (52. подается на первые входы соответс - вутещих схем 16 (16) сравнения , н другие входы которых подается содержимое регистров 15. (15) с результатами предыдущего выполнения команды и разрешающий высокий потенциал с выхода триггера 26, т.е. этот триггер обеспечивает запись информации в регистры 15.j и через блоки 14 и 14 с задержкой на время выполнения одной команды.

Результаты сравнения с выхода схемы 16 (162) сравнения поступают на соответствующий вход дешифратора 31 и вход счетчика 17 dT-a) единичные сигналы переполнения на выходах которых являются сигналами отказа ЭВМ li (1.). После повтореНИН ранее сбившейся команды может произойти сравнение или несравнение результатов в схеме 22 сравнения. В случае сравнения результатов к содержимому счетчика 17 (если сбой произошел в ЭВМ 1) или .к содержимому счетчика 17,j (если сбой произошел в ЭВМ 1) прибавляется единица. На вход триггера 26 поступает единичный сигнал, который перебрасывает его в нулевое состояние, и вычислительный процесс в дуплексной системе продолжается.

В случае повторного несравнения результатов к содержимому счетчиков 17 или П сбоев также прибавляется единица. Полученные значения результатов выполнениякоманды через блоки 14f и. 144 переписываются на регистры 15 и 15, а триггер 26 находится )вновь в елиничном состоянии, обеспечивая последующую работу схем 16 и 16,i. сравнения. КЕюме того, сигнал несравнения с выхода схемы 22 сравнения поступает на вход дешифратора 31.

Пусть для определенности про.изошел повторный .сбой в ЭВМ 1 тогда сигнал несравнения появляется на выходе схемы 16 сравнения, который поступает на счетчик 17,j и вход дешифратора 31. На другие входы дешифратора 31 поступает низкий потенциал (сигнал сравнения ) и сигнал несравнения с выхода схема 22 с.равнения. Такая комбинация сигнлов 101 на входах дешифратора соответствует сбою (отказу ЭВМ 1,. Аналогично комбинации 011 соответствует сбою (отказу) в ЭВМ 1.. Одновременно сигнал несравнения с выхода схемы (16) поступает на соответствующий счетчик 17. (17,. переполнение которого рассматривается как отказ ЭВМ 1 (l,), которая в последующем отключается из состава системы..

В случае необходимости сигнал на повторение неправильно выполненной команды может подаваться с некоторой задержкой, зависящей от длительности действия случайного сбоя.

Содержимое счетчиков 17 и 17 сбоев поступает на входы схемы 32 сравнения, которая обеспечивает появление высокого потенциала на первом выходе, если содержимое счетчика 17 не больше содержимого счетчика 172, или высоко.го потенциала на втором своем выходе, если содержимое счетчика 17. больше содержимого счетчика 17/2.- Поэтому выский потенциал присутствует только лишь на входе той группы элементов И 33 (ЗЗг) на соответствующем счетчике 17,, (IT) которой хранится минимальный код. В случае равенства кодов на счетчиках 17 высокий потенциал появляется на входе гpyп

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU955019A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

| Устройство для управления дуплексной системой | 1980 |

|

SU900278A1 |

| Устройство для сопряжения двухмашинной вычислительной системы | 1982 |

|

SU1075250A1 |

| Устройство для контроля хода программ | 1990 |

|

SU1737455A2 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1265789A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ : ДВУХ « ЧИСЛИТЕЛЬНЫХ МАШИН по авт. св. 955019, отличающееся тем, что, с целью повышения надежности, в устройство введены одиннадцатый и двенадцатый блоки элементов И, третий блок элементов, Или и четвертая схема сравнения, причем первый и второй вкоды четвертой схемы сравнения соединены соответственно с выходами первого и второго счетчиков сбоев, а первый и второй выходы - соответственно с первыми входами одиннадцатого и двенс(дцатого блоков элементов И, вторые входа которых соединены соответственно с первым и вторым вхо.п дами разрешения устройства, а выходы - соответственно с первым и вторым входами третьего блока элементов ИЛИ, выход которого является управляющим выходом устройства. (Л С

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU955019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-15—Публикация

1981-10-12—Подача