(5) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДУПЛЕКСНОЙ

1

Изобретение относится к вычислительной технике и может быть использовано при разработке высоконадежных адаптивных вычислительных систем с повышенными требованиями к живучести системы и к достоверности получаемых результатов.

Известно устройство сопряжения в вычислительной системе содержащей две подсистемы, причем одна из них работает в режиме с разделением времени,а другая (резервная) г в режиме пакетной обработки. В процессе работы такой системы для каждого пользователя осуществляется приоритетное резервирование устройств связи основной подсистемы с дублирующей to.

Однако эта вычислительная система не обеспечивает в случае сбоя, повторения только сбившейся команды. 6 ней для Ликвидации последствий сбоев необходимо повторить выполнение всей программы или ее части от некоторой СИСТЕМОЙ

контрольной точки, правильность выполнения которой гарантируется.

Известно также устройство сопряжения в вычислительной системе, состоящей из двух вычислительных машин ведущих одновременную обработку данных. В системе осуществляется проверка совпадения сигналов на выходных шинах обеих вычислительных машин 2.

Недостатком этой системы являет10ся то, что ее вычислительные машины не могут функционировать в автономном режиме по реализации различных программ.

Из известных устройств наиболее

15 близким по технической сущности к изобретению является устройство для управления вычислительной системы, содержащее две идентичные вычислитЬльные машины, каждая из которых

20 содержит блок управления, блок обработки прерываний, блок регистров общего назначения, первый и вторые вентильные группы, обеспечивающие

запись информации в Ьлок дополнитель ных регистров из блока основных регистров и наоборот по сигналам с выхода схемы сравнения результатов. Известная вычислительная система позволяет зафиксировать факт несовпадения результатов выполнения команды вычислительными машинами системы и повторить только ту команду, при выполнении которой произошел сбой. При достижении определенного числа сбоев в вычислительной системе фиксируется отказ, который далее локализуется диагностирующими программами ГЗ .

Однако известная вычислительная система не может функционировать в режиме повышенной производительности, в котором каждая машина решает отдельную программу, что бывает крайне необходимым при функционировании системы.

Цель изобретения - повышение производительности и надежности за счет обеспечения возможности функционирования в режиме повышенной производительности, при котором каждая вычислительная машина решает отдельную программу.

Поставленная цель достигается тем, что в устройство для управления дуплек(;ной системой, содержащее счетчик сбоев, схему сравнения, два блока элементов И, первые входы которых соединены с соответствующими выходами контроля вычислительных ма шин, вторые входы первого и второго блоков элементов И соединены с соответствующими выходами разрешения вычислительных машин, выходы первого и второго блоков элементов И соединены соответст-венно с первым и вторым входами схемы сравнения, выход счетчика сбоев подключен ко входам количества сбоев вычислительных машин, дополнительно введены оперативная память, дешифратор, шесть блоков элементов И, два блока элементов ИЛИ, два элемента И-НЕ,элементы И и ИЛИ, триггер режима работы, вход которого является входом задания режима устройства, прямой и инверсный выходы триггера режима работы соединены соответственно х первыми входами элемента И и элемента ИЛИ, выход которого соединен с выходом результата контроля устройства, первый и второй выходы схемы сравнения соединены со вторыми входами соответственно элемента ИЛИ и элемента И, выход которого соединен со входом счетчика сбоев и с выходом прерывания устройства, первый и второй адресные входы устройства соединены ссЗответственно через третий и четвертый блоки элементов И с первым и вторым входами первого блока элементов ИЛИ соответственно, выход которого соединен с адресным входом оперативной памяти, информационный выход которой пятый и шестой блоки элементов И соединен соответственно с информационными входами вычислительных машин, первый и второй информационные входы устройства соединены соответственно через седьмой и восьмой блоки элементов И с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с информационным входом one ративной памяти, первый вход запроса устройства соединен с первыми входами дешифратора и первого элемента И-НЕ, выход которого соединен с первым управляющим входом пятого блока элементов И, второй управляющий аход которого является первым входом записи устройства, второй вход запроса устройства соединен со вторым входом дешифратора и с первым входом второго элемента И-НЕ, выход которого соединен с первым управляющим входом шестого блока элементов И, второй управляющий вход которого является вторым входом записи устройства, первый выход дешифратора соединен с управляющим входом третьего блока элементов И, со вторым входом второго элемента И-НЕ и с первым управляющим входом седьмого блока элементов И, второй управляющий вход которого является первым входом считывания устройства, второй выход дешифратора соединен с управляющим входом четвертого блока элементов И, со вторым входом первого элемента И-НЕ и с первым управляющим -входом восьмого блока элементов И, управляющий вход которого является вторым входом считывания устройства.

В зависимости от состояния три:- гера режима работы реализуется режим повышенной надежности, при котором обе машины системы решают одну и ту же программу, а результаты выполнения каждой команды сравниваются, или режим повышенной производительности, при котором каждая машина системы функционирует автономно и реализует различные программы.

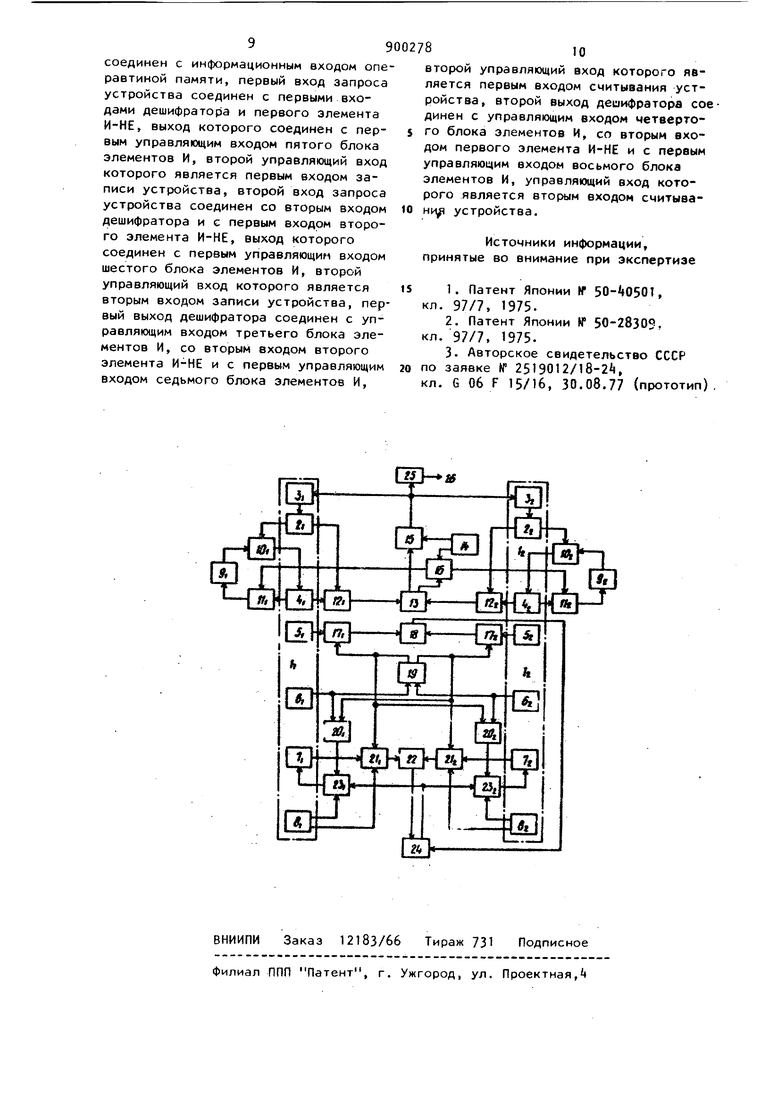

На чертеже представлена блок-схема системы.

Система содержит идентичные вычислительные машины 1 и 1, , представленные блоками управления 2 и 2 , блоками обработки прерываний Зи и Зг блоками основных регистров Ц и 4j, , регистрами адреса обращения 5 и 5д, триггерами наличия запроса 6i и bg , информационными регистрами 7, и 7г и триггерами записи-считывания 8j. Кроме того, вычислительная система содержит блоки дополнительных регистров 9 и Sj, блок элементов MI 10 - 12 и lOj- IZj, схему сравнения 13, триггер режима работы k, элемент И 15 элемент ИЛИ 16, четвертые вентиль-блоки элементов И 17, и 17г . 21, и 2Ц. 23, и 23, блоки элементов ИЛИ 18 и 22, дешифратор 19, элементы И-НЕ 20 и 20j, общую оперативную память 2k, счетчик сбоев 25 и выход 26.

Особенностью вычислительных машин 1J и 1 системы является то, что они содержат блоки регистров общего назначения k и i, , которые обеспечивают вместе с другими блоками вычислительной машины выполнение основных команд, характерных для современ .ых ЭВМ. Это команды типа регистр-регист регистр-память. При выполнении этих команд первый операнд находится на первом регистре блока k на этом же регистре остается и результат выполнения команды.

Вычислительная система может функционировать в двух режимах: режиме повышенной надежности, при котором обе вычислительные машины решают одну и ту же программу, а результаты выполнения команды сравниваются и в режиме повышенной производительности при котором каждая машина выполняет отдельную программу, в результате чего суммарная производительность вычислительной системы увеличивается вдвое.

В режиме повышенной надежности система функционирует следующим образом.

После выполнения каждой команды результат с одного из регистров блока (4) , в котором записан результат и содержимое счетчика команд подается через блоки 12(12г)на схему сравнения 13- В режиме повышенной надежности триггер режима работы 1 находится в единичном состоянии, поэтому на управляемом входе элемента И 15 будет находиться высокий потенциал, а на управляемом входе элемента ИЛИ 16 - низкий.

Сигнал сравнения результатов в схеме 13 подается через элемент 16 на входы вентильных групп 1 Ц и 11 , тем самым обеспечивается перезапись содержимого основных регистров 4 С через блоки 11 CU) блоки дополнительных регистров 9 (9г). Сигнал несравнения результатов в схеме 13 подается через элемент И 15 в блоки обработки прерываний 3 и 3 обеих машин. По этому сигналу блоки управления 2if и 2j обеспечивают повторение команды, при которой произошло несравнение результатов. Это происходит следующим образом. Так как сигнал сравнения с выхода схемы 13 отсутствует, то содержимое регистров блоков Э и 9j сохраняется прежним, поэтому после подачи управляющие го сигнала блоками управления 3 и Зя н соответствующие блоки 10 и tOj обеспечивается перезапись содержимого блоков 9, и 9ji в блоки и 2 при этом к счетчику сбоев 25 прибавляется единица. Такая перезапись обеспечивает возможность повторения команды, при которой произошел сбой. После повторения сбившейся команды может произойти или не произойти сравнение результатов в схеме 13. Переполнение счетчика сбоев классифицируется в системе как отказ в одной из вычислительных машин.

В режим повышенной производительности система переходит при переводе триггера I в нулевое состояние, при этом запрещается прерывание работы вычислительных машин по сигналам несравнения в схеме 13 и обеспечивается автономная работа вычислительных машин,так как на управляемых входах блоков 11 и 11 будет постоянный высокий потенциал, поступающий с нулевого выхода триггера 13 через элемент ИЛИ 1б. Предлагаемая система обеспечивает равноправный доступ к общей оперативной памяти (ООП) со стороны каждой машины и невозможност обращения одной из машин в локальную памят ь другой. Это происходит следующим образом. При необходимости обращения к ООП в вычислительной машине 1,(1)на регистре 5;( (5ji)появляется код адреса обращения к ООП, а триггер 6,, (6 наличия запроса перебрасывается в единичное состояние. Высокий потенциал с единичного выхода триггера 6 (бд)поступает на вход дешифратора 1У, который обеспечивает только на одном из двух выходов появление высокого потенциала, что в свою очередь обеспечивает подачу кода адреса обращения с регистра Si () через блок 17j (l7j)M блок 18 на первый вход ООП . С появлением кода адреса обращения на первом входе ООП начинается цикл работы ООП, при этом высокий потенциал с единичного выхода триггера 8, (8г)при считывании информации поступает на первые входы блока 23(232), на второй вход которого подается низкий потенциал, а с другого выхода дешифратора 19 через элемент И-НЕ 20;,{20г), причем на другой вход элемента 20,( (20)поступает также низкий потенциал с нуле вого выхода триггера 6 (6)вычислительной машины 1, (ij), посылающей запрос к ООП. Считанная информация поступает на информационный регистр Л (i) соответствующей вычислительной маиины через блок 23-( ). При записи информации машиной 1 (lj)B ООП содержимое информационного регистра 7 (.7) поступает через блок 21 (21) и блок 22 на второй вхо ООП. При этом на первый управляемый вход блока (21j) подается , высокий потенциал с нулевого выхода триггера 8 (За) , нулевое состояние котог рого соответствует процедуре записи в ООП, а на второй управляемый вход подается высокий потенциал с соответствующего выхода дешифратора 13. После окончания обращения к ООП, содержания регистров 5 (5г) . У i7i} и триггеров 6(6i), 84(84). Конфликтная ситуация, возникающая при одновременном появлении на входе дешифратора 13 кода 11, разрешается тем, что в этом случае на выходе дешифратора возбуждается только один выход, например первый, а передача информации из ООП 2 в другую машину и обратно блокируется низким потенциалом с другого выхода дешифратора на вход блока высоким потенциалом с первого выхода дешифратора через элемент И-НЕ 20г. 8 Таким образом, вычислительная система может функционировать в режиме повышенной надежности и режиме повышенной производительности. Формула изобретения Устройство для управления дуплексной системой, содержащее счетчик сбоев, схему сравнения, два блока элементов И, первые входы которых соединены с соответствующими выходами контроля вычислительных машин, вторые входы первого и второго блоков элементов И соединены с соответствующими выходами разрешения вычислительных машин, выходы первого и вто рого блоков элементов И соединены соответственно с первым и вторым входами схемы сравнения, выход счетчика сбоев подключен ко входам количества сбоев вычислительных машин, о т л. ичающееся тем, что, с целью повышения производительности и надежности, в устройство введены оперативная память, дешифратор, шесть блоков элементов И, два блока элементов ИЛИ, два элемента И-НЕ, элементы И и ИЛИ, триггер режима работы, вход которого является входом задания режима устройства, прямой и инверсный выходы триггера режима работы соединены соответственно с первыми входами элемента И и элемента ИЛИ, выход которого соединен с выходом результата контроля устройства, первый и второй выходы схемы сравнения соединены со вторыми входами соответственно элемента ИЛИ и элемента И, выход которого срединен со входом счетчика сбоев и с выходом прерывания устройства, первый и второй адресные входы устройства соединены соответственно через третий и четвертый блоки элементов И с первым и вторым входами первого блока элементов ИЛИ соответственно, выход которого соединен с адресным входом оперативной памяти, информационный выход которой через пятый и шестой блоки элементов И соединен соответственно с информаицонными входами вычислительных машин, первый и второй и информационные входы устройства соединены соответственно через седьмой и восьмой блоки элементов И с первым и вторым входами второго блока элементов ИЛИ, выход которого 99 соединен с информационным входом операвтиной памяти, первый вход запроса устройства соединен с первыми входами дешифратора и первого элемента И-НЕ, выход которого соединен с первым управляющим входом пятого блока элементов И, второй управляющий вход которого является первым входом записи устройства, второй вход запроса устройства соединен со вторым входом дешифратора и с первым входом второго элемента И-НЕ, выход которого соединен с первым управляющим входом шестого блока элементов И, второй управляющий вход которого является вторым входом записи устройства, первый выход дешифратора соединен с управляющим входом третьего блока элементов И, со вторым входом второго элемента И-НЕ и с первым управляющим входом седьмого блока элементов И, 8 второй управляющий вход которого является первым входом считывания устройства, второй выход дешифратора соединен с управляющим входом четвертого блока элементов И, со вторым входом первого элемента И-ИЕ и с первым управляющим входом восьмого блока элементов И, управлякйдий вход которого является вторым входом считыван f устройства. Источники информации, принятые во внимание при экспертизе 1.Патент Японии V SO-tOSOI, кл. 97/7, 1975. 2.Патент Японии № 50-2830. кл. 97/7. 1975. 3.Авторское свидетельство СССР по заявке № 2519012/18-2, кл. G 06 F 15/16, 30.08.77 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU955019A1 |

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU1035596A2 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

| Устройство для сопряжения цифровой вычислительной машины с внешними устройствами | 1985 |

|

SU1302288A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ УПРАВЛЯЮЩЕЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1995 |

|

RU2094842C1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения двухмашинной вычислительной системы | 1982 |

|

SU1075250A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

Авторы

Даты

1982-01-23—Публикация

1980-04-09—Подача