(5) УСТРОЙСТВО для СОПРЯЖЕНИЯ ДВУХ . ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух вычислительных машин | 1981 |

|

SU1035596A2 |

| Устройство для управления дуплексной системой | 1980 |

|

SU900278A1 |

| Устройство для сопряжения двух вычислительных машин | 1986 |

|

SU1310832A1 |

| Устройство для сопряжения двухмашинной вычислительной системы | 1982 |

|

SU1075250A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1265789A1 |

| Устройство для фиксации неустойчивых сбоев | 1985 |

|

SU1265777A1 |

| Устройство для отладки программ | 1980 |

|

SU922753A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для тестового контроля цифровых блоков | 1988 |

|

SU1714608A1 |

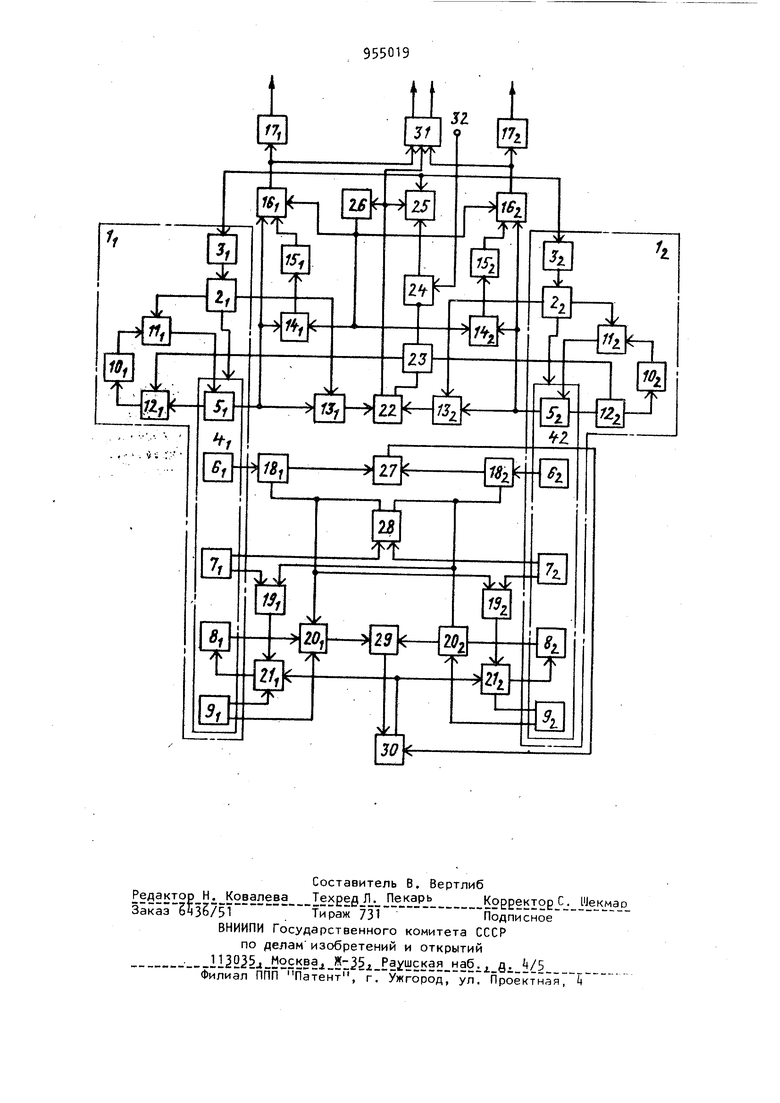

Изобретение относится к вычислительной технике и может быть использовано при разработке высоконадежных адаптивных вычислительных систем с повышенными требованиями к живучести системы и к достоверности получаемых результатов. Известно устройство сопряжения в вычислительной системе, состоящей ИЗ двух вычислительных машин с блоками дополнительных регистров общего назначения и вентильными группами, схемы сравнения и счетчика сбоев. Си тема позволяет повторить только одну сбившуюся команду 11. Недостатком этой системы является то, что ее вычислительные машины не могут функционировать в автономном режиме, а в режиме сравнения результатов при обнаружении сбоя (отказа) в одной из вычислительных машин не идентифицируется сбившаяся (отказавшая) машина. Наиболее близким к предлагаемому является устройство управления дуплексной системой, содержащее схему сравнения, триггер режима работы, элемент И, элемент ИЛИ, два блока элементов ИЛИ, дешифратор, восемь блоков элементов И, два элемента И-НЕ, выходы которых соответственно подсоединены к первым входам первого и второго элементов И, каждый из двух выходов дешифратора подсоединен к первым входам второго и третьего блоков элементов И и к первому входу второго элемента И-НЕ, выходы четвертого и третьего блоков элементов И подсоединены к соответствующим входам первого блока элементов ИЛИ, выходы первого и второго блоков элементов И подсоединены к соответственным входам второго блока элементов ИЛИ, выходы пятого и шестого блоков элементов И подсоединены к соответствующим входам схемы сравнения, первый выход которой подсоединен к первому входу элемента И, а второй выход - к первому входу элемента ИЛИ, второй вход которого подсоединен к первому выходу триггера режима работы, второй выход которого подсоединен к второму входу элемента И 2. Недостатками известного устройства являются ограниченные функциональные возможности. Так оно обеспечивает функционирование системы в режиме повышенной производительности, в котором каждая машина решает отдельную программу, а также в режиме повышенной надежности, при которомкаждая машина решает одну и ту же программу; факт несовпадения результатов выполнемия команды классифицируется как сбрй 1И сбившаяся команда повторяется. Однако при этом для идентификации сбившейся (отказавшей) вычислительной машины необходимо вызJэlвaть систему тестирующих и диагностирующих программ, работа которых требует больших временных затрат. Цель изобретения - расширение функ циоиальных возможностей за счет обеспечения идентификации ситуаций сбоя или отказа. Поставленная цель достигается тем, что в устройство, содержащее первый счетчик сбоев., оперативную память, адресный и информационные входы которой соединены соответственно с выходами первого и второго блоков элементов ИЛИ, схему сравнения результатов, первый и второй входы которой подключены соответственно к выходам первого и второго блоков элементов И, первые и вторые входы которых являются соответственно первым и вторым управляющими входами и первым и вторым входам результата операции устройства, триггер режима работы, вход которого со,единен с входом задания режима устрой ства, а ейиничный и нулевой выходы соответственно с первыми входами элемента И и элемента ИЛИ, вторыми входа ми подключенных соответственно к первому и второму выходам схемы сравнения результатов, а выходами - соответ ственно к выходам прерывания и задания режима работы устройства, первые входы третьего и четвертого блоков эл ментов И соединены соответственно с первым и вторым адресными входами уст ройства, выходы - соответственно с первым и вторым входами первого блока элементов ИЛИ, а вторые входы соответственнЬ с первым и вторым выходами первого дешифратора, первый и второй входы которого подключены соответственно к первому и второму входам запроса устройства и первым входам первого и второго элементов И-НЕ, вторыми входами соединенных соответственно с вторым и первым выходами первого дешифратора, а выходами - соответственно с первыми управляющими входами пятого и шестого блоков элементов И, информационные и вторые управляющие входы которых соединены соответственно с выходом оперативной памяти, соответственно первым и вторым входами считывания устройстра, а выходы являются и первым и втоЬым информационными выходами устройства, первый и второй входы второго блока элементов ИЛИ подключены соответственно к выходам седьмого и восьмого блоков элементов И, информационные и первые управляющие входы которых соединены соответственно с первым и вторым информационными входами устройства и первым и вторым входами записи устройства, а вторые управляющие входы - соответственно с первым и вторым выходами первого дешифратора, введены второй дешифратор, второй счетчик сбоев, две схемы сравнения, два регистра, девятый и десятый блоки элементов И и триггер наличия сбоя, причем первые входы первой, второй схем сравнения и девятого, десятого блоков элементов И соединены соответственно с первым и вторым входами результата устройства, вторые входы с выходом триггера наличия сбоя, выходы девятого и десятого блоков элементов И соединены соответственно через первый и второй регистры с третьими входами первой и второй схем сравнения , выходы которых подключены соответственно к первому и второму входам второго дешифратора и соответстде цо через первый и второй счетчики сбоев - к первому и второму выходам отказа устройства, первый и второй выходы второго дешифратора подключены соответственно к первому и второму выходам сбоя устройства, а третий вход - к входу триггера наличия сбоя первому выходу схемы сравнения результатов. На чертеже представлена блок-схема предлагаемого устройства. Устройство содержит вычислительные машины (ЭВМ) 1-1 и 1, каждая из которых содержит блок 2 управления, блок -3 обработки прерываний, блок Ц регистров Б составе регистров 5 общего назначения, регистр 6 адреса обращений, триггер 7 наличия запроса, информационный регистр 8 и триггер 9 записисчитывания, блок 10 дополнительных регистров общего назначения, блоки элементов И 11 и 12 (другие блоки ЭВМ не иллюстрирующие работу предлагаемого устройства, не показаны, индексы при номерах позиций соответствуют номеру ЭВМ), первый 13-1 второй 13/2, девятый 1 и десятый 14/2. блоки элементов И, первый и второй регистры 15-1 и 15(2. первая и вторая схемы 1б и 1бг2 сравнения, первый и второй счетчики 17-1 1 сбоев, третий 18 и четвертый iBrj блоки элементов И первый и второй элементы И-НЕ 19-1 и 20-1, восьмой 20г1, пя7, седьмой iu-,, 2lQ блоки элементый 21-1 и шестой гов И, схема 22 сравнения результа.тов, элемент ИЛИ 23, триггер 2k режима работы, элемент И 25, триггер 26 наличия сбоя, первый блок элементов ИЛИ 27, первый дешифратор 28, второй блок 29 элементов ИЛИ, оперативную память (ОП) 30, второй дешифратор 31, вход 32 задания режима. Особенностью вычислительных машин 1-, и 11 системы является наличие в них блоков регистров 5 общего назнамения, которые обеспечивают вместе с другими блоками ЭВМ выполнение основных команд, характеристик для современных ЭВМ ЕС. Это команды типа регистр-регистр и регистр-панятв. При выполнении этих команд первый операнд находится на одном из регистров блока 5, на этом же регистре остается и результат выполнени-я команды. Устройство обеспечивает функционирование дуплексной вычислительной системы в двух основных режимах: в ре жиме повышенной надежности, при котором обе ЭВМ решают одну и ту же программу, а результаты выполнения команды сравниваются, и в режиме повышенной производительности, при которо каждая ЭВМ выполняет отдельную nporpa му из решаемого пакета заданий, в результате чего суммарная производитель ность вычислительной системы увеличивается вдвое. Устройство работает .следующим оЬразом. В режиме повышенной производительности устройство управления обеспечивает функционирование системы аналогично известному следующим образом. . В такой режим система переходит при переводе по входу 32 триггера 2 и в нулевое состояние с пульта управления системы или по сигналу автомата управления режимами работы дуплексной системы, при этом запрещается прерывание работы ЭВМ по сигналам несравнения в схеме 22 сравнения и обеспечивается автономная работа ЭВМ, так как на управляемых входах блоков 12 и 12 будет постоянно действовать высокий потенциал, поступающий с нулевого выхода триггера 2t через элемент ИЛИ 23. Предлагаемое устройство обеспечивает равноправный доступ к общей оперативной памяти 30 со стороны каждой ЭВМ. Это происходит следующим.образом. При необходимости обращения к ОП 30 в ЭВМ 1 ( регистре 6-1(6|2)появляется код адреса обращения к ОП, а триггер 7i (TT. наличия запроса перебрасывается в единичное состояние. Высокий потенциал с единичного выхода 7риггера 7-1 (7i)поступает на вход дешифратора 28, который в этом случае обеспечивает появление высокого потенциала только на первом (втором) выходе, что обеспечивает подачу кода адреса обращения с регистра 6i (6rj) через блок 18, (l8) и блок 27 элементов ИЛИ на адресный вход ОП 30. G появлением кода адреса обращения начинается цикл работы ОП 30, при этом высокий потенциал с единичного выхода триггера Э (91.)при считывании информации поступает на вход блока 21 (21г2), на другой вход которого подается высокий потенциал с элемента И-НЕ 19-, (19г2), на вкоды которого поступают низкие потенциалы с нулевого выхода триггера 7- () ЭВМ 1 (l-ji, посылающий запрос к ОП, и с второго выхода дешифратора 28, считанная информация поступает на информационный регистр (8г ЭВМ 1- (1) через блок 21-J (21 г{). При записи информации ЭВМ 1 (fi} В ОП 30 содержимое информационного регистра 8-| (8г поступает через блок 20 ,, (20я) и блок 29 элементов ИЛИ на информационный вход ОП 30. При этом на первый управляемый вход блока 20-, (20) подается высокий потенциал с нулевого выхода триггера 9i (9п), нулевое состояние которого соответствует процедуре записи в ОП 30, а на второй управляющий вход - подается .высокий потенциал

795

с выхода дешифратора 28, После окончания обращения к ОП 30 содержимое регистров 6i (6i2) , 8-j (8/2), триггеров 7-т (7-2. 9 (Э) обнуляется.

Конфликтные ситуации, возникающие при одновременном появлении на входе дешифратора 28 запросов от обоих ЭВМ, разрешаются тем, что на выходе дешифратора 28 всегда врзбуждается только один выход, например первый вследствие чего передача информации из ОП 30 в ЭВМ или обратно блокируется низким потенциалом с,второго выхода дешифратора 28. В режиме повышенной надежности триггер режима работы находится в единичном состоянии, и система будет функционировать следующим образом.

После выполнения каждой команды результат с одного из регистров блока 5-1 (5«2), в котором записан результат выполнения команды, подается через блок 13 (13|2) на схему 22 сравнения. Сигнал сравнения результатов выполнения команды через элемент ИЛИ 23 обеспечивает перезапись содержимого блоков основных регистров 5 (5i) через блоки 12., С12-7) в блок 10-i (lO-j) и процесс выполнения программы продолжается. Сигнал несравнения результатов в схеме 22 сравнения чере открытый элемент И 25 подается в блоки и 3 обеих вычислительных машин. По этому сигналу блоки 2 и 2п управления обеспечивают повторение выполнения команды, при которой произошло несравнение результатов, путем выполнения сортветствукяцей микропрограммы повторного выполнения команды. Это происходит следующим образом.

Так как сигнал сравнения с выхода схемы сравнения 22 отсутствует, то содержимое регистров 10 и 10 сохраняется прежним, поэтому после подачи управляющего сигнала блоками 2 и 2 на блоки ТЦ и 11 (j обеспечивается перезапись содержимого блоков 10., (ij) в блоки 5-1 (5п). Такая перезапись обеспечивает возможность повторения команды, прикоторой произошел сбой, Одновременно с перезаписью содержимого блоков 10 1 (lOrj) в блоки 5 -i (51 осуществляется подача импульса несравнения с выхода схемы 22 сравнения на входы триггера 2б наличия сбоя, который перебрасывается в единичное состояние, После чего на блоки (Ис) подается, разрешающий сигнал, который обеспечивает перезапись ре98

зультата из регистров 5-, (5, ) в регистры 15-, (IS). Одновременно содержимое регистра 5 (5п) подается на Первые входы соответствующих схем 1б, (Тб) сравнения, на вторые входы которых подается содержимое регистров 15-f(l5i2) с результатами предыдущего выполнения команды, а на управляющие входы схем 16t и 162 сравнения подается разрешающий высокий потенциал с единичного выхода триггера 29, т.е. триггер 29 обеспечивает запись информации в регистры 15i и 15 через блоки 1t и, }kr с задержкой на время выполнения одной команды.

Результаты сравнения с выхода сравнения-схемы 1б 1 (1бг2) поступают на соответствующий вход дешифратора 31 и вход счетчика 17- (17г) единичные сигналы переполнения на выходах которых являются сигналами отказа ЭВМ 1-) (li). После повторения ранее сбившейся команды может произойти сравнение или несравнение результатов в схеме 22 сравнения. 8 случае сравнения результатов к содержимому счетчика 17-, , если сбой произошел в ЭВМ 1., , или к содержимому счетчика 17ft , если сбой произошел в ЭВМ Ifj, прибавляется единица. На нулевой вход триггера 2б поступает единичный си|- нал, который перебрасывает его в нулевое состояние, и вычислительный процесс в дуплексной системе будет продолжаться,

В случае повторного- несравнения результатов к содержимому счетчиков 17 или 177. сбоев также прибавляется единица. Полученные значения результатов выполнения команды через блоки Т и I+Q будут переписаны на регистры 15 и 15(1, а триггер 2б будет внов в единичном состоянии, обеспечивая последующую работу схем l6-i и 1бп сравненил. Кроме того, сигнал несравнения с выхода схемы 22 сравнения поступает на третий вход дешифратора 31 Пусть для определенности произошел повторный сбой в ЭВМ 1, тогда сигнал несравнения появится на выходе схемы 16 сравнения, который поступит на счетчик 17-) и первый вход дешифратора 31. На второй вход этого дешифратора 31 с выхода схемы 17-j поступает низкий потенциал - сигнал сравнения, а на третий его вход - сигнал несравнеиия с выхода схемы 22 сравнения. Такая комбинация сигналов (101 на входах дешифратора соответствует 995 сбою (отказу ) ЭВМ Ц, Аналогично ком бинация (011) соответствует сбою (от ,казу ) в ЭВМ Itj. Одновременно сигнал несравнения с выхода схемы 16-, (б) поступает на соответствующий счетчик 17(171 переполнение которого рассматривается как отказ ЭВМ 1-,(1,j) которая в последующем отключается из состава системы. В случае необходимости сигнал на повторение неправильно выполненной команды может подаваться с некоторой задержкой, зависящей от длительности действия случайного сбоя. Таким образом, устройство обеспечивает идентификацию сбившейся или отказавшейся ЭВМ, что позволяет при сбое в одной из ЭВМ системы повторить только одну команду, вместо длитель.ной работы контрольных и диагностических тестов. с/5 ормула изобретения Устройство для сопряжения двух вычислительных машин, содержащее первый счетчик сбоев, оперативную память адресный и информационный входы которой соединены соответственно е выходами первого и второго блоков элементов ИЛИ, схему сравнения результатов. первый и второй входы которой подклюмены соответственно к выходам первого и второго блоков элементов И, первые и вторые входы которых являются соответственно первым, вторым управляющими входами и первым и вторым входами результата операции устройства, триггер режима работы, вход которого является входом задания режима устройст ва, а единичный и нулевой выходы соединены соответственно с первыми вхрдами элемента И и элемента ИЛИ, вторыми входами подключенных соответственно к первому и второму выходам схемы сравнения результатов, а выхода ми - соответственно к выходам прерывания и задания режима работы устройства, первые входы третьего и четвертого блоков элементов И соединены соответственно с первым и вторым адресустройства, выходы - соными входами ответственно с первым и вторым входами первого блока элементов ИЛИ, а вторые входы - соответственно с первым и вторым выходами первого дешифратора, первый и второй входы которого подключены соответственно к первому и второму входам запроса устройства и первым входам первого и второго элементов И-НЕ, вторыми входами 9If соединенных соответстзенно ; вторым и первым выходами первого дешифратора, а выходами - соответственно с первыми управляющими входами пятого и шестого блоков элементов И, информационные и вторые управляющие входы которых соединены соответственно с выходом оперативной памяти, первым и вторым входами считывания устройства, а выходы являются первым и вторым информационными выходами устройства, первый и второй входы второго блока элементов ИЛИ подключены соответственно к выходам седьмого и восьмого блоков элементов И, информационные и первые управляющие входы которых соединены соответственно с первым и вторым информационными входами устройства и первым и вторым входами записи устройства, а вторые управляющие входы соответственно с первым и вторым выходами первого дешифратора, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения идентификации ситуаций сбоя иЛи отказа, в него введены второй дешифратор, второй счетчик сбоев, две схемы срав- ; нения, два регистра, девятый и десятый блоки элементов И и триггер наличия сбоя, причем первые входы первой, второй схем сравнения и девятого, десятого блоков элементов И соединены соот ветственно с первым и вторым входам/; результата устройства, вторые входы с выходом триггера наличия сбоя, выходы девятого и десятого блоков элементов И соединены соответственно через первый и второй регистры с третьими вxoдa первой и второй схем сравнения, выходы которых подключены соответственно к первому и второму входам второго дешифратора и соответственно через первый и второй счетчики сбоев - к первому и второму выходам отказа устройства, первый и второй выходы второго дешифратора подключены соответственно к первому и второму выходам сбоя устройства, а третий вход - к входу триггера наличия сбоя и первому выходу схемы сравнения результатов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР tf , кл. G 06 F 11/00, 1979. 2.Авторское свидетельство СССР по заявке N 2907398/28-2i, кл. G 06 F 3/0, 1980.

Авторы

Даты

1982-08-30—Публикация

1981-01-15—Подача