Изобретение относится к вычислительной технике и автоматике и может быть использовано в устройствах управления вычислительных машин для подсчета циклов в операциях ускоренного счета по сложным алгоритмам, а также для организации гибких дисциплин обслуживания запросов на прерывание программы.

Известен вычитающий параллельный счетчик, содержащий основной и вспомогательный триггеры и четыре элемента И, входы установки и сброса триггеров соединены с выходами соответствующих элементов И, прямой и инверсный выходы вспомогательного триггера соединены с первыми входами соответственно первого и второго элементов И, а прямой и инверсный выходы основного триггера соединены с входами соответственно третьего и четвертого элементов И того же разряда, вспомогательные входы первого и второго элементов И соединены с первой тактовой шиной, вторая тактовая шина соединена с вспомогательными входами третьего и четвертого элементов И, а дополнительные входы первого и второго элементов И соединены с инверсными выходами вспомогательных триггеров последующих разрядов 1.

Недостатком этого вычитающего параллельного счетчика является огрниченность его функциональных возможностей.

Наиболее близким к предложенному техническому решению является вычитающий параллельный счетчик, содер жащий разряды, каждый из которых содержит основной триггер, вспомогателйный триггер, четыре элемента И, выходы которых соединены соответственно с входами установки и сброса основного триггера и входами установки и сброса вспомогательного триггера, а также содержащий в каждом разряде триггер памяти, прямЪй выход вспомогательного триггера каждого разряда соединен с первым входом первого элемента И этого разряда, второй и дополнительные входы которого соединены соответственно с первой тактовой, шиной и инверсными выходами вспог огательных триггеров следующих разрядов, инверсный выход ка5кдого вспомогательного тр иггера каждого разряда соединен с первым входом второго элемента И этого разряда, второй и дополнительные входы которого соединены соответственно с первой тактовой шиной и инверсными выходами вспомогательных триггеров следующих разрядов, инверсный выход основного триггера каждого разряда соединен с первым входом третьего элемента И этого разряда, второй

вход которого соединен с второй тактовой шиной которая соединена с первым входом четвертого элемента И каждого разряда, второй вход которого соединен с прямым выходом основного триггера этого разряда f2j.

Недостатком известного вычитгиощего параллельного счетчика также является ограниченность функциональных возможностей, так как он не обеспечивает возможности управления модулем счета.

Целью изобретения является расширение функциональных возможностей путем управления модулем счета,

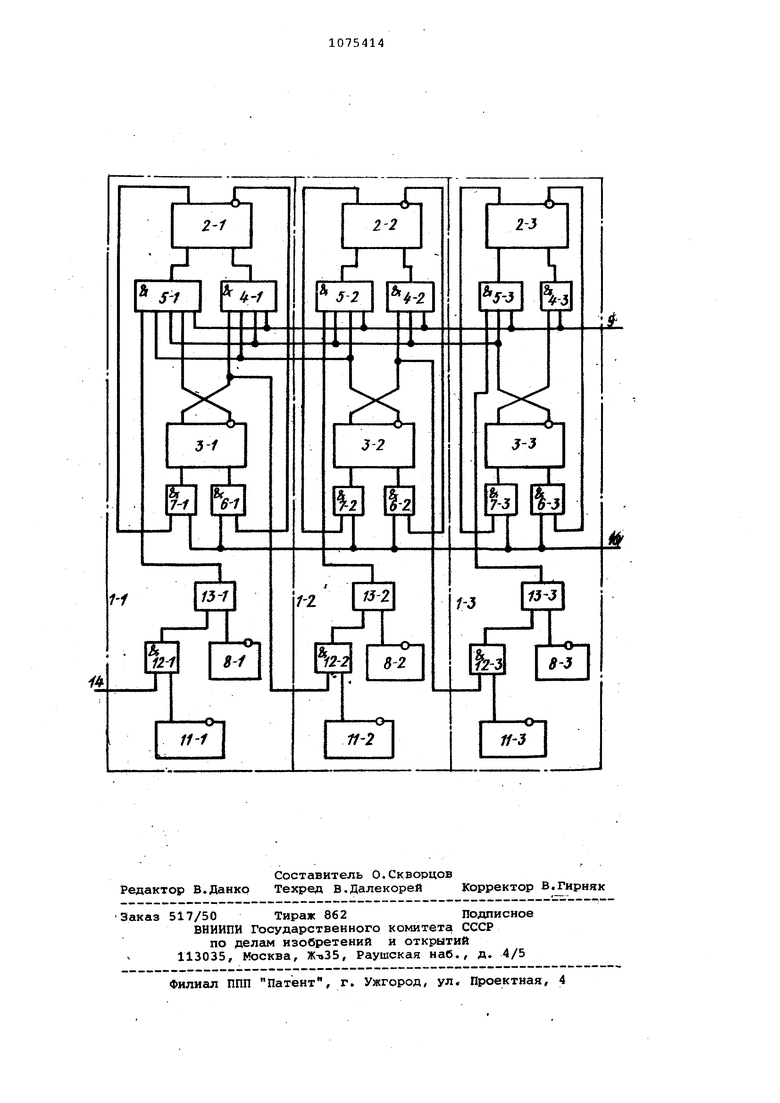

Поставленная цель достигается тем, что в вычитающий параллельный счетчик, содержащий разряды, рсаждый из которых содержит основной триггер, вспомогательный триггер, четыре элемента И, выходы которых соединены соответственно с вхопаг /ш vcraновки и сброса основного триггера и i входами установки и сброса вспомогательного триггера, а также содержащий в каждом разряде триггер памяти, прямой выход вспомогательного триггера каждого разряда соединен с первым входом первого элемента И этого разряда, второй и дополнительные входы которого соединены соответственно с первой тактовой шиной и инверсными выходами вспомогательных триггеров следующих разрядов, инверсный выход каждого вспомогательного триггера каждого разряда соединен с первым входом второго элемента И этого разряда. второй и дополнительные входы которого соединены соответственно с первой тактовой шиной и инверсньл-ш выходами вспомогательных триггеров следующих разрядов, инверсный выход основного триггера каждого разряда соединен с первы - входом третьего элемента И этого разряда, второй вход которого соединен с второй тактовой шиной, которая соединена с первым входом четвертого элемента И каждого разряда, второй вход которого соединен с прямым выходом основного триггера этого разряда, в каждый разряд введен введен дополнительный триггер памяти, дополнительный элемент и и элемент ИЛИ, выход которого соединен с вспомогательным входом второго элемента И этого разряда, входы элемента ИЛИ соединены соответственно с прямым выходом триггера памяти и выходом дополнительного элемента И этого разряда, входы дополнительного элемента И этого разряда соединена соответственно с прямым выходом дополнительного триггера памяти этого разряда и прямым выходом вспомогательного триггера предыдущего раэряда во всех разрядах, кроме первого где входы дополнительного элемента И соединены с выходом дополнительного триггера памяти первого разря и дополнительным входом счетчика. На чертеже представлена структурная схема трехразрядного вычитающего параллельного счетчика. Вычитаюидай параллельный счетчик содержит разряды 1-1 - 1-3, каждый из которых содержит основной триггер 2-1 - 2-3, вспомогательный триггер 3-1 - 3-3, четыре элемента И 4-1 - 4-3 4- 7-1 - 7-3, выходы которых соединены соответственно с входами установки и сброса основ ного .триггера 2-1 - 2-3 и входами установки и сброса вспомогательног триггера 3-1 - 3-7, а также содержащий в каждом разряде триггер 8-1 - 8-3 памяти, прямой выход всп могательного триггера 3--i каждого i-ro разряда соединен с первым входом первого элемента И 4-i этог разряда, второй и дополнительный входы которого соединены соответственно с первой тактовой шиной 9 и инверсными: выходами вспомогатель ных триггеров следующих разрядов, инверсный выход каждого вспомогате ного триггера 3-i каждого i-ro раз ряда соединен с первьам входом второго элемента И 5-i этого разряда второй и дополнительные входы кото рого соединены соответственно с . первой тактовой шиной 9 и инверсны /ш выходами вспомогательных триггеров следующих разрядов, инве ный выход основного триггера 2-i каждого i-ro разряда соединен с первым входом третьего элемента И 6-1 этого разряда, второй вход кот рого соединен с второй TaKTOBOif шиной 10, которая соединена с первым входом четвертого элемента И 7-1 каждого разряда, второй вход которого соединен с прямым выходом основного триггера 2-i этого разряда. Разряды содержат также допол нительный триггер 11-1 - 11-3 памя ти, дополнительный элемент И 12-1 1:2-3 и элемент ИЛИ 13-1 - 13-3, в ход которого соединен с вспомогательным входом второго элемента И.5-i этого 1-го разряда, вход элемента ИЛИ 13-i соединены соответственно с прямым выходом тригге ра 8-1 памяти и выходом дополнительного элемента И 12-i этого i 1азряда, входы дополнительного эле мента И 12-1 этого разряда соединены соответственно с прямым выходом дополнительного триггера 11-i памяти этого разряда и прямым выходом вспомогательного триггера 3-|-1 предыдущего г -1-го разряда во всех разрядах, кроме первого, где входщ дополнительного элемента И 12-1 соединены с выходом дополнительного триггера 11-1 памяти первого разряда и дополнительным входом 14 счетчика. ; Вычитающий параллельный счетчик работает следующим образом. Вычитание единиц осуществляется счетчиком тогда, когда триггеры 8-1 - 8-3 находятся в единичном состоянии, а триггеры 11-1 - 11-3 в нулевом состоянии. В этом случае правило переключения состояний разрядов счетчика следующее. Если счетчик находится в состоянии С(t)...1000...0, то следующее состояние равно C{t+l) ...0111..,, причем старшие разряды счетчика не меняют свои состояния. Другими словами f-и разряд счетчика переключается в следуюшее состояние, если конъюнкция 1 т.е. если все младшие разряды до г -го находятся в нулевом состоянии. Если это условие не выполняется, то -и разряд сохраняет предыдущее состояние. Приме р.Пусть содержимое триггеров 2-1 - 2-3 соответственно равно 1, О и О (триггер 2-1 соответствует старшему разряду, триггер 2-3 - младшему разряду счетчика) . В этом случае элементы И 4-1 и 5-2 открыты, а элементы И 5-1, 4-2 и 4-3 закрыты, примем элемент И 5-1 закрыт нулевым логическим сигналом инверсного выхода триггера 3-1, а вентили-элементы И 4-2 и 4-3 - нулевым логическим сигналом прямого выхода триггеров 3-2 и 3-3 соответственно. При поступлении первого счетного импульса триггер 2-1 установится в ноль, а,триггеры 2-2 и 2-3 - в .единицу./Содержимое счетчика окажется равным 011.После перезаписи кода 011 во вспомогательные триггеры 3-1, 3-2 и 3-3 открытым будет лишь элемент И 4-3. Остальные элементы И управляющие входами триггеров 2-1 и 2-3, будут закрыты, причем элементы И 4-1, 4-2, 5-1, 5-2 и 5-3 будут закрыты нулевым логическим сигналом инверсного выхода триггера 3-3, элементы И 7, 4-1, 5-1 и 5-2 - дополнительно нулевьам логическим сигналом инверсного, выхода триггера 3-2, а элемент И 4-1 - нулевым логическим сигналом прямого выхода триггера 3-1. В связи с этим очередным счетным импульсом триггер 2-3 установится в ноль, а триггеры 1 и 2 сохранят прежнее состояние и, таким образе, содержимое счетчика станет равным 010. При другой разрядности

счетчика или другом его начальном состоянии устройство работает аналогично.

Стирание единиц (вычитание двоек четверток, восьмерок и т.д.) осущес вляется счетчиком при нулевом соетоянии триггеров 8-1 - 8-3 и 11-1 11-3. Это достигается тем, что при этом условии элементы И 5-1 - 5-3 закрыты нулевым логическим сигналом соответственно элементов ИЛИ l3-l - 13-3.

Стирание с последующим вычитанием из содержимого счетчика 2 (пересчет постепени 2 ) осуществляется при нулевом состоянии тригг ров 8-i-X (,1,...,J-1) разрядов при условии, что триггеры 8-i старших разрядов i j , j -f 1 , . . . , n находяся в единичном состоянии, а все три геры 11- i- в нулевом состоянии,

Пример. Пусть в трехраз- рядном счетчике записано число 111, триггер 8-1 находится в единичном состоянии, а триггеры 8-2, 8-3, 11-1 - 11-3 - в нулевом состоянии. В этом случае первый счетный импуль проходит только на вход триггера 2-3 и устанавливает его в ноль, в рзультате в счетчике код числа стане равным 110. Для второго счетного импульса, таким образом, будет откр только элемент И 4-2. В результате чего триггер 2-2 установится в ноль, и в счетчике останется код 100 (показание его уменьшится на 2). Таким образом, пересчет К-го разряда в данном случае осуществлен по степени 2. Очевидно на каждом последующем счетном импульсе при большей разрядности счетчика в дальнейшем вычиталось бы число 2..

Пересчет по убывающим степеням, начиная со- степени 2 (К | осуществляется при нулевом состоянии триггеров 8-1-х (i 0,1,. . . , J-1 j разряг дов при условии, что триггеры 8-J старших разрядов j, j-H ,...,m находятся в единичном, триггеры 11-К 11-К+1,о..,11- n- в нулевом, а разряды 11-К-1,. . .,11-0 в единичном состоянии.

Работу устройства проиллюстрируем на примере трехразрядного счетчика.

Пусть в счетчике записан код 100, при этом пусть , т.е. триггеры 11-2, 11-3 находятся в единичном состоянии, а триггеры 8-2, 8-3 и 11-1 - в нулевом.

При поступлении первого счетного импульса триггер 2-rl установится в нулевое, а триггер 2-2 - в единичное состояние. В счетчике.I таким образом, установится код 010.

При поступлении второх-о счетного импульса триггер 2-2 установится в нулевое, триггер 2-3 - в единичное состояние, а триггер 2-1 состояние не изменит, в счетчике будет код 001. Таким образом, пересчет содержимого счетчика осуществлен по убывающим степеням.

Стирание с последующим вычитание из содержимого счетчика чисел 2 и пересчетом ® ,..., ,..., разрядов ( по степеням 2f+i , , 2 осуществляется .

Аналохично построенный многоразрядный счетчик можно таким же образом настроить на вычитание четверок, восьмерок, шестнадцати и т.д причем степень максимально вычитаемого числа определяется крайней правой единицей в коде числа, записанного в триггеры 8-1.- 8-3.

Стирание с последующим вычитанием из содержимого счетчика чисет 2J и пересчетом К-го разряда ( по степени 2 осуществляется при нулевом, состоянии триггеров 8-i-x (,l,..., j-1 разрядов при условии, что триггеры 8- i старших разрядов J, j +1,..., n находятся в единичном состоянии, а все триггеры 11-i, кроме (К-1)-го находятся в нулевом состоянии, причем содержимое триггера 11-К-1 единичное.

Работу устройства для этого случая поясним на примере трехразрядного счетчика. Пусть в счетчике содержится код 111, в триггерах 8-1 - 8-3 - код 100 и в триггерах 11-1 - 11-3 - код 010. В соответствии с принятыми обозначениями , К 1. В этом случае при поступлении первого счетного импульса триггер 2-3 установится в нулевое состояние, а триггеры ,2-2 и 2-1 останутся в прежнем состоянии. В счетчике установится код 110. После перезаписи кода 110 в триггеры 3-1 - 3-3 открытым будет только элемент И 4-2. Вторым счетным импульсом триггер 2-2 установится в ноль, а триггеры 1 и 3 сохранят прежнее состояние. В счетчике установится код 100. При нулевом состоянии триггеров 8-i-x (ч 0 ,1,... , J-1/ разрядов при условии, что триггеры старших разрядов 8- j, 8 j +1,... , 8-п, находятся в единичном, а все триггеры 11- Б кроме -1, 11 -1, ,-1 в нулевом состоянии. Устройство при этом работает аналогично указанному.

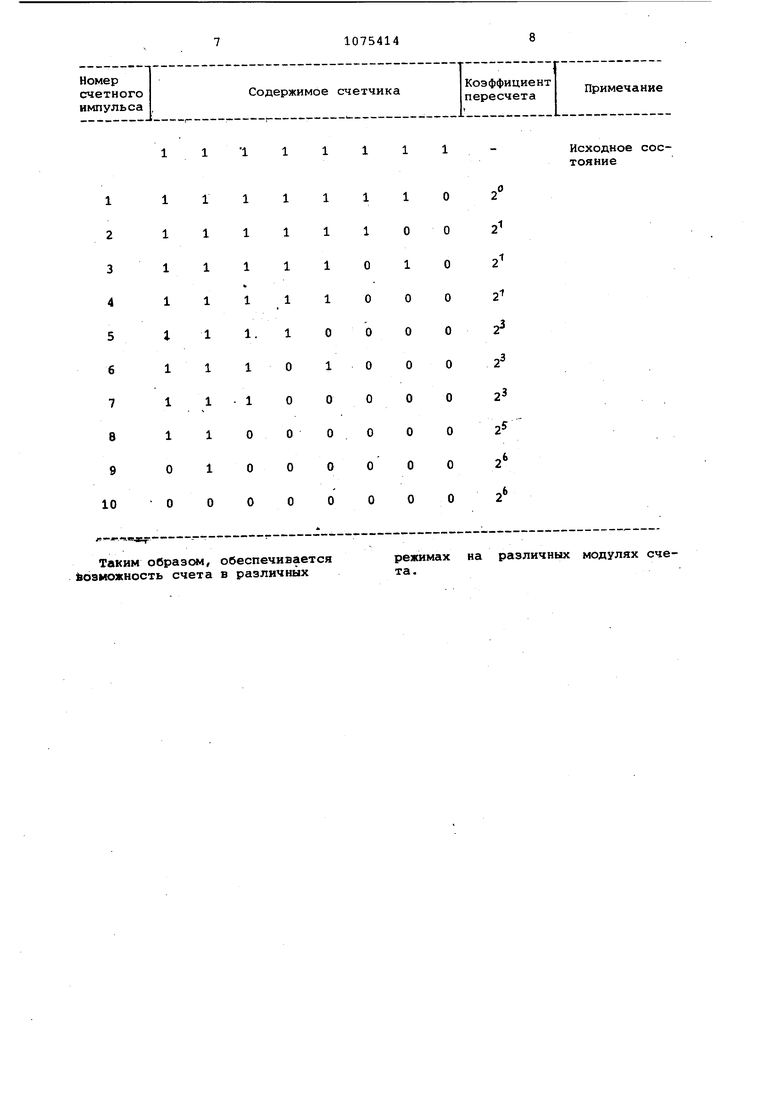

Изменения содержимого счетчика для случая , , 4, ч 2 поясняются та блиц ей.

Таким образом, обеспечивается Ьоаиожность счета в различных

режимах на различных модулях счета.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Сенсорный переключатель | 1983 |

|

SU1092725A1 |

| Счетчик импульсов в Р-кодах Фибоначчи | 1991 |

|

SU1803974A1 |

| Устройство для упорядочивания чисел | 1981 |

|

SU1012239A1 |

| Кольцевой счетчик | 1983 |

|

SU1128391A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство для определения разностидВуХ п-РАзРядНыХ чиСЕл | 1979 |

|

SU824208A1 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| Счетчик импульсов в р-кодах Фибоначчи | 1987 |

|

SU1443168A1 |

ВЫЧИТМОЩИЙ ПАРАЛЛЕЛЬНЫЙ СЧЕТЧИК, содержащий разряды, каждый из которых содержит основной триггер, вспомогательный триггер, четыре элемента И, выходы которых соединены соответственно с входами установки и сброса основного триггера и входами установки и сброса вспомогательного триггера, а также содержащий в каждом разряде триггер памяти, прямой выход вспомогательного триггера каждого разряда соединен с первым входом nep-,j вого элемента И этого разряда-, второй и дополнительные входы которого соединены соответственно с первой тактовой шиной и инверсными выходами вспомогательных триггеров следующих разрядов, инверсный выход каждого вспомогательного триггера каждого разряда соединен с первым входом второго элемента И этого разряда, второй и дополнительные входаа которого соединены соответственно с первой тактовой шиной и инверсными выходами вспомогательных триггеров следуюшлх разрядов, инверсный выход основного триггера каждого разряда соединен с первым входом третьего элемента ч И этого разряда, второй вход которого соединен с второй тактовой шиной, которая соединена с первым входом четвертого элемента И каждого разряда, второй вход которого соединен с прямым выходом основного триггера этого разряда, отлич ающий ся тем, что, с целью расширения функциональных возможностей путем управления модулем счета в каждый разряд введен дополнительный триггер памяти дополнительный элемент И и эле(Л мент ИЛИ, выход которого соединен с вспомогательным входом второго элемента И этого разряда, входы элемента ИЛИ соединены соответственно с прямым выходом триггера памяти и выходом дополнительного элемента И этого разряда, входы дополнительного элемента И этого раз ел ряда соединены соответственно с прямым выходом дополнительного триггера памяти этого разряда и прямым 4: выходом вспомогательного триглгера предыдущего разряда во всех разрядах, кроме первого, где входи дополнительного элемента И Соединены с выходом дополнительного триггера памяти первого разряда и дополнительным входом счетчика.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Майоров С.А., Новиков Г.Ц | |||

| Принципы организации цифровых машин | |||

| П., Машиностроение, 1974, с | |||

| Способ нанесения гальванических покрытий на металлокерамические лампы и способ крепления ламп и подвода тока к ним в гальванической ванне | 1960 |

|

SU136146A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычитающий параллельный счетчик | 1979 |

|

SU824441A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-23—Публикация

1982-08-17—Подача