Изобретение относится к вычислитель- но0 технике и может быть использовано для пересчета импульсов с непосредственным представлением результатов в минимальны Р-кодах Фибоначчи.

Цель изобретения - упрощение и повышение регулярности логической структуры.

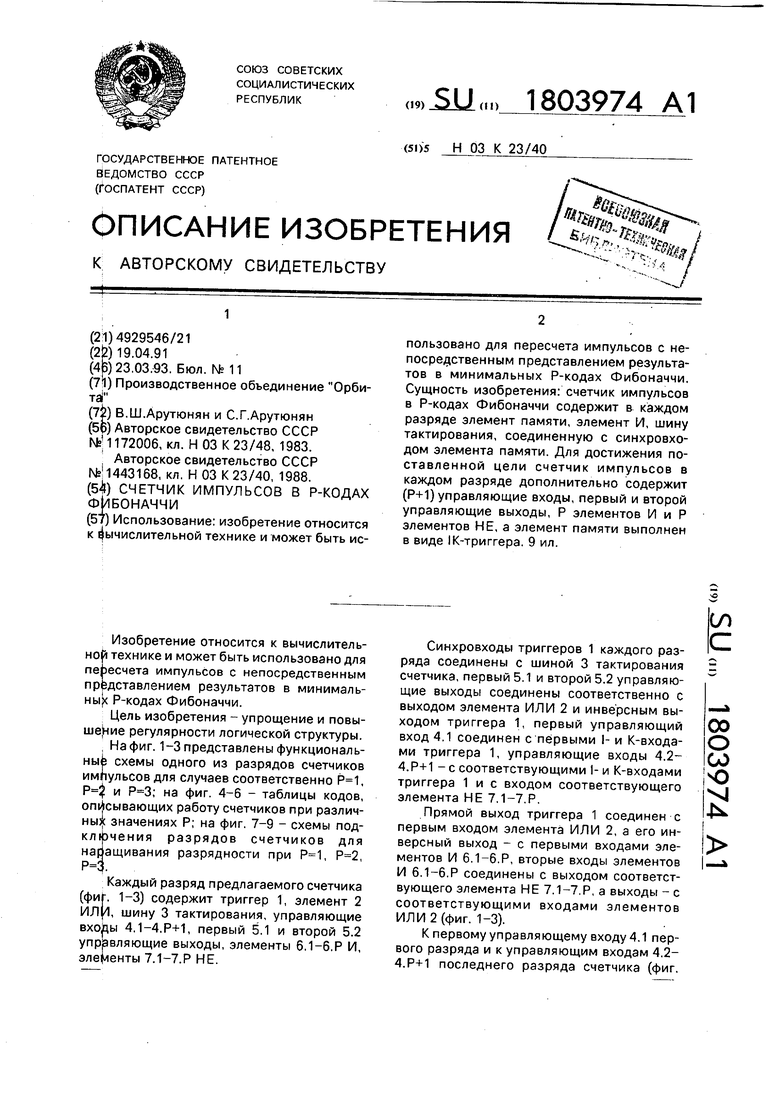

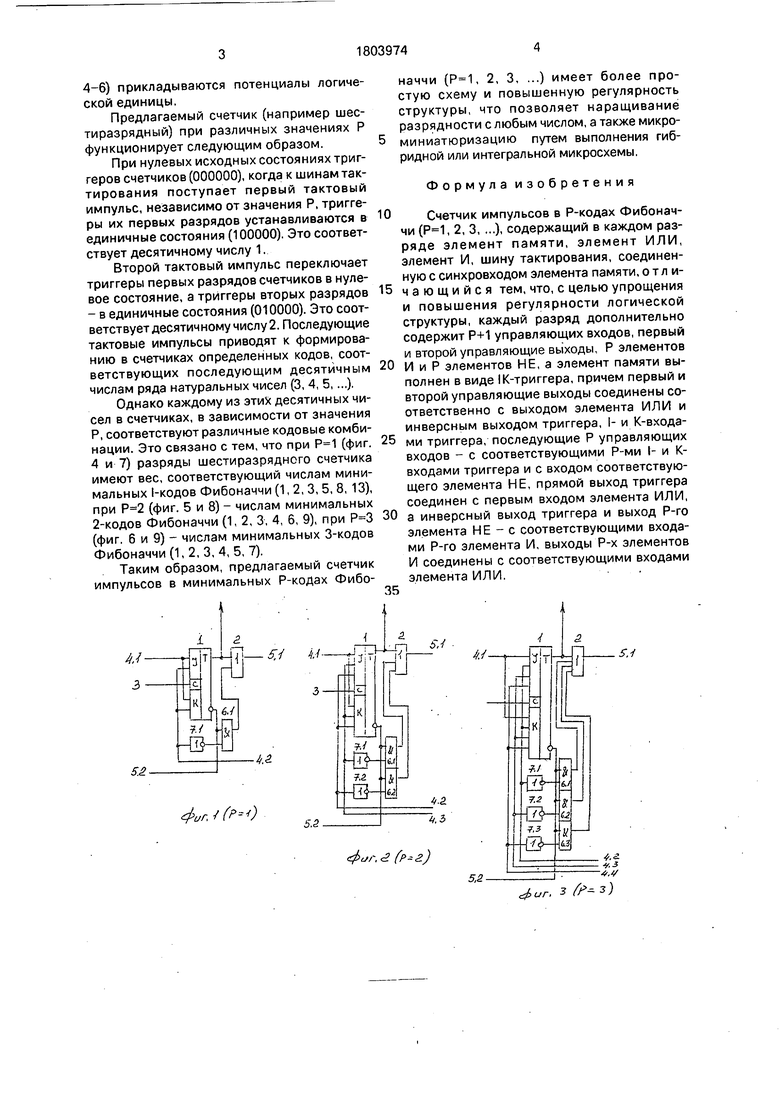

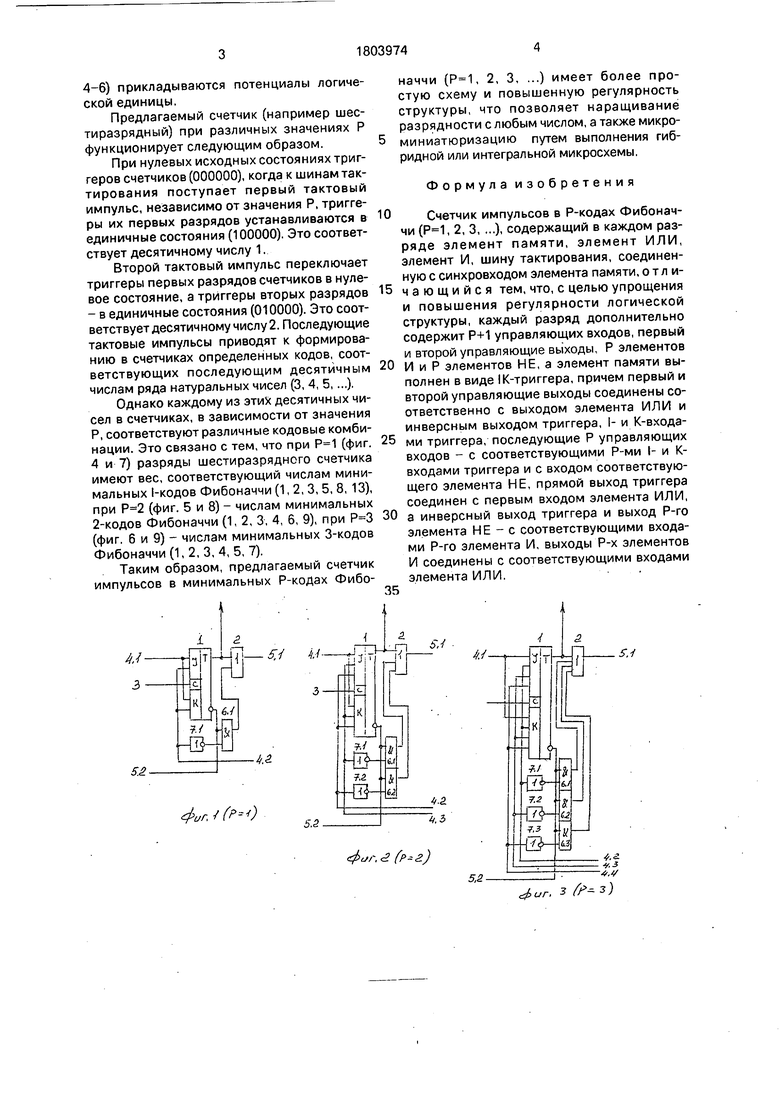

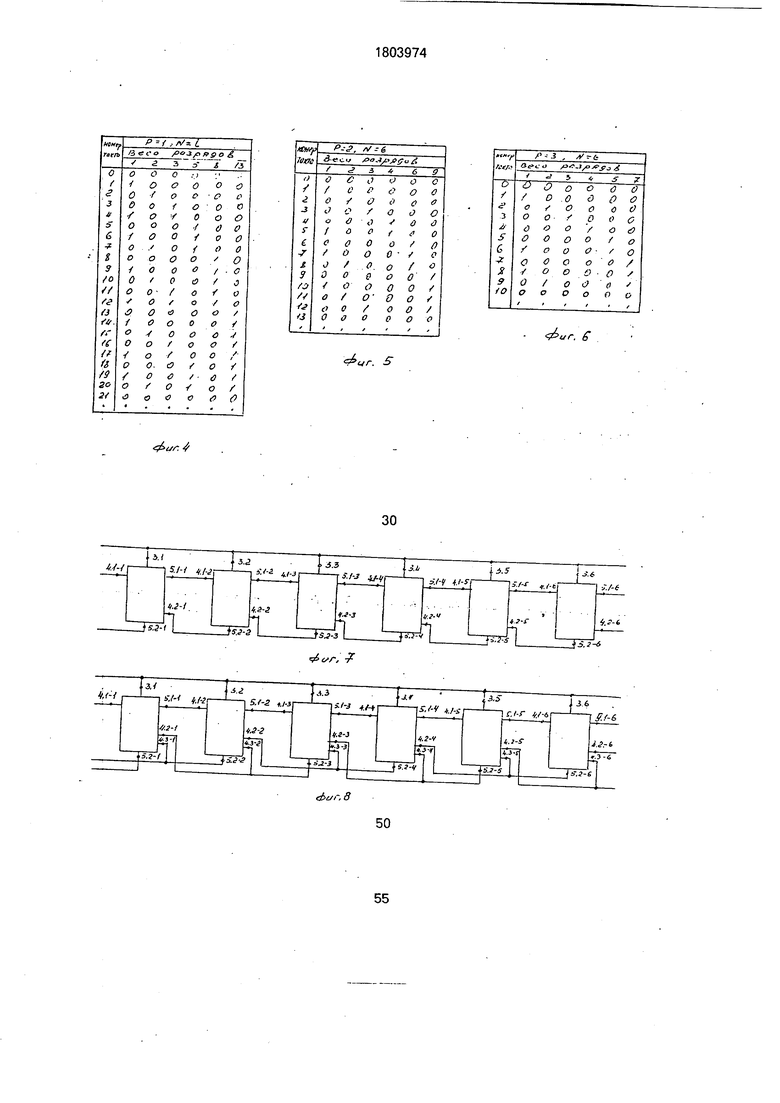

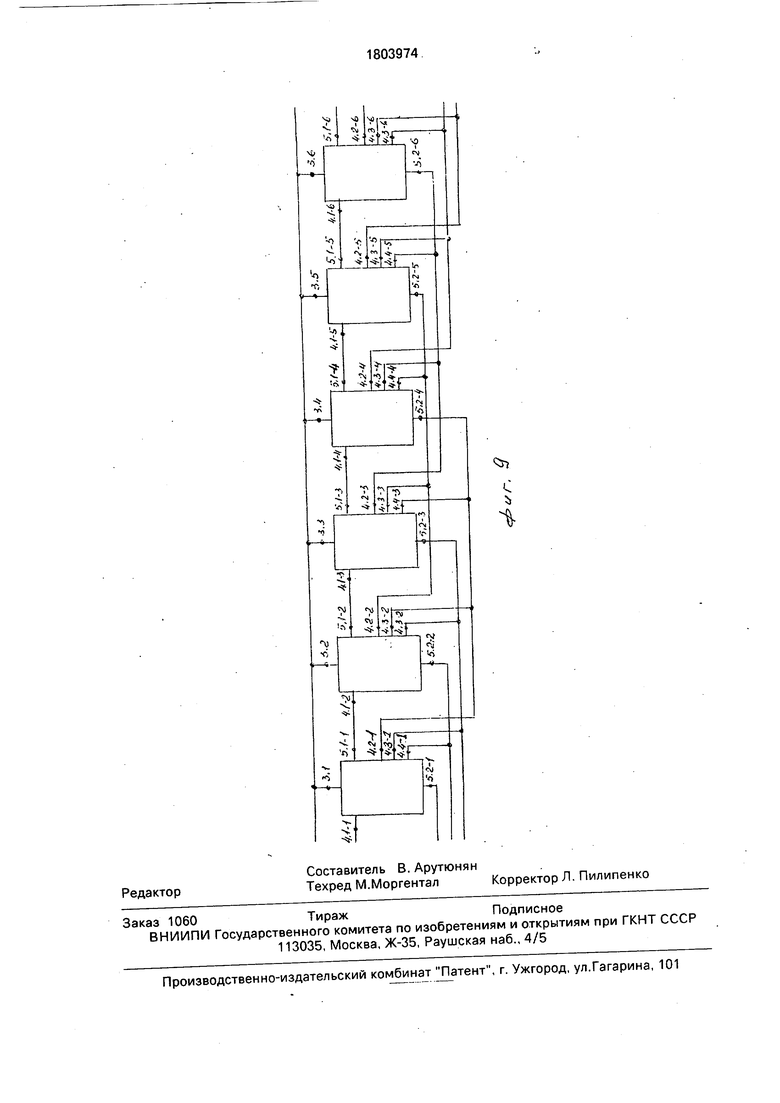

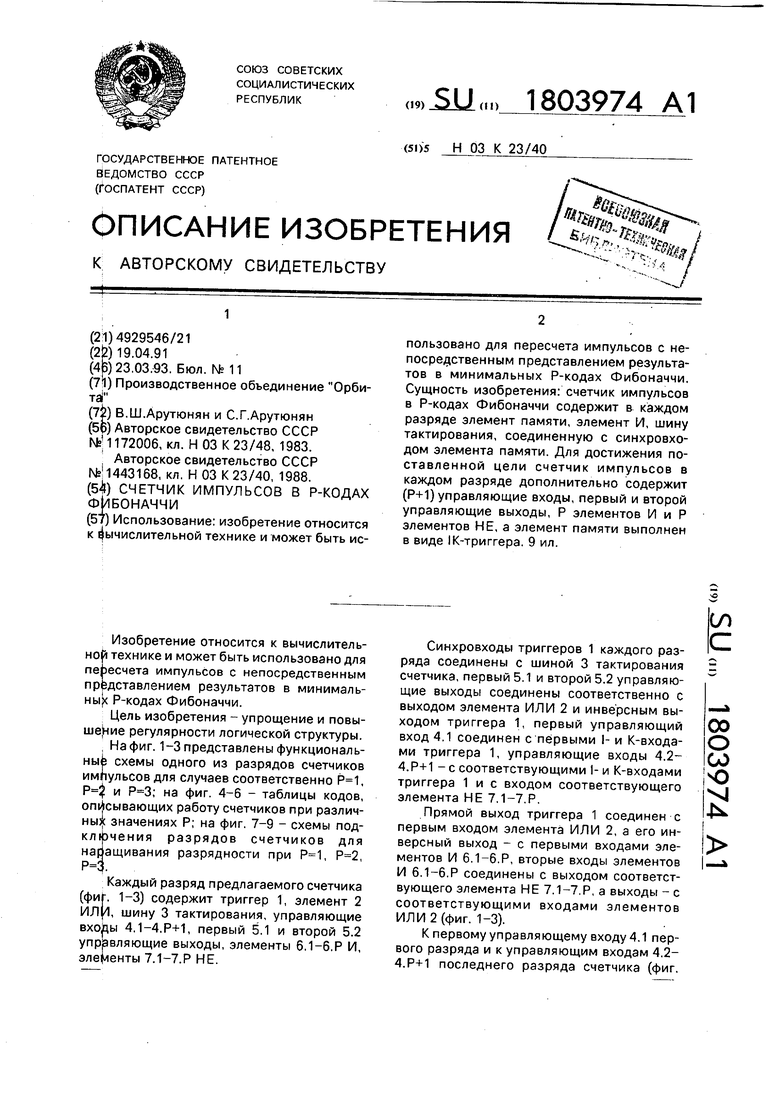

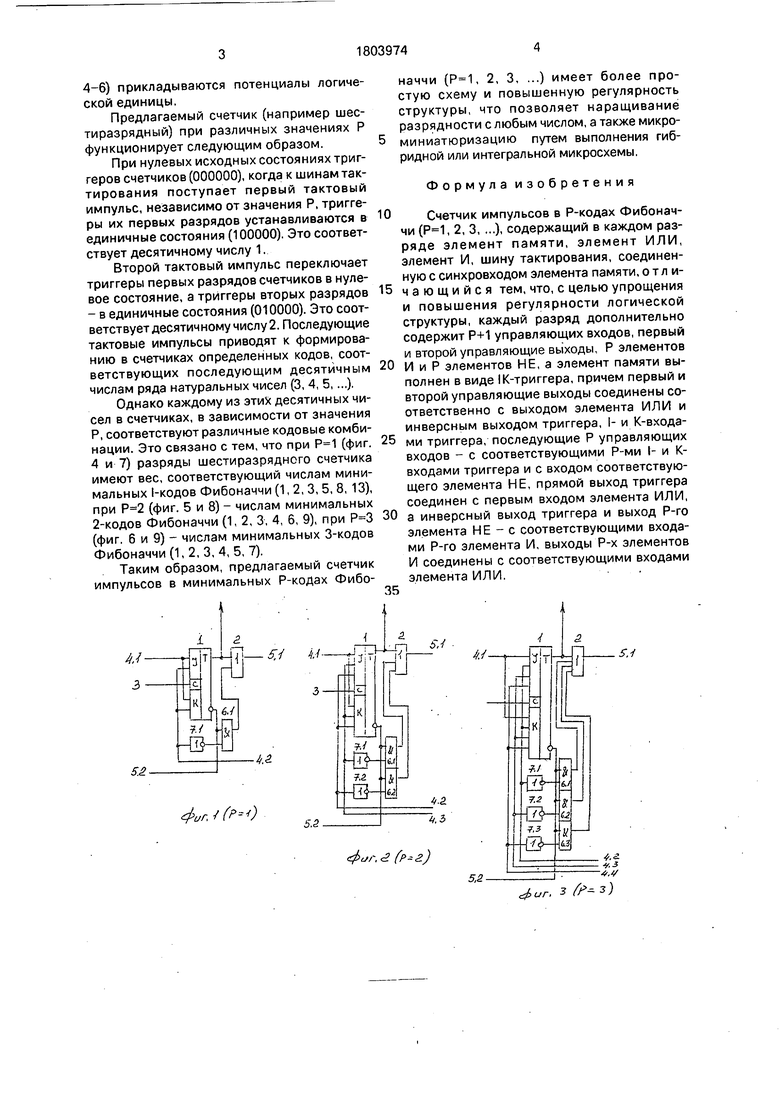

На фиг. 1-3 представлены функциональны схемы одного из разрядов счетчиков импульсов для случаев соответственно , и на фиг. 4-6 - таблицы кодов, описывающих работу счетчиков при различны)}: значениях Р; на фиг. 7-9 - схемы подключения разрядов счетчиков для наращивания разрядности при , , .

Каждый разряд предлагаемого счетчика (фиг, 1-3) содержит триггер 1, элемент 2 ИЛ(4, шину 3 тактирования, управляющие вхо|цы 4.1-4.Р+1, первый 5.1 и второй 5.2 управляющие выходы, элементы 6.1-6.Р И, элементы 7.1-7.Р НЕ.

Синхровходы триггеров 1 каждого разряда соединены с шиной 3 тактирования счетчика, первый 5.1 и второй 5.2 управляющие выходы соединены соответственно с выходом элемента ИЛИ 2 и инверсным выходом триггера 1, первый управляющий вход 4.1 соединен с первыми I- и К-входа- ми триггера 1, управляющие входы 4.2- 4.Р+1 - с соответствующими I- и К-входами триггера 1 и с входом соответствующего элемента НЕ 7.1-7.Р.

Прямой выход триггера 1 соединен с первым входом элемента ИЛИ 2, а его инверсный выход - с первыми входами элементов И 6.1-6.Р, вторые входы элементов И 6.1-6.Р соединены с выходом соответствующего элемента НЕ 7.1-7.Р, а выходы - с соответствующими входами элементов ИЛ И 2 (фиг. 1-3).

К первому управляющему входу 4.1 первого разряда и к управляющим входам 4.2- 4. Р+1 последнего разряда счетчика (фиг.

ел

с

оо о со

3

4

4-6) прикладываются потенциалы логической единицы,

Предлагаемый счетчик (например шестиразрядный) при различных значениях Р функционирует следующим образом.

При нулевых исходных состояниях триггеров счетчиков (000000), когда к шинам тактирования поступает первый тактовый импульс, независимо от значения Р, триггеры их первых разрядов устанавливаются в единичные состояния (100000). Это соответствует десятичному числу 1.

Второй тактовый импульс переключает триггеры первых разрядов счетчиков в нулевое состояние, а триггеры вторых разрядов - в единичные состояния (010000). Это соответствует десятичному числу 2. Последующие тактовые импульсы приводят к формированию в счетчиках определенных кодов, соответствующих последующим десятичным числам ряда натуральных чисел (3, 4, 5,...).

Однако каждому из этих десятичных чисел в счетчиках, в зависимости от значения Р, соответствуют различные кодовые комбинации. Это связано с тем, что при (фиг. 4 и 7) разряды шестиразрядного счетчика имеют вес, соответствующий числам минимальных 1-кодов Фибоначчи (1, 2, 3, 5, 8, 13), при (фиг. 5 и 8) - числам минимальных 2-кодов Фибоначчи (1, 2, 3, 4, 6, 9), при (фиг. 6 и 9) - числам минимальных 3-кодов Фибоначчи (1,2, 3, 4, 5, 7).

Таким образом, предлагаемый счетчик импульсов в минимальных Р-кодах Фибо0

5

0

5

0

5

наччи (, 2, 3, ...) имеет более простую схему и повышенную регулярность структуры, что позволяет наращивание разрядности с любым числом, а также микроминиатюризацию путем выполнения гибридной или интегральной микросхемы.

Формула изобретения

Счетчик импульсов в Р-кодах Фибоначчи (, 2, 3, ...), содержащий в каждом разряде элемент памяти, элемент ИЛИ, элемент И, шину тактирования, соединенную с синхровходом элемента памяти, отличающийся тем, что, с целью упрощения и повышения регулярности логической структуры, каждый разряд дополнительно содержит Р+1 управляющих входов, первый и второй управляющие выходы, Р элементов И и Р элементов НЕ, а элемент памяти выполнен в виде IK-триггера, причем первый и второй управляющие выходы соединены соответственно с выходом элемента ИЛИ и инверсным выходом триггера, I- и К-входа- ми триггера, последующие Р управляющих входов - с соответствующими Р-ми I- и К- входами триггера и с входом соответствующего элемента НЕ, прямой выход триггера соединен с первым входом элемента ИЛИ, а инверсный выход триггера и выход Р-го элемента НЕ - с соответствующими входами Р-го элемента И, выходы Р-х элементов И соединены с соответствующими входами элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов в минимальных Р-кодах Фибоначчи | 1991 |

|

SU1786657A1 |

| Счетчик импульсов в р-кодах Фибоначчи | 1987 |

|

SU1443168A1 |

| Счетчик импульсов в максимальных Р-кодах Фибоначчи | 1988 |

|

SU1511861A1 |

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Синхронный десятичный счетчик | 1989 |

|

SU1661994A1 |

| Счетчик импульсов в кодах Фибоначчи | 1990 |

|

SU1762408A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1780188A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1990 |

|

SU1720157A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1800612A1 |

Использование: изобретение относится к вычислительной технике и может быть использовано для пересчета импульсов с непосредственным представлением результатов в минимальных Р-кодах Фибоначчи, Сущность изобретения: счетчик импульсов в Р-кодах Фибоначчи содержит в каждом разряде элемент памяти, элемент И, шину тактирования, соединенную с синхровхо- дом элемента памяти. Для достижения поставленной цели счетчик импульсов в каждом разряде дополнительно содержит (Р+1) управляющие входы, первый и второй управляющие выходы, Р элементов И и Р элементов НЕ, а элемент памяти выполнен в виде IK-тригтера. 9 ил.

иг, 3 ()

С ъ

Авторы

Даты

1993-03-23—Публикация

1991-04-19—Подача