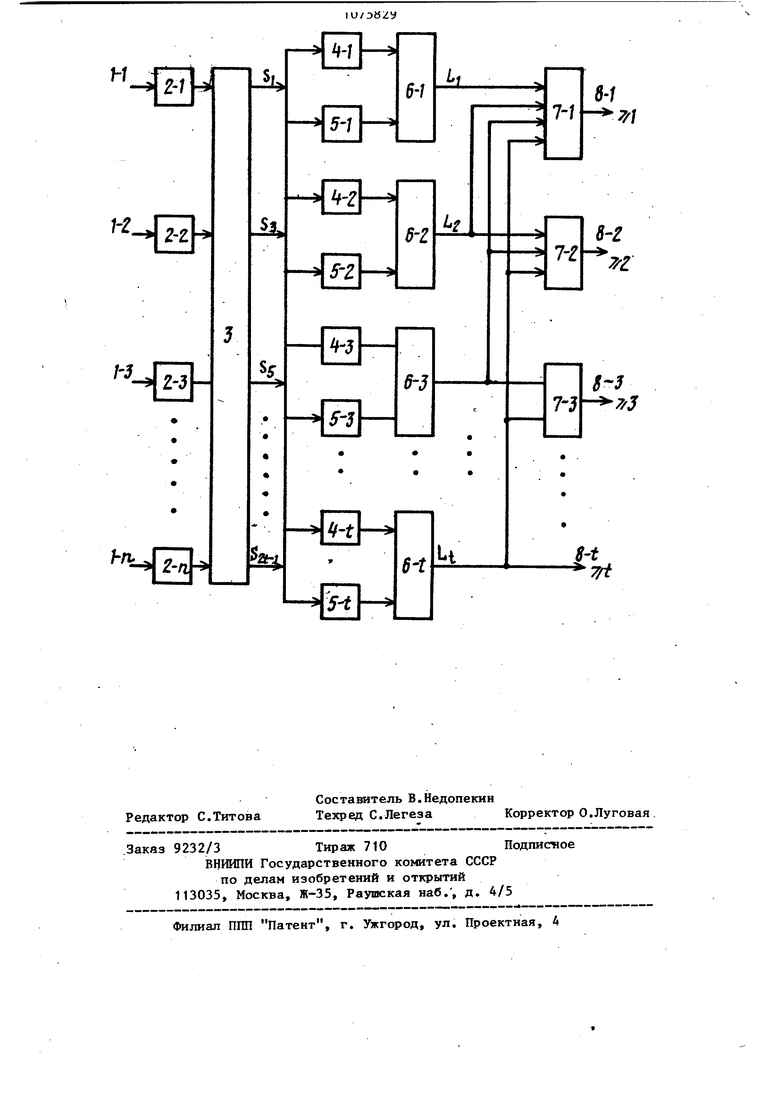

11 Изобретение относится к ядерной электронике и вычислительной технике, . Известно устройство для цифрового отбора t ядерных частиц из N час тиц, построенное по последовательной схеме Л . Такое устройство может строиться без ограничений на увеличение числа входов. Однако оно имеет малое быст родействие, обусловленное тем, что задержка сигнала на выходе устройст ва зависит от числа входов Наиболее близким техническим реш нием к описываемому изобретению является устройство для отбора t ядер ных частиц из N частиц, основанное на цифровом суммировании количества пришедших сигналов от детектора заряженных частиц, оно содержит п уси лителей-формир ователей, t-1 групп элементов ИЛИ и t выходных каналов 2j . Хотявеличина задержки в таком устройстве меньше, она тагсже зависит от числа входов устройства и, например, при п 50 величина задержки может оказаться слишком большой, что недопустимо в устройствах с наносекундным быстродействием. Целью изобретения является повышение быстродействия устройства. Указанная цель достигается тем, что в устройство для отбора t ядерных частиц из N частиц, содержащее п усилителей-формирователей t-1 групп элементов ШШ и t выходных ка налов, введены группа схем проверки на четность и t арифметических блоков, каждый из которых включает бло умножения, блок возведения в степен элементов поля Галуа GF (2 ) и сумматор по модулю два, причем, выходы усилителей-формирователей соединены с входами группы схем проверки на четность в соответствии с матрицей проверочных соотношений кода БоузаЧоудхури, а входы блоков умножения и возведения элементов поля Галуа GF (2) в степень соеданены с соответствующими им выходами группы схем проверки на четность, а их выходы соединеныс входами соответствующих им сумматоров по модулю два, выходы которых подключены ко входам cooтвeтcтвyюшJ x им групп элементов ИЛИ, а остальные входы грзтп элемен тов ИЛИ соединены с выходами суиматоров по модулю два последующих арифметических блоков. В описаний использованы следующие обозначения: а, а а, элементы конечного поля (поля Галуа) QF (2 ) - стандартное обозначение поля Гапуа, где 2 - основание двоичной системы счисления; m - степень непроводимого полинома, при помощи которого строятся элементы поля Галуа: t - количество сигналов, поступивших одновременно на вход устройства п - количество входов уст- ройства, причем; т.е. N п , Sg ,..., Sjj, . - элементарные симметрические функции. На чертеже представлена блок-схема описываемого устройства. Устройство содержит информационные входы (1.1-1.п), усилители-формирователи (2.1-2.п) группы схем проверки на четность 3,t арифметических блоков, состоящих из t блоков умножения (4.1-4.t) элементов поля QF (2), t блоков воздействия элементов поля QF (2) в степень (5.15.t) и t блоков суммирования по модулю два (6.1-6.t) блоков элементов ШШ (7.1-7,t) и выходы устройства (8.1-8.t). Устройство работает следукицим образом. Импульсы от многоканального детектора ядерных частиц (на чертеже не показан) или от какого-нибудь другого источника сигналов по информационным входам (l.1-1.n) поступают на входы усилителей-формирователей (2.1-2.п). После усиления и формирования импульсы поступают на входы группы схем проверки на четность. Правило соединения выходов усилителей формирователей с входами группы схем проверки на четность 3 задаются при помощи матрицы связей Н, которая аналогична матрице проверочньк соотношений кода Боуза-Чаудхури, известного из теории кодирования. При заданном числе m и поле F (2) эти связи однозначны. Другие способы описания таких связей неизвестны, так как они изменяются с; изменением числа m и носят нерегулярньвЧ характер.

Итак, матрица связей Н имеет вид:

1

1

,Н-1

Н

аЗ(-.. а - гдеК

На выходах группы схем проверки на четность 3 формируются элементарный симметрические функции S , S. ,

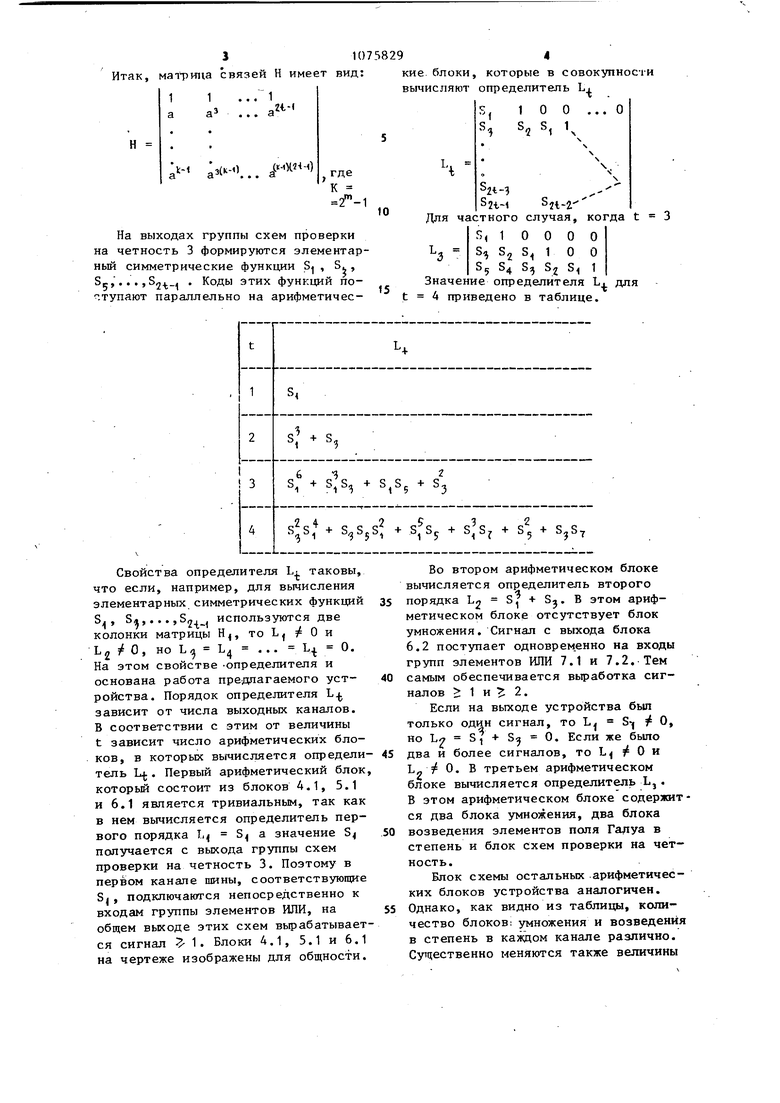

S 2-t-i ОДЬ этих функций по.тупают параллельно на арифметические. блоки, которые в совокупносчИ вычисляют определитель Li

I 00 ... О

f

S. 1 5

L.

%-з

SjtM

Sn-2 3 частного случая, когда t

( 1 0000

S,

S2 S4

S 1 О

S: S S

Значение определителя L, для 4 приведено в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отбора @ ядерных частиц | 1987 |

|

SU1497597A1 |

| Устройство для определения множественности при регистрации ядерных частиц | 1987 |

|

SU1532893A1 |

| Процессор для определения координат частиц в координатной пропорциональной камере | 1979 |

|

SU875408A1 |

| Устройство для определения координат и значений кластеров при регистрации ядерных частиц | 1988 |

|

SU1571620A1 |

| Устройство для формирования имитостойких последовательностей сигналов сложной формы | 1984 |

|

SU1203533A1 |

| Устройство для декодирования кода | 1983 |

|

SU1190525A1 |

| Устройство для умножения произвольных элементов полей Галуа GF(р @ ) | 1979 |

|

SU900281A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

УСТРОЙСТВО ДЛЯ ОТБОРА t ЯДЕРНЫХ ЧАСТИЦ ИЗ N ЧАСТИЦ, содержащее п усилителей-формирователей, t-1 групп элементов КПП и i выходных каналов, отличающеес я.тем, что, с целью увеличения быстродействия, в устройство введены группа схем проверки на четность и t арифметических блоков, каядый из которых . включает блок умножения, блок возведения в степень элементов попя Галуа GF

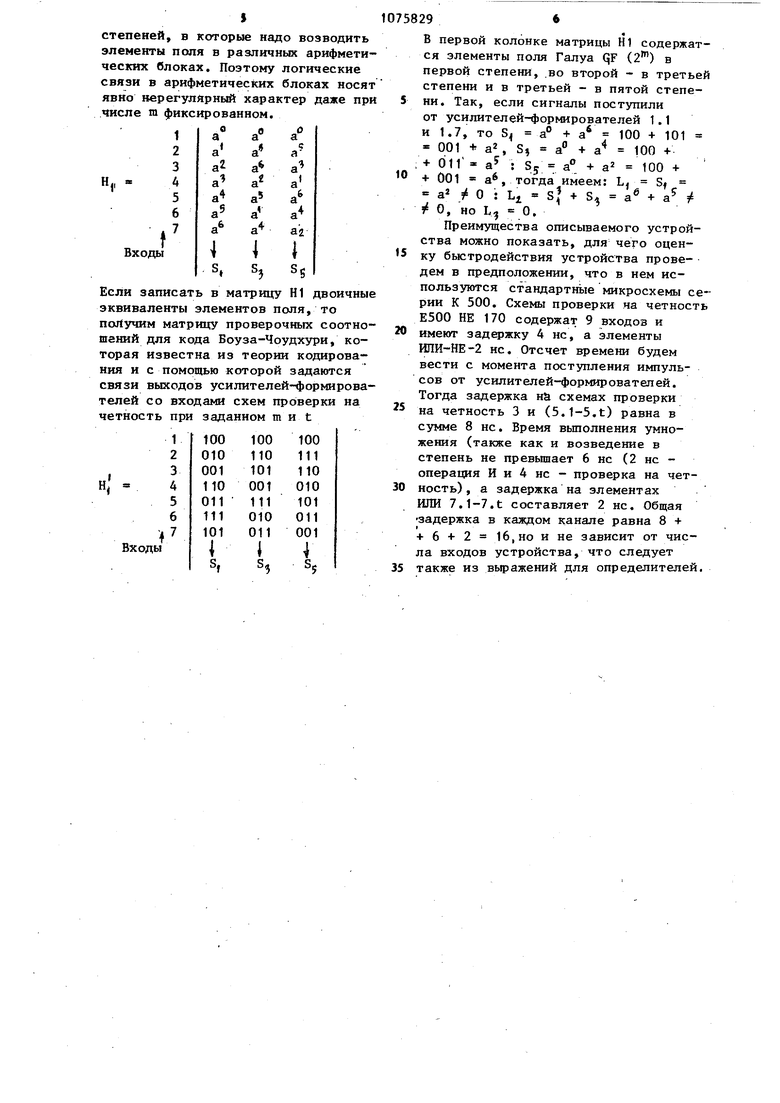

Свойства определителя Li таковы, что если, например, для вычисления элементарных симметрических функций ,. .., S используются две колонки матрицы Н, то L О и Lg О, но L L ... Ц 0. На этом свойстве -определителя и основана работа предпагаемого устройства. Порядок определителя L зависит от числа выходных каналов. В соответствии с этим от величины t зависит число арифметических блоков, в которых вычисляется определи тель Ц. Первый арифметический блок который состоит из блоков 4.1, 5.1 и 6,1 является тривиальным, так как в нем вычисляется определитель первого порядка Т. S а значение 84 получается с выхода группы схем проверки на четность 3. Поэтому в первом канале шины, соответствующие Sj, подключаются непосредственно к входам группы элементов ИЛИ, на общем выходе этих схем вырабатывает ся сигнал - 1. Блоки 4.1, 5.1 и 6. на чертеже изображены для общности Во втором арифметическом блоке вычисляется определитель второго порядка L2 S + Si. В этом арифметическом блоке отсутствует блок умножения. Сигнал с выхода блока 6.2 поступает одновременно на входы групп элементов ИЛИ 7.1 и 7.2. Тем самым обеспечивается выработка сигналов 5 1 и 2. Если на выходе устройства бып только один сигнал, то Lj S-j э О, S, + S 0. Если же бьло j и 1 й два и более сигналов, то L j О и L- 0. В третьем арифметическом блоке вычисляется определитель L,. В этом арифметическом блоке содержится два блока умножения, два блока возведения элементов поля Галуа в степень и блок схем проверки на четность. Блок схемы остальных .арифметических блоков устройства аналогичен. Однако, как видно из таблицы, количество блоков: умножения и возведения в степень в каждом канале различно. Сучественно меняются также величины степеней, в которые надо возводить элементы поля в различных арифметических блоках. Поэтому логические связи в арифметичес1сих блоках носят явно нерегулярный характер даже при числе m фиксированном. 4I Если записать в матрицу HI двоичные эквиваленты элементов поля, то получим матрицу проверочных соотношений для кода Боуза-Чоудхури, которая известна из теории кодирования и с помощью которой задаются связи выходов усилителей-формирователей со входами схем проверки на четность при заданном m и t 1075 5 О 5 20 25 30 35 9 В первой колонке матрицы HI содержатся элементы поля Галуа QF (2) в первой степени, .во второй - в третьей степени и в третьей - в пятой степени. Так, если сигналы поступили от усилителей-формирователей 1.1 и 1.7, то S а° + а 100 + 101 001 а, S, а + а 100 + + 011 а : 55; а° а 100 + + 001 а, тогда имеем: L, Sf а У О : Li sj -I- S а + а О, но L 0. Преимущества описываемого устройства можно показать, для чего оценку быстродействия устройства проведем в предположении, что в нем используются стандартньте Микросхемы серии К 500. Схемы проверки на четность Е500 НЕ 170 содержат 9 входов и имеют задержку 4 не, а элементы ИЛИ-НЕ-2 НС. Отсчет времени будем вести с момента поступления импульсов от усилителей-формирователей. Тогда задержка н& схемах проверки на четность 3 и (5.1-5.t) равна в сумме 8 НС. Время вьшолнения умножения (также как и возведение в степень не превышает 6 не (2 не операция И и 4 не - проверка на четность), а задержка на элементах ИЛИ 7.1-7.t составляет 2 не. Общая задержка в каждом канале равна 8 + + 6 + 2 16, но и не зависит от числа входов устройства, что следует также из выражений для определителей.

-/

2-/ J и

iu/эигу

J-f

е-/

7-/

/

k

Я-2

7-2

М

/-J

2-3

5-J

-5

7-5

U

5-Г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Басиладзе С.Г | |||

| и др | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Насос | 1917 |

|

SU13A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Басиладзе С.Г | |||

| и др | |||

| Много.входовая мажоритарная схема совпадений большей кратности с цифровым отбором | |||

| Предприят | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1984-12-23—Публикация

1982-02-19—Подача