торого соединен с выходом первого сумматора, второй вход - с выходом второго сумматора, а третий вход - с вторым выходом корректора, управляющий вход которого соединен с выходом блока обнаружения ошибок, выход умножителя подключен к пятому входу блока отказа от декодирования.

2,Устройство по п. 1, отличающее с я тем, что корректор содержит блок элементов И-ИЛИ-НЕ, сумматор блок инверторов, первьй и второй дешифраторы старших разрядов, первый и второй дешифраторы младших разрядов, управляющие входы которых объединены

и соединены с управляющим входом корректора, первьй корректирующий вход которого соединен с информационными входами первых дешифраторов младшего и старшего разрядов, а второй корректирующий вход - с информационными входами вторых дешифраторов младшего и старшего разрядов, выходы дешиф- раторов через блок элементов И-ИЛИ-НЕ соединены с первым входом сумматора, второй вход которого соединен через блок инверторов с информационным входом корректора, а выход - с первым выходом корректора, выходы дешифраторов соединены с вторым выходом корректора.

3.Устройство по пп. 1 и 2, отличающееся тем, что вычислитель обратных корней содержит дешифраторы младшего и старшего разрядов, блок элементов И-ИЛИ-НЕ, блок элементов И-НЕ и дешифратор нуля, вход которого соединен с выходом блока элементов И-НЕ и первым выходом вычислителя обратных корней, вход которого соединен с входами дешифраторов младшего и старшего разрядов, выходы которых соединены с соответствующими входами блока элементов.. И-ИЛИ-НЕ, выход которого соединен с входом блока элементов И-НЕ, выход дешифратора нуля подключен к второму выходу вычислителя обратных корней.

4.Устройство по пп. 1-3, отличающееся тем, что формирователь исключенных кодов содержит первый, второй, третий и четвертый элементы И и первьй и второй элементы ИЛИ, входы первого и второго элементов И соединены соответственно

с первьм и вторым входами формирователя исключенных кодов, а выходы с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы которых, а также первые и вторые входы третьего и четвертого элементов И подключены к третьему входу формирователя исключенных кодов, выходы третьего и четвертого элементов И соединены с третьими входами соответственно первого и второго элементов ИЛИ, выходы которых соединены с выходом формирователя исключенных кодов.

5.Устройство по пп. 1-4, о т л ичающееся тем, что корректор четности содержит первьй и второй элементы И и сумматор, первьй вход которого соединен с первым входом корректора четности, второй вход которого соединен с первым входом певого элемента И, третий и четвертьй входы корректора четности соединены

с соответствующими входами второго элемента И, выход которого подключен к второму входу первого элемента И, выходы элементов И и второй и третий входы корректора четности соединены с соответствующими вторыми входами сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования составного корректирующего кода | 1983 |

|

SU1229969A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| ВЫЧИСЛИТЕЛЬ ОШИБОК ПОМЕХОУСТОЙЧИВОГО ДЕКОДЕРА | 1999 |

|

RU2152130C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

| Декодирующее устройство для исправления ошибок | 1985 |

|

SU1295531A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КАСКАДНОГО КОДА РИДА-СОЛОМОНА | 1993 |

|

RU2036512C1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Вычислитель ошибок помехоустойчивого декодера | 1985 |

|

SU1295532A1 |

| Кодек каскадного блочного кода | 1985 |

|

SU1338075A1 |

1. УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ КОДА, содержащее первый и второй сумматоры, вычислитель.четности, блок отказа от декодирования, умножитель, формирователь кодов, корректор, блок обнаружения ошибок к пер- вьй блок сумматоров, вход которого объединен с первым входом вычислителя четности, информационным входом корректора н соединен с первым входом устройства, а первый выход соединен с первыми входами блока обнаружения ошибок, формирователя кодов и первого сумматора, второй вход вычислителя четности соединен с вторым входом устройства, а выход - с первым входом блока отказа от декодирования, первьй выход корректора является первым выходом устройства, выход блока отказа от декодирования является вторым выходом устройства, выход первого сумматора соединен с первым корректирующим входом корректора, второй корректирующий вход которого соединен с выходом второго сумматора, к входу которого подключей выход формирователя кодов, выход блока обнаружения ошибок соединен с вторым входом блока отказа от декодирования и является третьим выходом устройства, отличающееся тем, что, с целью повышения быстродействия и достоверности обрабатываемой информации, в него введены второй и третий блоки сумматоров, вычислитель обратных корней, формирователь исключенных кодов и корректор четности, первый вход которого объединен с вторым входом устройства, второй вход объединен с вторым входом блока обнарз ения ошибок и соединен с выходом вычислителя четности, третий вход соединен с выходом блока обнаружения ошибок, четвертый вход с выходом блока отказа от декодирования, а выход является четвертым выходом устройства, первый вход второго блока сумматоров объединен с входами первого и третьего блоков сумматоров, второй вход соединен с вторым выходом первого блока сумматоров, а выход - с первым входом умножителя и вторым входом формирователя кодов, выход третьего блока сумматоров соединен с третьим входом блока обнаружения ошибок и вторым входом умножителя, третий вход которого подключен к первому выходу первого блока сумматоров, а выход - к входу вычислителя обратных корней, первый выход которого соединен с третьим входом формирователя кодов, выход которого соединен с вторым входом первого сумматора, второй выход вычислителя обратных корней соединен с третьим входом блока отказа от декодирования, четвертый вход которого подключен к выходу формирователя исключенных кодов, первьй вход ко

Изобретение относится к вычислительной технике и может быть использовано в системах обработки, хранения и передачи информации, в частности в быстродействующих запоминающих устройствах с параллельной записью и считыванием.

Целью изобретения является повышение быстродействия путем ускоренной вьщачи кодового слова при отсутствии ошибок и достоверности обрабатываемой информации за счет использования, при отборе от декодирование}, фактов отсутствия решения квадратного уравнения и наличия исключенных локаторов,

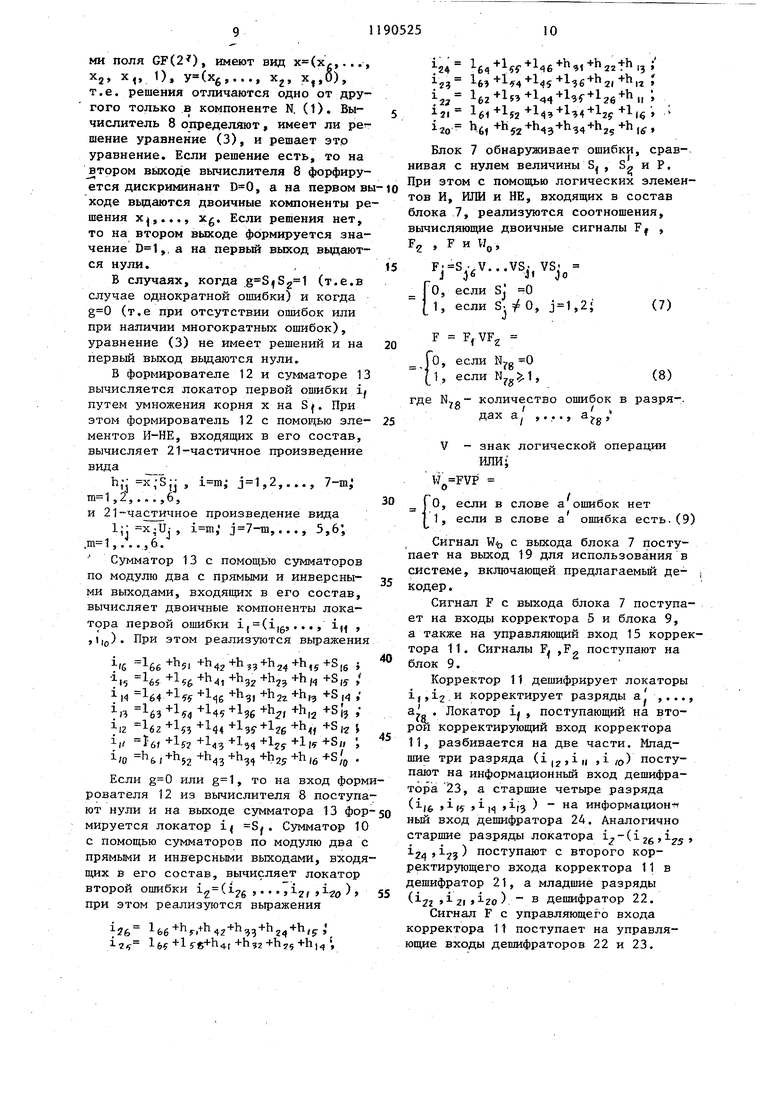

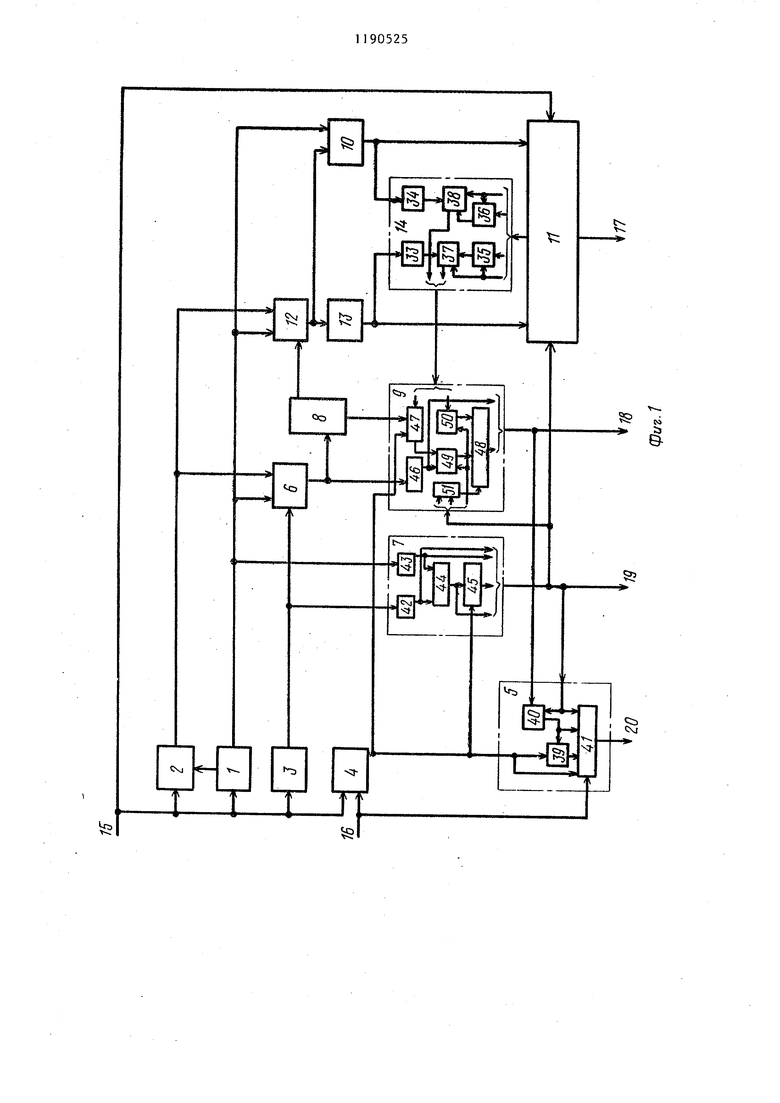

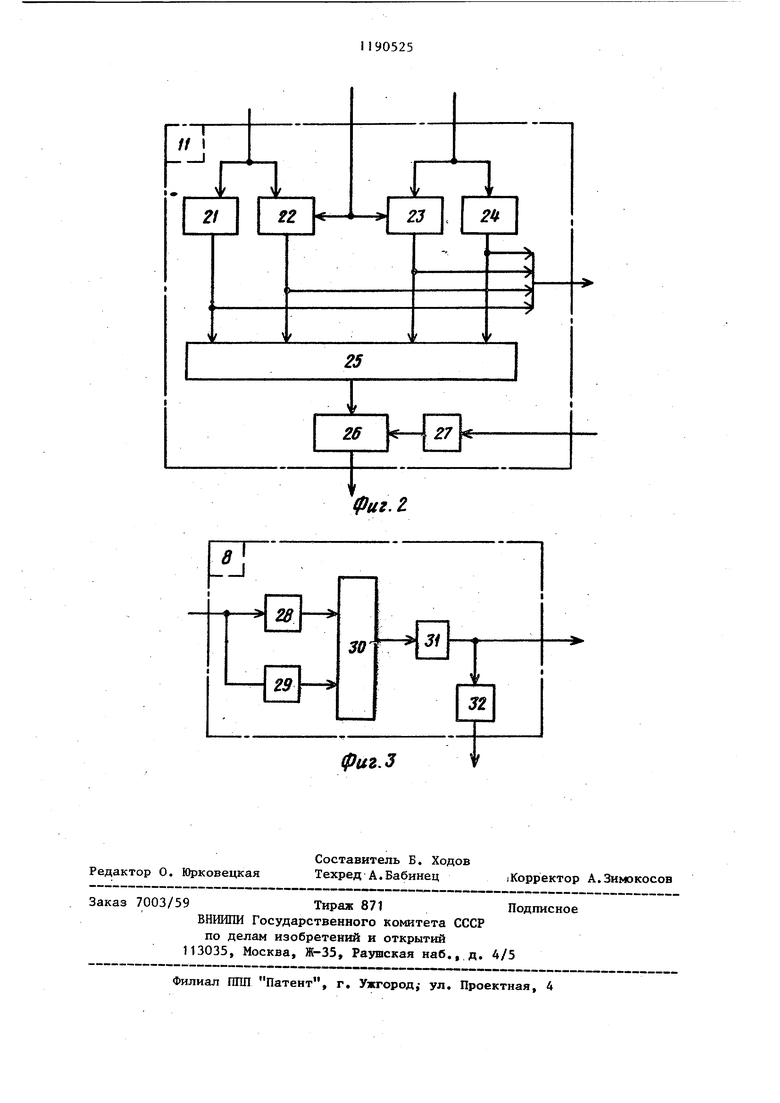

На фиг. 1 при ведена блок-схема устройства для декодирования кода; на фиг. 2 - блок-схема корректора; на фиг. 3 - блок-схема вычислителя обратньгх корней.

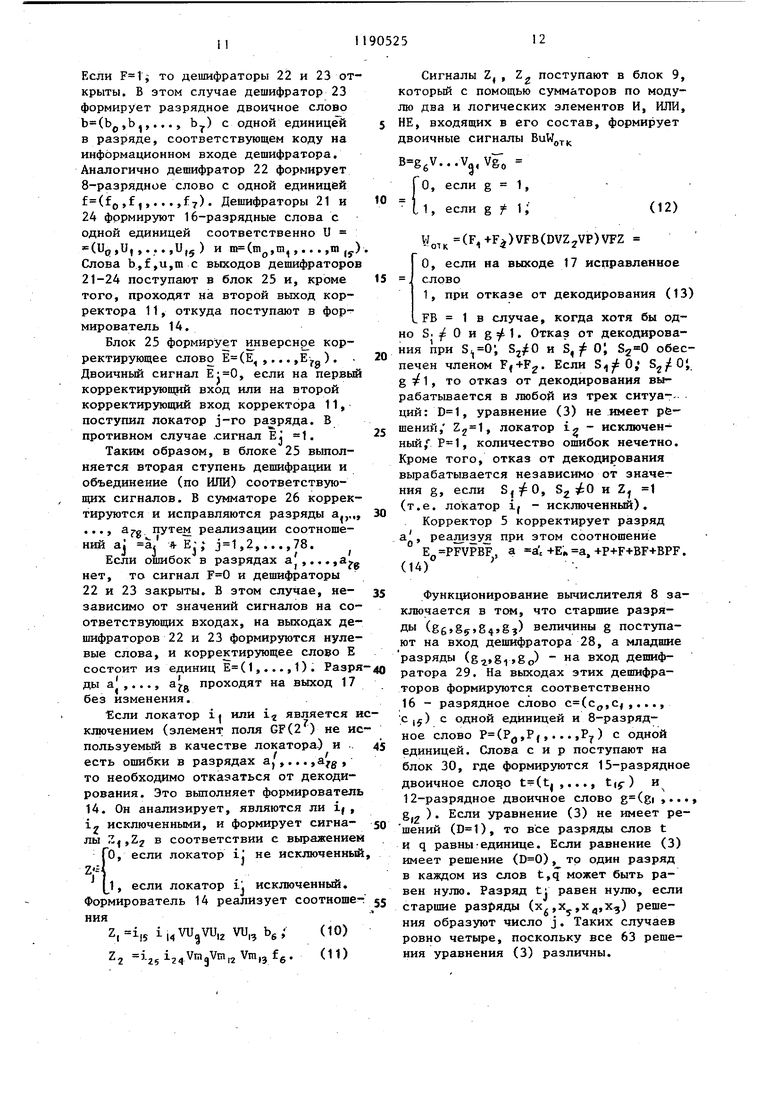

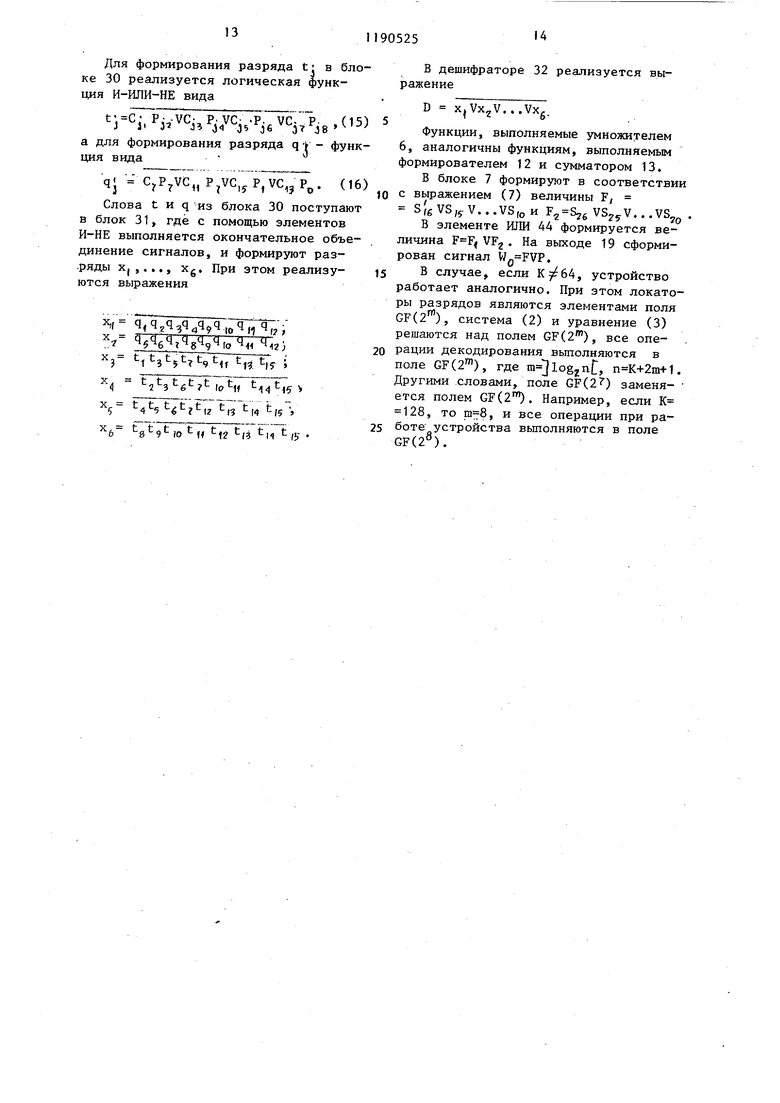

Устройство для декодирования кода содержит первый блок 1 сумматоров, второй блок 2 сумматоров, третий бло 3 сумматоров, вычислитель 4 четности корректор 5 четности, умножитель 6, блок 7 обнаружения ошибок, вычислитель 8 обратных корней, блок 9 отказа от декодирования, первый сумматор 10, корректор 11, формирователь 12 кодов, второй сумматор 13, формирователь 14 исключенных кодов, первый вход 15, второй вход 16, первьй выход 17, второй выход 18, третий выход 19, четвертый выход 20. Корректор 11 содержит первый дешифратор 21 старшихразрядов, первый дешифратор 22 младших разрядов второй дешифратор 23 младших разрядов, второй дешифратор 24 старших разрядов, блок 25 элементов И-ИЛИ-НЕ, сумматор 26 и инвертор 27. Вычислитель 8 обратных корней содержит дешифратор 28 старших разрядов, дешифратор 29 младших разрядов, блок 30 элементов И-ИЛИ-НЕ, блок 31 эле.ментов И-НЕ и дешифратор 32 нуля. Формирователь „14 исключенных кодов содержит первый, второй, третий и четвертый элементы И 33-36 И и первый и второй элементы ИЛИ 37 и 38. Корректор 5 четности содержит первый и второй элементы И 39 и 40 и сумматор 41. Блок 7 обнаружения ошибок содержит элементы ИЛИ 42-45, а блок 9 отказа от декодирования - элементы ИЛИ 46-48, элементы И 49 и 50 и сумматор 51. Одной связи фиг. 1-3 соответствует несколько электрических связей. Например, от входа 15, выхода 17 и выходов блока 25 отходят шины шириной t7 -1 разрядов. От первого выхода блока 1 и от выходов бло ка 3 и умножителя 6, сумматора 10, сумматора 13 отходят 2т-разрядные шины (т-разрядов - прямые значения сигналов иmразрядов - инверсные значения) . От первого выхода вьгчислителя 8 отходи г (т-1)-разрядная шина. От выхода формирователя 12 отходит 42-разрядная шина.

Устройство работает следующим образом.

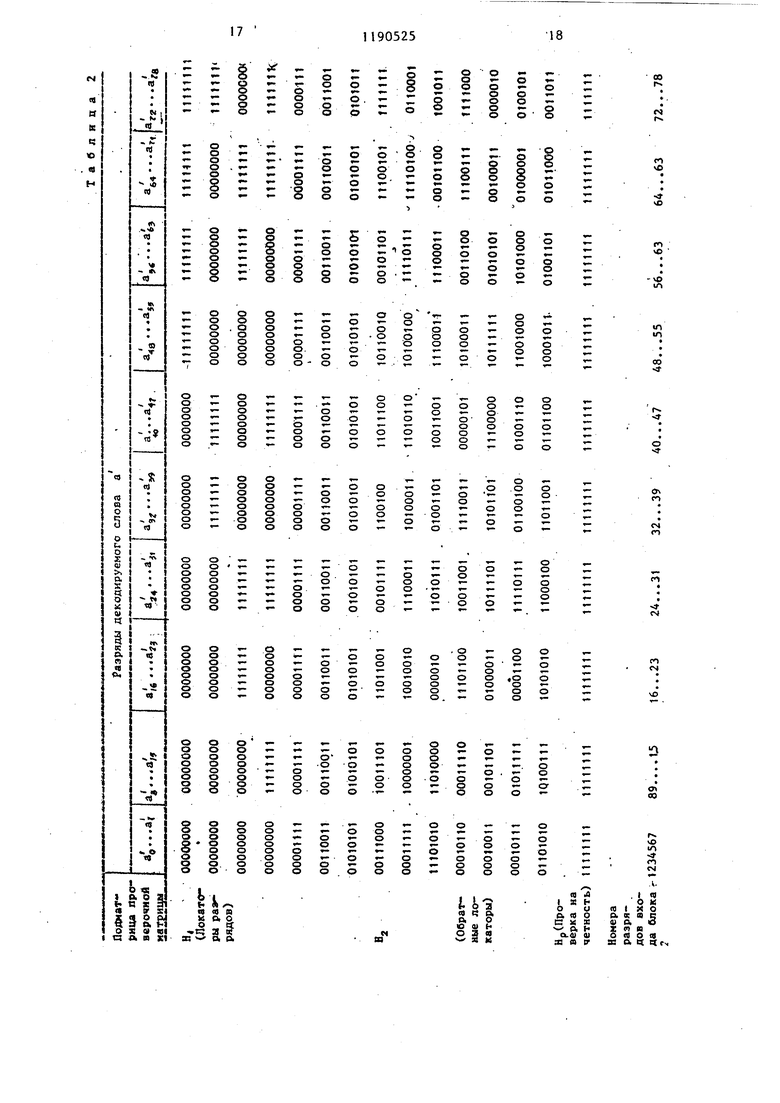

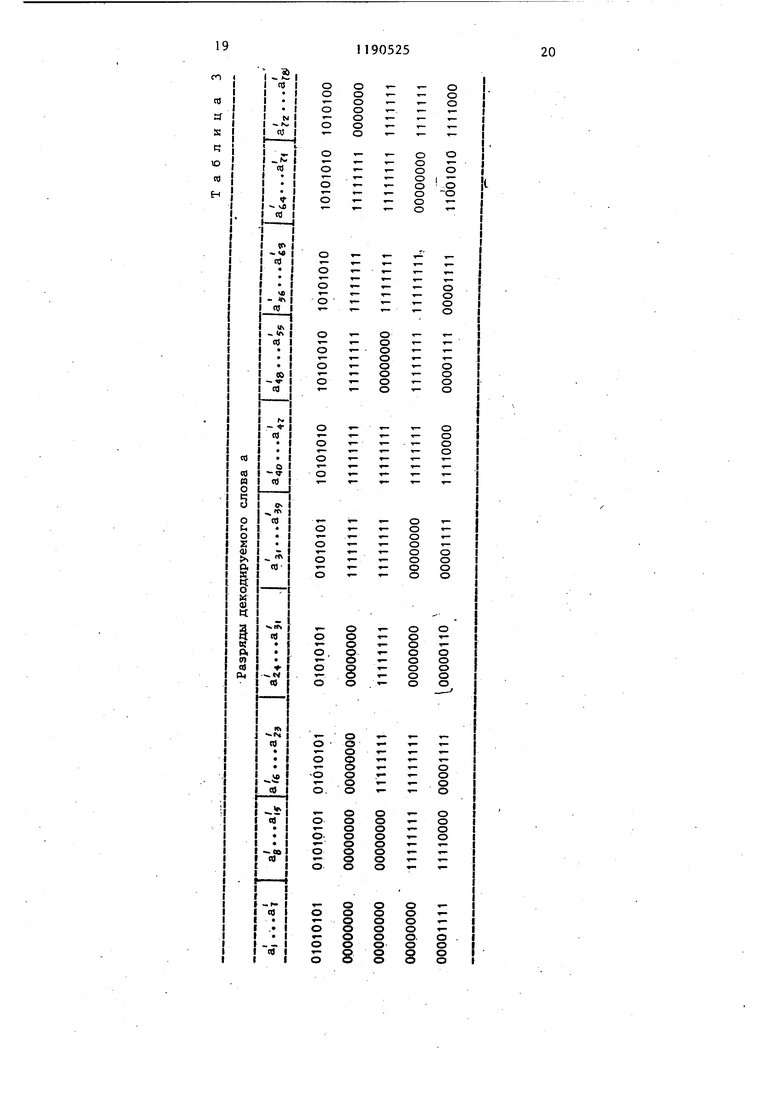

Работа устройства описана для случая, когда количество информационных разрядов , а длина декодируемого кода п t79, т.е. 15 разрядов являются проверочньми. Информация поступает в устройство и передается между блоками в параллельной форме. Декодируемое 7-9-разрядное слово а (ао, а|,..., arg), которое, возможно, содержит ошибки, поступает на Входы 15 и 16 устройства. При этом разряд проверки на четность а поступает на вход 16, откуда проходит в вычислитель 4 и корректор 5, а остальные разряды а,, ..., а/ поступают на вход 15, откуда проходят в блоки 1-3, вычислитель 4 и корректор 11.

При работе устройства каждому разряду декодируемого слова а ставится в соответствие локатор разряда, являющийся элементом конечного поля Галуа GF(2 ). Это поле содержит 128 элементов. Элемент N поля GF(2) представляется либо набором из семи двоичных разрядов

N (N,, ..., N, N.),

(1)

либо многочленом N(«) ..

,

где N;e {0,1,

. te - примитивный элемент поля GF(2 ), являющийся корнем многочлена х + х + 1. Знак + здесь и далее обозначает сложение по модулю два (для векторов - поразрядное сложение по модулю два). Для коррекции ошибок в устройстве вычисляются локаторы искаженных разрядов: локатор первой ошибки i , локатор второй ошибки i.

Локаторы ошибок формируются следующим образом. По декодируемому слову а блок 1 вычисляет сумму локаторов ошибок S xii+ig, блок 3 вычисляет сумму обратных локаторов $2

S --+--, вычислитель 4 вычисля1., 12

ет проверку на четность Р. Если S, и , то ошибок в слове а нет. Если S 82 О и , то имеется ошибка в разряде а . Если 5,, Sj/ 0,-g- SgCT.e. 8,) и , то

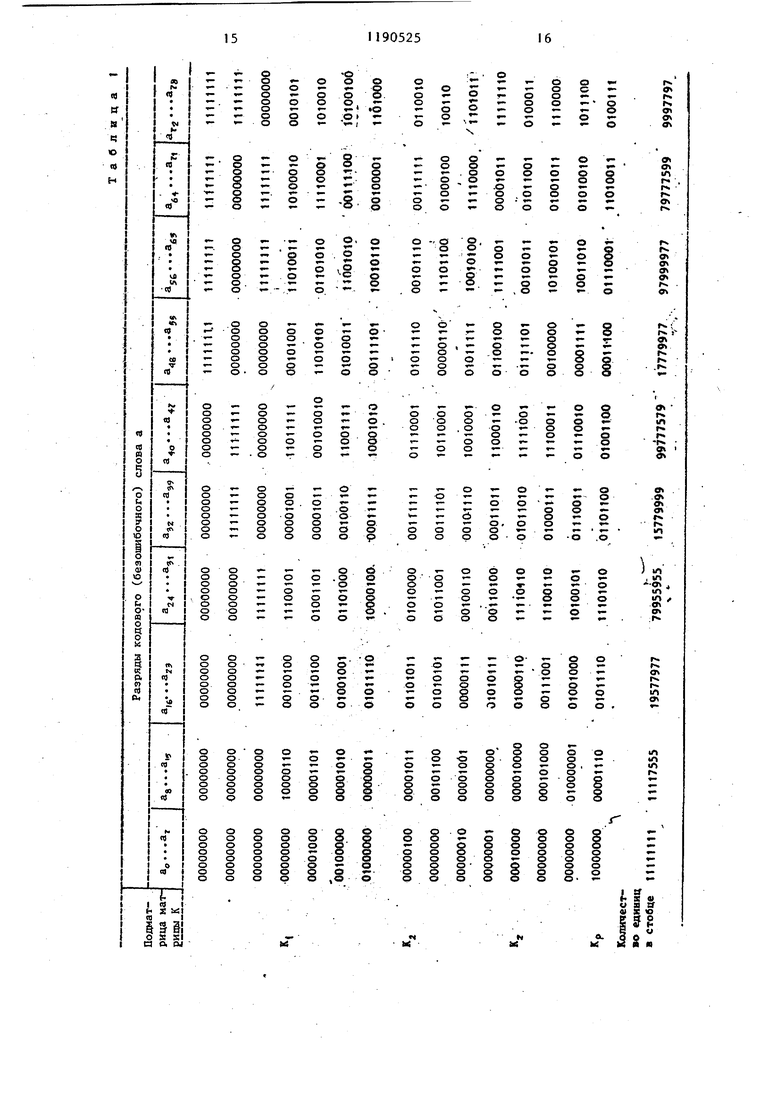

имеется одна ошибка в разряде с лркатором i| S, . Если S, 4f О, , S и , TO имеется ошибка в раз ряде с локатором и,кроме тог ошибка в разряде а . Наконец, если S, О, , и , то пре полагается, что имеются две ошибки в разрядах , ..., а с локаторам i I, i. Во всех остальных случаях (в частности, если 5,, Sg О, или S, 0, , или 8,0, , 5,82/1, ) необходимо отказаться рт декодирования, так как количеств ошибок равно или больше трех. В случае, когда , , S,8jf1, и , локаторы ошибок i, вычисляются путем решения (в умножителе 6, вычислителе 8, сумматоре 10, формирователе 12 и сумматоре 13 системы уравнений над полем GF(2 ) + 12 S, Ч -2 Для решения системы (2) вначале вычисляется корень квадратного урав нения к . 1- О, SjSg. м умножитель-6 формирует При этом , умножая в поле GF(2 ) S величину на 8. Вычислитель 8 по величине обратной свободному члену о нахо 3 дит корень X квадратного уравнения (3) или определяет, что уравнение (3) не имеет решений. В последнем случае устройство отказывается от декодирования. Формирователь 12 и сумматор 13, умножая корень х на 8,формирует ло тор первой ошибки i, х8,. Параллельно, использ.уя промежуточные результаты, формирователь 12 и сумматор 13 формируют локатор вто рой ошибки Г Корректор 11 осуществляет коррек цию искаженных разрядов, используя значения локаторов i j и i. Если ошибка имеется в разряде а она корректируется в корректоре 5. Блок 7 обнаруживает ошибки, срав нивая с нулем величины 8; и 82. Бло 9, используя информацию из корректора 5, блока 7, вычислителя 8 и формироват ля 14 формирует сигнал отказа от декодирования при наличии трехкратных ошибок и фазированных пакетов ошибок длины 4. Декодирование слова а вьтолняется в устройстве с учетом того, что кодовое (безошибочное) слово а (а, а,, ..., ) сформировано с помощью матрицы К, состоящей из трех К,, Kg, Кр подматриц, приведенных в табл. 1. В слове а разряды а, а,..-, .; 40 э,е , а,2 4в проверочные, остальные разряды - а,, ..., Ч 3( ЭЗ , a-jg - информационные. Каждому ;пр о в ер ОЧНОМУ разряду соответствует в матрице К столбец с одной единицейi строка, содержащая эту единицу, указывает (своими единицами), какие информационные разряды участвуют в формировании данного проверочного разряда. Например, , + + ,. .+a-fg i ,,+ a, + .. .+ . . .+ . + а„ + Матрице К при декодировании соответствует проверочная матрица Н, состоящая из трех подматриц Н, Н, Нр и приведенная в табл. 2. (В табл. 2 показано также, что с входа 16 разряд d/l поступает на i-й разряд входа блока 1, ,...,78). Каждый столбец матрицы Н. является локатором соответствующего разряда декодируемого слова а . Локатор разряда представляет собой семиразрядньй двоичньш набор - элемент поля GF(2). Каждый столбец матрицы Hg является элементом поля GF(2), обратным соответствующему локатору, т.е. если столбец матрицы Н| есть элемент 1 поля GF(2 ), то соответствующий, столбец матрицы Н есть элемент тполя GF(2). Матрица Нп является строкой из 79 единиц и обеспечивает проверку на четность декодируемого слова. Блок 1 вычисляет ,(8f6 ,...,8i, ,8,е,) (4) , путем умножения слова (О, а . .., ) на транспонированную матрицу Кц , реализуя при этом (S,j ,...,84 ,) (0, а/,..., )Hj, где Т - знак транспонирования матрицы. Умножение вектора на матрицу реализуется с помощью сумматоров по модулю два которые при необходимости им ют прямые и инверсные.выходы. Напри мер, д;воичные разряды S ,g , 8, форми руются так: S,... , S,y. . . .+a j+ajy+.. ,+afg , т.е. при формировании i-го разряда произведе ния вычисляется сумма по модулю два тех разря;.ов слова а , номера которых соответствуют единичным элементам i-й строки матрицы. В связи с тем, что количество вх дов сумматора по модулю два не прев шает 8 или 9, то при реализации умн жения вектора на матрицу обычно вна чале получают промежуточные суммы А: из 8-9 слагаемых, из которых зат формируют разряды произведения. Так для получения S|6 и 8,5 можно вначале сформировать промежуточные суммы А| 48 « S5 2 96 АЗ 4ч+ ... ; А.4 ...+arg, А а;2+...+а;9, 6 а затем разряды произведения 8f6 А, H-Aj+A +A ; ,-bAg+A4. Блок 3 с помощью сумматоров по модулю два с прямыми и инверсными выходами, входящих в его состав, вычисляет сумму обратных локаторов 8,, являющуюся элементом поля GF(2 17 путем умножения слова (о,а{,..., на транспонированную матрицу 2. Блок 4 с помощью сумматоров по модулю два с прямыми и инверсными выходами.входящих в его состав, вычисляет проверку на четность Р, реа лизует при этом соотношение P(ao,a|,...,a/g) +а, + .. .а I. Блок 2 с целью подготовки умножения в умножителе 6 вычисляет в фо мирователе 12 и сумматоре 13 шесть попарных сумм двоичных компонентов величины 8 j Uj 8,j +8,(j4,); j 1,..., 5, ,6 + При этом величины U2,..., U, ко торые используются в умножителе 6, вычисляются непосредственно по деко дируемому слову одновременно с величиной 84. Это позволяет начать умножение в умножителе 6 сразу же после вычисления 8, Szt что сокращает время декодирования. Вычисление и ,..., Ug вьшолняется в блоке 2 с помощью сумматоров по модулю два путем.умножения слова (о,а ,..,, ) на транспонированную матрицу N4 , приведенную в табл. 3. При этом реализуется соотношение , (Ug, ..., U„ф(o,a...,a;в)(5). Для реализации вьфажения (5) в блоке 2 могут быть использованы промежуточные результаты суммирования А;,-полученные в блоке 1 при реализации выражения (4). Например, Uj А,Aj+A +Aj+Ag. Указанные промежуточные результаты Aj поступают в блок 2 с второго выхода блока 1. С этого же выхода в блок 2 поступают двоичные компоненты величины S, необходимые для формирования тех сумм Uj; которые используются только в формирователе 12. В рассматриваемом случае - это 8( , по которым вычисляется U, 8,, +8|2 Умножитель 6, используя величины U U выполняет в поле GF(2 ) умножение S на Sj, получая величину (gg,.. el ё.о При этом с помощью логических элементов И-НЕ, НЕ и сумматоров по модулю два с прямьв4И и инверсными выходами, входящих в состав умножителя 6, реализуются соотношения. .,+Sg Ug+8;, 8„ +8 - 8 и-1- Э ч 4-Q Q лГСС- 2. го и .Цб -5„ S,, + + &22 12 Sj, 8( , и., +82, и, -f и + - ..- .з- . -If spv sTVFWi s T y ( г 13 g . + S J, S, rt S TSf Jl TUa- sITUs -s,u-,-s, 8( S7gS(( +8gy 8,g , +8, 8,4 + , Величина g обратна свободному члену квадратного уравнения (3). Это уравнение либо имеет два решения х и у, либо не имеет решений. При этом решения х и у, являющиеся элементами поля GF(2), имеют вид х(х,,..., Xj, X,, 1), y(Xg Х, Х,,0), т.е. решения отличаются одно от другого только в компоненте N. (1). Вычислитель 8 определяют, имеет ли perшение уравнение (3), и решает это уравнение. Если решение есть, то на jBTopoM выходе вычислителя 8 форфируется дискриминант , а на первом вы ходе вьщаются двоичные компоненты ре шения х,..., Xg. Если решения нет, то на втором выходе формируется значение ,, а на первый выход вьодаются нули., В случаях, когда (т.е.в случае однократной ошибки) и когда (т.е при отсутствии ошибок или при наличии многократных ошибок), уравнение (3) не имеет решений и на первьй выход выдаются нули. В формирователе 12 и сумматоре 13 вычисляется локатор первой ошибки if путем умножения корня х на Sj. При этом формирователь 12 с помощью элементов И-НЕ, входящих в его состав, вычисляет 21-частичное произведение вида h,- x,-Sjj , ,2,..., 7-m, ,2,...,6, и 21-частичное произведение вида ij ,..., 5,6; .,. .. ,6. Сумматор 13 с помощью сумматоров по модулю два с прямыми и инверсными выходами, входящих в его состав, вычисляет двоичные компоненты лока- тора первой ошибки i.(i -16 М .1 Ю t I , 1 ,) , При этом реализу1отся вьфажения i|6 1бб . +h42 +ll,,+h,,4+h,5 +S,6 i ii5 1б5 +l56 , +h,4 +S,f / i И 1б4 +h,, +S и ; Ьз 1бЗ +l45 +Ь, +h,2 +81, ,iiz -l62+lf3 144+135-+1гб +h;,, +S,2 j 1бг -H +1-13 +IM +1 +1/9 +s,, ; i/o &i+ 52+ti43 3t 2 +( Если или , TO на вход форм рователя 12 из вычислителя 8 поступа ют нули и на выходе сумматора 13 фор мируется локатор i Sj. Сумматор 10 с помощью сумматоров по модулю два с прямыми и инверсными выходами, входя щих в его состав, вычисляет локатор второй ошибки ,,. .,iyi ,1) , при этом реализуются вьфажения ,+Ь42+Ь, 2- I6f+l5-e+h4f +h92+h25+h,. 44 Ч U +iM-l s- l e+hj.+h,, , i- 1.,+1«-ьЬа+1ч -+1ос+Ь„ ; i2r 1б1+152-11Й1 4+12 +1-.6 i-7n ht. +h«+h4a+li44+h,+h Блок 7 обнаруживает ошибки, сравнивая с нулем величины S , S и Р. При этом с помощью логических элементов И, ИЛИ и НЕ, входящих в состав блока 7, реализуются соотношения, вычисляющие двоичные сигналы F , Рг F « о F.S.,V...VS,.,VSj Го, если Sj 0 l, если S 0, j 1,2 (7) F Го, если Nj,g 0 1, если ,(8) где N,o количество ошибок в разря-. о I/ дах а. ,..«, , V - знак логической операции ИЛИ 0,если в слове а ошибок нет 1,если в слове а ошибка есть.(9) Сигнал Wt, с выхода блока 7 поступает на выход 19 для использования в системе, включающей предлагаемьй де- , кодер. Сигнал F с выхода блока 7 поступает на входы корректора 5 и блока 9, а также на управляющий вход 15 корректора 11. Сигналы F. ,F поступают на блок 9. Корректор 11 дешифрирует локаторы i,,12.и корректирует разряды а ,..., а . Локатор ii , поступающий на второй корректирующий вход корректора 11, разбивается на две части. Млад- ™® РИ разряда (i,.,,, ,i /д) поступают на информационный вход дешифратора 23, а старшие четыре разряда (ij i (5 гз ) из. информацион-« ньй вход дешифратора 24. Аналогично старшие разряды локатора (i g, iy,,) поступают с второго корректирующего входа корректора 11 в дешифратор 21, а младшие разряды ( ,12, ,izo), в дешифратор 22. Сигнал F с управляющего входа корректора 11 поступает на управляющие входы дешифраторов 22 и 23.

Если то деимфраторы 22 и 23 открыты, В этом случае дешифратор 23 формирует разрядное двоичное слово Ь(Ьд,Ь,..., Ь) с одной единицей в разряде, соответствующем коду на информационном входе дешифратора. Аналогично дешифратор 22 формирует 8-разрядное слово с одной единицей f(fo,f,,,.., Дешифраторы 21 и 24 Формируют 16-разрядные слова с одной единицей соответственно U (UQ,U,,...,U,5 ) и m(m,m,.. . ,m ,у) Слова b,f,u,m с выходов дешифраторов 21-24 поступают в блок 25 и, кроме того, проходят на второй выход корректора 11, откуда поступают в формирователь 14.

Блок 25 формирует инверснре корректирующее слово Е(Е, ,... ,Еу ) . . Двоичный сигнал , если на первый корректирующий вход или на второй корректирующий вход корректора 11, поступил локатор j-ro разряда. В противном случае .сигнал Ej 1.

Таким обраэом, в блоке 25 вьтолняется вторая ступень дешифрации и объединение (по ИЛИ) соответствующих сигналов. В сумматоре 26 корректируются и исправляются разряды а.,.,, ..., путем реализации соотношений aj а, Е:; ,2,...,78.

J J J/ f

Если ошибок в разрядах а ,,

е

нет, то сигнал и дешифраторы 22 и 23 закрыты. В этом случае, независимо от значений сигналов на соответствующих входах, на выходах дешифраторов 22 и 23 формируются нулевые слова, и корректирующее слово Е состоит из единиц Е(1,...,1). Разря ды а| ,..., aj.g проходят на выход 17 без изменения.

Если локатор г или i является иключением (элемент поля GF(2 ) не используемый в качестве локатора) и .. есть ошибки в разрядах aj,...,, то необходимо отказаться от декодирования. Это выполняет формирователь 14. Он анализирует, являются ли ij, 1„ исключенными, и формирует сигналы Z ,2 в соответствии с выражением

го,

если локатор ij не исключенный

П-. если локатор ij исключенный.

Формирователь 14 реализует соотношения

Z, 1,5 L,VUgVU,2 VU,, bg,- (10)

Zj i..,Vm,fg, (11)

Сигналы Z , Z поступают в блок 9, который с помощью сумматоров по модулю два и логических злементов И, ИЛИ, НЕ, входящих в его состав, формирует двоичные сигналы BuW

...v,vi;

(о, если g 1, 1, если g ;« 1;(12)

W(F,+F)VFB()VFZ

0,если на выходе 17 исправленное слово

1,при отказе от декодирования (13

FB 1 в случае, когда хотя бы одно S. О и . Отказ от декодирования при и S, 5 о; обеспечен членом . Если S 0; , g 1 1, то отказ от декодирования вырабатывается в любой из трех ситуа-- ций: , уравнение (3) не имеет решений, , локатор iy - исключенный ,, количество ошибок нечетно. Кроме того, отказ от декодирования вырабатывается независимо от значения g, если , S и Z| 1 (т.е. локатор ij - исключенный).

Корректор 5 корректирует разряд а , реализ у при этом соотношение

Е PFVPBF, а а . +Е а, +F+F+BF+BPF. (14)

Функционирование вьиислителя 8 заключается в том, что старшие разряды (g6,g,) величины g поступают на вход дешифратора 28, а младшие разряды (gi,gi,go) «а вход дешифратора 29. На выходах этих дешифраторов формируются соответственно 16 - разрядное слово c(c,c,,..., с ij) с одной единицей и 8-разрядное слово Р(Рд,Р(,...,Р) с одной единицей. Слова сир поступают на блок 30, где формируются 15-разрядное

двоичное слово t(tj ) и

12-разрядное двоичное слово g(gi g,2 ) Если уравнение (3) не имеет решений (), то все разряды слов t и q равныединице. Если равнение (3) имеет решение (), то один разряд в каждом из слов t,q может быть равен нулю. Разряд tj равен нулю, если старшие разряды (х,Ху,х,Хз) решения образуют число j. Таких случаев ровно четыре, поскольку все 63 решения уравнения (3) различны. Для формирования разряда t- в б ке 30 реализуется логическая функция И-ИЛИ-НЕ вида ..Pj7V jeVC5,Pje а для формирования разряда q г - фу ция вида ,VC,,,,P,VC,3P, Слова t и q из блока 30 поступа в блок 31, где с помощью элементов И-НЕ выполняется окончательное объ динение сигналов, и формируют разXg. При этом реализу.ряды X, ются выражения ( q q q q gyqio figf 7 ) Xj t, tjtjt tg t, t tjj. ; 6 7 X t,t,t 4 u с L L , L , - 14 - /5 -9 (0 - fl -I (Э И t (у 6 t, В дешифраторе 32 реализуется выражениеD XjVx2V,..VXg. функции, выполняемые умножителем 6, аналогичны функциям, выполняемым формирователем 12 и сумматором 13. В блоке 7 формируют в соответствии с выражением (7) величины F/ s,eVS,V..,VS,oH F2 Sj6VS 5V..,VSyp . В элементе ИЛИ 44 формируется величина VF2 , На выходе 19 сформирован сигнал , В случае, если К , устройство работает аналогично. При этом локаторы разрядов являются элементами поля GF(2 ), система (2) и уравнение (3) решаются над полем GF(2), все операции декодирования выполняются в поле GF(), где ,nt, n K+2m+1. Другими словами, поле GF(2) заменя- ется полем GF(), Например, если К 128, то , и все операции при работе устройства вьшолняются в поле GF(2).

фиг.З

fpui. i

| Модульная система для коммутации кабельных линий электропередачи 6-10 кВ | 2023 |

|

RU2817864C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Патент США № 4030067, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-07—Публикация

1983-11-21—Подача