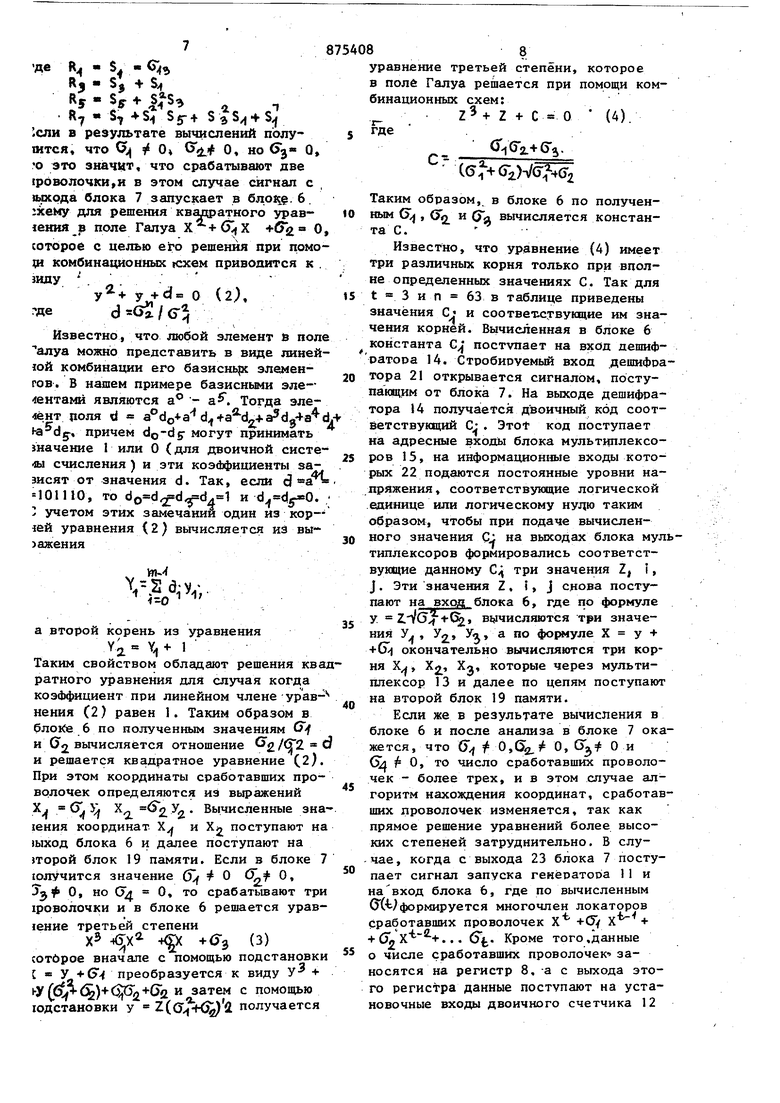

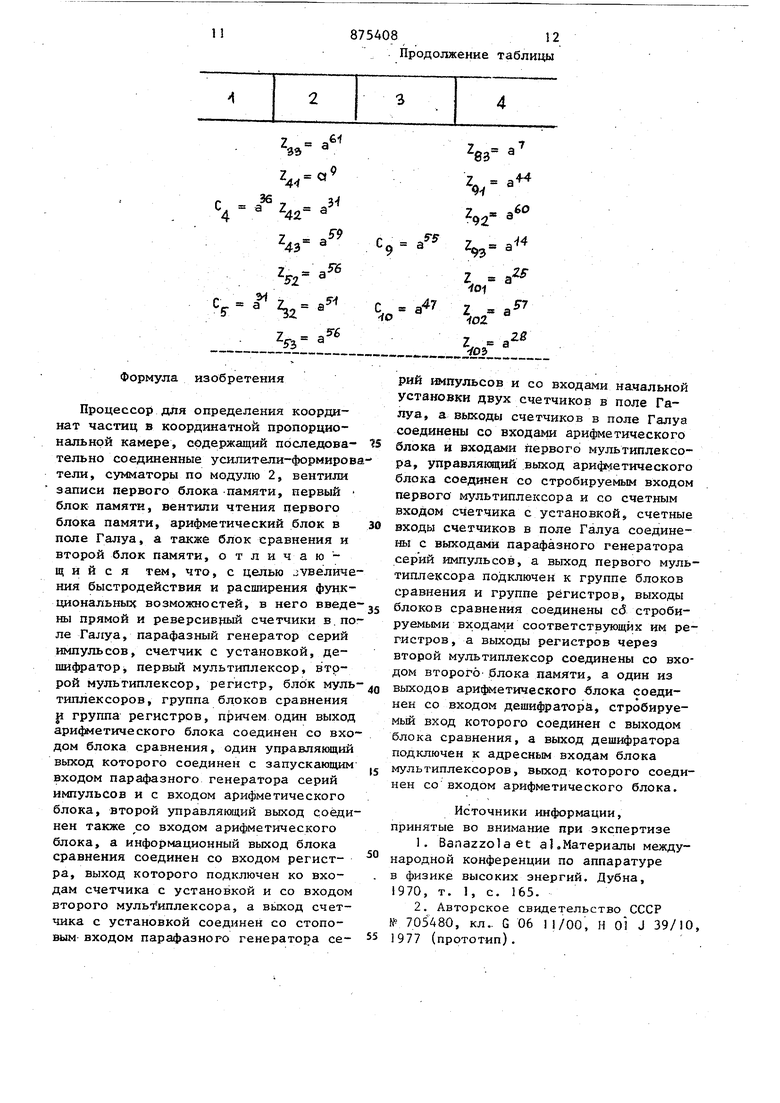

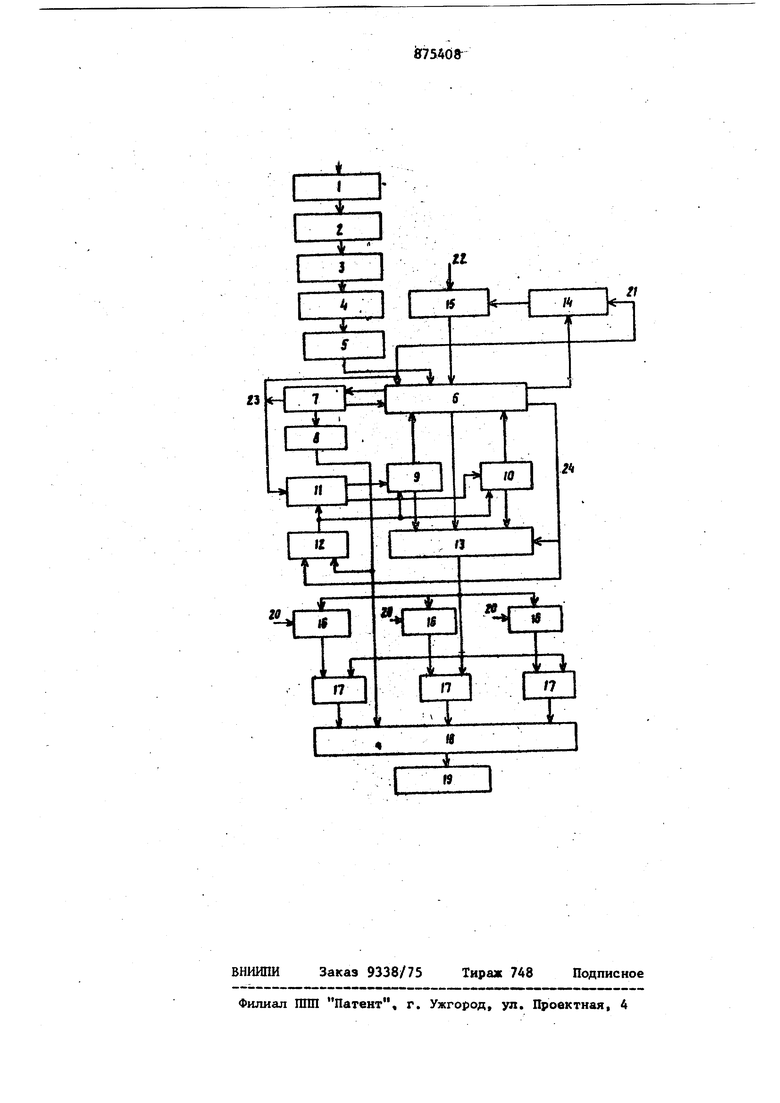

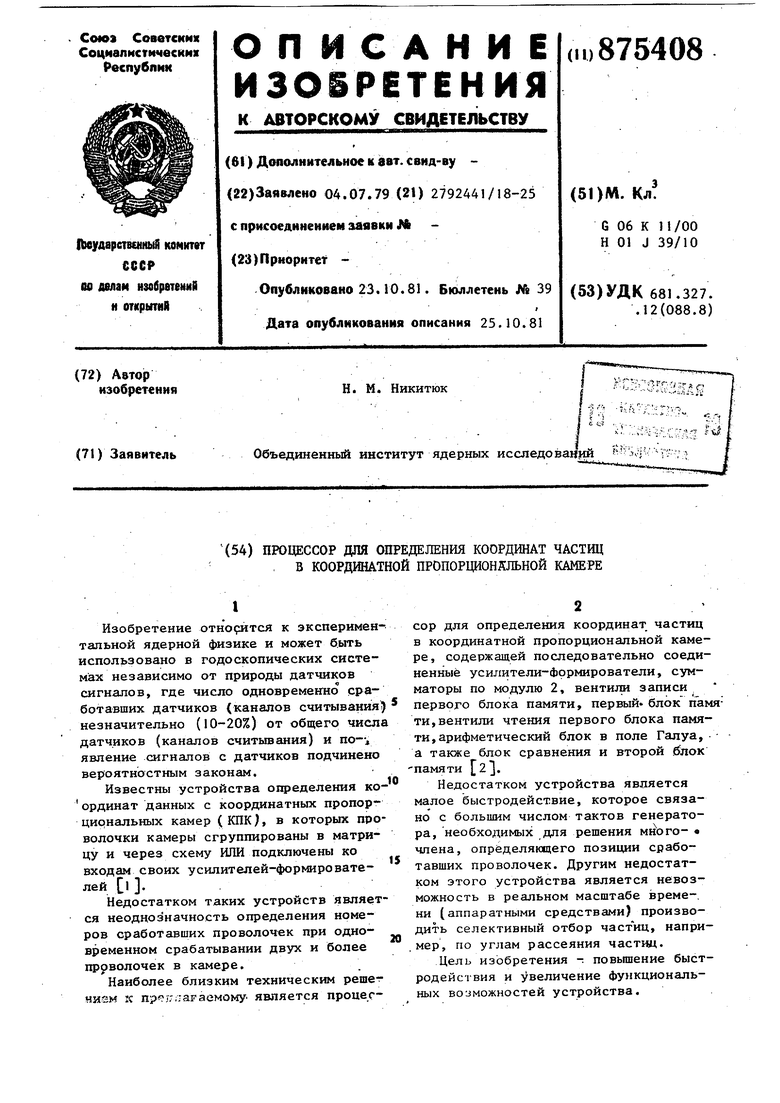

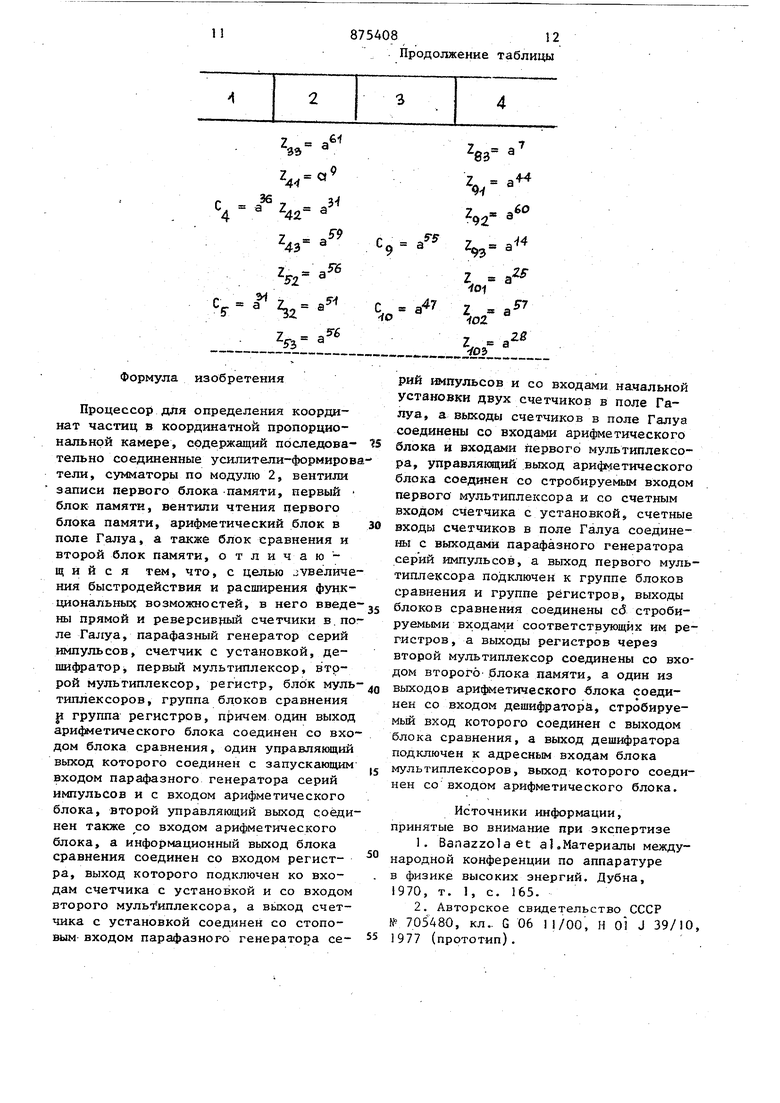

(54) ПРОЦЕССОР ДЛЯ ОПРЕДЕЛЕНИЯ КООРДИНАТ ЧАСТИЦ . В КООРДИНАТНОЙ ПРОПОРЦИОНАЛЬНОЙ КАМЕРЕ Изобретение относится к экспериментальной ядерной физике и может быть использовано в годоскопнческих системах независимо от природы датчиков сигналов, где число одновременно сра ботавших датчиков (каналов считывания незначительно (10-20%) от общего числ датчиков (каналов считывания) и по-, явление сигналов с датчиков подчинено вероятностным законам. Известны устройства определения ко ординат данных с координатных пропорциональных камер (КПК), в которых про волочки камеры сгруппированы в матрицу и через схему ИДИ подключены ко входам своих усилителей-формирователей | . Недостатком таких устройств являет ся неоднозначность определения номеров сработавших проволочек при одновременном срабатывании двух и более пррволочек в камере. Наиболее близким техническим решет ниам к .-акаемому является процегсор для определения координат частиц в координатной пропорциональной камере, содержащей последовательно соединенные усилители-формирователи, сумматоры по модулю 2, вентили записи, первого блока памяти, первый, блок памяти, вентили чтения первого блока памяти, арифметический блок в поле Галуа, а также блок сравнения и второй блок памяти 2}. Недостатком устройства является малое быстродействие, которое связано с большим числом тактов генератора, необходимых для решення много- члена, определяющего позиции сработавших проволочек. Другим недостатком этого устройства является невозможность в реальном масштабе време-. ни (аппаратными средствами) производить селективный отбор частиц, например, по углам рассеяния частиц. Цель изобретения - повьппение быстродействия и увеличение функциональных возможностей устройства. 8 Поставленная цель достигается тем что в устройство, содержащее последовательно соединенные усилители-формирователи, сумматоры по модулю 2, вентили записи первого блока памяти, блок памяти, вентили чтения, первого блока памяти, арифметический блок в поле Галуа, а также блок сравнения и второй блок памяти, введены .прямой и реверсивный счетчики в поле Галуа, парафазный генератор серий импульсов, счетчик с установкой, дешифратор, первый мультиплексор, второй мультиплексор, регистр, блок муль типлексоров, группа блоков сравнения и группа регистров, причем один выход арифметического блока соединен со вхо дом блока сравнения, один управляющий выход которого соединен с запуска ющим входом парафазного генератора тактовых импульсов и с входом арифметического блока, второй управляющий выход соединен также со входом арифметического блока, а информационный выход блока сравнения соединен сО вхо дом регистра, выход которого подключен ко входам счетчика с установкой и со входом второго мультиплексора, , а выход счетчика с уставкой соединен со стоповым входом парафазного генера тора серии импульсов и со входами начальной установки двух счетчиков в по ле Галуа, а выходы счетчиков в поле Галуа соединены со входами арифметического блока и входами первого мультиплексора, управлякшшй выход арифметического блока соединен со стробируемым входом первого мультиплексора и со счетным входом счетчика с установкой, счетные входы счетчиков в поле Галуа соединены с выходами парафазного генератора тактовых импульсов а выход первого мультиплексора подключен к группе блоков сравнения и к группе регистров, а выходы блоков сравненния соединены со стробируемыми -входами соответствующих им регистров, а выходы регистров через второй мультиплексор соединены со входом второго блока памяти, а один из выходов арифметического блока соединен со входом дешифратора, стробируемый вход кото-м рого соединен с выходом блока сравнения, а выход дешифратора соединен с адресными входами блока мультиплексоров, выход которого соединен со входом арифметического блока. На чертеже представлена схема пред лагаемого процессора., Устройство содержит последовательно соединенные усилители-формирователи I, сумматс1ры по модулю 2, вентили записи Первого блока 3 памяти, первый блок 4 памяти, вентили 5 чтения первого блока памяти, арифметический блок 6 в поле Галуа, блок 7 сравнения, регистр 8, прямой счетчик 9 в поле Галуа, реверсивный счетчик Ш в поле Галуа, пар афазный генератора II серий импульсов, счетчик 12 с установкой, первый мультиплексор 13, дешиф-. ратор 14, блок 15 мультиплексоров, группу блоковое сравнения, группу регистров 17, второй мультиплексор 18, и второй блок 19 памяти, вторые входы 20 группы блоков сравнения для подключения набирателей констант, стробируемый вход 21 дешифратора, ин;формационные входы 22 блока мультиплексоров, выход 23 блока сравнения, управляющий выход 24 блока 6. При описании устройства использованы следующие обозначения: а,а ,а, элементы расширенного конечного поля Галуа; GF(2 ) - стандартное обозначение поля Галуа, где , 2 - основание двоичной системы счисления;. У - степень неприводимого полинома; матрица проверочных соотношение для БЧХ-кода; fc - корректирующая способность кода 5.6,6,-. степенные симметрические функ1, 32-t-17 ции, получаемые из г ттрицы Н (синдром кода); i( элементарные симметрические функ1 ,ции:.-, к к е э-Л4V Il вспомогательные козффидиенты, получаемые 5i, Зз, S5/ . число проволочек в камере, число одновременно сработавших проволочек. Процессор работает следующим образом. Импульсы с каждой проволочки камеры после усиления и формирования по-, ступают на вход блока 2. В зтем блоке данные, поступающие на его вход, по каналам на выходе блока сжимаются до . разрядности синдрома .корректирующего кода Боуза-ЧоудхуриДоквингема. Проволочки камеры, содержащей V) 63 пр Волочек, пронумеоованы в порядке воз растания степеней элементов поля Галуа, причем а 010000 является кор нем непроводимого многочлена X +Х+1. Тогда с помощью этого многочлена мож но получить 63 ненулевых элемента по ля. Среди них шесть элементов а 1 100000, а 001000, а 000100, а 000010, а - 000001 и а 010000 образуют базис поля, а 58 элементов поля образуют остальные6 11 11ПППП -Т а+1 110000, а по.поавуглу: а 6 2. -а-х-а а +а 011000 и т.д. 100000. При построении элементов поля операции сложения выполняются по модулю 2, а операции умножения вы полняются по модулю многочлена X +Х+ +1. Элементы поля образуют цикличесf так, что а х а- , а X ( д-ИА а а4и т.д. . Матрица проверочных соотношений для БЧХ-кода исправляющего fc-ошибок, имеет вид где И - длина кода (в нашем случае число проволочек в камере). Предположим, что t 3, тогда матриц Н для И 63 имеет вид: . Таким образом, структура блока 2 однозначно описывается.матрицей Н , где вместо элементов а обычно записываются их эквиваленты в двоичной системе счисления. На выходе блока формируется синдром кода в виде CTeneH-jg ных симметрических функций S. SA , , При этом разрядность синдрома равна N t.log2 или в criV4ae t 3 и п в 63 N 18. Далее сжатые данные через вентили 3 записи поступают в первый блок 4 памяти, где информация накапливается в течение времени действия пучка частиц на детекторы. После накопления данных в памяти междуцикa -«(2tH Д«-0 (2t-l){Hгдри ме сл Г лами работы ускорителя код синдрома через вентили 5 чтения поступает на вход арифметического блока 6. В зависимости от физических -условий в камере может сработать одна, две, три или более трех проволочек. Когда число сработавших проволочек не превышает трех, то степень многочлена локаторов ошибок не превышает трех и часто встречающейся на практике случай может быть сведен к решению такого уравнения быстро при помощи комби1)ационных схем. Когда t I, тогда на выходе блока 2 вырабатывается сишхпом и. в блоке 7 проверится соотношение S jfc О и S 85- О. Это означает, что срабатывает одна проволочка с координатой S. Если, например, сработала вторая проволочка, то S а. Эта координата сразу же поступает с выхода ари4(етического блока 6 на вход первого мультиплексора 13 и далее с выхода этого мультиплексора . значение 5х( поступает на группу схем сравнения 16, на вторые входы 20 которых подаются заданные константы, соответствующие тем константам, сработавших проволочек, которые, исходя из 4 зической задачи, необходимо регистрировать. В случае сравнения.- координата поступает на один из регистров 17 и далее через второй мультиплексор 18 поступает на второй блок 19 памяти. Число схем сравнения 16 и регистров 17 выбирается .из условия постановки эксперимента и ни современном этапе не превьппает 10. Если же в блоке 7 вырабатывается условие S j j S, то считаем что сработали одновременно две, три или более трех проволочек. В этом случав;в блоке 6 решается матричное уравнение 100О 10. Zi.-t S2t-2 0 СГ tG,.. элементарные симметые функции, которые связаны с симическими функциями S, S2...S2 ующими для t 4 соотношениями ( S R it - RT SV Г Я О КгЯт-1-Я 5 R,,, де R - S. - R. Sj Ч $4 RS- ,83 V . R « 87 -VS 85-+ ,, .спи в результате вычислений полу штся, что (j| 1 О Gji.if О, но 6j« О, О это значит, что срабатывают две фоволочкИуИ в этом случае сигнал с яькрда блока 7 запускает в бло11@.6. :хену для решения квадратного урав1ения в поле Галуа X +(Х(Х О соторое с целью его решения при помо Qi комбинационных (Схем привошггся к . }иду . . у+d« о (2), :де Известно, что любой элемент 1з пол алуа можно представить в виде линей юй комбинации его базисных элементов. В нашем примере базисными эле- а. Тогда элементами являются d дант поля d на d5, причем do-d 5 могут принимать шачение 1 или О (для двоичной систе ш счисления ) и эти коэдфициенты зазисят от значения d. Так, если о а 101110, то .1 и . учетом этих замечаний один из кор1ей уравнения (2) вычисляется из выражения второй корень из уравнения Таким свойством обладают решения ква ратного уравнения для случая когда коэФ4 1Циент при линейном члене ур авнения (2) равен 1. Таким образом в блоке 6 по полученш 1м значениям CT-f и (32 вычисляется отношение и решается квадратное уравнение (2) При этом координаты сработавших проволочек определяются иЗ выражений Х Вычисленные зна координат XV и Хл поступают н )ыход блока 6 и далее поступают на }торой блок 19 памяти. Если в блоке юлУчится значение (Xf О (У„ О, 5 О, но С О, то срабатьшают тр фоволочки и в блоке 6 решается урав 1ение третьей степени Х +6-3 (3) сотброе вначале с помощью подстановк С У +(- преобразуется к виду У- У((( затем с помощью юдстановки у получается 8 уравнение третьей степени, которое в поле Галуа решается при помощи комбинационных схем: Z + Z -н С « О O gz- gsCej4-G2) Таким образом, в блоке 6 по полученным 6 , ОГ и Ол вычисляется константа С. Известно, что уравнение (4) имеет три различных корня только при вполне определенных значениях С. Так для t 3 и п 63 в таблице приведены значения С- и соответствующие им значения корней. Вычисленная в блоке 6 константа поступает на вход дешифоатооа 14. Стробиоуемый вход дешифратора 21 открывается сигналом, поступающим от блока 7. На выходе дешифратора 14 получается двоичный код соответствующий С-. Этот код поступает на адресные входь блока мультиплексоров 15, на информационные входы которых 22 подаются постоянные уровни напряжения , соответствующие логической единице или логическому нудю таким образом, чтобы при подаче вычисленного значения Q- на выходах блока мультиплексоров формировались соответствующие данному С три значения Z, I, J. Эти значения Z, 5, j снова поступают на вход„блока 6, где по формуле У. вычисляются три значения У , У2, УЗ ° X у + +С окончательно вычисляются три корня Х t Xg, Ха, которые через мультиплексор 13 и далее по цепям поступают на второй блок 19 памяти. Если же в результате вычисления в блоке 6 и после анализа в блоке 7 окажется, что б f 0,&2. О, О и GA О, то число сработавших проволочек - более трех, и в этом случае алгоритм нахождения координат, сработавших проволочек изменяется, так как прямое решение уравнений более высоких степеней затруднительно. В случае, когда с выхода 23 блока 7 поступает сигнал запуска генератора 11 и навход блока 6, где по вычисленным ОС /формируется многочлен локаторов Сработавших проволочек X +€5 X + + ... G. Кроме того .данные о числе сработавших проволочек заносятся на регистр 8. -а с выхода этого регистра данные поступают на установочные входы двоичного счетчика 12 и на вход мультиплексора 19 и далее на вход второго блока памяти. Тактовы импульсы с выходов блока 11 со сдвигом по Фазе поступают на счетные входы счетчиков 9 и 10 в поле Галуа. При чем счетчик 10 начинает свой от начального значения, соответствующего середине камеры а в обратном направлении, а счетчик 9 начинает счет от начального значения прямом направлении..Такое включение счетчиков в поле Галуа позволяет существенно ускорить процесс нахождения координат многочлена локаторов сработавших iipoволочек, так как в реальном экспери-. менте пучок заряженных частицНаправляется в центр камеры, а рассеяшоле частицы практически симмет1шчно разлетаются относительно центральной оси симметрии координатной камеры. Первой вычи&тенной координатой является- та которая ближе расположена к центру ка меры, а в нашем примере центром являются координа1Ы а н а Выходы счетчиков 9 и 10 соединены со входом блока 6 и входом мультиплексора 13« Если очередное значение, поступившее в блок 6, обращает в нуль многочлен, то с выход 1 24 блока 6 поступает сигнал стробирования на мультиплексор 13 и значения соответствующего счетчика 9 или 10 с выхода мультиплексора 1 поступят на группу схем сравнения 16 и, если это значение координатыУдовлетворяет заданному условию, то на один из регистров 17 запишется коо14ди ната сработавшей проволочки. Далее через мультиплексор 18 эта координата запишется в эапокинающее устройство. Одновременно импульсом с выхода 24 в счетчик 12 добавится единица. Аналогично находят координаты остальных сработавших проволочек. После нахождения последней координаты с помощью сигнала с выхода счетчика 12 генератор тактовых импульсов II останавлгавается. . Таким образом, число тактов работы щ оцессора зависит от числа сработавших проволочек, а в запоминающее устройство заносятся только те координаты значения которых устанавливаются на входах 20 блоков 16 сравнения. Высокое быстродействие процессора по сравнению с известньм устрой т.вом обеспечивается за счет решения многочлена 3-ей степени 1фн помощи комбинацноншлс схем; за счет включения счетчиков в поле Галуа, один из которых считает в прямом направлении, а другой - в обратном направлении от начального значения, соответствующего центру камеры; а также за счет исполь зования счетчика с установкой, который прекращает работу процессора после определения последней координаты. Функциональные возможности процессора расширяются применением группы схем сравнения, при помощи которых в запоминающее устройство записываются только те координаты сработавших проволочек, которые необходимы, исходя из постановки задачи, путем использования в качестве постоянного запоминакацего устройства для хранения конетант группы мультиплексоров. Формула изобретения Процессор для определения координат частиц в координатной пропорциональной камере, содержащий последовательно соединенные усилители-формиров тели, сумматоры по модулю 2, вентили записи первого блока памяти, первый блок памяти, вентили чтения первого блока памяти, арифметический блок в поле Галуа, а также блок сравнения и второй блок памяти, отличающийся тем, что, с целью лувеличе ния быстродействия и расширения функциональных возможностей, в него введе ны прямой и реверсив шй счетчики в.по ле Галуа, парафазный генератор серий импульсов, счетчик с установкой, дешифратор, первый мультиплексор, втррой мультиплексор, регистр, блок муль типлексоров, группа блоков сравнения и группа регистров, причем один выход арифметического блока соединен со вхо дом блока сравнения, один управляющий выход которого соединен с запускающим входом парафазного генератора серий импульсов и с входом арифметического блока, второй управляющий выход соеди нен также со входом арифметического блока, а информационный выход блока сравнения соединен со входом регистра, выход которого подключен ко входам счетчика с установкой и со входом второго мультиплексора, а вькод счетчика с установкой соединен со стоповым входом парафазного генератора серий импульсов и со входами начальной установки двух счетчиков в поле Галуа, а вькоды счетчиков в поле Галуа соединены со входами арифметического блока н входами первого мультиплексора, управлякяций выход арифметического блока соединен со стробируемым входом . первого мультиплексора и со счетным входом счетчика с установкой, счетные входы счетчиков в поле Галуа соединены с выходами парафазного генератора серий импульсов, а выход первого мультиплексора подключен к группе блоков сравнения и группе регистров, выходы блоков сравнения соединены сб стробируемыми входами соответствующих им регистров , а выходы регистров через второй мультиплексор соединены со входом второго- .блока памяти, а один из выходов арифметического блока соединен со входом дешифратора, стробируемый вход которого соединен с выходом блока сравнения, а выход дешифратора подключен к адресным входам блока мультиплексоров, выход которого соединен со входом арифметического блока. Источники информации, принятые во внимание при зкспертизе 1.Banazzolaet al.Материалы международной конференции по аппаратуре в физике высоких энергий. Дубна, 1970, т. 1, с. 165. 2.Авторское свидетельство СССР № 705480, кл.. G 06 1|/00, Н 01 J 39/10, 977 (прототип).

Г I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания данных с координатных пропорциональных камер | 1977 |

|

SU705480A1 |

| Устройство регистрации информации с координатной камеры | 1989 |

|

SU1612269A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| Декодер линейного кода | 1986 |

|

SU1432786A1 |

| Устройство для определения номеров элементов двоичных кодовых последовательностей | 1983 |

|

SU1098100A1 |

| Устройство для вычисления координат | 1978 |

|

SU752350A1 |

| Устройство для отбора @ ядерных частиц | 1987 |

|

SU1497597A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| Устройство регистрации информации с координатной камеры | 1983 |

|

SU1172381A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации | 2015 |

|

RU2613760C2 |

Авторы

Даты

1981-10-23—Публикация

1979-07-04—Подача