Изобретение относится к импульсной технике, в частности к распределителям импульсов, и может быть использовано в устройствах электронной коммутации.

Известен распределитель, содержащий последовательно соединенные шину тактирования и распределитель уровней, состоящий из счетчика и последовательно соединенного с ним дешифратора 1.

Недостаток этого распределителя ограниченные функциональные возможности в связи с отсутствием самостоятельной синхронизации каждого из выходных импульсов.

Известен также распределитель, содержащий в каждом канале элемент И, вйходы каждого из которых являются выходными шинами, а первый вход каждого подключен к соответствующему выходу распределителя уровней. Вход которого соединен с первой шиной тактирова.ния и нулевым входом первого триггера, единичный вход которого подключен к выходу первого компаратора, единичный выход к вторым входам элементов И, а нулевой выход соединен со стробируютцим входом первого компаратора, первый информационный вход которого соединен с выходом мультиплексора, а второй с первой шиной опорного сигнала, управляющие входы мультиплексора соединены с соответствующими выходами распределителя уровней, а информационные входы - с шинами синхроимпульсов 2. 1

Недостаток данного распределителя - ограниченные функциональные возможности в связи с отсутствием самостоятельной синхронизации заднего фронта выходных импульсов,

Цель изобретения - расширение функциональных возможностей.

Указанная цель достигается тем, что в распределитель, содержащий в каждом канале элемент И, выходы каждого из которых являются выходными шинами, а первый вход каждого подключен к соответствующему выходу распределителя уровней, вход которого соединен с первой шиной тактирования и нулевым входом первого тригера, единичный вход которого подклчен к выходу первого компаратора, единичный выход - к вторым входам элементов И, а нулевой выход соединен со стробирующим входом первого компаратора, первый информационный вход которого соединен с выходом мультиплексора, а второй - с первой шиной опорного сигнала, управляющие входы мультиплексора соединены с соответствующими выходами распределителя уровней, а информационные входы - с шинами синхроимпульсов, введены второй компаратор, второй и

третий триггеры, причем выход третьего триггера соединен со стробирующим входом второго компаратора, а нулевой вход - с первой шиной тактирования, -первый информационный вход второго компаратора подключен к выходу мультиплексора, а выход - к единичному входу второго триггера, нулевой вход которого подключен к первой шине тактирования, а выход - к

0 третьим входам элементов И, причем единичный вход третьего триггера и второй информационный вход второго компаратора подключены соответственно к вторым шинам тактирования и

с опоры.

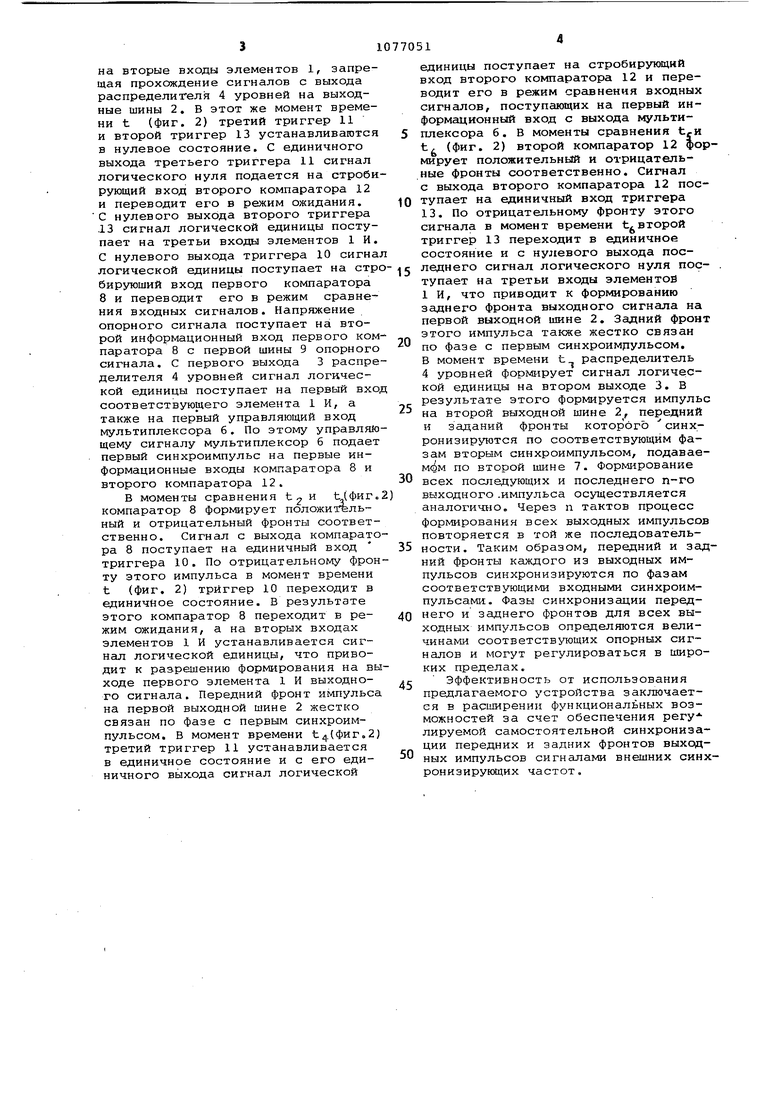

На фиг. 1 представлена функциональная схема распределителя; на фиг. 2 - временная диаграмма работы устройства.

Q Распределитель содержит в каждом канале элемент 1 И,выходы каждого из которых являются выходными шинами 2. Первый в;сод каждого из элементов 1 И подключен к соответствующе5 му выходу 3 распределителя 4 уровней, вход которого соединен с первой шиной 5 тактирования. Выходы распределителя 4 уровней соединены с соответствующими управляющими входами мультиплексора.6, информационные

входы которого соединены с соответствующими шинами 7 синхроимпульсов, а выход подключен к первому информационному входу первого компаратора 8, второй информационный вх-од которо5 го подключен к первой шине 9 опоры, а выход и стробирующий вход соединен соответственно с единичным входом и нулевым выходом первого триггера 10, единичный выход которого

0 соединен с вторыми входами элементов 1 И. Нулевой вход первого триггера 10 соединен с первой шиной 5 тактирования и нулевым входом третьего триггера 11, выход которого сое5 динен со стробирующим входом второго компаратора 12, первый информационный вход и выход которого соединены соответственно с выходом мультиплексора б и единичным входом второго триггера 13, нулевой вход которого соединен с первой шиной 5 тактирования, а выход подключен к третьим входам элементов 1 И. Единичный вход третьего триггера 11 соединен с второй шиной 14 тактирования, а второй

5 информационный вход второго компаратора 12 соединен с второй шиной 15 опоры.

Распределитель работает следующим образом.

0 в момент времени t (фиг. 2) распределитель 4 уровней устанавливается в исходное состояние, первый триггер 10 сбрасывается в нулевое состояние и с его единичного выхода

5 сигнал логического нуля подается на вторые входы элементов 1, запре щая прохождение сигналов с выхода распределителя 4 уровней на выходные шины 2. В этот же момент времени t (фиг. 2) третий триггер 11 и второй триггер 13 устанавливаютс в нулевое состояние. С единичного выхода третьего триггера 11 сигнал логического нуля подается на строби рующий вход второго компаратора 12 и переводит его в режим ожидания. С нулевого выхода второго триггера ,13 сигнал логической единицы поступает на третьи входы элементов 1 И С нулевого выхода триггера 10 сигна логической единицы поступает на стр бируюший вход первого компаратора 8 и переводит его в режим сравне НИН входных сигналов. Напряжение опорного сигнала поступает на второй информационный вход первого ком паратора 8 с первой шины 9 опорного сигнала. С первого выхода 3 распре делителя 4 уровней сигнал логической единицы поступает на первый вхо соответствующего элемента 1 И, а также на первый управляющий вход мультиплексора б. По этому управляю щему сигналу мультиплексор б подает первый синхроимпульс на первые информационные входы компаратора 8 и второго компаратора 12. В моменты сравнения t и ифиг компаратор 8 формирует положительный и отрицательный фронты соответственно. Сигнал с выхода компарато ра 8 поступает на единичный вход триггера 10. По отрицательному фрон ту этого импульса в момент времени t (фиг. 2) триггер 10 переходит в единичное состояние. В результате этого компаратор В переходит в режим ожидания, а на вторых входах элементов 1 И устанавливается сигнал логической единицы, что приводит к разрешению формирования на вы ходе первого элемента 1 И выходного сигнала. Передний фронт импульса на первой выходной шине 2 жестко связан по фазе с первым синхроимпульсом. В момент времени (ф1гг,2} третий триггер 11 устанавливается в единичное состояние и с его единичного выхода сигнал логической единицы поступает на стробирующий вход второго компаратора 12 и переводит его в режим сравнения входных сигналов, поступакяцих на первый информационный вход с выхода мультиплексора б. В моменты сравнения Ъ,и t (фиг. 2) второй компаратор 12 формирует положительный и отрицательные фронты соответственно. Сигнал с выхода второго компаратора 12 поступает на единичный вход триггера 13. По отрицательному фронту этого сигнала в момент времени t второй триггер 13 переходит в единичное состояние и с нулевого выхода последнего сигнал логического нуля поступает на третьи входы элементов 1 И, что приводит к формированию заднего фронта выходного сигнала на первой выходной шине 2. Задний фронт этого иьшульса также жестко связан по фазе с первым синхроимдульсом. В момент времени t распределитель 4 уровней формирует сигнал логической единицы на втором выходе 3. В результате этого формируется импульс на второй выходной шине 2, передний и заданий фронты которого синхронизируются по соответствующим фазам вторым синхроимпульсом, подаваемом по второй шине 7. Формирование всех последующих и последнего п-го выходного .импульса осуществляется аналогично. Через п тактов процесс формирования всех выходных импульсов повторяется в той же последовательности. Таким образом, передний и задний фронты каждого из выходных импульсов синхронизируются по фазам соответствующими входными синхроимпульсами. Фазы синхронизации переднего и заднего фронтов для всех выходных импульсов определяются величинами соответствующих опорных сигналов и могут регулироваться в широких пределах. Эффективность от использования предлагаемого устройства заключается в расширении функциональных возможностей за счет обеспечения регу лируемой самостоятельной синхронизации передних и задних фронтов выходных импульсов сигналами внешних синхронизирукяцих частот.

/

r

BuxoS 3

Второй Цшод 3

п-ый Btixodi

Пер9оя шина 7

Втоаар шина 7

п-ая шина

Выход G

В 15 Выход 8

„о Выход W Выход 11

Выход 72 Выхо073

первая uj(JHO г

ЗтЪрай шиНа Z

шина Z.

(Риг. 2

t

-t

t

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель | 1981 |

|

SU959278A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2002 |

|

RU2218669C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство управления коммутатором | 1981 |

|

SU1056456A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

| Преобразователь время-амплитуда импульсов | 1987 |

|

SU1444949A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

РАСПРЕДЕЛИТЕЛЬ, .содержащий В кажцом канале элемент И, выходы каждого из которых являются выходными шинами, а первый вход каждого подключен к соответствующему выходу распределителя уровней, вход которого соединен с первой шиной тактирования и нулевым входом первого триггера, единичный вход которого подключен к выходу первого компаратора, единичный выход - к вторым входам элементов И, а нулевой выход соединен со стробирующим входом первого компаратора, первый информадионный вход которого соединен с выходом мультиплексора, а второй - с первой шиной опорного сигнала, управляющие входы мультиплексора соединены с соответствующими выходами ра пределителя уровней, а информационные входы - с шинами синхроимпульсов, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены второй компаратор, второй и третий триггеры, причём выход третьего триггера соединен со стробирующим вх,одом второго кймпаратора, а нулевой вход с первой шиной тактирования, первый информационный вход второго компаратора подключен к выходу мультиплексора, а выход - к единичному входу второго триггера, нулевой вход кото- О рого подключен к первой шине такти(Я рования, а выход - к третьим входам элементов И, причем единичный вход третьего триггера и второй информационный вход второго компаратора подключены соответственно к вторым а шинам тактирования и опоры. ч о СП

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Распределитель импульсов | 1975 |

|

SU668091A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-02-28—Публикация

1982-11-18—Подача