Изобретение относится к электро- и радиосвязи и может использоваться в проводных, радио-, радиорелейных и метеорных линиях связи.

Известная система связи, содержащая на передающей стороне кодирующий блок, синхронизатор, временный манипулятор, передатчик и синхроблок, а на приемной стороне приемник, согласованный фильтр, компаратор, первое и второе запоминающие устройства, дешифратор, устройство хранения и выборки сигнала, синхроблок, формирователь импульсов, двоичный счетчик и линию связи [1]. (Здесь двоичные символы, поступающие от К источников информации, можно рассматривать как сообщение из К двоичных символов в параллельном виде одного источника).

Однако такая система связи не может быть использована в стартстопном режиме.

Наиболее близкой по технической сущности к предлагаемой системе связи является стартстопная система связи [2] (второй вариант, с.40), принятая за прототип.

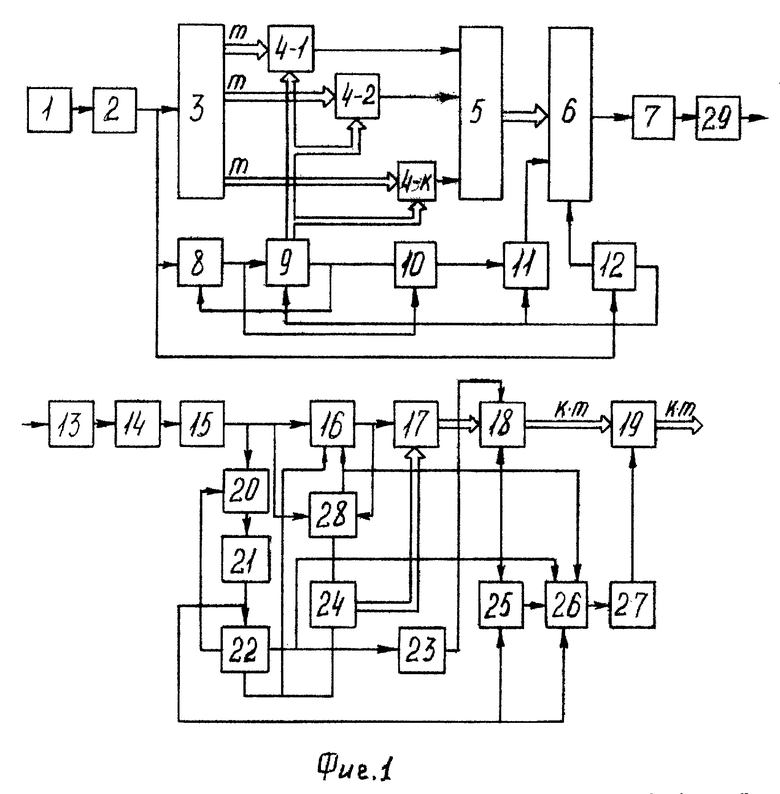

Схема системы-прототипа приведена на фиг.1, где обозначено:

1 - датчик;

2, 27 - первое и второе пороговое устройство (ПУ);

3, 17 - первое и второе запоминающее устройство (ЗУ);

(4-1)÷(4-К) - мультиплексоры;

5 - двоичный сумматор;

6 - вычитающий счетчик;

7 - передатчик;

8 - триггер;

9, 24, 25 - первый, второй и третий двоичный счетчик;

10 - элемент НЕ;

11 - элемент ИЛИ;

12 - генератор сеток импульсов;

13 - приемник;

14 - амплитудный детектор (АД);

15 - фильтр нижних частот (ФНЧ);

16 - компаратор;

18 - сдвиговый регистр;

19 - дешифратор;

20 - ключ;

21 - синхроблок;

22 - формирователь импульсов;

23 - формирователь пачек импульсов;

26 - накопитель;

28 - блок выборки и хранения сигнала;

29 - линия связи.

Стартстопная система связи-прототип содержит на передающей стороне последовательно соединенные датчик 1, первое ПУ 2 и первое ЗУ 3. К выходов которого соединены шинами через соответствующие мультиплексоры (4-1)÷(4-К) с К входами двоичного сумматора 5, выход которого шиной соединен с информационными входами вычитающего счетчика 6, выход которого через передатчик 7 соединен с входом линии связи 29. Кроме того, содержит последовательно соединенные триггер 8, первый двоичный счетчик 9, элемент НЕ 10 и элемент ИЛИ 11, выход которого соединен с входом разрешения записи кода вычитающего счетчика 6. При этом выход триггера 8 соединен со вторым входом элемента НЕ; выход первого двоичного счетчика 9 соединен со вторым входом триггера 8, первый вход которого соединен с выходом первого ПУ 2 и входом генератора сеток импульсов 12, первый выход которого соединен со счетным входом вычитающего счетчика 6. Второй выход генератора сеток импульсов 12 соединен со вторыми входами первого двоичного счетчика 9 и элемента ИЛИ. Причем второй выход первого двоичного счетчика 9 шиной соединен со вторыми входами мультиплексоров (4-1)÷(4-К).

На приемной стороне система связи-прототип содержит последовательно соединенные приемник 13, АД 14, ФНЧ 15, компаратор 16 и второе ЗУ 17, сдвиговый регистр 18 и дешифратор 19, выход которого является выходом устройства. Причем ЗУ l7, сдвиговый регистр 18, дешифратор 19 соединены между собой шиной. Кроме того, последовательно соединенные ключ 20, синхроблок 21, формирователь импульсов 22 и формирователь пачек импульсов 23, выход которого соединен с тактовым входом сдвигового регистра 18. Второй выход формирователя импульсов 22 соединен со счетным входом второго двоичного счетчика 24 и тактовым входом компаратора 16.

Третий выход формирователя импульсов 22 соединен со вторым входом ключа 20, первый вход которого соединен с выходом ФНЧ 15. Последовательно соединенные третий двоичный счетчик 25, накопитель 26 и второй ПУ 27, выход которого соединен с управляющим входом дешифратора 19. При этом выход синхроблока 21 соединен с установочными входами третьего двоичного счетчика 25 и накопителя 26.

Первый выход формирователя импульсов 22 соединен с установочными входами второго двоичного счетчика 24 и блока выборки и хранения сигнала 28, счетным входом третьего двоичного счетчика 25 и стробирующими входами сдвигового регистра 18 и накопителя 26, сигнальный вход которого соединен со вторым входом компаратора 16 и выходом блока выборки и хранения сигнала 28, сигнальный вход которого соединен с выходом ФНЧ 15, а управляющий вход с выходом компаратора 16. Выход второго двоичного счетчика 24 шиной соединен с информационным входом второго ЗУ 17. Вход приемника 13 является входом приемной стороны системы связи. Передающая и приемная стороны стартстопной системы связи соединены посредством линии связи 29.

Система связи-прототип работает следующим образом.

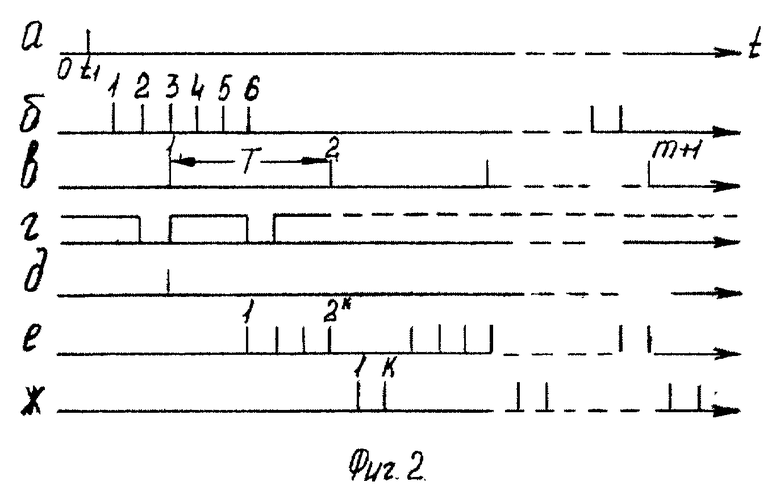

На передающей стороне в начальный момент времени t=0 на выходе триггера 8 присутствует сигнал логического "0", а на выходе блока 6 логической "1" и передатчик не работает. В случайный момент времени на выходе датчика 1 (сейсмического, акустического и т. д. ) появляется сигнал определенного уровня. При превышении им определенного порога в блоке 2 в момент времени t1 формируется короткий импульс (фиг. 2а), который осуществляет запись K•m разрядного двоичного числа (K≥1, m≥1: например, номера датчика) в ЗУ 3, запускает генератор 12, на первом выходе которого формируются короткие импульсы с периодом следования τ (фиг.2б), а на втором выходе с задержкой на 3τ с периодом T-(2K+2)τ (фиг.2в) и переводит триггер 8 в состояние "l".

Последнее приводит к обнулению счетчика 9, в результате чего с S выходов его разрядов (где S - число, большее на единицу значения log2(m+1)) сигналы логического "0" по шинам поступают на управляющие входы мультиплексоров (4-1)÷(4-K) с (m+1) информационными входами, на первые из которых (на фиг.1 не показаны) всегда подается сигнал логического "0". Общее число K•m выходов ЗУ 3, на которых действуют символы сообщения, разбивается на К групп по m символов в каждой группе (шине), так что ко вторым входам всех мультиплексоров 4 по одному подключаются (1÷К)-й выходы ЗУ 3, к третьим - [(K+1)÷2K]-й выходы, . . . к (m+1)-ым входам -([(m-1)K+1]÷K•m-й выходы. Таким образом, в момент времени t1 на выходе всех блоков 4 действуют сигналы логического "0" (поступающие с их первых входов).

Двоичный сумматор 5 имеет две группы по К входов. На К входов второй группы (на фиг.1 они не показаны) всегда подается двоичное число, равное в десятичной форме двум, поэтому в тот же момент времени на одном из его (К+1) выходов, соответствующем второму младшему разряду двоичного числа, действует сигнал логической "1". По перепаду выходного напряжения схемы ИЛИ 11 при t-t1 это число записывается в блок 6, на его выходе сохраняется прежний уровень "1" и открывается счетный вход, на который поступают импульсы с первого выхода ГСИ 12 (фиг.2б). Второй из них передним фронтом произведет обнуление счетчика 6 и на его выходе установится уровень логического "0" до момента поступления третьего импульса (фиг.2г).

При этом откроется передатчик и на его выходе сформируется синхросигнал - радиоимпульс длительности τ с определенной несущей частотой. В момент действия заднего фронта первого импульса на втором выходе, ГСИ 12 (фиг.2в), младший разряд счетчика 9 устанавливается в единичное состояние и на выходы блоков 4 поступят логические сигналы, действующие на их первых входах, поступающих по шинам с выходов блока 3. В сумматоре 5 это двоичное число в параллельном виде увеличится на два затем запишется выходным импульсом блока 11 в счетчик 6. Момент появления нулевого сигнала на выходе последнего (и сигнала на выходе передатчика) зависит от значения двоичного числа, действующего на вторых входах блоков 4. Если оно в десятичной форме равно q[0≤q≤(2K-1)] то он появится через интервал времени τ(2+q) относительно первого импульса фиг.2в (на фиг.2г - 3τ; К=2).

Аналогичным образом осуществляется передача остальных К-разрядных двоичных чисел. При поступлении последнего (m+1)-го импульса со второго выхода ГСИ 12 на четный вход блока 9 на его выходе формируется сигнал, который возвращает триггер 8 в исходное состояние и на выходе блока 6 будет действовать сигнал логической "1". Следующий сигнал на выходе датчика 1 может появиться только через интервал времени, больший или равный 2m(2+2K)τ.

На приемной стороне принимаемый сигнал после фильтрации в приемнике 13, амплитудного детектирования в блоке 14 и фильтрации в ФНЧ 15 поступает на вход компаратора 16 через открытый в исходном состоянии ключ 20 на вход синхроблока 21 и на сигнальный вход блока 28. В синхроблоке 21, представляющем собой оптимальный измеритель временного положения сигнала (рис.7.2, [3]), при отсутствии помех формируется короткий импульс, соответствующий моменту действия максимума принимаемого отфильтрованного синхросигнала (фиг. 2д). В блоке 22 по нему создаются две сетки импульсов на первом выходе с периодом T (как на фиг. 2в), на втором с периодом τ (фиг.2е), а на третьем выходе формируется импульс длительности m(2K+2)τ, размыкающий на это время ключ 20.

При этом в блоке 23 формируются пачки коротких импульсов (фиг.2ж). Выходной импульс синхроблока 21 производит обнуление счетчика 25 и накопителя 26, а первый импульс с первого выхода блока 22 (задним фронтом) блоков 24 и 28. В момент действия переднего фронта первого из импульсов на втором выходе блока 22 входной сигнал компаратора сравнивается по уровню с сигналом, поступающим на его второй вход с блока 28 (в данном случае нулевым). Если он оказывается больше последнего, то на выходе компаратора 16 формируется перепад напряжения, который открывает вход блока 28 и позволяет в нем запомнить уровень выходного сигнала ФНЧ 15.

Указанная процедура повторяется 2К раз. В результате к моменту прихода второго импульса с первого выхода блока 22 в блок 28 оказывается записанным уровень наибольшего из выходных сигналов ФНЧ l5 в течение времени Т-2τ. Двоичный К-разрядный счетчик 24 предназначен для подсчета числа импульсов, поступающих на него со второго выхода блока 22. Каждый раз, когда на выходе компаратора 16 появляется перепад напряжения, показания К разрядов его считываются в ЗУ l7. Этo позволяет зафиксировать в нем номер временной позиции наибольшего из выходных сигналов ФНЧ 15 на интервале времени Т-2τ.

В момент действия переднего фронта второго импульса (фиг.2в) число, записанное в ЗУ 17, записывается в блоке 18 и затем сдвигается на К разрядов выходными импульсами блока 23 (фиг.2ж). Аналогичным образом осуществляется обработка выходного сигнала ФНЧ l5 на других интервалах времени длительности Т-2τ. В результате этого в момент прихода последнего (m+1)-го импульса с первого выхода блока 22 в блок 18 оказывается записанной информация о временных положениях максимальных уровней выходного сигнала ФНЧ 15.

Дешифратор 19 однозначным образом преобразует входное двоичное число, в результате чего двоичное число в параллельном виде на его выходах при отсутствии помех в линии связи совпадает с выходными символами ЗУ 3. Блок 26 предназначен для суммирования выходных сигналов блока 28 в моменты действия передних фронтов импульсов фиг.2в, а счетчик 25 для их подсчета.

Последний (m+1)-й импульс производит его обнуление. В этот момент времени выходной сигнал блока 26 считывается на вход ПУ 27 с определенным порогом и, если он превышает порог, то на выходе блока 27 формируется импульс, который считывает информацию дешифратора 19 на его выходы.

Все блоки, входящие в это устройство, являются известными. Формирователи пачек импульсов, например, могут быть получены с помощью схем с контурами ударного возбуждения (см. книгу Л. М. Голленберга. Импульсные и цифровые устройства. М.: Связь, 1973, с. 224). Блоки 16, 17, 24 и 28 использовались в [1].

Однако такая стартстопная система связи имеет большую вероятность ложных срабатываний (см. рисунки в [2]).

Изобретение направлено на снижение вероятности ложных срабатываний.

Для устранения указанного недостатка в стартстопную систему связи, содержащую на передающей стороне последовательно соединенные датчик, первый пороговый блок и запоминающий блок, К выходов которого шинами соединены с первыми входами К мультиплексоров, выходы которых соединены с К входами двоичного сумматора соответственно, выход которого шиной соединен с информационным входом вычитающего счетчика, выход которого соединен с входом передатчика, выход которого соединен с входом линии связи, а также последовательно соединенные первый триггер и первый двоичный счетчик, первый выход которого соединен со вторым входом первого триггера, второй выход первого двоичного счетчика шиной соединен со вторыми входами К мультиплексоров, кроме того, последовательно соединенные первые элементы НЕ и ИЛИ, выход которого соединен с входом разрешения записи кода вычитающего счетчика, при этом вход первого элемента НЕ соединен с выходом первого триггера, вход которого соединен с выходом первого порогового блока, счетный вход первого двоичного счетчика соединен со вторым входом первого элемента ИЛИ, выход генератора импульсов соединен со счетным входом вычитающего счетчика, на приемной стороне содержит последовательно соединенные приемник, амплитудный детектор, фильтр нижних частот, а также первый формирователь импульсов, второй и третий двоичные счетчики, второй пороговый блок и сдвиговый регистр, при этом выход первого формирователя импульсов соединен с установочным входом третьего двоичного счетчика, причем, выход линии связи соединен с входом приемника, на передающей стороне введен дифференцирующий блок, вход которого соединен с выходом вычитающего блока, а выход со вторым входом первого элемента ИЛИ, на приемной стороне введены первый элемент И, последовательно соединенные второй элемент ИЛИ и делитель частоты, а также (К+1)-й мультиплексор, последовательно соединенные оконечный блок и третий элемент ИЛИ, последовательно соединенные счетчик-распределитель, первый Д-триггер, четвертый элемент ИЛИ, второй триггер, второй элемент НЕ, пятый элемент ИЛИ и четвертый двоичный счетчик, выход которого шиной соединен с входами первого и второго цифровых компараторов, а также последовательно соединенные третий триггер, третий элемент НЕ и второй элемент И, кроме того, последовательно соединенные третий элемент И и четвертый элемент НЕ, а также второй Д-триггер, четвертый элемент И, второй формирователь импульсов и генератор тактовых импульсов, выход которого соединен с тактовым входом делителя частоты и счетным входом третьего двоичного счетчика.

При этом выход первого цифрового компаратора соединен с входом третьего триггера. Выход второго элемента И соединен с третьим входом четвертого элемента ИЛИ. Выход второго цифрового компаратора через четвертый элемент И соединен со вторым входом четвертого элемента ИЛИ. Выход четвертого элемента НЕ соединен со вторыми входами первого и четвертого элементов И.

Первый вход третьего элемента И соединен с третьим выходом делителя частоты и вторым входом второго триггера. Второй вход третьего элемента И соединен с выходом третьего триггера, установочный вход которого соединен с выходом пятого элемента ИЛИ. Выход третьего элемента И соединен с тактовым входом оконечного блока, второй выход которого соединен со вторыми входами второго и пятого элементов ИЛИ. Выход первого элемента И соединен с информационными входами первого и второго Д-триггеров и счетным входом четвертого двоичного счетчика.

Первый вход счетчика-распределителя соединен с выходом первого формирователя импульсов и установочными входами первого и второго Д-триггеров, причем стробирующий вход второго Д-триггера соединен со вторым выходом счетчика-распределителя, третий выход которого соединен с его установочным входом. Счетный вход счетчика-распределителя подсоединен к второму выходу делителя частоты. Четвертый выход счетчика-распределителя соединен с установочным входом второго двоичного счетчика, выход переполнения которого соединен с входом второго формирователя импульсов, выход которого соединен до вторым входом второго элемента И. Выход второго Д-триггера соединен с четвертым входом четвертого элемента ИЛИ. Второй выход третьего двоичного счетчика соединен со вторым входом третьего элемента ИЛИ. Третий выход третьего двоичного счетчика соединен с его запрещающим входом.

Первый выход третьего двоичного счетчика шиной соединен с управляющим входом (К+1)-го мультиплексора, выход которого соединен с входом сдвигового регистра. Вход (К+1)-гo мультиплексора шиной соединен с выходом второго двоичного счетчика, первый вход которого соединен с первым выходом делителя частоты. Выход третьего элемента ИЛИ соединен с тактовым входом сдвигового регистра. Выход фильтра низших частот через последовательно соединенные второй пороговый блок, первый элемент И и первый формирователь импульсов соединен с входом второго элемента ИЛИ.

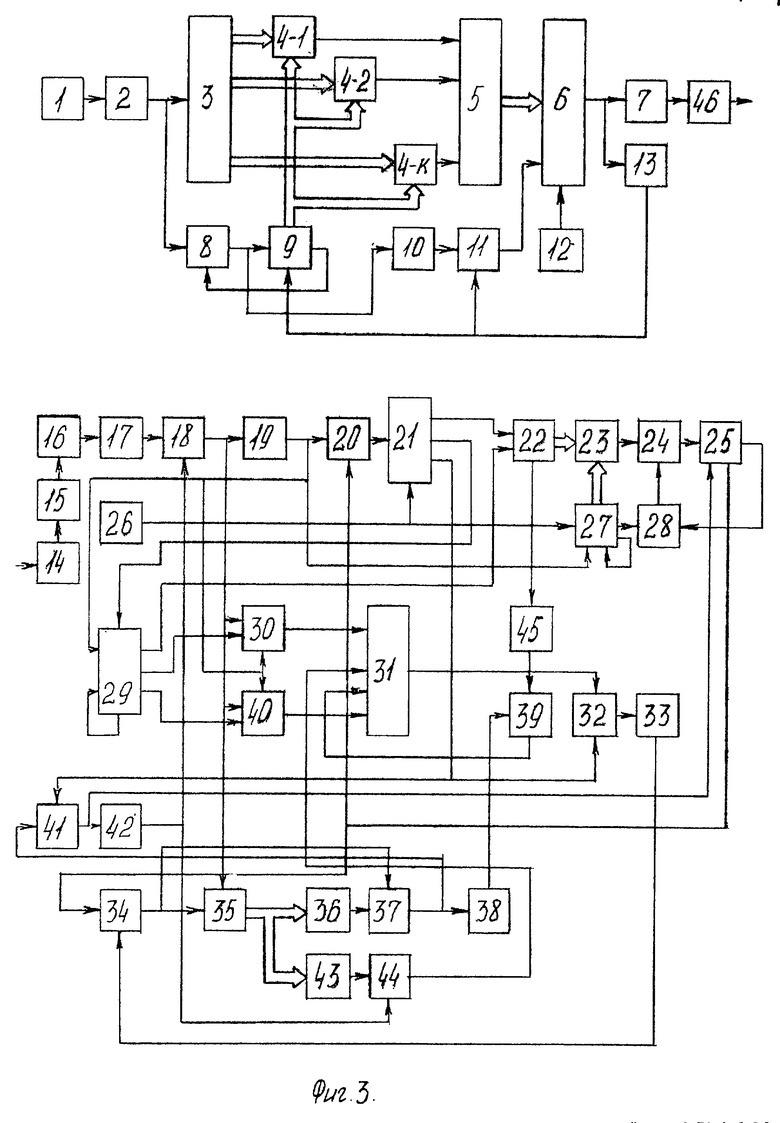

На фиг.3 представлена схема предлагаемой стартстопной системы связи, где обозначено:

1 - датчик;

2, 17 - первый и второй пороговый блок;

3 - запоминающий блок;

(4-1)÷(4-К) - мультиплексоры;

5 - двоичный сумматор;

6 - вычитающий счетчик;

7 - передатчик;

8, 32, 37 - первый, второй, третий триггер;

9, 22, 27, 35 - первый, второй, третий и четвертый двоичный счетчик;

10, 33, 38, 42 - первый, второй, третий и четвертый элемент НЕ;

11, 20, 28, 31, 34 - первый, второй, третий, четвертый и пятый элемент ИЛИ;

12 - генератор импульсов;

13 - дифференцирующий блок;

14 - приемник;

15 - амплитудный детектор (АД);

16 - фильтр нижних частот (ФНЧ);

18, 39, 41, 44 - первый, второй, третий и четвертый элемент И;

19, 45 - первый и второй формирователь импульсов;

21 - делитель частоты;

23 - (К+1)-й мультиплексор;

24 - сдвиговый регистр;

25 - оконечный блок;

26 - генератор тактовых импульсов (ГТИ);

29 - счетчик-распределитель;

30, 40 - первый и второй Д-триггер;

36, 43 - первый и второй цифровой компаратор;

46 - линия связи.

Предлагаемая стартстопная система связи содержит передающую и приемную стороны, соединенные линией связи 46. Передающая сторона содержит последовательно соединенные датчик 1, первый пороговый блок 2 и запоминающее устройство 3, К выходов которого соединены шинами с первыми входами К мультиплексоров (4-1)÷(4-К), выходы которых соединены с К входами двоичного сумматора 5 соответственно, выход которого шиной соединен с информационным входом вычитающего счетчика 6, выход которого соединен с входами передатчика 7 и дифференцирующего блока 13. Выход передатчика 7 соединен с входом линии связи 46. Кроме того, содержит последовательно соединенные первый триггер 8 и первый двоичный счетчик 9, первый выход которого соединен со вторым входом триггера 8, второй выход двоичного счетчика 9 шиной соединен со вторыми входами мультиплексоров (4-1)÷(4-К), последовательно соединенные первые элементы НЕ 10 и ИЛИ 11, выход которого соединен с входом разрешения записи кода вычитающего счетчика 6.

При этом вход первого элемента НЕ 10 соединен с выходом первого триггера 8. Выход генератора импульсов 12 соединен со счетным входом вычитающего счетчика 6. Выход дифференцирующего блока 13 соединен со счетным входом первого двоичного счетчика 9 и вторым входом первого элемента ИЛИ 11. Выход первого порогового блока 2 соединен с входом первого триггера 8.

На приемной стороне система связи содержит последовательно соединенные приемник 14, АД 15, ФНЧ 16, второй пороговый блок 17, первый элемент И 18, первый формирователь импульсов 19, второй элемент ИЛИ 20, делитель частоты 21 и второй двоичный счетчик 22, выход которого шиной соединен с входом (К+1)-го мультиплексора 23, выход которого через последовательно соединенные сдвиговый регистр 24 и оконечный блок 25 соединен с первым входом третьего элемента ИЛИ 28, выход которого соединен с тактовым входом сдвигового регистра 24. Выход ГТИ 26 соединен с тактовым входом делителя частоты 21 и счетным входом третьего двоичного счетчика 27, первый выход которого шиной соединен с управляющим входом (К+1)-го мультиплексора 23. Второй выход третьего двоичного счетчика 27 соединен со вторым входом третьего элемента ИЛИ 28. Третий выход третьего двоичного счетчика 27 соединен с его запрещающим входом. А установочный вход третьего двоичного счетчика 27 соединен с выходом первого формирователя импульсов 19.

Кроме того, последовательно соединенные счетчик-распределитель 29, первый Д-триггер 30, четвертый элемент ИЛИ 31, второй триггер 32, второй элемент НЕ, пятый элемент ИЛИ 34 и четвертый двоичный счетчик 35, выход которого шиной соединен с входами первого 36 и второго 43 цифровых компараторов. Второй выход счетчика-распределителя 29 соединен со стробирующим входом второго Д-триггера 40, выход которого соединен с четвертым входом четвертого элемента ИЛИ 31. Третий выход счетчика-распределителя 29 соединен с его установочным входом, а четвертый выход с установочным входом второго двоичного счетчика 22. Первый вход счетчика-распределителя 29 соединен с установочными входами первого 30 и второго 40 Д-триггеров, а также с выходом первого формирователя импульсов 19. Счетный вход счетчика-распределителя 29 соединен со вторым выходом делителя частоты 21. Информационные входы первого 30 и второго 40 Д-триггеров соединены с выходом первого элемента И 18 и счетным входом четвертого двоичного счетчика 35. Выход первого цифрового компаратора 36 через последовательно соединенные третий триггер 37 и третий элемент НЕ 38 соединен с первым входом второго элемента И 39. Выход второго цифрового компаратора 43 через четвертый элемент И 4 соединен со вторым входом четвертого элемента ИЛИ 31, третий вход которого подсоединен к выходу второго элемента И 39.

Выход переполнения второго двоичного счетчика 22 через второй формирователь импульса 45 соединен со вторым входом второго элемента И 39. Выход пятого элемента ИЛИ 34 соединен с установочным входом третьего триггера 37, выход которого соединен со вторым входом третьего элемента И 41, первый вход которого соединен до вторым входом второго триггера 32 и третьим выходом делителя частоты 21. Выход третьего элемента И 41 соединен с тактовым входом оконечного блока 25 и входом четвертого элемента НЕ 42, выход которого соединен со вторыми входами первого 18 и четвертого 44 элементов И. Второй выход оконечного блока 25 соединен со вторыми входами второго 20 и пятого 34 элементов ИЛИ.

Стартстопная система связи работает следующим образом.

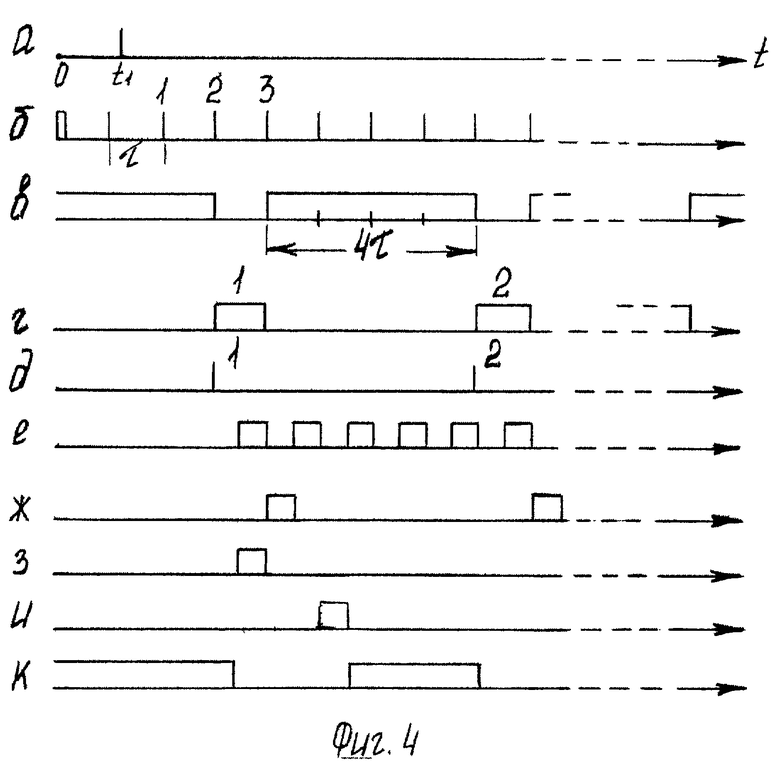

На передающей стороне в начальный момент времени (t=0) на выходе триггера 8 действует сигнал логического "0", а на выходе блока 6 логической "1" и передатчик 7 не работает. В случайный момент времени на выходе датчика 1 (сейсмического, акустического и т.д.) создается сигнал того или иного уровня. При превышении им определенного порога в блоке 2 в момент времени t1 формируется короткий импульс (фиг.4а), который осуществляет запись K•m-разрядного двоичного числа (K>1, m>1, например, номера датчика) в блоке 3 и переводит триггер 8 в противоположное состояние. Это приводит к обнулению блока 9, в результате чего с S выходов его разрядов (где S ближайшее большее к log2(m+1) число) сигналы логического "0" по шинам поступают на управляющие входы мультиплексоров (4-1)÷(4-K) с (m+1) информационными входами, на первые из которых (на фиг.3 не показаны) всегда подается сигнал "логического "0".

Общее число K•m выходов блока 3, на которых действуют символы сообщения, разбивается на К групп по m выходов в каждой группе (шине), так что ко вторым входам всех мультиплексоров (4-1)÷(4-K) по одному подключаются 1-й÷К-й выходы блока 3, к третьим (K+1)-й ÷ 2К-й выходы, к (m+1) входам [(m-1)K+1] -й÷K•m-й. Таким образом, в момент времени на выходе каждого блока 4 действует сигнал логического "0", поступающий с первого входа, двоичной сумматор 5 имеет группы по К входов. На К входов второй группы (на фиг.3 они не показаны) всегда подается двоичное число, равное в десятичной форме двум, поэтому в этот же момент времени только на одном из его (K+1) выходов, соответствующем второму младшему разряду, действует сигнал логической "1".

Полученное на выходе блока 5 число записывается в блок 6 перепадом напряжения с выхода триггера, поступающим через элементы НЕ 10 и ИЛИ 11 на вход записи кода блока 6. При этом его выходной сигнал сохраняется прежним и открывается счетный вход, на который поступают импульсы с блока 12 (фиг.4б) с периодом следования τ. Второй из них произведет обнуление блока 6 и на его выходе устанавливается уровень логического "0" до момента поступления третьего импульса (фиг. 4в). При этом откроется передатчик 7 и на его выходе сформируется синхросигнал - радиоимпульс длительности τ с определенной несущей частотой, а на выходе блока 13 в момент действия положительного фронта выходного импульса блока 6 (фиг.3в) - короткий импульс, который устанавливает младший разряд блока 9 в единичное состояние, и на выходы блоков 4 поступят логические сигналы, действующие на их вторых входах, поступающие по шинам с выходов блока 3.

В блоке 5 это двоичное число в параллельном виде увеличится на два и затем запишется выходным импульсом блока 11 в блоке 6. Момент появления нулевого сигнала на выходе последнего (и сигнала на выходе передатчика 7 зависит от значения двоичного числа, действующего на вторых входах блоков 4. Если оно в десятичной форме равно q(0≤q≤2K-1), то он появится через интервал времени (2 +q)τ относительно момента окончания синхросигнала (на фиг.4в - 4τ; K=2). Аналогичным образом осуществляется передача остальных К-разрядных двоичных чисел. При поступлении последнего (m+1)-гo импульса с генератора 12 на счетный вход блока 9 на его выходе формируется сигнал, который возвращает триггер 8 в исходное состояние и на выходе блока 6 будет действовать сигнал логической "1". Следующий сигнал на выходе датчика 1 может появиться только через интервал времени, больший или равный 2m(2+2K)•τ.

На приемной стороне принимаемый сигнал после фильтрации в приемнике 14, амплитудного детектирования в блоке 15 и фильтрации в ФНЧ 16 поступает на вход второго блока 17. При отсутствии помех на его выходе момент превышения сигналом порога формируется импульс с уровнем логической "1" и длительностью, близкой к значению τ, на втором входе первого элемента И 18 действует сигнал логической "1", на выходе элемента ИЛИ 31 логического "0" и на выходе триггера 32 логической "1". Поэтому первый импульс принимаемого сигнала (синхроимпульс) (фиг.4г) проходит через блок 18 и на выходе блока 19 по его переднему фронту формируется короткий импульс (фиг.4д), который запускает счетчик-распределитель 29 и осуществляет через блок 20 сброс делителя частоты 21. На первом, втором и третьем выходах последнего формируются меандры с периодами следования импульсов, соответственно, равными τ, 0,5τ и 16τ путем деления частоты ГТИ 26, равной 32/τ, а на четвертом выходе счетчика-распределителя 29 создается импульс длительности 0,5τ с задержкой относительно первого импульса фиг.4д на τ (фиг.4ж), который обнуляет блок 22 своим передним фронтом. После этого в блоке 22 осуществляется подсчет импульсов фиг. 4е. В результате к моменту прихода второго импульса фиг.4д в нем оказывается записанным в двоичном виде временное положение второго импульса фиг.4г относительно синхроимпульса.

Этот импульс производит обнуление и разрешение на подсчет импульсов в блоке 27, поступающих с ГТИ 26. В результате сигналами с К разрядов блока 27, действующими через шину на управляющие входы мультиплексора 23, данные К разрядов блока 22 поочередно поступают на вход сдвигового регистра 24 с (K+1)•m разрядами, на тактовый вход которого через блок 28 поступают импульсы с выхода первого разряда блока 27. При поступлении (К+1)-го импульса с ГТИ 26 на вход последнего сигнал с его второго выхода запрещает подсчет остальных импульсов до поступления следующего импульса с выхода блока 19.

Аналогичным образом осуществляется определение временного положения остальных (m-1) информационных импульсов. При отсутствии помех, как и раньше, после приема последнего из них на выходе элемента И 41 формируется положительный перепад напряжения (сигнал "сообщение принято"), который запускает оконечный блок 25 (например, ЭЦВМ). При этом на его первом выходе формируются тактовые импульсы с определенной частотой, считывающие на его вход данные с блока 24. После обработки информации в блоке 25 на его втором выходе формируется сигнал "сброс", который через блок 20 обнуляет блок 21 и через блок 34 блок 35 и триггер 37.

При наличии помех сигнал "сообщение принято" появится, если произойдут одновременно следующие события: на интервалах времени Тn>8τ до приема синхросигнала (стартовая пауза) и после последнего m-го импульса сообщения (стоповая пауза) не появится ложные импульсы на выходе блока 17, число импульсов на его выходе N будет равным (m+1), не произойдет переполнение счетчика 22, длительность принимаемых импульсов окажется меньше, например, 2τ, а защитной паузы больше, например, 1,5τ. Контроль длительности стартовой паузы осуществляется посредством блока 21.

Если в момент действия первого импульса на выходе блока 19 на третьем выходе блока 21 уровень сигнала равен логической "1" (что свидетельствует о том, что Тn>8τ), то это означает, что произошло обнуление триггера 32 и через элементы НЕ 33 и ИЛИ 34 - счетчика 35, в котором начнется подсчет числа импульсов, поступающих с выхода блока 18. При N - (m+1) на выходе блока 36 появится импульс, который установит триггер 37 в единичное состояние и откроется элемент И 41.

Если при этом у последнего (m+1)-го импульса принимаемого сигнала уровень сигнала на третьем выходе блока 21 будет равным "1" (что свидетельствует о наличии стоповой паузы), то на выходе элемента И 41 появится положительный импульс, разрешающий прием сообщения, а на выходе блока 42 сигнал логического "0", запрещающий передачу сигналов через элемент И 18. Д-триггеры 30 и 40 предназначены для контроля длительностей импульсов сообщения. Выходными импульсами блока 19 они обнуляются; на их вторые входы подаются импульсы с выхода блока 18, а на третьи - с первого (фиг.4з) и второго (фиг.4и) выходов счетчика-распределителя 29 соответственно; по заднему фронту последнего осуществляется его блокировка до прихода следующего импульса с выхода блока 19 (фиг.4к).

Если отсутствует перекрытие по времени импульсов, действующих на первых и вторых их входах, то их состояние не изменяется. При отсутствии стартовой паузы не будет производиться подсчет импульсов в блоке 35, N будет меньше (m+1), на выходе элемента НЕ 36 (на втором входе блока 39) будет действовать сигнал логической "1" и, если при этом произойдет переполнение блока 22, то на выходах блока 45, блока 39 и элемента ИЛИ 31 появится импульс, устанавливающий триггер 32 в исходное состояние.

То же самое произойдет при переполнении, если N - (m+1). Такой же сигнал возникнет на ее выходе, если произойдет перекрытие импульсов хотя бы в одном из Д-триггеров 30 и 40, или в случае, когда число N окажется большим (m+1) при выполнении прочих условий. Последнее приведет к появлению импульса на выходе блока 43, который через открытый выходным сигналом блока 42 элемент И 44 и элемент ИЛИ 31 поступит на первый вход триггера 32.

Таким образом, предлагаемая стартстопная система связи позволяет существенно уменьшить вероятность ложных срабатываний.

При практически используемых значениях вероятности правильного приема сообщения, равных 0,95-0,999, вероятность ложных срабатываний в ней имеет порядок 10-25-10-15. В прототипе в лучшем случае можно достичь значения этой вероятности порядка 10-10.

Все блоки, входящие в систему связи, являются устройствами известными. Двоичный сумматор 5 может быть выполнен на микросхемах 564ИМ1 [4], счетчики 22, 27 - на 564ИЕ10 [4], счетчик 29 на 564ИЕ9 [4], цифровые компараторы 36, 43 на 564ИМ1 [4].

Источники информации

1. Патент РФ 2103827, Н 04 J 11/00, H 04 Q 11/00.

2. В. И. Николаев, Г.Б. Волобуев, В.И. Дедовских. О помехоустойчивости m-ичных сигналов при стартстопной передаче сообщений. Телекоммуникации, 1, 2001, с.38-41, (ООО "Наука и технологии", М., 2001).

3. Ю.С. Лезин. Введение в теорию и технику радиотехнических систем. М.: Радио и связь, 1986.

4. Е. А. Зельдин. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре. Л.: Энергоиздат, 1986.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2006 |

|

RU2312465C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2261531C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Пороговое устройство | 1986 |

|

SU1368979A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396722C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2004 |

|

RU2270527C1 |

| Оптоэлектронное устройство ввода информации | 1987 |

|

SU1501022A1 |

| Устройство для цифровой записи-воспроизведения речевой информации | 1987 |

|

SU1490691A1 |

Изобретение относится к области электро- и радиосвязи и может быть использовано в проводных, радио-, радиорелейных и метеорных линиях связи. Для уменьшения вероятности ложных срабатываний в систему связи-прототип на передающей стороне введен дифференцирующий блок 13, на приемной стороне - второй - пятый элементы ИЛИ, делитель 21 частоты, (К+1)-й мультиплексор 23, оконечный блок 25, счетчик-распределитель 29, первый 30 и второй 40 Д-триггеры, второй формирователь 45 импульсов, второй 32 и третий 37 триггеры, первый 36 и второй 43 цифровые компараторы, четвертый двоичный счетчик 35, первый - четвертый 18, 39, 41, 44 элементы И, второй - четвертый 33, 38, 42 элементы НЕ, а также генератор 26 тактовых импульсов. 4 ил.

Стартстопная система связи, содержащая на передающей стороне последовательно соединенные датчик, первый пороговый блок и запоминающий блок, а также К мультиплексоров, ко вторым входам которых по одному подключены выходы запоминающего блока с 1-го по К-й, к третьим входам - выходы с (К+1)-го по 2К-ый, к (m+1)-м входам - выходы с [(m-1)К+1]-го по К m-й, выходы К мультиплексоров соединены с К входами двоичного сумматора соответственно, выход которого шиной соединен с информационным входом вычитающего счетчика, выход которого соединен с входом передатчика, выход которого соединен с входом линии связи, а также последовательно соединенные первый триггер и первый двоичный счетчик, первый выход которого соединен со вторым входом первого триггера, второй выход первого двоичного счетчика шиной соединен с управляющими входами К мультиплексоров, кроме того, последовательно соединенные первые элементы НЕ и ИЛИ, выход которого соединен с входом разрешения записи кода вычитающего счетчика, при этом, вход первого элемента НЕ соединен с выходом первого триггера, вход которого соединен с выходом первого порогового блока, счетный вход первого двоичного счетчика соединен со вторым входом первого элемента ИЛИ, выход генератора импульсов соединен со счетным входом вычитающего счетчика, на приемной стороне содержит последовательно соединенные приемник, амплитудный детектор и фильтр нижних частот, а также первый формирователь импульсов, второй и третий двоичные счетчики, второй пороговый блок и сдвиговый регистр, при этом выход первого формирователя импульсов соединен с установочным входом третьего двоичного счетчика, выход линии связи соединен с входом приемника, отличающаяся тем, что на передающей стороне введен дифференцирующий блок, вход которого соединен с выходом вычитающего счетчика, а выход - со вторым входом первого элемента ИЛИ, на приемной стороне введены первый элемент И, последовательно соединенные второй элемент ИЛИ и делитель частоты, а также (К+1)-й мультиплексор, последовательно соединенные оконечный блок и третий элемент ИЛИ, последовательно соединенный счетчик-распределитель, первый Д-триггер, четвертый элемент ИЛИ, второй триггер, второй элемент НЕ, пятый элемент ИЛИ и четвертый двоичный счетчик, выход которого соединен шиной с входами первого и второго цифровых компараторов, выход первого цифрового компаратора через последовательно соединенные третий триггер и третий элемент НЕ соединен с первым входом второго элемента И, выход которого соединен с третьим входом четвертого элемента ИЛИ, выход второго цифрового компаратора через четвертый элемент И соединен со вторым входом четвертого элемента ИЛИ, последовательно соединенные третий элемент И и четвертый элемент НЕ, выход которого соединен со вторыми входами первого и четвертого элементов И, первый вход третьего элемента И соединен с третьим выходом делителя частоты и вторым входом второго триггера, второй вход третьего элемента И соединен с выходом третьего триггера, установочный вход которого соединен с выходом пятого элемента ИЛИ, выход третьего элемента И соединен с тактовым входом оконечного блока, второй выход которого соединен со вторыми входами второго и пятого элементов ИЛИ, кроме того, выход первого элемента И соединен с информационными входами первого и второго Д-триггеров и счетным входом четвертого двоичного счетчика, первый вход счетчика-распределителя соединен с выходом первого формирователя импульсов и установочными входами первого и второго Д-триггеров, причем стробирующий вход второго Д-триггера соединен со вторым выходом счетчика-распределителя, третий выход которого соединен с его установочным входом, счетный вход счетчика-распределителя подсоединен к второму выходу делителя частоты, четвертый выход счетчика-распределителя соединен с установочным входом второго двоичного счетчика, выход переполнения которого соединен с входом второго формирователя импульсов, выход которого соединен со вторым входом второго элемента И, выход второго Д-триггера соединен с четвертым входом четвертого элемента ИЛИ, при этом выход генератора тактовых импульсов соединен с тактовым входом делителя частоты и счетным входом третьего двоичного счетчика, второй выход которого соединен со вторым входом третьего элемента ИЛИ, третий выход третьего двоичного счетчика соединен с его запрещающим входом, первый выход третьего двоичного счетчика шиной соединен с управляющим входом (К+1)-го мультиплексора, выход которого соединен с входом сдвигового регистра, выход которого соединен с входом оконечного блока, вход (К+1)-го мультиплексора шиной соединен с выходом второго двоичного счетчика, первый вход которого соединен с первым выходом делителя частоты, выход третьего элемента ИЛИ соединен с тактовым входом сдвигового регистра, выход фильтра нижних частот через последовательно соединенные второй пороговый блок, первый элемент И и первый формирователь импульсов соединен с входом второго элемента ИЛИ.

| МНОГОКАНАЛЬНАЯ СИСТЕМА СВЯЗИ | 1996 |

|

RU2103827C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 1999 |

|

RU2157053C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2000 |

|

RU2168867C1 |

| US 5623522, 22.04.1997 | |||

| JP 2001127744, 11.05.2001 | |||

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| НИКОЛАЕВ В.И | |||

| и др | |||

| О помехоустойчивости m-ичных сигналов при стартстопной передаче сообщений | |||

| Телекоммуникации | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

Авторы

Даты

2003-12-10—Публикация

2002-03-11—Подача